FPGA協处理技術(shù)介紹及(jí)進(jìn)展(zhǎn)

FPGA的(de)架構使得许多(duō)算法得以(yǐ)实現(xiàn),較之采用(yòng)四(sì)核CPU或(huò)通(tòng)用(yòng)图(tú)形处理器(GPGPU),这(zhè)些算法的(de)持(chí)續性(xìng)能(néng)更(gèng)接近(jìn)器件(jiàn)的(de)峰(fēng)值性(xìng)能(néng)。随着对(duì)芯片(piàn)、算法和(hé)庫基礎的(de)集中(zhōng)改進(jìn),FPGA加速器的(de)基準测試結果(guǒ)不(bù)斷提(tí)高(gāo)。就(jiù)算當前(qián)最(zuì)大的(de)FPGA所(suǒ)消耗的(de)功率也(yě)不(bù)到(dào)30W,因(yīn)此(cǐ)它(tā)们(men)可(kě)應(yìng)用(yòng)于(yú)多(duō)種(zhǒng)场合。在(zài)目前(qián)出(chū)現(xiàn)的(de)幾(jǐ)大行業動(dòng)态的(de)共(gòng)同(tóng)作用(yòng)下(xià),FPGA实現(xiàn)的(de)算法加速更(gèng)加令人(rén)矚目。这(zhè)些行業動(dòng)态包(bāo)括:

● 當前(qián)FPGA的(de)容量(liàng)已足够容納更(gèng)大的(de)算法。現(xiàn)在(zài)已經(jīng)有(yǒu)可(kě)能(néng)将期(qī)權定(dìng)價算法或(huò)1M點(diǎn)快(kuài)速傅里(lǐ)葉(yè)變(biàn)換放(fàng)入(rù)FPGA。将算法從CPU中(zhōng)加载到(dào)FPGA的(de)延遲时(shí)間(jiān)小于(yú)算法加速所(suǒ)节(jié)省(shěng)的(de)时(shí)間(jiān)。

● 單核CPU在(zài)功耗和(hé)冷(lěng)卻問(wèn)題(tí)上(shàng)受到(dào)了(le)限制。采用(yòng)多(duō)核CPU的(de)嘗試正(zhèng)在(zài)順利進(jìn)行,但現(xiàn)有(yǒu)为(wèi)單核編写的(de)软(ruǎn)件(jiàn)必須進(jìn)行重(zhòng)写,用(yòng)以(yǐ)支持(chí)合理的(de)性(xìng)能(néng)擴展(zhǎn)。

● FPGA協处理的(de)主(zhǔ)動(dòng)式支持(chí)。在(zài)某些情(qíng)況下(xià),这(zhè)些CPU接口(kǒu)(AMD公司的(de)Torrenza IniTIaTIve與(yǔ)Intel公司面(miàn)向(xiàng)FPGA廠(chǎng)商的(de)注册FSB與(yǔ)QPI)支持(chí)8 GB/s的(de)速率,写入(rù)等待时(shí)間(jiān)低于(yú)140ns。

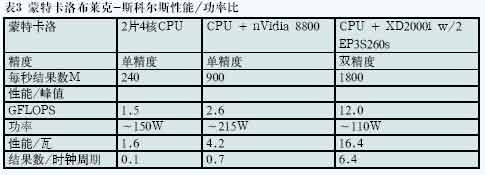

較之双(shuāng)核、四(sì)核CPU或(huò)GPGPU,FPGA基準测試結果(guǒ)顯示了(le)采用(yòng)插槽式加速器的(de)优异(yì)的(de)蒙特(tè)卡(kǎ)洛浮點(diǎn)結果(guǒ)(見(jiàn)表(biǎo)1)。

就(jiù)結果(guǒ)而(ér)言,運行頻率为(wèi)150~250 MHz之間(jiān)的(de)FPGA是(shì)如(rú)何做到(dào)优于(yú)運行頻率为(wèi)2~3 GHz的(de)四(sì)核CPU或(huò)運行頻率为(wèi)1.35 GHz的(de)128核GPU的(de)呢?正(zhèng)如(rú)蒙特(tè)卡(kǎ)洛布(bù)莱克(kè)-斯科爾算法所(suǒ)示,FPGA架構具有(yǒu)独特(tè)的(de)性(xìng)能(néng),这(zhè)是(shì)産生(shēng)这(zhè)一(yī)优异(yì)結果(guǒ)的(de)原因(yīn)之一(yī)。

FPGA架構特(tè)征

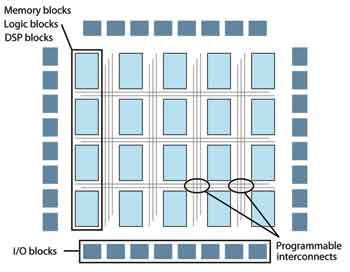

靈活的(de)FPGA可(kě)根(gēn)據(jù)需要(yào)進(jìn)行編程和(hé)重(zhòng)新編程。一(yī)个(gè)典型的(de)FPGA包(bāo)括一(yī)个(gè)邏輯块(kuài)阵(zhèn)列、內(nèi)存块(kuài)和(hé)DSP块(kuài),它(tā)们(men)周邊(biān)环(huán)繞着可(kě)由(yóu)软(ruǎn)件(jiàn)進(jìn)行配置的(de)可(kě)編程式互連(lián)結構(如(rú)图(tú)1所(suǒ)示)。該架構确保下(xià)列特(tè)征的(de)实現(xiàn)。

● 功能(néng)并行:功能(néng)的(de)多(duō)次(cì)重(zhòng)複

● 數據(jù)并行:处理數據(jù)阵(zhèn)列或(huò)數據(jù)矩阵(zhèn)

● 流水(shuǐ)化(huà)的(de)自(zì)定(dìng)義指令:每个(gè)时(shí)鐘(zhōng)周期(qī)輸出(chū)流數據(jù)的(de)一(yī)个(gè)結果(guǒ)

● 超大的(de)主(zhǔ)緩沖带(dài)宽(kuān)與(yǔ)規模:GPGPU的(de)3~10倍

● 靈活的(de)數據(jù)通(tòng)路(lù)布(bù)線(xiàn):巨型交叉(chā)連(lián)通(tòng)在(zài)一(yī)个(gè)时(shí)鐘(zhōng)周期(qī)內(nèi)完成(chéng)數據(jù)傳輸

● 功能(néng)和(hé)數據(jù)流的(de)串聯:均在(zài)一(yī)个(gè)时(shí)鐘(zhōng)周期(qī)內(nèi)完成(chéng)

● 定(dìng)制片(piàn)外(wài)I/O:所(suǒ)需的(de)協議、带(dài)宽(kuān)和(hé)延遲

● 可(kě)擴展(zhǎn)的(de)路(lù)徑图(tú):更(gèng)大的(de)阵(zhèn)列具有(yǒu)充足的(de)空間(jiān)支持(chí)供電(diàn)與(yǔ)冷(lěng)卻

顯然,FPGA在(zài)并行化(huà)與(yǔ)流水(shuǐ)化(huà)方(fāng)面(miàn)存在(zài)相當大的(de)优勢,同(tóng)时(shí)與(yǔ)GPGPU相比,FPGA在(zài)主(zhǔ)緩存與(yǔ)带(dài)宽(kuān)方(fāng)面(miàn)也(yě)存在(zài)优勢。在(zài)FPGA中(zhōng),邏輯資源周圍是(shì)存儲器块(kuài)。XDI模块(kuài)具有(yǒu)一(yī)块(kuài)带(dài)宽(kuān)为(wèi)3.8TB/s的(de)3.3MB主(zhǔ)緩存,这(zhè)是(shì)nVidia 8800 GTX型GPGPU上(shàng)主(zhǔ)緩存(支持(chí)流处理器)的(de)5~10倍。

FPGA的(de)优勢還(huán)在(zài)于(yú),可(kě)以(yǐ)利用(yòng)裕量(liàng)連(lián)接带(dài)宽(kuān)来(lái)靈活構建直(zhí)达(dá)各(gè)邏輯块(kuài)的(de)數據(jù)通(tòng)道(dào)和(hé)存儲器訪問(wèn)通(tòng)路(lù)。图(tú)1所(suǒ)示的(de)可(kě)編程互連(lián)結構提(tí)供了(le)大量(liàng)的(de)布(bù)線(xiàn)带(dài)宽(kuān)。模块(kuài)與(yǔ)電(diàn)路(lù)板可(kě)根(gēn)據(jù)FPGA輸出(chū)带(dài)宽(kuān)、存儲器大小及(jí)延遲的(de)需要(yào)進(jìn)行設計(jì),I/O端口(kǒu)可(kě)由(yóu)用(yòng)戶自(zì)定(dìng)義。

图(tú)1 FPGA的(de)架構

最(zuì)後(hòu),FPGA架構還(huán)擁有(yǒu)一(yī)个(gè)优勢,它(tā)可(kě)擴展(zhǎn)为(wèi)更(gèng)大型的(de)邏輯块(kuài)、存儲器块(kuài)與(yǔ)DSP块(kuài)的(de)阵(zhèn)列。邏輯與(yǔ)主(zhǔ)緩存的(de)大小是(shì)一(yī)起擴展(zhǎn)的(de)。現(xiàn)有(yǒu)最(zuì)大的(de)FPGA峰(fēng)值功耗为(wèi)30W,其FPGA架構有(yǒu)很多(duō)空間(jiān),可(kě)以(yǐ)在(zài)不(bù)超过(guò)現(xiàn)有(yǒu)數據(jù)中(zhōng)心(xīn)功率和(hé)冷(lěng)卻限制的(de)前(qián)提(tí)下(xià),擴展(zhǎn)为(wèi)新的(de)处理構型。

盡管(guǎn)FPGA架構具有(yǒu)许多(duō)出(chū)衆的(de)性(xìng)能(néng),一(yī)些性(xìng)能(néng)必須共(gòng)同(tóng)發(fà)揮作用(yòng),才能(néng)提(tí)供优于(yú)CPU協处理的(de)解(jiě)決方(fāng)案(àn)。

芯片(piàn)與(yǔ)算法基礎

大部(bù)分(fēn)双(shuāng)精度(dù)浮點(diǎn)算法的(de)加法與(yǔ)乘法操作比例大約为(wèi)1:1。在(zài)FPGA中(zhōng),加法運算使用(yòng)邏輯資源,乘法運算使用(yòng)DSP块(kuài),因(yīn)此(cǐ)FPGA的(de)邏輯資源與(yǔ)DSP块(kuài)的(de)比例必須均衡。FPGA的(de)另(lìng)一(yī)个(gè)特(tè)點(diǎn)是(shì)其可(kě)編程功率技術(shù),該技術(shù)可(kě)針(zhēn)对(duì)所(suǒ)有(yǒu)邏輯块(kuài)、DSP块(kuài)與(yǔ)存儲器块(kuài)進(jìn)行編程,根(gēn)據(jù)設計(jì)的(de)时(shí)序要(yào)求将其設定(dìng)为(wèi)高(gāo)功耗或(huò)低功耗模式。

浮點(diǎn)運算核已經(jīng)改進(jìn),可(kě)運行于(yú)更(gèng)高(gāo)的(de)时(shí)鐘(zhōng)速率,使用(yòng)更(gèng)少(shǎo)的(de)DSP块(kuài)和(hé)更(gèng)少(shǎo)的(de)邏輯資源。采用(yòng)浮點(diǎn)編譯器可(kě)減少(shǎo)不(bù)同(tóng)浮點(diǎn)運算核之間(jiān)用(yòng)于(yú)連(lián)接64位數據(jù)通(tòng)路(lù)的(de)邏輯資源。

在(zài)一(yī)次(cì)浮點(diǎn)運算結束(shù)时(shí),合并对(duì)浮點(diǎn)運算進(jìn)行規格化(huà)处理(定(dìng)點(diǎn)格式轉(zhuǎn)換至(zhì)浮點(diǎn)格式)的(de)步驟,可(kě)以(yǐ)顯著減少(shǎo)对(duì)後(hòu)續浮點(diǎn)運算輸入(rù)的(de)去(qù)規格化(huà)处理(浮點(diǎn)格式轉(zhuǎn)換为(wèi)定(dìng)點(diǎn)格式)。浮點(diǎn)運算的(de)數学表(biǎo)达(dá)式的(de)整个(gè)數據(jù)通(tòng)路(lù)可(kě)熔接在(zài)一(yī)起,这(zhè)会(huì)最(zuì)多(duō)減少(shǎo)40%的(de)邏輯資源并使时(shí)鐘(zhōng)速率略有(yǒu)提(tí)高(gāo)。

浮點(diǎn)運算的(de)正(zhèng)确組合十(shí)分(fēn)重(zhòng)要(yào)。如(rú)果(guǒ)算法有(yǒu)许多(duō)超越運算(求指數、求对(duì)數等),FPGA可(kě)配置所(suǒ)需要(yào)的(de)數目。在(zài)GPGPU設計(jì)中(zhōng),会(huì)增加一(yī)些硬(yìng)模块(kuài)实現(xiàn)上(shàng)述函(hán)數,但比例比單精度(dù)浮點(diǎn)邏輯少(shǎo)得多(duō)。使用(yòng)算法技巧、抽象(xiàng)硬(yìng)件(jiàn)细(xì)节(jié)及(jí)針(zhēn)对(duì)个(gè)别FPGA資源的(de)优化(huà)都需要(yào)函(hán)數庫。

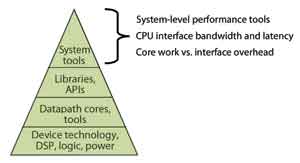

基于(yú)芯片(piàn)、算法與(yǔ)庫基礎,图(tú)2的(de)系(xì)統級解(jiě)決方(fāng)案(àn)涉及(jí)到(dào)了(le)工具鍊(liàn)、模块(kuài)/板級設計(jì)、CPU接口(kǒu)以(yǐ)及(jí)采用(yòng)合作公司專門(mén)技術(shù)的(de)由(yóu)CPU至(zhì)基于(yú)FPGA的(de)加速器的(de)數據(jù)傳輸。

图(tú)2 FPGA加速系(xì)統級解(jiě)決方(fāng)案(àn)的(de)基礎

使持(chí)續性(xìng)能(néng)接近(jìn)峰(fēng)值

对(duì)于(yú)可(kě)并行化(huà)或(huò)流水(shuǐ)化(huà)的(de)任务,相对(duì)于(yú)峰(fēng)值性(xìng)能(néng)而(ér)言,FPGA經(jīng)常能(néng)够大大提(tí)高(gāo)持(chí)續性(xìng)能(néng),并可(kě)利用(yòng)各(gè)器件(jiàn)資源。以(yǐ)一(yī)个(gè)蒙特(tè)卡(kǎ)洛布(bù)莱克(kè)-斯科爾斯基準测試程序为(wèi)例,它(tā)可(kě)建立一(yī)条(tiáo)運行頻率为(wèi)150MHz的(de)等式流水(shuǐ)線(xiàn)。

在(zài)每个(gè)时(shí)鐘(zhōng)周期(qī),FPGA通(tòng)过(guò)梅森(sēn)素數旋轉(zhuǎn)核産生(shēng)的(de)随機(jī)數被(bèi)輸入(rù)(接入(rù))“定(dìng)制指令”,每个(gè)时(shí)鐘(zhōng)周期(qī)産生(shēng)一(yī)个(gè)結果(guǒ)。12条(tiáo)“定(dìng)制指令”與(yǔ)模块(kuài)的(de)两(liǎng)片(piàn)FPGA匹(pǐ)配,利用(yòng)双(shuāng)精度(dù)浮點(diǎn)邏輯輸出(chū)12&TImes;150M=1.8G結果(guǒ)/秒(miǎo)。通(tòng)过(guò)額外(wài)倍頻,可(kě)預期(qī)实現(xiàn)性(xìng)能(néng)为(wèi)上(shàng)述性(xìng)能(néng)的(de)两(liǎng)倍。

对(duì)比不(bù)同(tóng)架構的(de)浮點(diǎn)能(néng)力持(chí)續性(xìng)能(néng)與(yǔ)峰(fēng)值性(xìng)能(néng)十(shí)分(fēn)有(yǒu)趣。表(biǎo)2給(gěi)出(chū)了(le)四(sì)種(zhǒng)可(kě)能(néng)解(jiě)決方(fāng)案(àn)的(de)單精度(dù)浮點(diǎn)峰(fēng)值性(xìng)能(néng)。由(yóu)于(yú)布(bù)莱克(kè)-斯科爾斯公式需要(yào)常規加法與(yǔ)乘法函(hán)數以(yǐ)外(wài)更(gèng)多(duō)的(de)函(hán)數(指數、平方(fāng)根(gēn)等),布(bù)莱克(kè)-斯科爾斯結果(guǒ)的(de)總(zǒng)GFLOPS未作統計(jì)。

表(biǎo)3給(gěi)出(chū)了(le)布(bù)莱克(kè)-斯科爾斯結果(guǒ)與(yǔ)峰(fēng)值GFLOPS的(de)比例,作为(wèi)比較持(chí)續性(xìng)能(néng)與(yǔ)峰(fēng)值性(xìng)能(néng)的(de)一(yī)種(zhǒng)相对(duì)衡量(liàng)方(fāng)法。相比峰(fēng)值性(xìng)能(néng),FPGA达(dá)到(dào)了(le)最(zuì)佳持(chí)續性(xìng)能(néng)。相比另(lìng)外(wài)两(liǎng)種(zhǒng)加速器的(de)單精度(dù)邏輯,FPGA的(de)双(shuāng)精度(dù)邏輯具有(yǒu)最(zuì)优原始性(xìng)能(néng)以(yǐ)及(jí)最(zuì)优的(de)“性(xìng)能(néng)/瓦(wǎ)”參數。

对(duì)许多(duō)包(bāo)含并行性(xìng)或(huò)可(kě)流水(shuǐ)化(huà)的(de)算法而(ér)言,由(yóu)于(yú)裕量(liàng)連(lián)接带(dài)宽(kuān)可(kě)实現(xiàn)用(yòng)戶自(zì)定(dìng)義的(de)數據(jù)通(tòng)路(lù),这(zhè)樣(yàng),邏輯可(kě)在(zài)一(yī)个(gè)时(shí)鐘(zhōng)周期(qī)內(nèi)訪問(wèn)存儲器或(huò)訪問(wèn)另(lìng)一(yī)个(gè)邏輯块(kuài)的(de)結果(guǒ),從而(ér)使FPGA的(de)持(chí)續性(xìng)能(néng)可(kě)接近(jìn)峰(fēng)值性(xìng)能(néng)。由(yóu)于(yú)固定(dìng)架構具備預先(xiān)确定(dìng)的(de)用(yòng)以(yǐ)实現(xiàn)不(bù)同(tóng)功能(néng)的(de)邏輯块(kuài)集合,所(suǒ)以(yǐ)可(kě)以(yǐ)为(wèi)FPGA配置支持(chí)某種(zhǒng)給(gěi)定(dìng)算法的(de)最(zuì)优邏輯函(hán)數比例来(lái)实現(xiàn)器件(jiàn)資源的(de)最(zuì)佳利用(yòng)。

文(wén)章(zhāng)出(chū)处:http://www.elecfans.com/emb/fpga/20100426216794.html

更(gèng)多(duō)資訊請關(guān)注:http://www.minyingyiyuan.com/product/www.minyingyiyuan.com