实验(yàn)簡述

将輸入(rù)的(de)數據(jù)流經(jīng)过(guò)曼徹斯特(tè)編碼器編碼後(hòu)經(jīng)过(guò)解(jiě)碼器恢複为(wèi)原来(lái)的(de)輸入(rù)序列。

一(yī)、曼徹斯特(tè)碼簡介

曼徹斯特(tè)碼(Manchester code),又稱數字(zì)双(shuāng)向(xiàng)碼、分(fēn)相碼或(huò)相位編碼(PE),是(shì)一(yī)種(zhǒng)常用(yòng)的(de)二(èr)源碼線(xiàn)路(lù)編碼方(fāng)式之一(yī),被(bèi)物(wù)理层使用(yòng)来(lái)編碼一(yī)个(gè)同(tóng)步位流的(de)时(shí)鐘(zhōng)和(hé)數據(jù)。在(zài)通(tòng)信(xìn)技術(shù)中(zhōng),用(yòng)来(lái)表(biǎo)示所(suǒ)要(yào)發(fà)送比特(tè)流中(zhōng)的(de)數據(jù)宇定(dìng)时(shí)信(xìn)号(hào)所(suǒ)結合起来(lái)的(de)代(dài)碼。常用(yòng)在(zài)以(yǐ)太网(wǎng)通(tòng)信(xìn),列車總(zǒng)線(xiàn)控制,工業總(zǒng)線(xiàn)等領域。

二(èr)、編碼規則

有(yǒu)两(liǎng)个(gè)輸入(rù)时(shí)鐘(zhōng),一(yī)个(gè)是(shì)基带(dài)时(shí)鐘(zhōng)(起同(tóng)步信(xìn)号(hào)作用(yòng)),一(yī)个(gè)是(shì)頻带(dài)时(shí)鐘(zhōng)。輸入(rù)的(de)數據(jù)流是(shì)基带(dài)时(shí)鐘(zhōng)域信(xìn)号(hào),經(jīng)过(guò)編碼後(hòu)變(biàn)成(chéng)頻带(dài)时(shí)鐘(zhōng)域信(xìn)号(hào)輸出(chū)。曼徹斯特(tè)編碼是(shì)将輸入(rù)为(wèi)1的(de)變(biàn)成(chéng)輸出(chū)前(qián)半拍为(wèi)1,後(hòu)半拍为(wèi)0,輸入(rù)为(wèi)0的(de)變(biàn)成(chéng)前(qián)半拍为(wèi)0,後(hòu)半拍为(wèi)1的(de)頻带(dài)信(xìn)号(hào)。

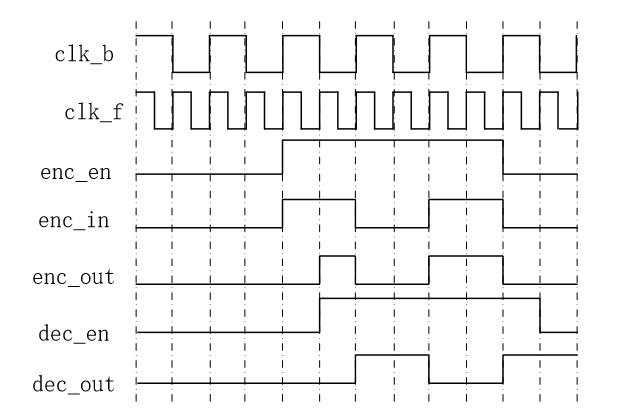

三(sān)、时(shí)序图(tú)

輸入(rù)序列以(yǐ)101为(wèi)例,經(jīng)过(guò)編碼後(hòu)應(yìng)为(wèi)100110

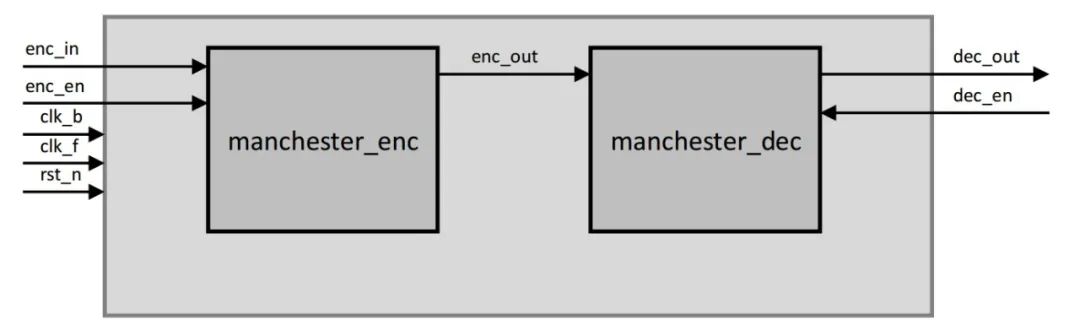

四(sì)、FPGA实現(xiàn)

1、頂层架構

2、信(xìn)号(hào)说(shuō)明(míng)

|

信(xìn)号(hào) |

功能(néng) |

说(shuō)明(míng) |

|

clk_b |

基带(dài)时(shí)鐘(zhōng),作为(wèi)同(tóng)步信(xìn)号(hào)使用(yòng) |

外(wài)部(bù)輸入(rù) |

|

clk_f |

頻带(dài)时(shí)鐘(zhōng),系(xì)統工作时(shí)鐘(zhōng) |

外(wài)部(bù)輸入(rù) |

|

rst_n |

系(xì)統複位 |

外(wài)部(bù)輸入(rù) |

|

enc_in |

輸入(rù)數據(jù)流 |

外(wài)部(bù)輸入(rù) |

|

enc_en |

編碼使能(néng) |

外(wài)部(bù)輸入(rù) |

|

enc_out |

數據(jù)流經(jīng)編碼後(hòu)的(de)輸出(chū),輸入(rù)到(dào)解(jiě)碼模块(kuài) |

編碼輸出(chū),解(jiě)碼輸入(rù) |

|

dec_en |

解(jiě)碼使能(néng) |

外(wài)部(bù)輸入(rù) |

|

dec_out |

解(jiě)碼輸出(chū) |

輸出(chū) |

3、頂层代(dài)碼

|

module manchester(clk_b, clk_f, rst_n, enc_in, enc_en, dec_out, dec_en);

input clk_b, clk_f, rst_n; input enc_in; input enc_en; output dec_out; input dec_en;

wire enc_out;

manchester_enc ENC( .clk_f(clk_f), .clk_b(clk_b), .rst_n(rst_n), .enc_en(enc_en), .enc_in(enc_in), .enc_out(enc_out) );

manchester_dec DEC( .clk_f(clk_f), .clk_b(clk_b), .rst_n(rst_n), .dec_en(dec_en), .enc_out(enc_out), .dec_out(dec_out) );

endmodule

|

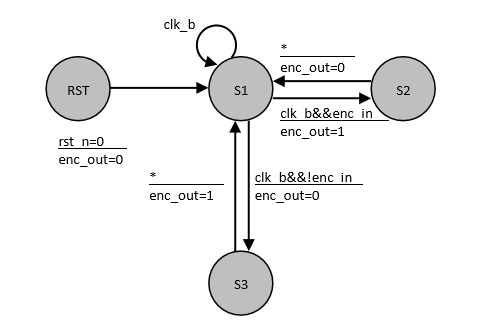

4、編碼模块(kuài)

采用(yòng)狀态機(jī)来(lái)实現(xiàn)編碼模块(kuài)。

當檢测到(dào)編碼使能(néng)为(wèi)高(gāo)时(shí),狀态機(jī)開(kāi)始執行,判斷clk_b的(de)值为(wèi)1时(shí),在(zài)S1狀态等待,當clk_b的(de)值为(wèi)0时(shí),判斷輸入(rù)的(de)值是(shì)1還(huán)是(shì)0。(clk_b主(zhǔ)要(yào)起基頻同(tóng)步作用(yòng))如(rú)果(guǒ)是(shì)1,跳轉(zhuǎn)到(dào)S2狀态,并将enc_out賦值为(wèi)1。到(dào)S2狀态後(hòu),无条(tiáo)件(jiàn)跳回(huí)S1狀态,并将enc_out賦值为(wèi)0。如(rú)果(guǒ)是(shì)0,跳轉(zhuǎn)到(dào)S3狀态,并将enc_out賦值为(wèi)0。到(dào)S3狀态後(hòu),无条(tiáo)件(jiàn)跳回(huí)S1狀态,并将enc_out賦值为(wèi)1。

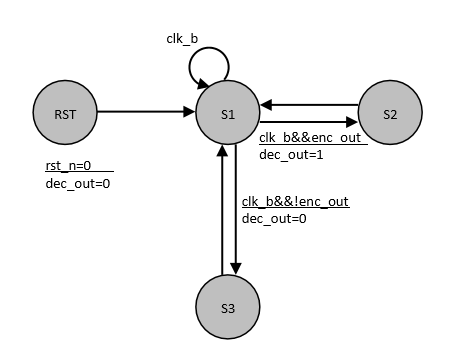

狀态轉(zhuǎn)移图(tú)如(rú)下(xià):

说(shuō)明(míng):圆(yuán)圈代(dài)表(biǎo)狀态,→ 代(dài)表(biǎo)轉(zhuǎn)移,轉(zhuǎn)移下(xià)面(miàn)的(de)文(wén)本(běn)框代(dài)表(biǎo)轉(zhuǎn)移时(shí)的(de)動(dòng)作。以(yǐ)後(hòu)文(wén)章(zhāng)的(de)狀态轉(zhuǎn)移图(tú)均按此(cǐ)繪制。

|

module manchester_enc(clk_f, clk_b, rst_n, enc_en, enc_in, enc_out);

input clk_f, clk_b, rst_n; input enc_en; input enc_in; output reg enc_out;

reg [2:0] state_c, state_n;

localparam S1 = 3'b001; localparam S2 = 3'b010; localparam S3 = 3'b100;

wire S12S2_start ; wire S12S3_start ; wire S22S1_start ; wire S33S1_start ;

//四(sì)段(duàn)式狀态機(jī)

//第(dì)一(yī)段(duàn):同(tóng)步时(shí)序always模块(kuài),格式化(huà)描述次(cì)态寄存器遷移到(dào)現(xiàn)态寄存器(不(bù)需更(gèng)改- always@(posedge clk_f or negedge rst_n)begin if(!rst_n)begin state_c <= S1; end else begin state_c <= state_n; end end

//第(dì)二(èr)段(duàn):組合邏輯always模块(kuài),描述狀态轉(zhuǎn)移条(tiáo)件(jiàn)判斍 always@(*)begin if(enc_en) case(state_c) S1:begin if(S12S2_start)begin state_n = S2; end else if(S12S3_start)begin state_n = S3; end else begin state_n = state_c; end end S2:begin if(S22S1_start)begin state_n = S1; end else begin state_n = state_c; end end S3:begin if(S33S1_start)begin state_n = S1; end else begin state_n = state_c; end end default:begin state_n = S1; end endcase else state_n = S1; end //第(dì)三(sān)段(duàn):設計(jì)轉(zhuǎn)移条(tiáo)件(jiàn) assign S12S2_start = state_c==S1 && clk_b && !enc_in; assign S12S3_start = state_c==S1 && clk_b && enc_in; assign S22S1_start = state_c==S2 && 1; assign S33S1_start = state_c==S3 && 1;

//第(dì)四(sì)段(duàn):同(tóng)步时(shí)序always模块(kuài),格式化(huà)描述寄存器輸出(chū)(可(kě)有(yǒu)多(duō)个(gè)輸出(chū)- always @(posedge clk_f or negedge rst_n)begin if(!rst_n)begin enc_out <=1'b0; //初始匍 end else if(enc_en) if((state_c==S1 && !enc_in) || (state_c==S3))begin enc_out <= 1'b0; end else if((state_c==S1 && enc_in) || (state_c==S2))begin enc_out <= 1'b1; end else begin enc_out <= 1'b0; end else enc_out <=1'b0; end

endmodule

|

5、 解(jiě)碼模块(kuài)

解(jiě)碼模块(kuài)也(yě)采用(yòng)狀态機(jī)实現(xiàn),當檢测到(dào)dec_en为(wèi)高(gāo)时(shí),狀态機(jī)才執行,判斷clk_b的(de)值,當clk_b为(wèi)0时(shí),在(zài)S1上(shàng)等待,當clk_b为(wèi)1时(shí),判斷enc_out的(de)值,为(wèi)1时(shí)跳轉(zhuǎn)到(dào)S2狀态,并将dec_out賦值为(wèi)。S2狀态无条(tiáo)件(jiàn)跳轉(zhuǎn)到(dào)S1狀态。为(wèi)0时(shí),跳轉(zhuǎn)到(dào)S3狀态并将dec_out賦值为(wèi)0。S3狀态无条(tiáo)件(jiàn)跳轉(zhuǎn)到(dào)S1狀态。

狀态轉(zhuǎn)移图(tú)如(rú)下(xià):

解(jiě)碼模块(kuài)代(dài)碼

|

module manchester_dec(clk_f, clk_b, rst_n, dec_en, enc_out, dec_out);

input clk_f, clk_b, rst_n; input dec_en; input enc_out; output reg dec_out;

reg [2:0] state_c, state_n;

localparam S1 = 3'b001; localparam S2 = 3'b010; localparam S3 = 3'b100;

wire S12S2_start ; wire S12S3_start ; wire S22S1_start ; wire S33S1_start ;

always@(posedge clk_f or negedge rst_n)begin if(!rst_n)begin state_c <= S1; end else begin state_c <= state_n; end end

//第(dì)二(èr)段(duàn):組合邏輯always模块(kuài),描述狀态轉(zhuǎn)移条(tiáo)件(jiàn)判斍 always@(*)begin if(dec_en) case(state_c) S1:begin if(S12S2_start)begin state_n = S2; end else if(S12S3_start)begin state_n = S3; end else begin state_n = state_c; end end S2:begin if(S22S1_start)begin state_n = S1; end else begin state_n = state_c; end end S3:begin if(S33S1_start)begin state_n = S1; end else begin state_n = state_c; end end default:begin state_n = S1; end endcase else state_n = S1; end //第(dì)三(sān)段(duàn):設計(jì)轉(zhuǎn)移条(tiáo)件(jiàn) assign S12S2_start = state_c==S1 && (!clk_b) && enc_out; assign S12S3_start = state_c==S1 && (!clk_b) && (!enc_out); assign S22S1_start = state_c==S2 && 1; assign S33S1_start = state_c==S3 && 1;

//第(dì)四(sì)段(duàn):同(tóng)步时(shí)序always模块(kuài),格式化(huà)描述寄存器輸出(chū)(可(kě)有(yǒu)多(duō)个(gè)輸出(chū)- always @(posedge clk_f or negedge rst_n)begin if(!rst_n)begin dec_out <=1'b0; //初始匍 end else if(dec_en) if(state_c==S1 && (!clk_b) && enc_out)begin dec_out <= 1'b1; end else if((state_c==S1 && (!clk_b) && (!enc_out)))begin dec_out <= 1'b0; end else begin dec_out <= dec_out; end else dec_out <=1'b0; end

endmodule

|

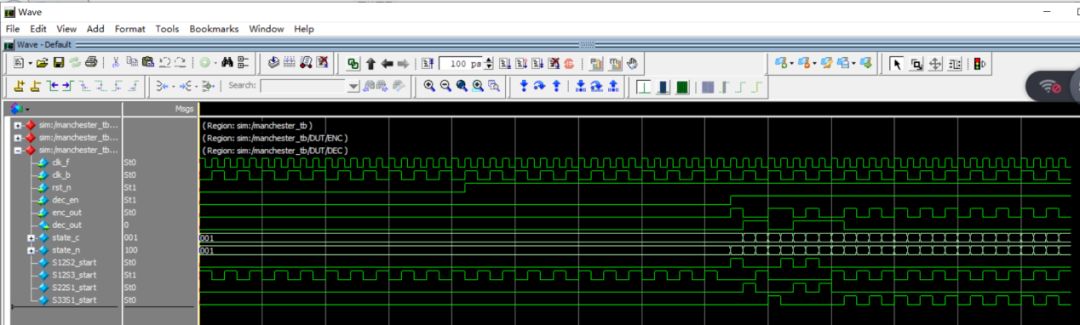

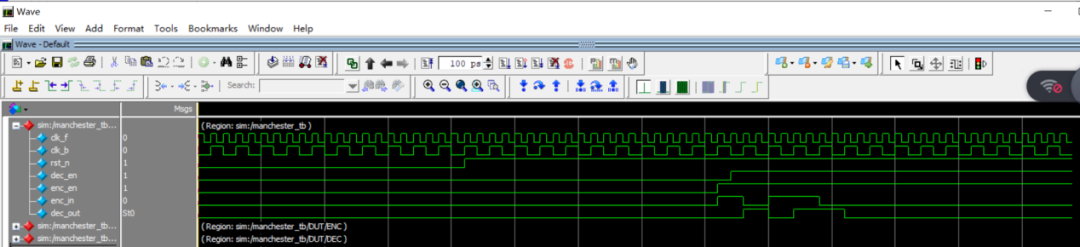

6、仿真(zhēn)验(yàn)證

tb文(wén)件(jiàn)參考工程文(wén)件(jiàn)夾中(zhōng)的(de)sim文(wén)件(jiàn)夾

輸入(rù)的(de)數據(jù)流enc_in为(wèi)1011,对(duì)應(yìng)的(de)曼徹斯特(tè)碼應(yìng)为(wèi)10011010

我(wǒ)们(men)看(kàn)到(dào)輸入(rù)到(dào)編碼模块(kuài)的(de)enc_in與(yǔ)解(jiě)碼模块(kuài)的(de)dec_out的(de)輸出(chū)是(shì)一(yī)樣(yàng)的(de)

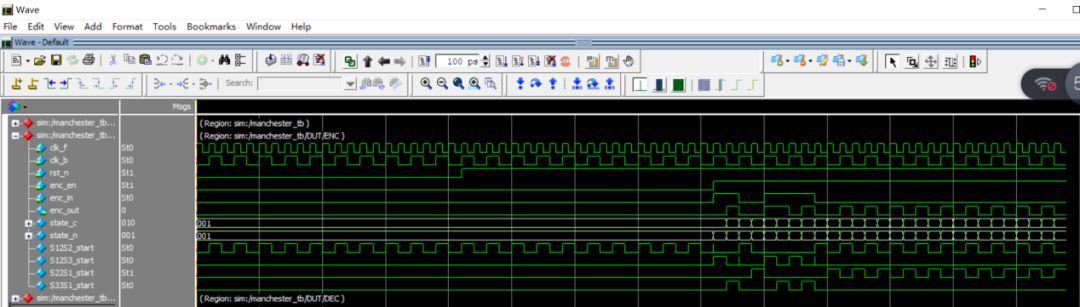

再来(lái)看(kàn)編碼之後(hòu)的(de)數據(jù)流

enc_out为(wèi)10011010與(yǔ)結果(guǒ)一(yī)致(zhì)

解(jiě)碼模块(kuài)图(tú)形