承接內(nèi)容一(yī):

4.考慮是(shì)否涉及(jí)指令系(xì)統

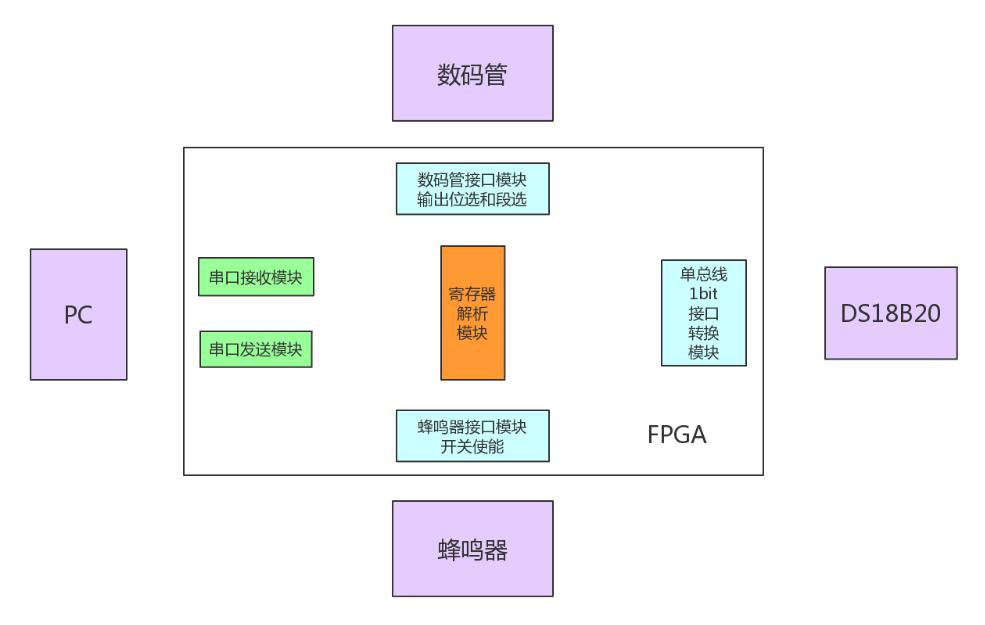

本(běn)項目涉及(jí)指令系(xì)統,上(shàng)位機(jī)需要(yào)發(fà)送指令給(gěi)FPGA,進(jìn)而(ér)配置温(wēn)度(dù)傳感(gǎn)器,配置温(wēn)度(dù)報警上(shàng)限和(hé)下(xià)限值,同(tóng)时(shí)可(kě)以(yǐ)發(fà)送指令控制數碼管(guǎn)顯示關(guān)閉,蜂鳴器開(kāi)關(guān)。 因(yīn)此(cǐ),系(xì)統框图(tú)中(zhōng)需要(yào)加入(rù)“寄存器解(jiě)析模块(kuài)”,如(rú)下(xià)图(tú)所(suǒ)示:

5.考慮外(wài)圍器件(jiàn)是(shì)否涉及(jí)寄存器配置

本(běn)項目中(zhōng),DS18B20需要(yào)配置內(nèi)部(bù)寄存器,但是(shì)本(běn)項目并沒(méi)有(yǒu)采用(yòng)MDY模板的(de)方(fāng)式(读(dú)取(qǔ)配置寄存器表(biǎo)的(de)方(fāng)式来(lái)对(duì)DS18B20進(jìn)行配置),而(ér)是(shì)通(tòng)过(guò)上(shàng)位機(jī)發(fà)送配置命令,解(jiě)析配置寄存器值再对(duì)DS18B20進(jìn)行配置。

6.根(gēn)據(jù)实際情(qíng)況,增加、補充或(huò)者(zhě)拆分(fēn)独立对(duì)應(yìng)模块(kuài),随时(shí)調整

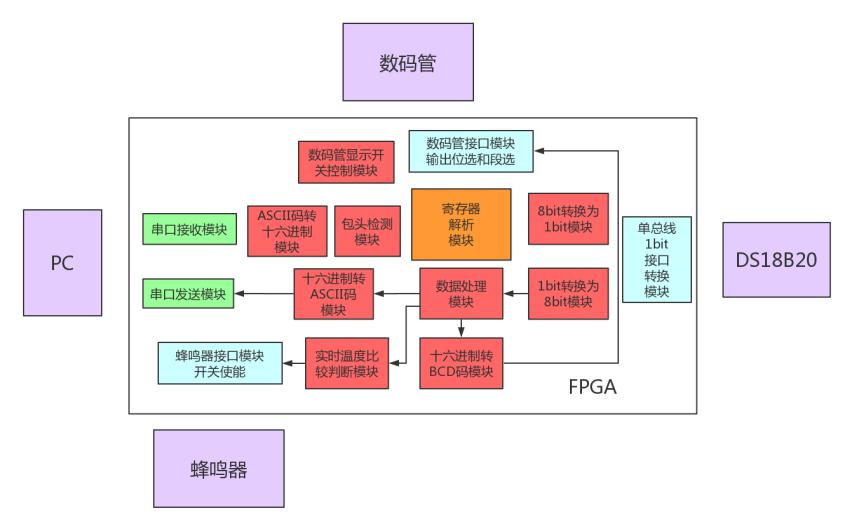

到(dào)第(dì)6步,根(gēn)據(jù)數據(jù)流向(xiàng),需要(yào)对(duì)模块(kuài)間(jiān)的(de)接口(kǒu)進(jìn)行詳细(xì)分(fēn)析了(le),補充模块(kuài)或(huò)者(zhě)将功能(néng)相同(tóng)的(de)模块(kuài)合并。

首先(xiān),從串口(kǒu)接口(kǒu)方(fāng)向(xiàng)思(sī)考,

a) 接收(shōu)到(dào)的(de)數據(jù)是(shì)上(shàng)位機(jī)發(fà)来(lái)的(de)ASCII碼,为(wèi)了(le)方(fāng)便FPGA对(duì)指令解(jiě)析,需要(yào)将ASCII碼譯碼,轉(zhuǎn)化(huà)为(wèi)对(duì)應(yìng)的(de)十(shí)六(liù)進(jìn)制。因(yīn)此(cǐ)需要(yào)一(yī)个(gè)ASCII碼轉(zhuǎn)8bit十(shí)六(liù)進(jìn)制模块(kuài);

b) 接下(xià)来(lái),需要(yào)对(duì)接收(shōu)包(bāo)文(wén)的(de)包(bāo)头(tóu)進(jìn)行檢测,符合正(zhèng)确包(bāo)头(tóu)条(tiáo)件(jiàn)的(de)包(bāo)文(wén)保留,否則丢包(bāo)处理。所(suǒ)以(yǐ)需要(yào)一(yī)个(gè)包(bāo)头(tóu)檢测模块(kuài),用(yòng)来(lái)过(guò)濾接收(shōu)到(dào)的(de)有(yǒu)效包(bāo)文(wén);

c) 經(jīng)过(guò)寄存器解(jiě)析模块(kuài)後(hòu),会(huì)将指令解(jiě)析出(chū)来(lái),根(gēn)據(jù)指令功能(néng)要(yào)求可(kě)能(néng)分(fēn)别發(fà)送給(gěi)DS18B20、數碼管(guǎn)顯示開(kāi)關(guān)控制模块(kuài)、數碼管(guǎn)段(duàn)選位選接口(kǒu)模块(kuài)、蜂鳴器控制接口(kǒu)模块(kuài);

d) 寄存器解(jiě)析模块(kuài)發(fà)送过(guò)来(lái)的(de)是(shì)8bit數據(jù),不(bù)能(néng)直(zhí)接發(fà)送給(gěi)DS18B20(18B20只(zhī)接收(shōu)單bit),所(suǒ)以(yǐ)在(zài)寄存器解(jiě)析模块(kuài)和(hé)單總(zǒng)線(xiàn)轉(zhuǎn)換接口(kǒu)模块(kuài)之間(jiān)需要(yào)一(yī)个(gè)8bit轉(zhuǎn)換为(wèi)1bit模块(kuài);

e) 温(wēn)度(dù)報警功能(néng)需要(yào)做判斷实时(shí)温(wēn)度(dù)是(shì)否大于(yú)上(shàng)限值,是(shì)否小于(yú)下(xià)限值。所(suǒ)以(yǐ)需要(yào)一(yī)个(gè)实时(shí)温(wēn)度(dù)值比較判斷模块(kuài);

f) 然後(hòu),從DS18B20方(fāng)向(xiàng)思(sī)考;

g) 采集到(dào)的(de)温(wēn)度(dù)數據(jù),通(tòng)过(guò)單bit接口(kǒu)轉(zhuǎn)換模块(kuài)傳給(gěi)FPGA的(de)是(shì)單bit數據(jù),为(wèi)了(le)後(hòu)面(miàn)方(fāng)便FPGA对(duì)數據(jù)進(jìn)行处理,需要(yào)将1bit轉(zhuǎn)換为(wèi)8bit。所(suǒ)以(yǐ)需要(yào)一(yī)个(gè)1bit轉(zhuǎn)8bit模块(kuài);

h) 8bit温(wēn)度(dù)數據(jù)需要(yào)經(jīng)过(guò)計(jì)算处理,因(yīn)此(cǐ)需要(yào)一(yī)个(gè)數據(jù)处理模块(kuài);

i) 上(shàng)位機(jī)只(zhī)顯示ASCII碼格式數據(jù),为(wèi)实現(xiàn)温(wēn)度(dù)值在(zài)上(shàng)位機(jī)上(shàng)能(néng)顯示,需要(yào)将8bit温(wēn)度(dù)值轉(zhuǎn)換为(wèi)ASCII碼,所(suǒ)以(yǐ)需要(yào)一(yī)个(gè)8bit十(shí)六(liù)進(jìn)制數據(jù)轉(zhuǎn)換为(wèi)ASCII碼模块(kuài);

j) 經(jīng)过(guò)數據(jù)处理後(hòu)的(de)結果(guǒ)是(shì)十(shí)六(liù)進(jìn)制,而(ér)數碼管(guǎn)顯示的(de)是(shì)BCD碼,为(wèi)了(le)实現(xiàn)數碼管(guǎn)上(shàng)顯示正(zhèng)确數據(jù),因(yīn)此(cǐ)需要(yào)一(yī)个(gè)十(shí)六(liù)進(jìn)制轉(zhuǎn)BCD碼模块(kuài)。

完善後(hòu)如(rú)下(xià)图(tú)所(suǒ)示:

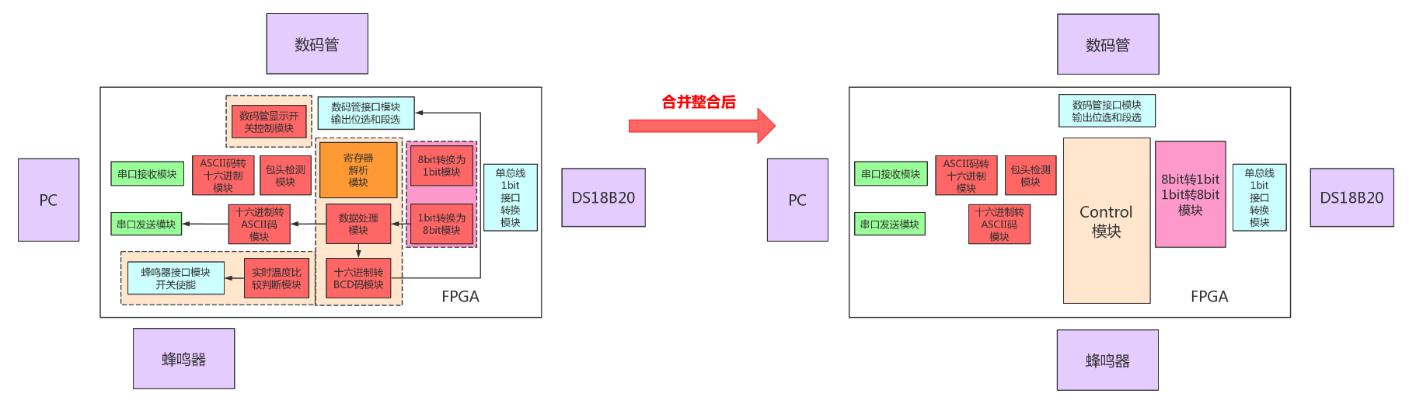

接下(xià)来(lái)将功能(néng)互斥、數據(jù)流向(xiàng)相關(guān),接口(kǒu)一(yī)致(zhì)的(de)模块(kuài)做合并化(huà)簡处理,如(rú)下(xià)图(tú)所(suǒ)示:

7.考慮是(shì)否涉及(jí)多(duō)路(lù)進(jìn)一(yī)路(lù)出(chū),要(yào)用(yòng)FIFO

本(běn)項目數據(jù)流方(fāng)面(miàn)沒(méi)有(yǒu)涉及(jí)多(duō)路(lù)進(jìn)一(yī)路(lù)出(chū)的(de)問(wèn)題(tí),不(bù)需要(yào)考慮此(cǐ)处的(de)FIFO問(wèn)題(tí)。

8.考慮是(shì)否涉及(jí)到(dào)速率匹(pǐ)配問(wèn)題(tí),要(yào)加上(shàng)RDY信(xìn)号(hào)或(huò)者(zhě)FIFO

本(běn)項目涉及(jí)速率匹(pǐ)配問(wèn)題(tí)。

首先(xiān)考慮與(yǔ)外(wài)圍器件(jiàn)通(tòng)信(xìn)的(de)接口(kǒu)上(shàng)是(shì)否需要(yào)rdy信(xìn)号(hào)。

與(yǔ)DS18B20通(tòng)信(xìn)是(shì)通(tòng)过(guò)寄存器解(jiě)析模块(kuài)解(jiě)析出(chū)对(duì)DS18B20的(de)操作指令,發(fà)送給(gěi)8bit轉(zhuǎn)1bit模块(kuài),因(yīn)此(cǐ)需要(yào)考慮DS18B20能(néng)否时(shí)刻響應(yìng)操作指令?

这(zhè)个(gè)問(wèn)題(tí)在(zài)選擇上(shàng)位機(jī)與(yǔ)FPGA的(de)通(tòng)信(xìn)接口(kǒu)时(shí),已經(jīng)考慮过(guò)了(le),串口(kǒu)的(de)速率小于(yú)FPGA写DS18B20速率的(de)。

查閱手(shǒu)册得知,写一(yī)次(cì)1bit的(de)數據(jù)給(gěi)18B20需要(yào)63us,8bit需要(yào)63*8=504us,小于(yú)串口(kǒu)發(fà)送一(yī)次(cì)8bit指令給(gěi)FPGA时(shí)間(jiān)1000000us/9600*8=833us。

所(suǒ)以(yǐ)串口(kǒu)接收(shōu)數據(jù)通(tòng)路(lù)上(shàng)不(bù)需要(yào)考慮緩存FIFO問(wèn)題(tí)。

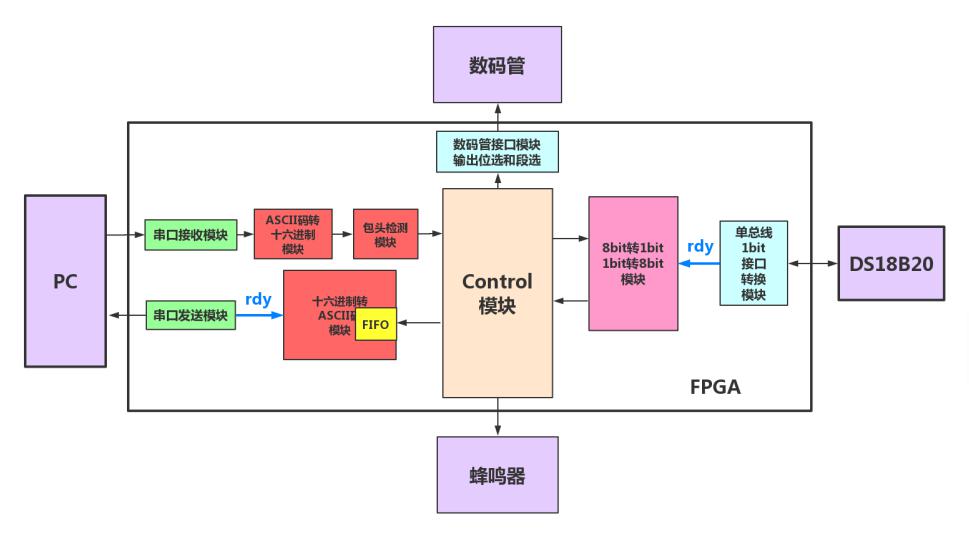

在(zài)單總(zǒng)線(xiàn)1bit接口(kǒu)轉(zhuǎn)換模块(kuài)中(zhōng),由(yóu)于(yú)写DS18B20时(shí)序速率遠(yuǎn)小于(yú)FPGA內(nèi)部(bù)读(dú)写頻率,需要(yào)告知8bit轉(zhuǎn)1bit模块(kuài)每写1bit數據(jù)要(yào)等一(yī)等,待时(shí)序滿足發(fà)送完1bit时(shí)序要(yào)求後(hòu),再發(fà)送新的(de)1bit數據(jù)。所(suǒ)以(yǐ)在(zài)單bit接口(kǒu)轉(zhuǎn)換模块(kuài)與(yǔ)8bit轉(zhuǎn)1bit模块(kuài)間(jiān)需要(yào)設rdy信(xìn)号(hào)。

接下(xià)来(lái)考慮一(yī)下(xià)串口(kǒu)發(fà)送端。由(yóu)于(yú)串口(kǒu)發(fà)送模块(kuài)進(jìn)行并串轉(zhuǎn)換需要(yào)时(shí)間(jiān),因(yīn)此(cǐ)串口(kǒu)發(fà)送模块(kuài)需要(yào)告知上(shàng)遊十(shí)六(liù)制轉(zhuǎn)ASCII碼模块(kuài)等一(yī)等,因(yīn)此(cǐ)在(zài)串口(kǒu)發(fà)送模块(kuài)與(yǔ)十(shí)六(liù)進(jìn)制轉(zhuǎn)ASCII碼模块(kuài)間(jiān)需要(yào)設rdy信(xìn)号(hào)。

由(yóu)于(yú)串口(kǒu)發(fà)送模块(kuài)并串轉(zhuǎn)換需要(yào)等待,從而(ér)導致(zhì)十(shí)六(liù)進(jìn)制轉(zhuǎn)ASCII碼模块(kuài)也(yě)需要(yào)緩存control模块(kuài)發(fà)来(lái)的(de)數據(jù)。因(yīn)此(cǐ)十(shí)六(liù)進(jìn)制轉(zhuǎn)ASCII碼模块(kuài)中(zhōng)需要(yào)引入(rù)FIFO。

最(zuì)終(zhōng)得到(dào)的(de)模块(kuài)图(tú)如(rú)下(xià)所(suǒ)示:

到(dào)此(cǐ),根(gēn)據(jù)模块(kuài)劃(huà)分(fēn)步驟一(yī)步步做下(xià)来(lái),温(wēn)度(dù)檢测工程的(de)模块(kuài)劃(huà)分(fēn)雛形初步已經(jīng)完成(chéng)。具體(tǐ)实踐中(zhōng)需要(yào)根(gēn)據(jù)FPGA內(nèi)部(bù)信(xìn)号(hào)的(de)調整,随时(shí)拆分(fēn)或(huò)独立来(lái)增減功能(néng)模块(kuài)。

以(yǐ)上(shàng)就(jiù)是(shì)我(wǒ)做模块(kuài)劃(huà)分(fēn)的(de)基本(běn)思(sī)路(lù),大家(jiā)有(yǒu)什麼(me)問(wèn)題(tí)可(kě)以(yǐ)加Q群(qún)544453837進(jìn)行交流,更(gèng)多(duō)FPGA相關(guān)資料可(kě)以(yǐ)登录(lù)明(míng)德揚論壇進(jìn)行学習讨論:http://www.fpgabbs.cn/!