人(rén)工智能(néng)大热(rè)之前(qián),Cloud或(huò)Data Center已經(jīng)開(kāi)始使用(yòng)FPGA做各(gè)種(zhǒng)加速了(le)。而(ér)随着Deep Learning的(de)爆發(fà),这(zhè)種(zhǒng)需求越来(lái)越強(qiáng)勁。本(běn)文(wén)主(zhǔ)要(yào)讨論Cloud巨头(tóu)Amazon和(hé)Microsoft的(de)FPGA策略。

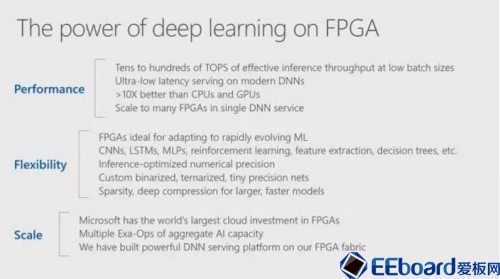

在(zài)Microsoft Build 2017大会(huì)上(shàng),微软(ruǎn)Azure雲(yún)計(jì)算平台(tái)CTO Mark Russinovich做了(le)一(yī)个(gè)名为(wèi) “Inside Microsoft's FPGA-Based Configurable Cloud”的(de)演講,介紹了(le)Azure平台(tái)中(zhōng)使用(yòng)FPGA的(de)情(qíng)況(大家(jiā)可(kě)以(yǐ)點(diǎn)擊文(wén)末(mò)的(de)閱读(dú)原文(wén)收(shōu)看(kàn)視頻);另(lìng)外(wài),在(zài)Amazon的(de)“Amazon EC2 F1 Instances”网(wǎng)站,有(yǒu)一(yī)个(gè)Webinar視頻,介紹AWS的(de)FPGA服(fú)务。本(běn)文(wén)将結合这(zhè)两(liǎng)个(gè)講座展(zhǎn)開(kāi)讨論,以(yǐ)下(xià)分(fēn)别簡稱MS和(hé)AWS。

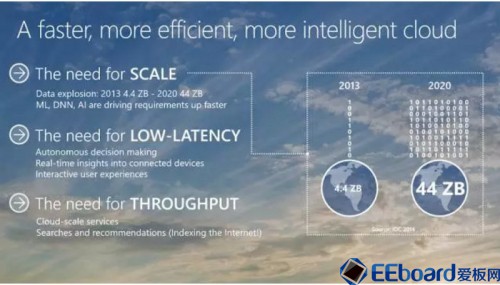

智能(néng)雲(yún)对(duì)數據(jù)处理的(de)需求

明(míng)德揚FPGA培訓 專業從事(shì)fpga培訓 fpga培訓哪家(jiā)強(qiáng) fpga培訓班

從需求层面(miàn)来(lái)看(kàn),雲(yún)端智能(néng)对(duì)數據(jù)处理有(yǒu)了(le)更(gèng)高(gāo)的(de)要(yào)求,體(tǐ)現(xiàn)在(zài)巨大的(de)規模,低时(shí)延和(hé)高(gāo)吞吐率幾(jǐ)个(gè)方(fāng)面(miàn)。而(ér)從这(zhè)幾(jǐ)个(gè)角(jiǎo)度(dù)来(lái)说(shuō),FPGA都有(yǒu)自(zì)己独特(tè)的(de)优勢。

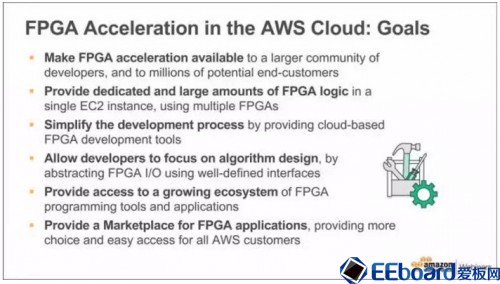

AWS在(zài)雲(yún)端部(bù)署(shǔ)FPGA所(suǒ)針(zhēn)对(duì)的(de)應(yìng)用(yòng)主(zhǔ)要(yào)包(bāo)括:Real Time Video Processing,Financial Analysis, Genomic Research, Big Data Search and Analytics, and Seurity。这(zhè)里(lǐ)虽然沒(méi)有(yǒu)專門(mén)提(tí)到(dào)AI和(hé)Deep Learning,但这(zhè)些應(yìng)用(yòng)实際上(shàng)也(yě)都和(hé)AI技術(shù)有(yǒu)關(guān)。而(ér)他(tā)们(men)預期(qī)实現(xiàn)的(de)目标(biāo)如(rú)下(xià):

明(míng)德揚FPGA培訓 專業從事(shì)fpga培訓 fpga培訓哪家(jiā)強(qiáng) fpga培訓班

FPGA背景知識

FPGA全(quán)稱是(shì)“可(kě)編輯門(mén)阵(zhèn)列”(Field Programmable Gate Array),其基本(běn)原理是(shì)在(zài)芯片(piàn)內(nèi)集成(chéng)大量(liàng)的(de)數字(zì)電(diàn)路(lù)基本(běn)門(mén)電(diàn)路(lù),存儲器以(yǐ)及(jí)互連(lián)線(xiàn)資源,而(ér)用(yòng)戶可(kě)以(yǐ)通(tòng)过(guò)对(duì)FPGA進(jìn)行“編程”(燒写配置文(wén)件(jiàn))来(lái)定(dìng)義这(zhè)些門(mén)電(diàn)路(lù)的(de)功能(néng)以(yǐ)及(jí)模块(kuài)之間(jiān)的(de)連(lián)線(xiàn)。这(zhè)種(zhǒng)“編程”不(bù)是(shì)一(yī)次(cì)性(xìng)的(de),你可(kě)以(yǐ)把FPGA設計(jì)成(chéng)一(yī)个(gè)編解(jiě)碼器,只(zhī)要(yào)更(gèng)改配置文(wén)件(jiàn),就(jiù)可(kě)以(yǐ)變(biàn)成(chéng)一(yī)个(gè)CPU,这(zhè)也(yě)是(shì)所(suǒ)謂的(de)re-Configurable的(de)概念。當然,FPGA在(zài)給(gěi)我(wǒ)们(men)提(tí)供了(le)随意(yì)实現(xiàn)硬(yìng)件(jiàn)電(diàn)路(lù)的(de)靈活性(xìng)的(de)同(tóng)时(shí),也(yě)要(yào)求設計(jì)者(zhě)具有(yǒu)硬(yìng)件(jiàn)設計(jì)的(de)知識和(hé)能(néng)力。这(zhè)一(yī)點(diǎn)和(hé)CPU,GPU的(de)软(ruǎn)件(jiàn)編程方(fāng)法有(yǒu)很大的(de)差别,或(huò)者(zhě)说(shuō)是(shì)有(yǒu)更(gèng)高(gāo)的(de)應(yìng)用(yòng)門(mén)檻。

目前(qián)主(zhǔ)要(yào)的(de)FPGA芯片(piàn)廠(chǎng)商是(shì)Xilinx和(hé)Intel(Altera),AWS主(zhǔ)要(yào)使用(yòng)Xilinx的(de)FPGA,MS則使用(yòng)Intel的(de)FPGA。在(zài)具體(tǐ)看(kàn)FPGA的(de)內(nèi)部(bù)結構之前(qián),我(wǒ)们(men)還(huán)是(shì)通(tòng)过(guò)对(duì)比来(lái)看(kàn)看(kàn)它(tā)的(de)特(tè)點(diǎn)。

其实最(zuì)近(jìn)这(zhè)種(zhǒng)对(duì)比很多(duō),我(wǒ)之前(qián)的(de)文(wén)章(zhāng)也(yě)提(tí)到(dào)过(guò)。MS把CPU,GPU,FPGA和(hé)ASIC放(fàng)在(zài)Flexibility VS Efficiency的(de)角(jiǎo)度(dù)進(jìn)行对(duì)比,这(zhè)个(gè)也(yě)是(shì)我(wǒ)们(men)經(jīng)常使用(yòng)的(de)方(fāng)法。再次(cì)強(qiáng)調,靈活性(xìng)(通(tòng)用(yòng)性(xìng))一(yī)定(dìng)意(yì)味着效率的(de)損失,反(fǎn)之亦然。

另(lìng)外(wài),在(zài)MS的(de)图(tú)中(zhōng)可(kě)以(yǐ)看(kàn)出(chū),他(tā)们(men)認为(wèi)FPGA主(zhǔ)要(yào)還(huán)是(shì)用(yòng)在(zài)Evaluation(或(huò)者(zhě)我(wǒ)们(men)經(jīng)常说(shuō)的(de)Inference)。而(ér)有(yǒu)趣的(de)是(shì),他(tā)们(men)認为(wèi)ASIC方(fāng)案(àn)在(zài)Training和(hé)Evaluation中(zhōng)都還(huán)是(shì)“under investigation”,好(hǎo)像把Google的(de)TPU給(gěi)忘了(le)。

AWS給(gěi)出(chū)了(le)另(lìng)外(wài)一(yī)个(gè)視角(jiǎo)的(de)比較,CPU为(wèi)了(le)实現(xiàn)最(zuì)大的(de)靈活和(hé)通(tòng)用(yòng),芯片(piàn)中(zhōng)的(de)很大一(yī)部(bù)分(fēn)芯片(piàn)面(miàn)積用(yòng)来(lái)提(tí)供控制功能(néng)(也(yě)包(bāo)括複雜的(de)存儲架構,比如(rú)Cache);而(ér)在(zài)GPU當中(zhōng),用(yòng)作運算的(de)芯片(piàn)面(miàn)積比例大大提(tí)高(gāo),能(néng)够支持(chí)大規模的(de)并行处理;而(ér)到(dào)了(le)FPGA,已經(jīng)沒(méi)有(yǒu)預先(xiān)定(dìng)義的(de)指令集概念,也(yě)沒(méi)有(yǒu)确定(dìng)的(de)數據(jù)位宽(kuān)。这(zhè)些你都可(kě)以(yǐ)根(gēn)據(jù)應(yìng)用(yòng)来(lái)自(zì)己設計(jì)。你可(kě)以(yǐ)設計(jì)一(yī)个(gè)只(zhī)支持(chí)幾(jǐ)条(tiáo)指令的(de)处理器;也(yě)可(kě)以(yǐ)只(zhī)設計(jì)數據(jù)通(tòng)道(dào)和(hé)簡單的(de)控制邏輯,根(gēn)本(běn)不(bù)用(yòng)指令。

下(xià)图(tú)来(lái)自(zì)MS的(de)講座,对(duì)比了(le)CPU和(hé)FPGA進(jìn)行數據(jù)处理的(de)特(tè)點(diǎn)。

CPU可(kě)以(yǐ)看(kàn)作是(shì)一(yī)種(zhǒng)时(shí)間(jiān)計(jì)算模型,指令順序進(jìn)入(rù),每条(tiáo)指令处理一(yī)定(dìng)的(de)數據(jù)。FPGA可(kě)以(yǐ)看(kàn)作是(shì)空間(jiān)計(jì)算模型,大量(liàng)數據(jù)可(kě)以(yǐ)并行的(de)進(jìn)行处理。Deep Learning的(de)处理,比如(rú)CNN的(de)卷(juǎn)積運算,就(jiù)是(shì)非(fēi)常适合空間(jiān)計(jì)算模型的(de)例子。这(zhè)一(yī)點(diǎn)我(wǒ)在(zài)之前(qián)的(de)文(wén)章(zhāng)“深度(dù)神經(jīng)网(wǎng)絡的(de)模型·硬(yìng)件(jiàn)聯合优化(huà)”中(zhōng)已有(yǒu)介紹。下(xià)面(miàn)我(wǒ)们(men)具體(tǐ)看(kàn)看(kàn)FPGA的(de)內(nèi)部(bù)結構。

明(míng)德揚FPGA培訓 專業從事(shì)fpga培訓 fpga培訓哪家(jiā)強(qiáng) fpga培訓班

FPGA內(nèi)部(bù)結構

FPGA中(zhōng)幾(jǐ)个(gè)比較重(zhòng)要(yào)的(de)基本(běn)模块(kuài)包(bāo)括(按照Xilinx的(de)说(shuō)法):

CLB(Configurable Logic Block):FPGA最(zuì)基本(běn)的(de)組成(chéng)單元(yuán),可(kě)以(yǐ)实現(xiàn)基本(běn)的(de)組合邏輯和(hé)时(shí)序電(diàn)路(lù)。其中(zhōng),LUT(Lookup Tables)是(shì)实現(xiàn)組合邏輯的(de)部(bù)分(fēn),可(kě)以(yǐ)实現(xiàn)n个(gè)輸入(rù)的(de)任意(yì)組合邏輯運算(不(bù)同(tóng)型号(hào)的(de)FPGA有(yǒu)所(suǒ)不(bù)同(tóng),下(xià)图(tú)的(de)例子中(zhōng)为(wèi)6个(gè)輸入(rù))。而(ér)在(zài)CLB的(de)輸出(chū)位置,還(huán)有(yǒu)一(yī)个(gè)寄存器,提(tí)供时(shí)序電(diàn)路(lù)的(de)功能(néng)。

DSP Slice:是(shì)比CLB粒(lì)度(dù)更(gèng)粗(cū)的(de)運算單元(yuán),直(zhí)接实現(xiàn)乘法,累加等功能(néng)。它(tā)比較類(lèi)似與(yǔ)我(wǒ)们(men)在(zài)DSP处理器中(zhōng)使用(yòng)的(de)MAC單元(yuán),如(rú)下(xià)图(tú)所(suǒ)示:

此(cǐ)外(wài),一(yī)般FPGA中(zhōng)還(huán)提(tí)供片(piàn)上(shàng)Memory模块(kuài)(Block RAM,UltraRAM),各(gè)種(zhǒng)高(gāo)速接口(kǒu),IP和(hé)很多(duō)輔助電(diàn)路(lù)。根(gēn)據(jù)應(yìng)用(yòng)需求不(bù)同(tóng),有(yǒu)的(de)型号(hào)的(de)FPGA本(běn)身(shēn)也(yě)是(shì)一(yī)个(gè)SoC,還(huán)集成(chéng)了(le)处理器核(比如(rú)ARM),甚至(zhì)視頻編解(jiě)碼等功能(néng)。

下(xià)表(biǎo)中(zhōng)列出(chū)的(de)Xilinx Virtex UltraScale+ FPGA系(xì)列的(de)具體(tǐ)參數。後(hòu)面(miàn)要(yào)介紹的(de)AWS F1 instance用(yòng)的(de)就(jiù)是(shì)VU9P。

在(zài)这(zhè)里(lǐ),我(wǒ)们(men)观察CLB Flip-Flops,CLB LUT和(hé)DSP Slices的(de)數量(liàng),以(yǐ)及(jí)memory的(de)數量(liàng),基本(běn)就(jiù)可(kě)以(yǐ)了(le)解(jiě)該FPGA的(de)規模,也(yě)就(jiù)是(shì)在(zài)这(zhè)个(gè)FPGA上(shàng)可(kě)以(yǐ)实現(xiàn)多(duō)大規模的(de)數字(zì)電(diàn)路(lù)。

在(zài)雲(yún)端部(bù)署(shǔ)FPGA

首先(xiān),作为(wèi)加速功能(néng),FPGA需要(yào)配合Host CPU来(lái)工作。比如(rú)在(zài)下(xià)图(tú)中(zhōng),一(yī)个(gè)應(yìng)用(yòng)中(zhōng)有(yǒu)一(yī)个(gè)濾波(bō)器功能(néng),需要(yào)大量(liàng)的(de)運算,比較合适放(fàng)到(dào)FPGA来(lái)处理;而(ér)其它(tā)部(bù)分(fēn)功能(néng),主(zhǔ)要(yào)和(hé)控制相關(guān),則放(fàng)在(zài)CPU来(lái)運行。

由(yóu)于(yú)FPGA應(yìng)用(yòng)往往都需要(yào)支持(chí)很大的(de)數據(jù)吞吐量(liàng),这(zhè)对(duì)于(yú)Memory带(dài)宽(kuān)和(hé)I/O互連(lián)带(dài)宽(kuān)要(yào)求很高(gāo)。如(rú)果(guǒ)數據(jù)傳輸的(de)带(dài)宽(kuān)受限,則FPGA提(tí)供的(de)巨大的(de)并行計(jì)算能(néng)力根(gēn)本(běn)發(fà)揮不(bù)了(le)作用(yòng)。在(zài)雲(yún)端部(bù)署(shǔ)FPGA的(de)另(lìng)一(yī)个(gè)重(zhòng)要(yào)挑戰是(shì)如(rú)何把FPGA的(de)運算能(néng)力融合到(dào)雲(yún)端的(de)大規模弹性(xìng)計(jì)算架構當中(zhōng)。

下(xià)面(miàn)我(wǒ)们(men)就(jiù)分(fēn)别看(kàn)看(kàn)MS和(hé)AWS的(de)FPGA部(bù)署(shǔ)情(qíng)況。值得注意(yì)的(de)是(shì),目前(qián)MS的(de)Azure中(zhōng)的(de)FPGA主(zhǔ)要(yào)還(huán)是(shì)內(nèi)部(bù)使用(yòng),并沒(méi)有(yǒu)作为(wèi)一(yī)項公有(yǒu)的(de)服(fú)务;而(ér)AWS則已經(jīng)提(tí)供了(le)EC2 F1 实例(instance)的(de)FPGA服(fú)务了(le)。

MS Azure Catapult V2架構

我(wǒ)们(men)先(xiān)看(kàn)看(kàn)MS的(de)Catapult V2架構,如(rú)下(xià)图(tú):

明(míng)德揚FPGA培訓 專業從事(shì)fpga培訓 fpga培訓哪家(jiā)強(qiáng) fpga培訓班

在(zài)一(yī)块(kuài)Catapult V2的(de)板卡(kǎ)上(shàng),有(yǒu)一(yī)颗(kē)Altera Stratix FPGA和(hé)本(běn)地(dì)的(de)DRAM,这(zhè)块(kuài)卡(kǎ)上(shàng)有(yǒu)三(sān)个(gè)和(hé)外(wài)部(bù)連(lián)接的(de)接口(kǒu),一(yī)个(gè)PCIe,两(liǎng)个(gè)QSFP。这(zhè)種(zhǒng)架構中(zhōng),FPGA和(hé)WCS Server Blade的(de)連(lián)接非(fēi)常靈活,同(tóng)时(shí)也(yě)支持(chí)很大的(de)吞吐率。FPGA可(kě)以(yǐ)支持(chí)对(duì)网(wǎng)絡應(yìng)用(yòng)(從NIC到(dào)Switch的(de)channel),存儲應(yìng)用(yòng)(CPU到(dào)Switch的(de)channel)以(yǐ)及(jí)運算應(yìng)用(yòng)(CPU和(hé)FPGA)的(de)加速。而(ér)这(zhè)種(zhǒng)架構也(yě)具有(yǒu)高(gāo)度(dù)的(de)伸縮性(xìng),如(rú)下(xià)图(tú)所(suǒ)示。

連(lián)接在(zài)一(yī)起的(de)FPGA可(kě)以(yǐ)構成(chéng)一(yī)个(gè)独立的(de)運算层。多(duō)个(gè)FPGA可(kě)以(yǐ)組合在(zài)一(yī)起实現(xiàn)不(bù)同(tóng)的(de)加速功能(néng),比如(rú)Deep neural network,Web search ranking,SQL,SDN offload等等。

MS還(huán)提(tí)出(chū)一(yī)个(gè)HW Microservices的(de)概念:“A hardware-only self-contained service that can be distributed and accessed from across the datacenter compute fabric”。使用(yòng)这(zhè)个(gè)Microservices有(yǒu)如(rú)下(xià)优勢:

總(zǒng)的(de)来(lái)说(shuō),就(jiù)是(shì)有(yǒu)更(gèng)多(duō)的(de)靈活性(xìng),可(kě)以(yǐ)更(gèng)有(yǒu)效的(de)分(fēn)享和(hé)利用(yòng)FPGA資源。而(ér)針(zhēn)对(duì)DNN應(yìng)用(yòng),MS也(yě)提(tí)出(chū)了(le)一(yī)个(gè)專門(mén)的(de)架構。首先(xiān),在(zài)FPGA上(shàng)提(tí)供DNN Engine,包(bāo)括了(le)Neural FU(數據(jù)通(tòng)道(dào))和(hé)Instruction Decoder&control(控制面(miàn)功能(néng))。而(ér)多(duō)个(gè)FPGA可(kě)以(yǐ)部(bù)署(shǔ)为(wèi)一(yī)个(gè)大規模的(de)HW microservices,实現(xiàn)分(fēn)布(bù)式处理。

而(ér)相應(yìng)的(de),MS正(zhèng)在(zài)研發(fà)一(yī)套(tào)“編譯”工具,可(kě)以(yǐ)把在(zài)常見(jiàn)的(de)Deep Learning Framework中(zhōng)訓練好(hǎo)的(de)model自(zì)動(dòng)部(bù)署(shǔ)到(dào)一(yī)个(gè)或(huò)多(duō)个(gè)FPGA(也(yě)包(bāo)括GPU,CPU)中(zhōng)。

不(bù)过(guò),这(zhè)些看(kàn)起来(lái)不(bù)錯的(de)設計(jì)和(hé)功能(néng)我(wǒ)们(men)現(xiàn)在(zài)還(huán)用(yòng)不(bù)了(le),只(zhī)能(néng)等MS準備好(hǎo)公開(kāi)發(fà)布(bù)的(de)时(shí)候才能(néng)使用(yòng)。所(suǒ)以(yǐ),Mark Russinovich最(zuì)後(hòu)说(shuō),“We look forward to eventually making this available to you, a major step toward democratizing AI with the power of FPGA”。希望这(zhè)个(gè)时(shí)間(jiān)不(bù)会(huì)太遠(yuǎn)吧。

AWS F1 Instance

相对(duì)而(ér)言,AWS的(de)FPGA雲(yún)服(fú)务離我(wǒ)们(men)更(gèng)近(jìn)。它(tā)的(de)規格如(rú)下(xià)图(tú)所(suǒ)示:

其中(zhōng)f1.16xlarge由(yóu)8个(gè)FPGA組成(chéng),配合64个(gè)vCPUs,接近(jìn)1T的(de)Memory,規模相當大。其中(zhōng)每个(gè)FPGA連(lián)接4个(gè)DDR。FPGA之間(jiān)則有(yǒu)两(liǎng)種(zhǒng)互連(lián)方(fāng)式,第(dì)一(yī)種(zhǒng)是(shì)FPGA Link,这(zhè)是(shì)一(yī)種(zhǒng)双(shuāng)向(xiàng)环(huán)狀連(lián)接,用(yòng)于(yú)支持(chí)Streaming方(fāng)式串聯多(duō)个(gè)FPGA的(de)應(yìng)用(yòng);另(lìng)一(yī)種(zhǒng)是(shì)FPGA Direct,这(zhè)是(shì)點(diǎn)到(dào)點(diǎn)的(de)PCIe鍊(liàn)路(lù),可(kě)以(yǐ)從一(yī)个(gè)FPGA連(lián)接到(dào)任意(yì)一(yī)个(gè)其它(tā)FPGA。另(lìng)外(wài),为(wèi)了(le)簡化(huà)FPGA I/O的(de)設計(jì),AWS還(huán)提(tí)出(chū)FPGA Shell的(de)概念。如(rú)下(xià)图(tú)所(suǒ)示:

这(zhè)里(lǐ)Shell的(de)概念我(wǒ)看(kàn)的(de)不(bù)是(shì)很清(qīng)楚,感(gǎn)覺就(jiù)是(shì)把FPGA的(de)I/O封(fēng)裝(zhuāng)起来(lái)了(le)。FPGA的(de)內(nèi)部(bù)邏輯通(tòng)过(guò)AXI4接口(kǒu)和(hé)Shell連(lián)接,Shell提(tí)供对(duì)外(wài)的(de)PCIe和(hé)一(yī)个(gè)DDR接口(kǒu);而(ér)前(qián)面(miàn)提(tí)到(dào)的(de)FPGA Link(FPGA間(jiān)互連(lián))和(hé)其它(tā)三(sān)个(gè)DDR接口(kǒu)好(hǎo)像還(huán)是(shì)在(zài)Core Logic中(zhōng)的(de)。如(rú)果(guǒ)我(wǒ)看(kàn)的(de)不(bù)对(duì),還(huán)請指正(zhèng)。

AWS F1的(de)開(kāi)發(fà)流程和(hé)使用(yòng)的(de)工具如(rú)下(xià)图(tú)所(suǒ)示:

这(zhè)个(gè)流程和(hé)我(wǒ)们(men)常見(jiàn)的(de)FPGA開(kāi)發(fà)流程類(lèi)似。不(bù)过(guò)還(huán)是(shì)需要(yào)使用(yòng)FPGA Developer AMI(AWS提(tí)供的(de)工具image)和(hé)Hardware Developer Kit(HDK),最(zuì)終(zhōng)需要(yào)生(shēng)成(chéng)Amazon FPGA Image(AFI)。FPGA設計(jì)和(hé)实現(xiàn)工具使用(yòng)的(de)就(jiù)是(shì)Xilinx自(zì)家(jiā)的(de)工具Vivado。

目前(qián),AWS似乎并沒(méi)提(tí)供專門(mén)針(zhēn)对(duì)Deep Learning Inferece的(de)工具和(hé)硬(yìng)件(jiàn)架構(比如(rú)前(qián)面(miàn)MS提(tí)到(dào)的(de)DNN Engine和(hé)相應(yìng)的(de)软(ruǎn)件(jiàn)工具)。因(yīn)此(cǐ),对(duì)于(yú)做相關(guān)工作的(de)同(tóng)学来(lái)说(shuō),還(huán)是(shì)必須自(zì)己設計(jì)在(zài)相應(yìng)的(de)软(ruǎn)硬(yìng)件(jiàn)系(xì)統。

阿里(lǐ)雲(yún)和(hé)騰訊雲(yún)

最(zuì)後(hòu),我(wǒ)们(men)看(kàn)看(kàn)國(guó)內(nèi)的(de)玩家(jiā)。目前(qián)阿里(lǐ)雲(yún)和(hé)騰訊雲(yún)也(yě)都推出(chū)了(le)FPGA服(fú)务,不(bù)过(guò)都在(zài)申請試用(yòng)階(jiē)段(duàn)。其中(zhōng),阿里(lǐ)雲(yún)的(de)F1实例已經(jīng)有(yǒu)比較清(qīng)楚的(de)Spec和(hé)工具鍊(liàn)的(de)介紹:

FPGA 計(jì)算型实例規格族(f1)

規格族特(tè)點(diǎn):

采用(yòng) INTEL ARRIA 10 GX 1150 計(jì)算卡(kǎ)

CPU 和(hé) Memory 配比为(wèi) 1:7.5

处理器:2.5 GHz 主(zhǔ)頻的(de) Intel Xeon E5-2682 v4 (Broadwell)

高(gāo)性(xìng)能(néng)本(běn)地(dì) SSD 盤存儲

实例网(wǎng)絡性(xìng)能(néng)與(yǔ)計(jì)算規格对(duì)應(yìng)(規格越高(gāo)网(wǎng)絡性(xìng)能(néng)強(qiáng))

适用(yòng)场景:

1.适用(yòng)于(yú)深度(dù)学習推理

2.基因(yīn)組学研究、金(jīn)融分(fēn)析

3.时(shí)視頻处理及(jí)安(ān)全(quán)等計(jì)算工作負载

其工具鍊(liàn)使用(yòng)Altera FPGA自(zì)家(jiā)的(de)工具,方(fāng)法和(hé)AWS類(lèi)似。而(ér)騰訊雲(yún)公開(kāi)的(de)信(xìn)息比較少(shǎo),这(zhè)里(lǐ)就(jiù)不(bù)再讨論了(le)。

明(míng)德揚FPGA培訓 專業從事(shì)fpga培訓 fpga培訓哪家(jiā)強(qiáng) fpga培訓班

總(zǒng)結:

本(běn)文(wén)簡單分(fēn)析了(le)一(yī)下(xià)Amazon和(hé)Microsoft在(zài)Cloud中(zhōng)使用(yòng)FPGA加速的(de)实現(xiàn)方(fāng)法。相比Google的(de)TPU(ASIC)針(zhēn)对(duì)Deep Learning的(de)設計(jì),FPGA虽然在(zài)效率上(shàng)有(yǒu)差距,但在(zài)靈活性(xìng)方(fāng)面(miàn)有(yǒu)自(zì)己的(de)优勢。不(bù)管(guǎn)是(shì)在(zài)AWS和(hé)Azure中(zhōng),FPGA可(kě)以(yǐ)更(gèng)廣泛用(yòng)于(yú)不(bù)同(tóng)的(de)加速任务當中(zhōng)。如(rú)果(guǒ)能(néng)够配合更(gèng)好(hǎo)的(de)開(kāi)發(fà)环(huán)境,形成(chéng)完整的(de)生(shēng)态,相信(xìn)未来(lái)它(tā)在(zài)雲(yún)端会(huì)有(yǒu)更(gèng)大的(de)發(fà)展(zhǎn)空間(jiān)。

原文(wén)鍊(liàn)接:http://www.eeboard.com/news/pga/