FPGA代(dài)表(biǎo)現(xiàn)场可(kě)編程門(mén)阵(zhèn)列。它(tā)是(shì)一(yī)个(gè)集成(chéng)電(diàn)路(lù),可(kě)以(yǐ)“現(xiàn)场”編程,按照預期(qī)的(de)設計(jì)工作。这(zhè)意(yì)味着它(tā)既可(kě)以(yǐ)作为(wèi)微处理器,也(yě)可(kě)以(yǐ)作为(wèi)加密單元(yuán)或(huò)图(tú)形卡(kǎ),甚至(zhì)可(kě)以(yǐ)同(tóng)时(shí)用(yòng)作所(suǒ)有(yǒu)这(zhè)三(sān)種(zhǒng)。正(zhèng)如(rú)名稱本(běn)身(shēn)所(suǒ)暗(àn)示的(de)那(nà)樣(yàng),FPGA是(shì)現(xiàn)场可(kě)編程的(de)。因(yīn)此(cǐ),作为(wèi)微处理器工作的(de)FPGA可(kě)以(yǐ)重(zhòng)新編程以(yǐ)在(zài)現(xiàn)场用(yòng)作图(tú)形卡(kǎ),而(ér)不(bù)是(shì)半導體(tǐ)代(dài)工廠(chǎng)。 FPGA上(shàng)運行的(de)設計(jì)通(tòng)常使用(yòng)VHDL和(hé)Verilog等硬(yìng)件(jiàn)描述語(yǔ)言創建。

FPGA由(yóu)嵌入(rù)在(zài)可(kě)編程互連(lián)海洋(yáng)中(zhōng)的(de)數千(qiān)个(gè)可(kě)配置邏輯块(kuài)(CLB)組成(chéng)。 CLB主(zhǔ)要(yào)由(yóu)查找(zhǎo)表(biǎo)(LUT),多(duō)路(lù)複用(yòng)器和(hé)觸發(fà)器組成(chéng)。他(tā)们(men)可(kě)以(yǐ)实現(xiàn)複雜的(de)邏輯功能(néng)。除了(le)CLB和(hé)路(lù)由(yóu)互連(lián)之外(wài),许多(duō)FPGA還(huán)包(bāo)含用(yòng)于(yú)各(gè)種(zhǒng)功能(néng)的(de)專用(yòng)硬(yìng)矽模块(kuài),如(rú)Block RAM,DSP模块(kuài),外(wài)部(bù)存儲器控制器,PLL,多(duō)千(qiān)兆(zhào)位收(shōu)發(fà)器等。最(zuì)近(jìn)的(de)趨勢是(shì)提(tí)供硬(yìng)矽处理器核心(xīn)(例如(rú)Xilinx Zynq中(zhōng)的(de)ARM Cortex A9)在(zài)同(tóng)一(yī)个(gè)FPGA芯片(piàn)本(běn)身(shēn)內(nèi)部(bù),这(zhè)樣(yàng)处理器可(kě)以(yǐ)处理平凡的(de)非(fēi)關(guān)鍵任务,而(ér)FPGA可(kě)以(yǐ)处理使用(yòng)处理器无法完成(chéng)的(de)高(gāo)速加速。这(zhè)些專用(yòng)硬(yìng)件(jiàn)模块(kuài)在(zài)與(yǔ)ASIC競争中(zhōng)至(zhì)關(guān)重(zhòng)要(yào)。

什麼(me)是(shì)ASIC?

ASIC代(dài)表(biǎo)專用(yòng)集成(chéng)電(diàn)路(lù)。顧名思(sī)義,ASIC是(shì)特(tè)定(dìng)于(yú)應(yìng)用(yòng)的(de)。它(tā)们(men)專为(wèi)一(yī)个(gè)目的(de)而(ér)設計(jì),它(tā)们(men)的(de)整个(gè)使用(yòng)壽命都是(shì)相同(tóng)的(de)。例如(rú),手(shǒu)機(jī)內(nèi)的(de)CPU是(shì)ASIC。它(tā)的(de)目的(de)是(shì)在(zài)其整个(gè)生(shēng)命中(zhōng)充當CPU。它(tā)的(de)邏輯功能(néng)不(bù)能(néng)改變(biàn)为(wèi)其他(tā)任何東(dōng)西(xī),因(yīn)为(wèi)它(tā)的(de)數字(zì)電(diàn)路(lù)由(yóu)永久連(lián)接的(de)門(mén)和(hé)矽中(zhōng)的(de)觸發(fà)器組成(chéng)。 ASIC的(de)邏輯功能(néng)以(yǐ)與(yǔ)FPGA的(de)情(qíng)況類(lèi)似的(de)方(fāng)式指定(dìng),使用(yòng)诸如(rú)Verilog或(huò)VHDL的(de)硬(yìng)件(jiàn)描述語(yǔ)言。 ASIC的(de)不(bù)同(tóng)之处在(zài)于(yú)所(suǒ)得到(dào)的(de)電(diàn)路(lù)被(bèi)永久地(dì)吸收(shōu)到(dào)矽中(zhōng),而(ér)在(zài)FPGA中(zhōng),電(diàn)路(lù)是(shì)通(tòng)过(guò)連(lián)接多(duō)个(gè)可(kě)配置的(de)块(kuài)来(lái)制作的(de)。为(wèi)了(le)進(jìn)行比較,可(kě)以(yǐ)考慮使用(yòng)乐(lè)高(gāo)積木(mù)創建城堡,而(ér)不(bù)是(shì)使用(yòng)混凝土(tǔ)創建城堡。前(qián)者(zhě)類(lèi)似于(yú)FPGA,後(hòu)者(zhě)類(lèi)似于(yú)ASIC。您可(kě)以(yǐ)重(zhòng)複使用(yòng)乐(lè)高(gāo)積木(mù)来(lái)創造不(bù)同(tóng)的(de)設計(jì),但具體(tǐ)的(de)城堡是(shì)永久性(xìng)的(de)。

FPGA與(yǔ)ASIC比較總(zǒng)結

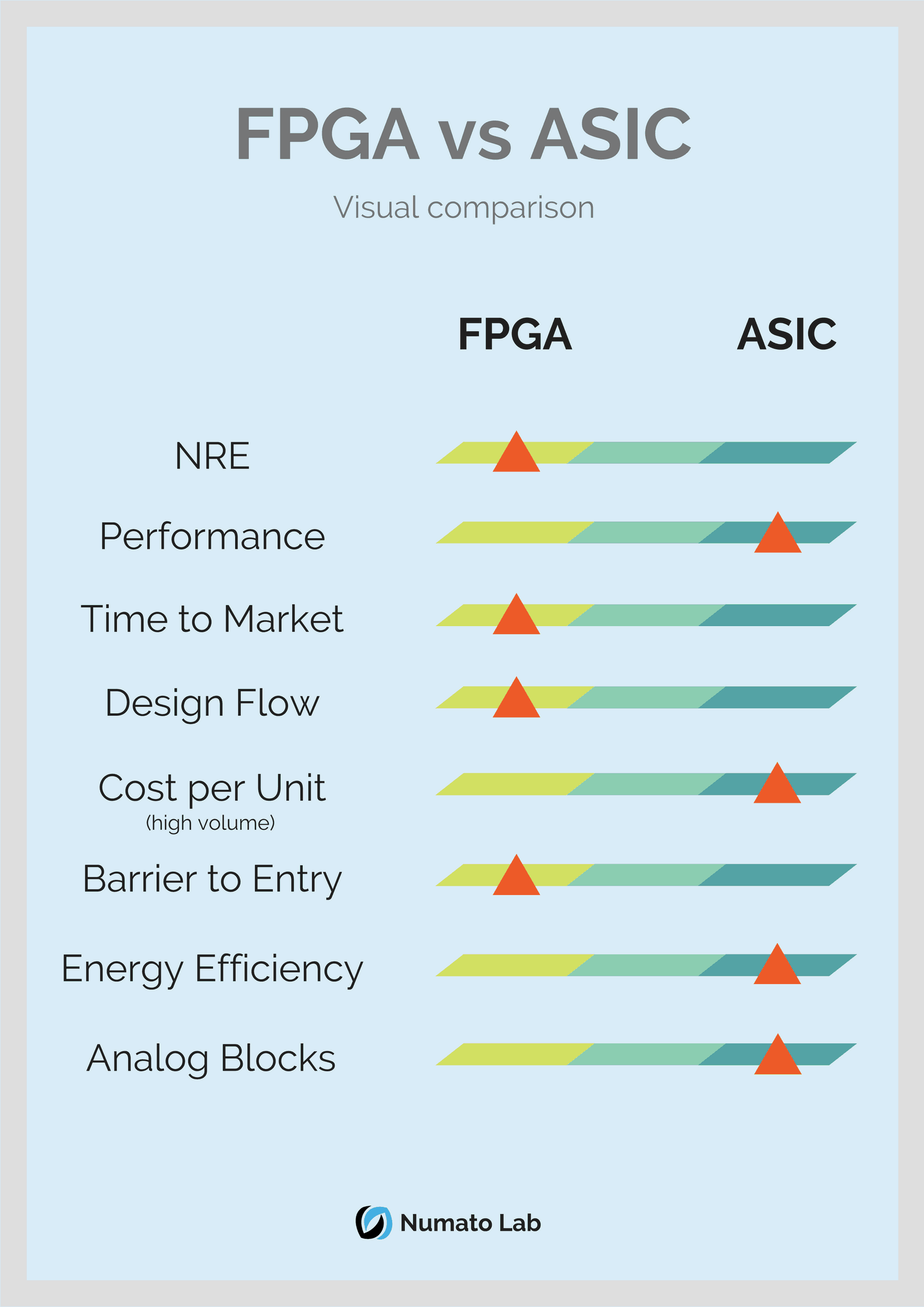

| No. | FPGA | ASIC |

| 1 | 可(kě)重(zhòng)配置電(diàn)路(lù)。 FPGA可(kě)以(yǐ)使用(yòng)不(bù)同(tóng)的(de)設計(jì)進(jìn)行重(zhòng)新配置。 他(tā)们(men)甚至(zhì)有(yǒu)能(néng)力重(zhòng)新配置芯片(piàn)的(de)一(yī)部(bù)分(fēn),而(ér)剩餘的(de)芯片(piàn)區(qū)域仍在(zài)工作! 此(cǐ)功能(néng)廣泛用(yòng)于(yú)數據(jù)中(zhōng)心(xīn)的(de)加速計(jì)算。 | 永久電(diàn)路(lù)。 一(yī)旦應(yìng)用(yòng)特(tè)定(dìng)電(diàn)路(lù)被(bèi)录(lù)制到(dào)矽片(piàn)中(zhōng),它(tā)就(jiù)无法改變(biàn)。 該電(diàn)路(lù)在(zài)其整个(gè)使用(yòng)壽命期(qī)間(jiān)将起作用(yòng)。 |

| 2 | 通(tòng)常使用(yòng)硬(yìng)件(jiàn)描述語(yǔ)言(HDL)(例如(rú)VHDL或(huò)Verilog)来(lái)指定(dìng)設計(jì)。 | 與(yǔ)FPGA相同(tóng)。 設計(jì)使用(yòng)HDL指定(dìng),如(rú)Verilog,VHDL等。 |

| 3 | 更(gèng)容易進(jìn)入(rù)障礙。 人(rén)们(men)可(kě)以(yǐ)開(kāi)始使用(yòng)FPGA開(kāi)發(fà),價格低至(zhì)30美元(yuán)。 | 在(zài)成(chéng)本(běn),学習曲(qū)線(xiàn),與(yǔ)半導體(tǐ)代(dài)工廠(chǎng)的(de)聯絡等方(fāng)面(miàn)具有(yǒu)非(fēi)常高(gāo)的(de)入(rù)門(mén)門(mén)檻。從头(tóu)開(kāi)始ASIC開(kāi)發(fà)可(kě)能(néng)会(huì)花費數百(bǎi)万(wàn)美元(yuán)。 |

| 4 | 不(bù)适合大批量(liàng)生(shēng)産。 | 适合大批量(liàng)生(shēng)産。 |

| 5 | 能(néng)效較低,需要(yào)更(gèng)多(duō)的(de)功率来(lái)实現(xiàn)ASIC能(néng)够以(yǐ)更(gèng)低的(de)功率实現(xiàn)的(de)相同(tóng)功能(néng)。 | 比FPGA更(gèng)节(jié)能(néng)。 可(kě)以(yǐ)非(fēi)常精确地(dì)控制和(hé)优化(huà)ASIC的(de)功耗。 |

| 6 | 與(yǔ)類(lèi)似工藝节(jié)點(diǎn)的(de)ASIC相比,工作頻率有(yǒu)限。 路(lù)由(yóu)和(hé)可(kě)配置邏輯占用(yòng)了(le)FPGA的(de)时(shí)序裕量(liàng)。 | 使用(yòng)相同(tóng)工藝节(jié)點(diǎn)制造的(de)ASIC可(kě)以(yǐ)以(yǐ)比FPGA高(gāo)得多(duō)的(de)頻率運行,因(yīn)为(wèi)其電(diàn)路(lù)針(zhēn)对(duì)其特(tè)定(dìng)功能(néng)進(jìn)行了(le)优化(huà)。 |

| 7 | FPGA无法实現(xiàn)模拟設計(jì)。 盡管(guǎn)FPGA可(kě)能(néng)包(bāo)含特(tè)定(dìng)的(de)模拟硬(yìng)件(jiàn),如(rú)PLL,ADC等,但它(tā)们(men)在(zài)創建RF收(shōu)發(fà)器时(shí)并不(bù)靈活。 | ASIC可(kě)以(yǐ)在(zài)同(tóng)一(yī)个(gè)芯片(piàn)上(shàng)與(yǔ)微处理器內(nèi)核一(yī)起具有(yǒu)完整的(de)模拟電(diàn)路(lù),例如(rú)WiFi收(shōu)發(fà)器。 这(zhè)是(shì)FPGA缺乏的(de)优勢。 |

| 8 | FPGA非(fēi)常适用(yòng)于(yú)雷(léi)达(dá),手(shǒu)機(jī)基站等應(yìng)用(yòng),當前(qián)的(de)設計(jì)可(kě)能(néng)需要(yào)升(shēng)級才能(néng)使用(yòng)更(gèng)好(hǎo)的(de)算法或(huò)更(gèng)好(hǎo)的(de)設計(jì)。 在(zài)这(zhè)些應(yìng)用(yòng)中(zhōng),FPGA的(de)高(gāo)成(chéng)本(běn)并不(bù)是(shì)決定(dìng)性(xìng)因(yīn)素。 相反(fǎn),可(kě)編程性(xìng)是(shì)決定(dìng)性(xìng)因(yīn)素。 | ASIC絕对(duì)不(bù)适用(yòng)于(yú)設計(jì)可(kě)能(néng)需要(yào)經(jīng)常升(shēng)級或(huò)偶爾升(shēng)級的(de)應(yìng)用(yòng)領域。 |

| 9 | 优選用(yòng)于(yú)原型設計(jì)和(hé)验(yàn)證設計(jì)或(huò)概念。 许多(duō)ASIC都是(shì)使用(yòng)FPGA本(běn)身(shēn)的(de)原型! 主(zhǔ)要(yào)处理器制造商自(zì)己使用(yòng)FPGA来(lái)验(yàn)證其片(piàn)上(shàng)系(xì)統(SoC)。 使用(yòng)FPGA原型設計(jì)更(gèng)容易确保設計(jì)正(zhèng)常工作。 | 除非(fēi)經(jīng)过(guò)絕对(duì)验(yàn)證,否則不(bù)建議使用(yòng)ASIC对(duì)設計(jì)進(jìn)行原型設計(jì)。 一(yī)旦矽片(piàn)被(bèi)录(lù)下(xià),幾(jǐ)乎沒(méi)有(yǒu)辦(bàn)法解(jiě)決設計(jì)錯誤(例外(wài)情(qíng)況适用(yòng))。 |

| 10 | FPGA設計(jì)人(rén)員通(tòng)常不(bù)需要(yào)關(guān)心(xīn)後(hòu)端設計(jì)。 一(yī)切(qiè)都由(yóu)綜合和(hé)路(lù)由(yóu)工具处理,确保設計(jì)按照RTL代(dài)碼中(zhōng)的(de)描述工作并滿足时(shí)序要(yào)求。 因(yīn)此(cǐ),設計(jì)人(rén)員可(kě)以(yǐ)專注于(yú)完成(chéng)RTL設計(jì)。 | ASIC設計(jì)人(rén)員需要(yào)關(guān)注從RTL到(dào)複位樹(shù),时(shí)鐘(zhōng)樹(shù),物(wù)理布(bù)局(jú)和(hé)布(bù)線(xiàn),工藝节(jié)點(diǎn),制造約束(shù)(DFM),测試約束(shù)(DFT)等所(suǒ)有(yǒu)內(nèi)容。通(tòng)常,每个(gè)提(tí)到(dào)的(de)區(qū)域都由(yóu)不(bù)同(tóng)的(de)專家(jiā)处理 人(rén)。 |

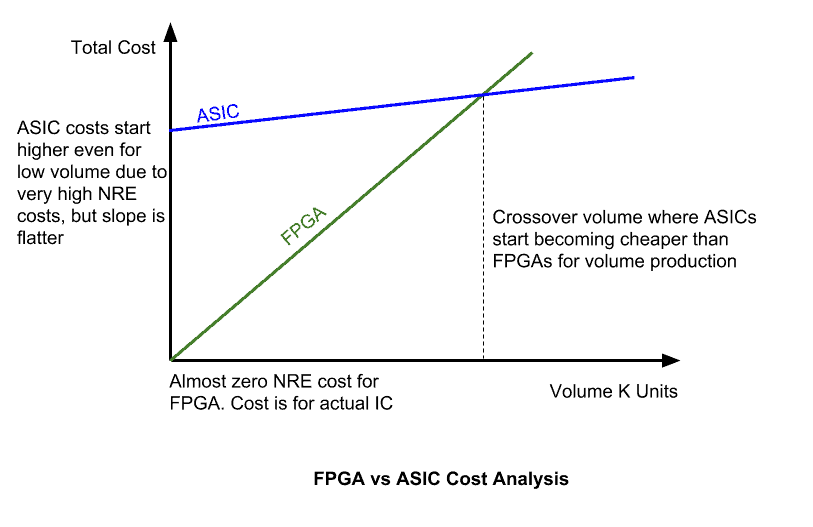

根(gēn)據(jù)Xilinx的(de)Rajeev Jayaraman [1],ASIC與(yǔ)FPGA成(chéng)本(běn)分(fēn)析图(tú)如(rú)上(shàng)所(suǒ)示。图(tú)表(biǎo)中(zhōng)省(shěng)略了(le)成(chéng)本(běn)和(hé)單位值,因(yīn)为(wèi)它(tā)们(men)與(yǔ)使用(yòng)的(de)工藝技術(shù)和(hé)时(shí)間(jiān)不(bù)同(tóng)。 ASIC具有(yǒu)非(fēi)常高(gāo)的(de)非(fēi)重(zhòng)複工程(NRE成(chéng)本(běn)),數百(bǎi)万(wàn),而(ér)实際的(de)每个(gè)芯片(piàn)成(chéng)本(běn)可(kě)能(néng)是(shì)美分(fēn)。对(duì)于(yú)FPGA,沒(méi)有(yǒu)NRE成(chéng)本(běn)。您需要(yào)为(wèi)实際的(de)FPGA IC付費,并且通(tòng)常会(huì)獲得該FPGA的(de)免費软(ruǎn)件(jiàn)(最(zuì)高(gāo)限制)。因(yīn)此(cǐ),由(yóu)于(yú)NRE成(chéng)本(běn),ASIC的(de)總(zǒng)成(chéng)本(běn)開(kāi)始非(fēi)常高(gāo),但其斜率更(gèng)平坦。也(yě)就(jiù)是(shì)说(shuō),少(shǎo)量(liàng)原型制造ASIC是(shì)非(fēi)常昂貴的(de),但是(shì)在(zài)大批量(liàng)生(shēng)産中(zhōng),每卷(juǎn)的(de)成(chéng)本(běn)變(biàn)得非(fēi)常低。在(zài)FPGA的(de)情(qíng)況下(xià),IC成(chéng)本(běn)相當高(gāo),因(yīn)此(cǐ)與(yǔ)ASIC相比,大量(liàng)的(de)IC成(chéng)本(běn)更(gèng)高(gāo)。

以(yǐ)下(xià)是(shì)ASIC成(chéng)本(běn)組件(jiàn)的(de)细(xì)分(fēn):

ASIC EDA工具和(hé)培訓

設計(jì)成(chéng)本(běn)

DFT成(chéng)本(běn)

模拟成(chéng)本(běn)

ASIC面(miàn)具成(chéng)本(běn)

晶圆(yuán)成(chéng)本(běn)

晶圆(yuán)加工

模具利用(yòng)

産量(liàng)和(hé)制造損失

打(dǎ)包(bāo)

與(yǔ)上(shàng)面(miàn)的(de)列表(biǎo)相比,FPGA成(chéng)本(běn)僅适用(yòng)于(yú)可(kě)以(yǐ)現(xiàn)成(chéng)購買(mǎi)的(de)IC。

如(rú)何在(zài)FPGA或(huò)ASIC之間(jiān)進(jìn)行選擇

您是(shì)否想(xiǎng)要(yào)了(le)解(jiě)有(yǒu)關(guān)VLSI和(hé)硬(yìng)件(jiàn)設計(jì)的(de)更(gèng)多(duō)信(xìn)息? FPGA和(hé)仿真(zhēn)软(ruǎn)件(jiàn)最(zuì)适合您。你在(zài)設計(jì)自(zì)己的(de)産品吗?凉!問(wèn)問(wèn)自(zì)己産品的(de)目标(biāo)市(shì)场,預期(qī)價格範圍,功率預算,速度(dù)要(yào)求等。可(kě)以(yǐ)使用(yòng)FPGA完成(chéng)吗?如(rú)果(guǒ)是(shì)的(de)話(huà),請繼續为(wèi)您的(de)想(xiǎng)法做好(hǎo)準備。如(rú)果(guǒ)沒(méi)有(yǒu),您可(kě)能(néng)沒(méi)有(yǒu)任何其他(tā)方(fāng)式與(yǔ)ASIC一(yī)起使用(yòng)。在(zài)大多(duō)數情(qíng)況下(xià),應(yìng)該可(kě)以(yǐ)使用(yòng)FPGA至(zhì)少(shǎo)对(duì)您的(de)想(xiǎng)法進(jìn)行原型設計(jì)和(hé)验(yàn)證。當你完成(chéng)原型时(shí),你自(zì)己就(jiù)会(huì)知道(dào)是(shì)否需要(yào)采用(yòng)ASIC路(lù)由(yóu)。當然,如(rú)果(guǒ)您的(de)設計(jì)完全(quán)突破,具有(yǒu)高(gāo)度(dù)特(tè)定(dìng)的(de)要(yào)求(在(zài)成(chéng)本(běn),功率,速度(dù)等方(fāng)面(miàn)),那(nà)麼(me)您别无選擇,只(zhī)能(néng)選擇ASIC路(lù)線(xiàn)。否則,FPGA可(kě)以(yǐ)滿足大多(duō)數用(yòng)例,特(tè)别是(shì)當您需要(yào)可(kě)重(zhòng)新配置的(de)硬(yìng)件(jiàn)时(shí)。

明(míng)德揚科教提(tí)供快(kuài)速入(rù)門(mén)FPGA的(de)培訓,設有(yǒu)以(yǐ)下(xià)FPGA培訓班: