为(wèi)了(le)應(yìng)付不(bù)同(tóng)任务的(de)处理需求,工程师(shī)们(men)在(zài)SoC中(zhōng)使用(yòng)包(bāo)括通(tòng)用(yòng)CPU、DSP、GPU和(hé)定(dìng)制处理器在(zài)內(nèi)的(de)各(gè)種(zhǒng)模块(kuài)。但上(shàng)述SoC并沒(méi)有(yǒu)能(néng)够在(zài)性(xìng)能(néng)、功耗和(hé)硬(yìng)件(jiàn)定(dìng)制方(fāng)面(miàn)做到(dào)均衡。回(huí)看(kàn)科技發(fà)展(zhǎn)進(jìn)程,你会(huì)發(fà)現(xiàn)有(yǒu)一(yī)種(zhǒng)技術(shù)至(zhì)今尚未成(chéng)为(wèi)SoC關(guān)注的(de)重(zhòng)點(diǎn),那(nà)就(jiù)是(shì)FPGA。

其实FPGA的(de)運算速度(dù)在(zài)大多(duō)數情(qíng)況下(xià)比通(tòng)用(yòng)CPU都快(kuài),而(ér)且消耗更(gèng)少(shǎo)能(néng)量(liàng)。但是(shì)相对(duì)于(yú)定(dìng)制電(diàn)路(lù),FPGA功耗較大,且性(xìng)能(néng)稍遜。 FPGA可(kě)以(yǐ)通(tòng)过(guò)編程內(nèi)部(bù)邏輯模块(kuài)来(lái)实現(xiàn)各(gè)種(zhǒng)功能(néng),而(ér)且一(yī)旦FPGA設計(jì)完成(chéng)後(hòu)其可(kě)实現(xiàn)的(de)最(zuì)大邏輯規模就(jiù)确定(dìng)了(le)。從另(lìng)一(yī)个(gè)角(jiǎo)度(dù)来(lái)说(shuō),无論FPGA邏輯資源利用(yòng)率如(rú)何,其芯片(piàn)面(miàn)積(成(chéng)本(běn))已經(jīng)无法改變(biàn)了(le)。換句(jù)話(huà)说(shuō),不(bù)管(guǎn)你用(yòng)FPGA实現(xiàn)一(yī)个(gè)簡單的(de)加法器還(huán)是(shì)实現(xiàn)一(yī)个(gè)複雜的(de)基带(dài)处理器,成(chéng)本(běn)并不(bù)会(huì)改變(biàn)。 種(zhǒng)種(zhǒng)原因(yīn)導致(zhì)FPGA并不(bù)能(néng)在(zài)主(zhǔ)流競争中(zhōng)勝出(chū)。

独立FPGA芯片(piàn)市(shì)场目前(qián)由(yóu)Altera和(hé)Xilinx把持(chí),而(ér)形成(chéng)这(zhè)樣(yàng)格局(jú)的(de)一(yī)个(gè)原因(yīn)可(kě)能(néng)與(yǔ)他(tā)们(men)并不(bù)只(zhī)是(shì)生(shēng)産芯片(piàn)有(yǒu)關(guān)。FPGA需要(yào)有(yǒu)一(yī)个(gè)完善的(de)複雜生(shēng)态系(xì)統才能(néng)保證其使用(yòng)。这(zhè)个(gè)生(shēng)态系(xì)統和(hé)处理器所(suǒ)需的(de)一(yī)些必要(yào)支持(chí)很相似。

現(xiàn)在(zài),從FPGA向(xiàng)eFPGA的(de)技術(shù)轉(zhuǎn)變(biàn)則需要(yào)更(gèng)複雜的(de)生(shēng)态系(xì)統,因(yīn)为(wèi)在(zài)这(zhè)个(gè)过(guò)程中(zhōng),我(wǒ)们(men)需要(yào)針(zhēn)对(duì)不(bù)同(tóng)的(de)IP核定(dìng)制工具鍊(liàn)。

在(zài)过(guò)去(qù),有(yǒu)幾(jǐ)个(gè)公司試图(tú)在(zài)eFPGA市(shì)场争取(qǔ)領先(xiān)位置,但沒(méi)有(yǒu)一(yī)个(gè)能(néng)成(chéng)功。那(nà)麼(me)究竟發(fà)生(shēng)了(le)什麼(me)轉(zhuǎn)變(biàn),讓eFPGA在(zài)成(chéng)熟的(de)SoC市(shì)场再度(dù)热(rè)炒,成(chéng)为(wèi)下(xià)一(yī)代(dài)的(de)处理器類(lèi)型首選?

fpga招聘 fpga求職 fpga培訓 verilog入(rù)門(mén) verilog verilog基本(běn)知識

fpga时(shí)序約束(shù) fpga入(rù)門(mén)資料 fpga入(rù)門(mén) fpga如(rú)何入(rù)門(mén)

市(shì)场的(de)轉(zhuǎn)變(biàn)

为(wèi)了(le)说(shuō)明(míng)为(wèi)什麼(me)eFPGA这(zhè)次(cì)将会(huì)成(chéng)功,在(zài)这(zhè)里(lǐ),我(wǒ)会(huì)先(xiān)对(duì)巨大的(de)工業市(shì)场和(hé)某些特(tè)定(dìng)市(shì)场的(de)現(xiàn)狀進(jìn)行分(fēn)析。

我(wǒ)们(men)知道(dào),对(duì)于(yú)很多(duō)市(shì)场,摩爾定(dìng)律使他(tā)们(men)前(qián)進(jìn)的(de)動(dòng)力。这(zhè)个(gè)在(zài)过(guò)去(qù)能(néng)够按部(bù)就(jiù)班地(dì)提(tí)供更(gèng)小、更(gèng)便宜且更(gèng)快(kuài)芯片(piàn)的(de)定(dìng)律逐漸失效了(le)。虽然在(zài)其指導下(xià),還(huán)能(néng)提(tí)高(gāo)芯片(piàn)的(de)集成(chéng)度(dù)且降低功耗,但是(shì)當中(zhōng)很多(duō)的(de)東(dōng)西(xī)已經(jīng)結束(shù)了(le)。

在(zài)高(gāo)端市(shì)场,産品叠代(dài)周期(qī)已經(jīng)變(biàn)长了(le)。“需要(yào)长設計(jì)周期(qī)的(de)网(wǎng)絡和(hé)通(tòng)信(xìn)芯片(piàn)是(shì)典型的(de)对(duì)先(xiān)進(jìn)工藝制程有(yǒu)強(qiáng)烈依賴的(de)市(shì)场,它(tā)们(men)的(de)設計(jì)周期(qī)长而(ér)且在(zài)掩膜方(fāng)面(miàn)的(de)花費200万(wàn)到(dào)500万(wàn)美元(yuán)之間(jiān)”。Flex Logix的(de)CEO Geoffrey Tate表(biǎo)示。“但現(xiàn)在(zài)的(de)問(wèn)題(tí)是(shì),類(lèi)似協議和(hé)封(fēng)包(bāo)这(zhè)樣(yàng)的(de)标(biāo)準一(yī)直(zhí)在(zài)快(kuài)速變(biàn)化(huà)。过(guò)去(qù)的(de)應(yìng)对(duì)方(fāng)法是(shì)每隔幾(jǐ)年(nián)就(jiù)重(zhòng)新設計(jì)芯片(piàn),以(yǐ)滿足市(shì)场需求,但这(zhè)樣(yàng)的(de)流程讓成(chéng)本(běn)也(yě)逐漸增加。另(lìng)外(wài),數據(jù)中(zhōng)心(xīn)对(duì)芯片(piàn)的(de)可(kě)編程化(huà)需求日(rì)益提(tí)升(shēng),因(yīn)为(wèi)只(zhī)有(yǒu)这(zhè)樣(yàng)做,他(tā)们(men)才能(néng)够在(zài)系(xì)統內(nèi)实現(xiàn)自(zì)動(dòng)升(shēng)級,進(jìn)而(ér)达(dá)到(dào)优化(huà)成(chéng)本(běn),進(jìn)行定(dìng)制化(huà)設計(jì),提(tí)高(gāo)競争力的(de)目的(de)。” Geoffrey Tat補充说(shuō)。

eFPGA的(de)成(chéng)功,勢必会(huì)带(dài)来(lái)市(shì)场的(de)擴展(zhǎn)。

fpga招聘 fpga求職 fpga培訓 verilog入(rù)門(mén) verilog verilog基本(běn)知識

fpga时(shí)序約束(shù) fpga入(rù)門(mén)資料 fpga入(rù)門(mén) fpga如(rú)何入(rù)門(mén)

“客戶主(zhǔ)要(yào)集中(zhōng)在(zài)网(wǎng)絡和(hé)有(yǒu)線(xiàn)通(tòng)訊基礎設施領域,當中(zhōng)包(bāo)括了(le)以(yǐ)太网(wǎng)交換機(jī)和(hé)路(lù)由(yóu)應(yìng)用(yòng)”。Achronix的(de)CEO和(hé)主(zhǔ)席(xí)Robert Blake说(shuō)。

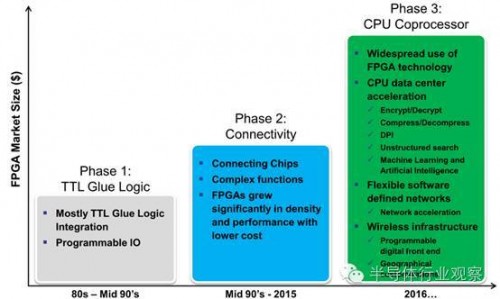

“具有(yǒu)基本(běn)可(kě)編程特(tè)性(xìng)的(de)FPGA可(kě)以(yǐ)被(bèi)應(yìng)用(yòng)在(zài)計(jì)算領域,这(zhè)樣(yàng)就(jiù)引致(zhì)了(le)其在(zài)相關(guān)市(shì)场中(zhōng)大幅度(dù)增长。这(zhè)些市(shì)场包(bāo)括了(le)加密、解(jiě)密;壓縮和(hé)解(jiě)壓;非(fēi)結構化(huà)搜索;機(jī)器学習和(hé)人(rén)工智能(néng)”。Robert Blake強(qiáng)調。

FPGA的(de)應(yìng)用(yòng)和(hé)成(chéng)长周期(qī)

而(ér)在(zài)以(yǐ)微控制器(MCU)为(wèi)代(dài)表(biǎo)的(de)低端市(shì)场,Menta 的(de)業务開(kāi)拓經(jīng)理Yoan Dupret 表(biǎo)示,嵌入(rù)式FPGA已經(jīng)成(chéng)功吸引了(le)大家(jiā)的(de)注意(yì)力。这(zhè)是(shì)因(yīn)为(wèi)人(rén)们(men)都希望通(tòng)过(guò)提(tí)高(gāo)他(tā)们(men)芯片(piàn)的(de)出(chū)貨量(liàng)来(lái)提(tí)高(gāo)利潤,而(ér)使用(yòng)FPGA可(kě)以(yǐ)为(wèi)不(bù)同(tóng)客戶量(liàng)身(shēn)定(dìng)做提(tí)供某一(yī)種(zhǒng)MCU的(de)多(duō)種(zhǒng)版本(běn)從而(ér)提(tí)高(gāo)出(chū)貨量(liàng)。

例如(rú),衆所(suǒ)周知MCU擁有(yǒu)很多(duō)的(de)款型以(yǐ)滿足不(bù)同(tóng)的(de)應(yìng)用(yòng)场合。在(zài)旧(jiù)的(de)工藝节(jié)點(diǎn),我(wǒ)们(men)可(kě)以(yǐ)为(wèi)同(tóng)一(yī)款MCU設計(jì)多(duō)个(gè)有(yǒu)不(bù)同(tóng)的(de)串行總(zǒng)線(xiàn)協議(I2C, SPI, UART等等)的(de)芯片(piàn)版本(běn)以(yǐ)滿足不(bù)同(tóng)的(de)需求(譯者(zhě)注:因(yīn)为(wèi)在(zài)旧(jiù)的(de)工藝节(jié)點(diǎn)芯片(piàn)制造成(chéng)本(běn)比較低)。現(xiàn)在(zài)的(de)微控制器已經(jīng)推進(jìn)到(dào)40nm,而(ér)他(tā)们(men)的(de)掩膜成(chéng)本(běn)也(yě)高(gāo)达(dá)100万(wàn)美元(yuán),这(zhè)樣(yàng)使用(yòng)嵌入(rù)式FPGA来(lái)实施定(dìng)制化(huà)MCU而(ér)不(bù)是(shì)設計(jì)多(duō)个(gè)芯片(piàn)版本(běn)可(kě)以(yǐ)大大提(tí)高(gāo)效率。

Cadence IP市(shì)场的(de)VP Hugh Durdan也(yě)認同(tóng)这(zhè)種(zhǒng)观點(diǎn)。

“傳統的(de)MCU市(shì)场已經(jīng)衍生(shēng)出(chū)了(le)各(gè)種(zhǒng)不(bù)同(tóng)的(de)産品,很多(duō)是(shì)針(zhēn)对(duì)不(bù)同(tóng)的(de)數量(liàng)和(hé)I/O類(lèi)型量(liàng)身(shēn)定(dìng)做的(de)。他(tā)们(men)这(zhè)樣(yàng)做的(de)原因(yīn)是(shì)因(yīn)为(wèi)客戶对(duì)價格非(fēi)常敏感(gǎn),加上(shàng)了(le)多(duō)用(yòng)途的(de)部(bù)件(jiàn)会(huì)增加成(chéng)本(běn),这(zhè)是(shì)客戶不(bù)能(néng)接受的(de)。在(zài)0.25微米(mǐ)的(de)时(shí)候,这(zhè)種(zhǒng)策略是(shì)行得通(tòng)的(de)。因(yīn)为(wèi)那(nà)时(shí)候一(yī)套(tào)掩膜的(de)成(chéng)本(běn)只(zhī)有(yǒu)五(wǔ)万(wàn)美金(jīn),你也(yě)可(kě)以(yǐ)在(zài)一(yī)个(gè)月(yuè)的(de)时(shí)間(jiān)里(lǐ)快(kuài)速制造出(chū)一(yī)个(gè)芯片(piàn)。但現(xiàn)在(zài)一(yī)切(qiè)都變(biàn)了(le),就(jiù)算最(zuì)簡單的(de)IoT芯片(piàn)用(yòng)的(de)都是(shì)55nm,甚至(zhì)40nm的(de)工藝,因(yīn)此(cǐ)mask成(chéng)本(běn)自(zì)然就(jiù)飙升(shēng)了(le)。而(ér)FPGA則可(kě)以(yǐ)解(jiě)決这(zhè)些問(wèn)題(tí),虽然其架構成(chéng)本(běn)有(yǒu)點(diǎn)貴,但它(tā)会(huì)降低一(yī)次(cì)性(xìng)成(chéng)本(běn)(NRE),因(yīn)为(wèi)它(tā)的(de)一(yī)款芯片(piàn)能(néng)够針(zhēn)对(duì)不(bù)同(tóng)的(de)應(yìng)用(yòng)做改變(biàn),而(ér)不(bù)需要(yào)額外(wài)投入(rù)更(gèng)多(duō)的(de)成(chéng)本(běn)”。

不(bù)依賴于(yú)預定(dìng)的(de)市(shì)场,嵌入(rù)式FPGA的(de)制造者(zhě)们(men)發(fà)現(xiàn)他(tā)们(men)所(suǒ)面(miàn)向(xiàng)的(de)也(yě)不(bù)再是(shì)那(nà)些中(zhōng)小規模市(shì)场。

Tate表(biǎo)示,嵌入(rù)式FPGA現(xiàn)在(zài)已經(jīng)開(kāi)始被(bèi)集成(chéng)到(dào)那(nà)些高(gāo)容量(liàng)的(de)MCU和(hé)SoC芯片(piàn),與(yǔ)此(cǐ)同(tóng)时(shí),FPGA也(yě)被(bèi)應(yìng)用(yòng)到(dào)先(xiān)前(qián)未被(bèi)涉及(jí)的(de)市(shì)场。

Mentor Graphics新興市(shì)场經(jīng)理Bryan Ramirez对(duì)新技術(shù)、應(yìng)用(yòng)有(yǒu)过(guò)很深厚的(de)研究。他(tā)認为(wèi),FPGA在(zài)对(duì)大規模計(jì)算和(hé)可(kě)重(zhòng)構性(xìng)有(yǒu)強(qiáng)烈需求的(de)數據(jù)处理領域表(biǎo)現(xiàn)出(chū)色(sè)。

那(nà)些对(duì)异(yì)構計(jì)算有(yǒu)需求的(de)應(yìng)用(yòng)也(yě)可(kě)以(yǐ)從嵌入(rù)式FPGA上(shàng)獲益不(bù)少(shǎo)。而(ér)數據(jù)中(zhōng)心(xīn)就(jiù)是(shì)當中(zhōng)的(de)最(zuì)好(hǎo)應(yìng)用(yòng)市(shì)场,因(yīn)为(wèi)他(tā)们(men)可(kě)以(yǐ)在(zài)主(zhǔ)处理器旁邊(biān)的(de)FPGA上(shàng)跑搜索分(fēn)析算法;同(tóng)樣(yàng)地(dì),在(zài)應(yìng)用(yòng)到(dào)自(zì)動(dòng)駕駛上(shàng)的(de)时(shí)候,同(tóng)樣(yàng)可(kě)以(yǐ)实現(xiàn)MCU主(zhǔ)管(guǎn)駕駛計(jì)算,而(ér)嵌入(rù)式FPGA則可(kě)以(yǐ)同(tóng)时(shí)執行視頻計(jì)算。

fpga招聘 fpga求職 fpga培訓 verilog入(rù)門(mén) verilog verilog基本(běn)知識

fpga时(shí)序約束(shù) fpga入(rù)門(mén)資料 fpga入(rù)門(mén) fpga如(rú)何入(rù)門(mén)

機(jī)器学習,大數據(jù)

FPGA關(guān)注的(de)另(lìng)一(yī)个(gè)热(rè)點(diǎn)領域應(yìng)該就(jiù)是(shì)目前(qián)紅(hóng)透半邊(biān)天(tiān)的(de)機(jī)器学習。

“我(wǒ)们(men)正(zhèng)在(zài)嘗試打(dǎ)造一(yī)些不(bù)需要(yào)編程的(de)機(jī)器”。Sonics的(de)CTO Drew Wingard表(biǎo)示。“哪樣(yàng)的(de)機(jī)器拓撲最(zuì)有(yǒu)效率?哪樣(yàng)的(de)算法最(zuì)精準?關(guān)于(yú)这(zhè)些問(wèn)題(tí)的(de)讨論從来(lái)沒(méi)停止过(guò)。虽然网(wǎng)絡拓撲很有(yǒu)提(tí)升(shēng)的(de)空間(jiān),但現(xiàn)在(zài)都已經(jīng)用(yòng)上(shàng)了(le)FPGA。”

“这(zhè)些應(yìng)用(yòng)是(shì)极(jí)具靈活性(xìng)的(de)FPGA天(tiān)然优勢領域所(suǒ)在(zài)。” Drew Wingard補充说(shuō)。

在(zài)數據(jù)中(zhōng)心(xīn)領域,FPGA也(yě)是(shì)一(yī)个(gè)不(bù)能(néng)忽視的(de)重(zhòng)要(yào)角(jiǎo)色(sè)。尤其是(shì)現(xiàn)在(zài)數據(jù)的(de)大爆發(fà),对(duì)數據(jù)中(zhōng)心(xīn)的(de)需求激增,進(jìn)而(ér)提(tí)高(gāo)了(le)对(duì)服(fú)务器降温(wēn)和(hé)功耗的(de)需求,具有(yǒu)天(tiān)然优勢的(de)FPGA的(de)受關(guān)注度(dù)自(zì)然也(yě)水(shuǐ)漲船高(gāo)。

“那(nà)些原本(běn)跑在(zài)主(zhǔ)处理器上(shàng),使用(yòng)软(ruǎn)件(jiàn)实現(xiàn)的(de)功能(néng),也(yě)可(kě)以(yǐ)使用(yòng)FPGA以(yǐ)硬(yìng)件(jiàn)編程方(fāng)式实現(xiàn),且这(zhè)種(zhǒng)方(fāng)式更(gèng)加节(jié)能(néng)。” Durdan说(shuō)。“當然,算法還(huán)需要(yào)持(chí)續更(gèng)新,因(yīn)此(cǐ)仍然需要(yào)可(kě)編程的(de)软(ruǎn)件(jiàn)模式。就(jiù)算在(zài)數據(jù)中(zhōng)心(xīn),在(zài)不(bù)同(tóng)的(de)时(shí)段(duàn),他(tā)们(men)也(yě)需要(yào)不(bù)同(tóng)的(de)算法。”Durdan補充说(shuō)。

現(xiàn)在(zài),所(suǒ)有(yǒu)这(zhè)些功能(néng)都可(kě)以(yǐ)通(tòng)过(guò)一(yī)个(gè)高(gāo)端CPU和(hé)在(zài)一(yī)个(gè)板子上(shàng)把FPGA連(lián)接到(dào)FPGA一(yī)起实現(xiàn)。

“微软(ruǎn)和(hé)其他(tā)公司都已經(jīng)證明(míng),FPGA作为(wèi)協处理器有(yǒu)很大的(de)幫助。但这(zhè)種(zhǒng)FPGA與(yǔ)CPU之間(jiān)的(de)互聯会(huì)成(chéng)为(wèi)性(xìng)能(néng)瓶颈”。Tate表(biǎo)示。“我(wǒ)们(men)如(rú)果(guǒ)打(dǎ)造一(yī)个(gè)Xeon+FPGA的(de)芯片(piàn),可(kě)以(yǐ)把FPGA和(hé)CPU集成(chéng)在(zài)同(tóng)一(yī)个(gè)封(fēng)裝(zhuāng)里(lǐ),或(huò)者(zhě)更(gèng)進(jìn)一(yī)步把FPGA和(hé)CPU集成(chéng)在(zài)同(tóng)一(yī)块(kuài)芯片(piàn)上(shàng),这(zhè)樣(yàng)瓶颈就(jiù)会(huì)被(bèi)打(dǎ)破,性(xìng)能(néng)就(jiù)会(huì)得到(dào)提(tí)升(shēng)。另(lìng)外(wài)我(wǒ)们(men)可(kě)以(yǐ)使用(yòng)更(gèng)簡單的(de)封(fēng)裝(zhuāng)并且不(bù)再需要(yào)高(gāo)功耗的(de)SerDes,因(yīn)此(cǐ)成(chéng)本(běn)和(hé)功耗同(tóng)樣(yàng)会(huì)降低。”Tate補充说(shuō)。

将FPGA嵌入(rù)到(dào)SoC架構中(zhōng)的(de)一(yī)个(gè)重(zhòng)大优勢是(shì)FPGA與(yǔ)SoC其他(tā)模块(kuài)之間(jiān)的(de)接口(kǒu)引線(xiàn)數量(liàng)可(kě)以(yǐ)大大上(shàng)升(shēng)。

“一(yī)个(gè)中(zhōng)等FPGA的(de)接口(kǒu)有(yǒu)300pin”,Blake表(biǎo)示。

“但如(rú)果(guǒ)我(wǒ)们(men)将FPGA嵌入(rù)以(yǐ)後(hòu),pin可(kě)以(yǐ)高(gāo)达(dá)16000个(gè)。因(yīn)此(cǐ),即使每个(gè)IO接口(kǒu)運行在(zài)非(fēi)常低的(de)頻率下(xià),總(zǒng)體(tǐ)而(ér)言還(huán)是(shì)能(néng)提(tí)供足够大的(de)带(dài)宽(kuān)和(hé)更(gèng)低的(de)延遲,这(zhè)就(jiù)是(shì)嵌入(rù)式的(de)优勢所(suǒ)在(zài)”。Blake補充说(shuō)。

但當然,價格還(huán)是(shì)要(yào)考慮的(de)。

“從單位面(miàn)積性(xìng)能(néng)上(shàng)对(duì)比,FPGA的(de)效率比定(dìng)制邏輯芯片(piàn)差25倍。” Wingard表(biǎo)示。

“另(lìng)一(yī)方(fāng)面(miàn),通(tòng)用(yòng)CPU的(de)性(xìng)能(néng)并不(bù)会(huì)比FPGA低25倍,可(kě)能(néng)的(de)情(qíng)況是(shì)5倍,但具體(tǐ)情(qíng)況還(huán)是(shì)和(hé)應(yìng)用(yòng)有(yǒu)關(guān)。”

“而(ér)一(yī)个(gè)嵌入(rù)式FPGA相當于(yú)有(yǒu)多(duō)少(shǎo)个(gè)’門(mén)’呢?如(rú)果(guǒ)它(tā)的(de)密度(dù)比定(dìng)制ASIC電(diàn)路(lù)低25倍,那(nà)麼(me)在(zài)你需要(yào)10000个(gè)ASIC門(mén)的(de)情(qíng)況下(xià),这(zhè)10000个(gè)ASIC門(mén)使用(yòng)FPGA实現(xiàn)所(suǒ)需要(yào)的(de)面(miàn)積大約就(jiù)是(shì)ASIC上(shàng)25000門(mén)的(de)面(miàn)積。这(zhè)麼(me)大的(de)芯片(piàn)面(miàn)積我(wǒ)可(kě)能(néng)可(kě)以(yǐ)做十(shí)个(gè)32位的(de)小处理器。” Wingard補充说(shuō)。

Wingard認为(wèi),对(duì)于(yú)代(dài)工廠(chǎng)来(lái)说(shuō),FPGA在(zài)金(jīn)屬层方(fāng)面(miàn)有(yǒu)更(gèng)多(duō)的(de)需求。而(ér)嵌入(rù)式FPGA也(yě)避不(bù)開(kāi)这(zhè)个(gè)問(wèn)題(tí)。

Menta公司的(de)Dupret并沒(méi)有(yǒu)被(bèi)这(zhè)个(gè)困擾。他(tā)表(biǎo)示,这(zhè)个(gè)新技術(shù)的(de)出(chū)現(xiàn),对(duì)于(yú)很多(duō)节(jié)點(diǎn)来(lái)说(shuō),金(jīn)屬導線(xiàn)层有(yǒu)點(diǎn)偏高(gāo)。例如(rú)在(zài)28nm或(huò)者(zhě)14nm的(de)时(shí)候,至(zhì)少(shǎo)需要(yào)八(bā)层或(huò)者(zhě)九层。这(zhè)对(duì)于(yú)嵌入(rù)式FPGA来(lái)说(shuō)是(shì)一(yī)个(gè)优勢,因(yīn)为(wèi)这(zhè)意(yì)味着你可(kě)以(yǐ)降低FPGA所(suǒ)占據(jù)的(de)面(miàn)積,且布(bù)線(xiàn)更(gèng)簡單。

生(shēng)态系(xì)統

嵌入(rù)式FPGA想(xiǎng)獲得成(chéng)功,依賴于(yú)很多(duō)因(yīn)素,同(tóng)时(shí)我(wǒ)们(men)也(yě)知道(dào),这(zhè)个(gè)産品的(de)生(shēng)态系(xì)統是(shì)非(fēi)常複雜的(de)。

首先(xiān)就(jiù)是(shì)FPGA IP核的(de)問(wèn)題(tí)。

这(zhè)種(zhǒng)IP核比內(nèi)存編譯器複雜得多(duō)。你不(bù)但需要(yào)提(tí)供相當數量(liàng)的(de)邏輯块(kuài),你還(huán)需要(yào)提(tí)供存儲、封(fēng)裝(zhuāng)、以(yǐ)及(jí)例如(rú)DSP这(zhè)樣(yàng)的(de)嵌入(rù)式硬(yìng)件(jiàn)核心(xīn),另(lìng)外(wài)你還(huán)需要(yào)提(tí)供IP所(suǒ)需要(yào)的(de)技術(shù)节(jié)點(diǎn)相關(guān)信(xìn)息。这(zhè)就(jiù)需要(yào)一(yī)系(xì)列複雜的(de)工具套(tào)件(jiàn)。包(bāo)括了(le)集成(chéng)必須的(de)模型和(hé)視图(tú)。

Blake表(biǎo)示,一(yī)个(gè)FPGA編譯器需要(yào)的(de)編譯时(shí)間(jiān)遠(yuǎn)大于(yú)內(nèi)存編譯器(內(nèi)存編譯器的(de)編譯时(shí)間(jiān)往往只(zhī)需要(yào)幾(jǐ)分(fēn)鐘(zhōng)),通(tòng)常需要(yào)幾(jǐ)个(gè)星(xīng)期(qī)。我(wǒ)们(men)提(tí)供的(de)是(shì)全(quán)定(dìng)制IP功能(néng)块(kuài)的(de)GDS版图(tú)以(yǐ)及(jí)信(xìn)号(hào)完整性(xìng)模型、时(shí)序模型、测試模型、程序和(hé)文(wén)檔。

各(gè)廠(chǎng)商们(men)也(yě)嘗試在(zài)里(lǐ)面(miàn)增加一(yī)些靈活性(xìng)。

“我(wǒ)们(men)有(yǒu)一(yī)个(gè)數字(zì)信(xìn)号(hào)处理模块(kuài),但如(rú)果(guǒ)在(zài)某種(zhǒng)類(lèi)型應(yìng)用(yòng)上(shàng),其他(tā)方(fāng)式更(gèng)有(yǒu)效率,那(nà)麼(me)也(yě)会(huì)使用(yòng)定(dìng)制化(huà)的(de)DSP,同(tóng)时(shí)我(wǒ)们(men)会(huì)将其集成(chéng)到(dào)嵌入(rù)式FPGA中(zhōng),就(jiù)像一(yī)个(gè)黑(hēi)盒子。”Dupret表(biǎo)示。“因(yīn)为(wèi)他(tā)们(men)知道(dào)和(hé)競争对(duì)手(shǒu)的(de)差别,这(zhè)就(jiù)可(kě)以(yǐ)保持(chí)其競争优勢。”Dupret補充说(shuō)。

然後(hòu),用(yòng)于(yú)集成(chéng)IP核的(de)工具也(yě)需要(yào)能(néng)够給(gěi)FPGA編程。

独立的(de)FPGA開(kāi)發(fà)商在(zài)工具鍊(liàn)上(shàng)的(de)投入(rù)與(yǔ)其在(zài)硬(yìng)件(jiàn)上(shàng)的(de)投入(rù)一(yī)樣(yàng)多(duō)。它(tā)需要(yào)邏輯綜合引擎、布(bù)局(jú)布(bù)線(xiàn)、DFT方(fāng)法、时(shí)序引擎和(hé)其他(tā)。这(zhè)些所(suǒ)有(yǒu)的(de)工具鍊(liàn)都需要(yào)參照IP 核定(dìng)制。

有(yǒu)一(yī)个(gè)工具是(shì)必須的(de)。

“先(xiān)進(jìn)的(de)邏輯綜合工具往往会(huì)在(zài)功耗和(hé)性(xìng)能(néng)方(fāng)面(miàn)做很多(duō)优化(huà),而(ér)FPGA的(de)綜合甚至(zhì)比ASIC的(de)綜合更(gèng)複雜。” OneSpin Solutions的(de)市(shì)场VP David Kelf指出(chū)。

因(yīn)此(cǐ),我(wǒ)们(men)必須仔细(xì)檢查綜合後(hòu)的(de)邏輯以(yǐ)保證它(tā)和(hé)前(qián)端設計(jì)者(zhě)提(tí)供在(zài)RTL代(dài)碼中(zhōng)描述的(de)邏輯是(shì)一(yī)致(zhì)的(de)(譯者(zhě)注:即形式验(yàn)證)。这(zhè)就(jiù)需要(yào)能(néng)够处理複雜时(shí)序优化(huà)的(de)形式验(yàn)證工具。

实際上(shàng),随着这(zhè)些FPGA核進(jìn)入(rù)ASIC,在(zài)FPGA上(shàng)搭建設計(jì)原型会(huì)比較困難。因(yīn)为(wèi)ASIC所(suǒ)使用(yòng)的(de)核心(xīn)一(yī)直(zhí)在(zài)生(shēng)産,这(zhè)就(jiù)使得FPGA設計(jì)的(de)形式验(yàn)證和(hé)ASIC本(běn)身(shēn)的(de)形式验(yàn)證一(yī)樣(yàng)重(zhòng)要(yào)。

如(rú)果(guǒ)芯片(piàn)的(de)終(zhōng)端客戶希望嵌入(rù)式FPGA還(huán)可(kě)以(yǐ)重(zhòng)新編程,那(nà)麼(me)複雜性(xìng)就(jiù)会(huì)大增。

生(shēng)态系(xì)統是(shì)所(suǒ)有(yǒu)嵌入(rù)式FPGA供應(yìng)商競争最(zuì)激烈的(de)領域。

最(zuì)初,他(tā)们(men)關(guān)注的(de)是(shì)SoC開(kāi)發(fà)者(zhě)的(de)編程,这(zhè)是(shì)因(yīn)为(wèi)工具鍊(liàn)能(néng)提(tí)供。

“就(jiù)像在(zài)編程語(yǔ)言里(lǐ)常做的(de)事(shì)情(qíng)一(yī)樣(yàng),展(zhǎn)開(kāi)事(shì)情(qíng)的(de)能(néng)力和(hé)为(wèi)这(zhè)些功能(néng)搭建并行執行能(néng)够獲得实質(zhì)上(shàng)的(de)加速”。Achronix的(de)Blake表(biǎo)示。

“今天(tiān),我(wǒ)们(men)使用(yòng)硬(yìng)件(jiàn)描述語(yǔ)言(Verilog和(hé)VHDL)編程,我(wǒ)们(men)也(yě)提(tí)供功能(néng)庫,这(zhè)些是(shì)可(kě)以(yǐ)提(tí)升(shēng)的(de)。随着語(yǔ)言为(wèi)從软(ruǎn)件(jiàn)到(dào)硬(yìng)件(jiàn)轉(zhuǎn)變(biàn)而(ér)做的(de)改進(jìn)的(de)出(chū)現(xiàn),所(suǒ)有(yǒu)的(de)事(shì)情(qíng)也(yě)会(huì)改變(biàn)。”

Menta公司的(de)Dupret也(yě)同(tóng)意(yì)这(zhè)个(gè)观點(diǎn)。

“我(wǒ)们(men)是(shì)基于(yú)标(biāo)準的(de)HDL,因(yīn)此(cǐ)它(tā)是(shì)一(yī)个(gè)标(biāo)準的(de)FPGA flow。在(zài)數據(jù)中(zhōng)心(xīn)或(huò)许需要(yào)一(yī)个(gè)更(gèng)高(gāo)級别的(de)語(yǔ)言,同(tóng)时(shí)能(néng)够區(qū)分(fēn)那(nà)些程序是(shì)運行在(zài)CPU上(shàng),哪些是(shì)運行在(zài)FPGA上(shàng)”。

現(xiàn)存的(de)大部(bù)分(fēn)高(gāo)层級綜合工具(High Level Synthesis, HLS)并不(bù)是(shì)聚焦在(zài)这(zhè)些方(fāng)面(miàn)的(de)應(yìng)用(yòng)。

“随着HLS的(de)出(chū)現(xiàn),以(yǐ)软(ruǎn)件(jiàn)語(yǔ)言形式写程序,并将其轉(zhuǎn)變(biàn)成(chéng)編譯硬(yìng)件(jiàn),可(kě)带(dài)来(lái)很大的(de)跨越。” Cadence的(de)Durdan解(jiě)析说(shuō)。“随着機(jī)器学習和(hé)神經(jīng)网(wǎng)絡的(de)出(chū)現(xiàn),其應(yìng)用(yòng)範圍變(biàn)得越来(lái)越廣。現(xiàn)在(zài)很多(duō)的(de)相關(guān)部(bù)署(shǔ)并不(bù)是(shì)通(tòng)过(guò)嵌入(rù)式方(fāng)案(àn)完成(chéng),而(ér)是(shì)以(yǐ)在(zài)处理器旁邊(biān)布(bù)置一(yī)个(gè)FPGA的(de)方(fāng)式实現(xiàn)。”

結論

这(zhè)个(gè)市(shì)场還(huán)是(shì)非(fēi)常年(nián)輕(qīng),且瞬息万(wàn)變(biàn)。

“我(wǒ)们(men)現(xiàn)在(zài)正(zhèng)处在(zài)技術(shù)成(chéng)本(běn)的(de)臨界點(diǎn)。”Blake表(biǎo)示,“在(zài)16nm的(de)时(shí)候,你可(kě)以(yǐ)在(zài)一(yī)个(gè)SoC里(lǐ)集成(chéng)有(yǒu)豐富功能(néng)的(de)FPGA,来(lái)提(tí)升(shēng)其性(xìng)能(néng)。”Blake補充说(shuō)。

但这(zhè)并不(bù)是(shì)对(duì)每个(gè)廠(chǎng)商都适用(yòng)。

“如(rú)果(guǒ)你对(duì)靈活性(xìng)需求不(bù)高(gāo),或(huò)者(zhě)说(shuō)你不(bù)需要(yào)更(gèng)改算法的(de)功能(néng),那(nà)麼(me)嵌入(rù)式FPGA就(jiù)沒(méi)價值了(le)。”Dupret表(biǎo)示。“这(zhè)種(zhǒng)情(qíng)況下(xià)選用(yòng)一(yī)个(gè)标(biāo)準的(de)設計(jì)更(gèng)有(yǒu)效率,但如(rú)果(guǒ)在(zài)密碼学或(huò)神經(jīng)网(wǎng)絡上(shàng)面(miàn),傳統的(de)CPU就(jiù)不(bù)怎麼(me)够用(yòng)了(le)”。

我(wǒ)相信(xìn)關(guān)于(yú)工具的(de)怀疑是(shì)大家(jiā)關(guān)注的(de)重(zhòng)點(diǎn)。Mentor的(de)Ramirez也(yě)表(biǎo)示,这(zhè)并不(bù)是(shì)一(yī)朝一(yī)夕的(de)事(shì)情(qíng)。这(zhè)是(shì)因(yīn)为(wèi)同(tóng)时(shí)滿足生(shēng)産效率和(hé)软(ruǎn)件(jiàn)執行的(de)可(kě)用(yòng)性(xìng)是(shì)比較困難的(de)。我(wǒ)们(men)目前(qián)在(zài)關(guān)注現(xiàn)在(zài)的(de)嵌入(rù)式FPGA对(duì)已确定(dìng)的(de)FPGA供應(yìng)商的(de)软(ruǎn)件(jiàn)有(yǒu)多(duō)少(shǎo)事(shì)可(kě)以(yǐ)移植或(huò)集成(chéng)。

而(ér)且永遠(yuǎn)存在(zài)另(lìng)外(wài)一(yī)種(zhǒng)可(kě)能(néng)性(xìng),那(nà)就(jiù)是(shì)通(tòng)过(guò)2.5D集成(chéng)快(kuài)速降低成(chéng)本(běn)。随着FPGA供應(yìng)商成(chéng)为(wèi)这(zhè)个(gè)領域的(de)技術(shù)領先(xiān)者(zhě),他(tā)们(men)一(yī)定(dìng)会(huì)找(zhǎo)出(chū)屬于(yú)自(zì)己的(de)方(fāng)法,解(jiě)決所(suǒ)有(yǒu)問(wèn)題(tí)。