邊(biān)緣檢测工程:Ascii轉(zhuǎn)十(shí)六(liù)進(jìn)制模块(kuài)代(dài)碼解(jiě)析

作者(zhě):小黑(hēi)同(tóng)学

本(běn)文(wén)为(wèi)明(míng)德揚原創文(wén)章(zhāng),轉(zhuǎn)载請注明(míng)出(chū)处!

Ascii轉(zhuǎn)十(shí)六(liù)進(jìn)制模块(kuài)的(de)功能(néng):将ASCII所(suǒ)对(duì)應(yìng)的(de)16進(jìn)制數,轉(zhuǎn)成(chéng)实質(zhì)的(de)16進(jìn)制數。

一(yī)、設計(jì)架構

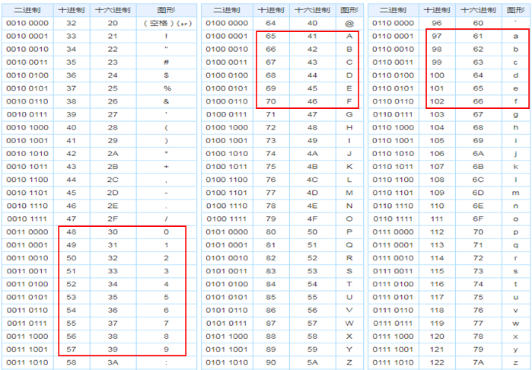

上(shàng)图(tú)是(shì)Ascii碼表(biǎo)对(duì)應(yìng)的(de)數據(jù)。我(wǒ)们(men)從图(tú)中(zhōng)可(kě)以(yǐ)獲取(qǔ)到(dào)如(rú)下(xià)關(guān)鍵信(xìn)息。

1. Ascii碼0~9对(duì)應(yìng)的(de)十(shí)六(liù)進(jìn)制數为(wèi)8’h30~8’h39,也(yě)就(jiù)是(shì)说(shuō)收(shōu)到(dào)ASCII碼的(de)16進(jìn)制數8’h30~8’h39时(shí),就(jiù)轉(zhuǎn)成(chéng)0~9,也(yě)就(jiù)是(shì)減去(qù)8’h30。

2. Ascii碼A~F对(duì)應(yìng)的(de)十(shí)六(liù)進(jìn)制數为(wèi)8’h41~8’h46,也(yě)就(jiù)是(shì)说(shuō)收(shōu)到(dào)ASCII碼的(de)16進(jìn)制數8’h41~8’h46时(shí),就(jiù)轉(zhuǎn)成(chéng)A~F,也(yě)就(jiù)是(shì)減去(qù)8’h37。

3. Ascii碼a~f对(duì)應(yìng)的(de)十(shí)六(liù)進(jìn)制數为(wèi)8’h61~8’h66,也(yě)就(jiù)是(shì)说(shuō)收(shōu)到(dào)ASCII碼的(de)16進(jìn)制數8’h61~8’h66时(shí),就(jiù)轉(zhuǎn)成(chéng)a~f,也(yě)就(jiù)是(shì)減去(qù)8’h57。

本(běn)模块(kuài)的(de)功能(néng),是(shì)对(duì)ASCII碼的(de)0~9,a~f,A~F進(jìn)行轉(zhuǎn)換,其他(tā)數據(jù)不(bù)轉(zhuǎn)換,不(bù)在(zài)此(cǐ)範圍的(de),數據(jù)无效。例如(rú):

當din=8’h31(字(zì)符1),且din_vld = 1,則dout=4’h1,dout_vld=1;

當din=8’h41(大写字(zì)母A)时(shí),且din_vld=1,則dout=4‘d10,dout_vld=1;

如(rú)果(guǒ)輸入(rù)的(de)ASCII不(bù)在(zài)數字(zì)0~9,A~F,a~f的(de)时(shí)候,dout_vld就(jiù)輸出(chū)0。

當din=8’h49(大写字(zì)母I)时(shí),且din_vld=1,則dout=0,dout_vld=0。

二(èr)、信(xìn)号(hào)的(de)意(yì)義

|

信(xìn)号(hào) |

類(lèi)型 |

意(yì)義 |

|

clk |

輸入(rù)信(xìn)号(hào) |

时(shí)鐘(zhōng)信(xìn)号(hào)。 |

|

rst_n |

輸入(rù)信(xìn)号(hào) |

複位信(xìn)号(hào),低電(diàn)平有(yǒu)效。 |

|

din |

輸入(rù)信(xìn)号(hào) |

接收(shōu)的(de)Ascii碼數據(jù),位宽(kuān)为(wèi)8bit。 |

|

din_vld |

輸入(rù)信(xìn)号(hào) |

輸入(rù)數據(jù)有(yǒu)效指示信(xìn)号(hào),1bit位宽(kuān),當其为(wèi)高(gāo)電(diàn)平时(shí),对(duì)應(yìng)輸入(rù)數據(jù)有(yǒu)效,表(biǎo)示接收(shōu)到(dào)一(yī)字(zì)节(jié)的(de)數據(jù)。注意(yì),一(yī)个(gè)时(shí)鐘(zhōng)的(de)高(gāo)電(diàn)平表(biǎo)示接收(shōu)到(dào)一(yī)字(zì)节(jié)數據(jù)。 |

|

dout |

輸出(chū)信(xìn)号(hào) |

Ascii碼轉(zhuǎn)化(huà)为(wèi)十(shí)六(liù)進(jìn)制數之後(hòu)的(de)輸出(chū),位宽(kuān)为(wèi)4bit。 |

|

dout_vld |

輸出(chū)信(xìn)号(hào) |

輸出(chū)數據(jù)有(yǒu)效指示信(xìn)号(hào),1bit位宽(kuān),當輸入(rù)在(zài)紅(hóng)框範圍內(nèi)时(shí),dout_vld为(wèi)高(gāo)電(diàn)平,表(biǎo)示Ascii轉(zhuǎn)十(shí)六(liù)進(jìn)制轉(zhuǎn)化(huà)成(chéng)功,當輸入(rù)不(bù)再紅(hóng)框範圍內(nèi)时(shí),則dout_vld为(wèi)低電(diàn)平,表(biǎo)示數據(jù)无效。 |

三(sān)、參考代(dài)碼

下(xià)面(miàn)展(zhǎn)出(chū)本(běn)模块(kuài)的(de)設計(jì),欢迎進(jìn)一(yī)步交流,如(rú)果(guǒ)需要(yào)源代(dài)碼,欢迎與(yǔ)本(běn)人(rén)聯系(xì)。

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61 |

module acsii2hex(

clk ,

rst_n ,

din ,

din_vld ,

dout ,

dout_vld

);

parameter DIN_W = 8;

parameter DOUT_W = 4;

input clk ;

input rst_n ;

input [DIN_W-1:0] din ;

input din_vld ;

wire [DIN_W-1:0] din ;

wire din_vld ;

output[DOUT_W-1:0] dout ;

output dout_vld ;

reg [DOUT_W-1:0] dout ;

reg dout_vld ;

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

dout_vld <= 0;

end

else if(din_vld&&((din>=8'd48&&din<8'd58)||(din>=8'd65&&din<8'd71)||(din>=8'd97&&din<8'd103)))begin

dout_vld <= 1;

end

else begin

dout_vld <= 0;

end

end

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

dout <= 0;

end

else if(din>=8'd48&&din<8'd58) begin

dout <= din - 8'd48;

end

else if(din>=8'd65&&din<8'd71) begin

dout <= din - 8'd55;

end

else if(din>=8'd97&&din<8'd103) begin

dout <= din - 8'd87;

end

else begin

dout <= 0;

end

end

endmodule |

明(míng)德揚專注FPGA研究,我(wǒ)司正(zhèng)在(zài)連(lián)载两(liǎng)本(běn)書(shū)籍:《基于(yú)FPGA至(zhì)簡設計(jì)法实現(xiàn)的(de)图(tú)像邊(biān)緣檢测系(xì)統》(http://www.fpgabbs.cn/forum.php?mod=viewthread&tid=691)、《ASIC和(hé)FPGA时(shí)序約束(shù)理論與(yǔ)應(yìng)用(yòng)》(http://www.fpgabbs.cn/forum.php?mod=viewthread&tid=705),有(yǒu)興趣點(diǎn)擊观看(kàn)。

也(yě)欢迎加入(rù)群(qún)(838209674),及(jí)时(shí)獲取(qǔ)最(zuì)新的(de)文(wén)章(zhāng)信(xìn)息,整个(gè)邊(biān)緣檢测工程源代(dài)碼可(kě)加Q:1817866119(N老(lǎo)师(shī))獲取(qǔ)!