FPGA(Field-Programmable Gate Array), 即現(xiàn)场可(kě)編程門(mén)阵(zhèn)列,它(tā)是(shì)在(zài)PAL、GAL、CPLD等可(kě)編程器件(jiàn)的(de)基礎上(shàng)進(jìn)一(yī)步發(fà)展(zhǎn)的(de)産物(wù)。它(tā)是(shì)作为(wèi)專用(yòng)集成(chéng)電(diàn)路(lù)(ASIC)領域中(zhōng)的(de)一(yī)種(zhǒng)半定(dìng)制電(diàn)路(lù)而(ér)出(chū)現(xiàn)的(de),既解(jiě)決了(le)定(dìng)制電(diàn)路(lù)的(de)不(bù)足,又克(kè)服(fú)了(le)原有(yǒu)可(kě)編程器件(jiàn)門(mén)電(diàn)路(lù)數有(yǒu)限的(de)缺點(diǎn)

一(yī)、FPGA工作原理

FPGA采用(yòng)了(le)邏輯單元(yuán)阵(zhèn)列LCA(Logic Cell Array)这(zhè)樣(yàng)一(yī)个(gè)概念,內(nèi)部(bù)包(bāo)括 可(kě)配置邏輯模块(kuài)CLB(Configurable Logic Block)、輸出(chū)輸入(rù)模块(kuài)IOB(Input Output Block)和(hé)內(nèi)部(bù)連(lián)線(xiàn)(Interconnect)三(sān)个(gè)部(bù)分(fēn)。 現(xiàn)场可(kě)編程門(mén)阵(zhèn)列(FPGA)是(shì)可(kě)編程器件(jiàn),與(yǔ)傳統邏輯電(diàn)路(lù)和(hé)門(mén)阵(zhèn)列(如(rú)PAL,GAL及(jí)CPLD器件(jiàn))相比,FPGA具有(yǒu)不(bù)同(tóng)的(de)結構。

FPGA利用(yòng)小型查找(zhǎo)表(biǎo)(16×1RAM)来(lái)实現(xiàn)組合邏輯,每个(gè)查找(zhǎo)表(biǎo)連(lián)接到(dào)一(yī)个(gè)D觸發(fà)器的(de)輸入(rù)端,觸發(fà)器再来(lái)驅動(dòng)其他(tā)邏輯電(diàn)路(lù)或(huò)驅動(dòng)I/O,由(yóu)此(cǐ)構成(chéng)了(le)既可(kě)实現(xiàn)組合邏輯功能(néng)又可(kě)实現(xiàn)时(shí)序邏輯功能(néng)的(de)基本(běn)邏輯單元(yuán)模块(kuài),这(zhè)些模块(kuài)間(jiān)利用(yòng)金(jīn)屬連(lián)線(xiàn)互相連(lián)接或(huò)連(lián)接到(dào)I/O模块(kuài)。FPGA的(de)邏輯是(shì)通(tòng)过(guò)向(xiàng)內(nèi)部(bù)静(jìng)态存儲單元(yuán)加载編程數據(jù)来(lái)实現(xiàn)的(de),存儲在(zài)存儲器單元(yuán)中(zhōng)的(de)值決定(dìng)了(le)邏輯單元(yuán)的(de)邏輯功能(néng)以(yǐ)及(jí)各(gè)模块(kuài)之間(jiān)或(huò)模块(kuài)與(yǔ)I/O間(jiān)的(de)聯接方(fāng)式,并最(zuì)終(zhōng)決定(dìng)了(le)FPGA所(suǒ)能(néng)实現(xiàn)的(de)功能(néng),FPGA允许无限次(cì)的(de)編程。

二(èr)、FPGA基本(běn)特(tè)點(diǎn):

1) 采用(yòng)FPGA設計(jì)ASIC電(diàn)路(lù)(專用(yòng)集成(chéng)電(diàn)路(lù)),用(yòng)戶不(bù)需要(yào)投片(piàn)生(shēng)産,就(jiù)能(néng)得到(dào)合用(yòng)的(de)芯片(piàn)。

2) FPGA可(kě)做其它(tā)全(quán)定(dìng)制或(huò)半定(dìng)制ASIC電(diàn)路(lù)的(de)中(zhōng)試樣(yàng)片(piàn)。

3) FPGA內(nèi)部(bù)有(yǒu)豐富的(de)觸發(fà)器和(hé)I/O引脚。

4) FPGA是(shì)ASIC電(diàn)路(lù)中(zhōng)設計(jì)周期(qī)最(zuì)短(duǎn)、開(kāi)發(fà)費用(yòng)最(zuì)低、风险最(zuì)小的(de)器件(jiàn)之一(yī)。

5) FPGA采用(yòng)高(gāo)速CMOS工藝,功耗低,可(kě)以(yǐ)與(yǔ)CMOS、TTL電(diàn)平兼容。

三(sān)、主(zhǔ)要(yào)FPGA生(shēng)産廠(chǎng)商

1) Xilinx 開(kāi)發(fà)平台(tái)是(shì)ISE、Vivado

2) Altera 開(kāi)發(fà)平台(tái)是(shì)Quartus II

3) Actel 開(kāi)發(fà)平台(tái)是(shì)Libero

4) Lattice

5) Atmel

四(sì)、FPGA基礎——編程語(yǔ)言 and 開(kāi)發(fà)工具

1)、熟練掌握硬(yìng)件(jiàn)編程語(yǔ)言-verilog(推薦)

2)、熟練使用(yòng)FPGA的(de)常用(yòng)開(kāi)發(fà)工具

3)、学会(huì)上(shàng)网(wǎng)查資料

4)、多(duō)逛論壇,與(yǔ)他(tā)人(rén)交流

五(wǔ)、推薦FPGA学習論壇

明(míng)德揚FPGA論壇(http://www.fpgabbs.cn/)

六(liù)、國(guó)內(nèi)FPGA課程專業培訓機(jī)構:明(míng)德揚科教http://www.minyingyiyuan.com/

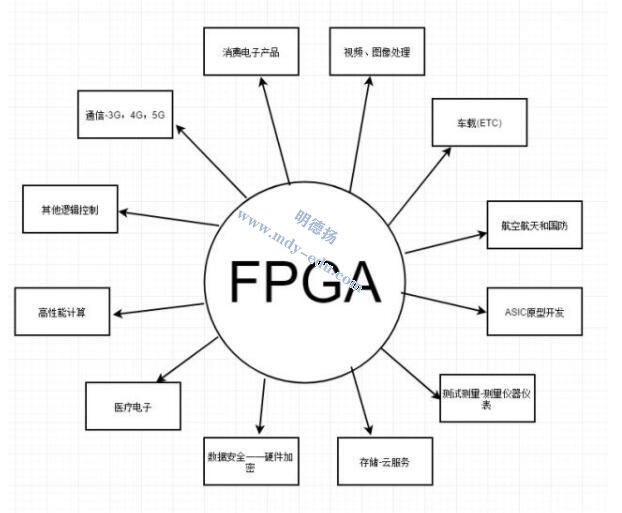

七(qī)、FPGA的(de)應(yìng)用(yòng)領域

當前(qián)FPGA的(de)最(zuì)火的(de)應(yìng)用(yòng)是(shì)FPGA雲(yún)服(fú)务器,人(rén)工智能(néng),雲(yún)計(jì)算,航空航天(tiān),數字(zì)信(xìn)号(hào)处理,图(tú)像处理,AI,機(jī)器学習,通(tòng)信(xìn)(3G、4G、5G)等。