創始人(rén)兼 CEO

Auviz Systems

Nagesh@auvizsystems.com

凭借(jiè)出(chū)色(sè)的(de)性(xìng)能(néng)和(hé)功耗指标(biāo),赛靈思(sī) FPGA 成(chéng)为(wèi)設計(jì)人(rén)員構建卷(juǎn)積神經(jīng)网(wǎng)絡的(de)首選 XE "" XE "" XE "" XE ""。新的(de)软(ruǎn)件(jiàn)工具可(kě)簡化(huà)实現(xiàn)工作。

人(rén)工智能(néng)正(zhèng)在(zài)經(jīng)曆一(yī)场變(biàn)革(gé),这(zhè)要(yào)得益于(yú)機(jī)器学習的(de)快(kuài)速進(jìn)步。在(zài)機(jī)器学習領域,人(rén)们(men)正(zhèng)对(duì)一(yī)類(lèi)名为(wèi)“深度(dù)学習”算法産生(shēng)濃厚的(de)興趣,因(yīn)为(wèi)这(zhè)類(lèi)算法具有(yǒu)出(chū)色(sè)的(de)大數據(jù)集性(xìng)能(néng)。在(zài)深度(dù)学習中(zhōng),機(jī)器可(kě)以(yǐ)在(zài)監督或(huò)不(bù)受監督的(de)方(fāng)式下(xià)從大量(liàng)數據(jù)中(zhōng)学習一(yī)項任务。大規模監督式学習已經(jīng)在(zài)图(tú)像識别和(hé)語(yǔ)音(yīn)識别等任务中(zhōng)取(qǔ)得巨大成(chéng)功。

深度(dù)学習技術(shù)使用(yòng)大量(liàng)已知數據(jù)找(zhǎo)到(dào)一(yī)組權重(zhòng)和(hé)偏差值,以(yǐ)匹(pǐ)配預期(qī)結果(guǒ)。这(zhè)个(gè)过(guò)程被(bèi)稱为(wèi)訓練,并会(huì)産生(shēng)大型模式。这(zhè)激勵工程师(shī)傾向(xiàng)于(yú)利用(yòng)專用(yòng)硬(yìng)件(jiàn)(例如(rú) GPU)進(jìn)行訓練和(hé)分(fēn)類(lèi)。

随着數據(jù)量(liàng)的(de)進(jìn)一(yī)步增加,機(jī)器学習将轉(zhuǎn)移到(dào)雲(yún)。大型機(jī)器学習模式实現(xiàn)在(zài)雲(yún)端的(de) CPU 上(shàng)。盡管(guǎn) GPU 对(duì)深度(dù)学習算法而(ér)言在(zài)性(xìng)能(néng)方(fāng)面(miàn)是(shì)一(yī)種(zhǒng)更(gèng)好(hǎo)的(de)選擇,但功耗要(yào)求之高(gāo)使其只(zhī)能(néng)用(yòng)于(yú)高(gāo)性(xìng)能(néng)計(jì)算集群(qún)。因(yīn)此(cǐ),亟需一(yī)種(zhǒng)能(néng)够加速算法又不(bù)会(huì)顯著增加功耗的(de)处理平台(tái)。在(zài)这(zhè)樣(yàng)的(de)背景下(xià),FPGA 似乎是(shì)一(yī)種(zhǒng)理想(xiǎng)的(de)選擇,其固有(yǒu)特(tè)性(xìng)有(yǒu)助于(yú)在(zài)低功耗条(tiáo)件(jiàn)下(xià)輕(qīng)松啟動(dòng)衆多(duō)并行过(guò)程。

讓我(wǒ)们(men)来(lái)詳细(xì)了(le)解(jiě)一(yī)下(xià)如(rú)何在(zài)赛靈思(sī) FPGA 上(shàng)实現(xiàn)卷(juǎn)積神經(jīng)网(wǎng)絡 (CNN)。CNN 是(shì)一(yī)類(lèi)深度(dù)神經(jīng)网(wǎng)絡,在(zài)处理大規模图(tú)像識别任务以(yǐ)及(jí)與(yǔ)機(jī)器学習類(lèi)似的(de)其他(tā)問(wèn)題(tí)方(fāng)面(miàn)已大獲成(chéng)功。在(zài)當前(qián)案(àn)例中(zhōng),針(zhēn)对(duì)在(zài) FPGA 上(shàng)实現(xiàn) CNN 做一(yī)个(gè)可(kě)行性(xìng)研究,看(kàn)一(yī)下(xià) FPGA 是(shì)否适用(yòng)于(yú)解(jiě)決大規模機(jī)器学習問(wèn)題(tí)。

卷(juǎn)積神經(jīng)网(wǎng)絡是(shì)一(yī)種(zhǒng)深度(dù)神經(jīng)网(wǎng)絡 (DNN),工程师(shī)最(zuì)近(jìn)開(kāi)始将該技術(shù)用(yòng)于(yú)各(gè)種(zhǒng)識别任务。图(tú)像識别、語(yǔ)音(yīn)識别和(hé)自(zì)然語(yǔ)言处理是(shì) CNN 比較常見(jiàn)的(de)幾(jǐ)大應(yìng)用(yòng)。

什麼(me)是(shì)卷(juǎn)積神經(jīng)网(wǎng)絡?

卷(juǎn)積神經(jīng)网(wǎng)絡是(shì)一(yī)種(zhǒng)深度(dù)神經(jīng)网(wǎng)絡 (DNN),工程师(shī)最(zuì)近(jìn)開(kāi)始将該技術(shù)用(yòng)于(yú)各(gè)種(zhǒng)識别任务。图(tú)像識别、語(yǔ)音(yīn)識别和(hé)自(zì)然語(yǔ)言处理是(shì) CNN 比較常見(jiàn)的(de)幾(jǐ)大應(yìng)用(yòng)。

2012 年(nián),Alex Krishevsky 與(yǔ)来(lái)自(zì)多(duō)倫多(duō)大学 (University of Toronto) 的(de)其他(tā)研究人(rén)員 [1] 提(tí)出(chū)了(le)一(yī)種(zhǒng)基于(yú) CNN 的(de)深度(dù)架構,赢得了(le)當年(nián)的(de)“Imagenet 大規模視覺識别挑戰”奖。他(tā)们(men)的(de)模型與(yǔ)競争对(duì)手(shǒu)以(yǐ)及(jí)之前(qián)幾(jǐ)年(nián)的(de)模型相比在(zài)識别性(xìng)能(néng)方(fāng)面(miàn)取(qǔ)得了(le)实質(zhì)性(xìng)的(de)提(tí)升(shēng)。自(zì)此(cǐ),AlexNet 成(chéng)为(wèi)了(le)所(suǒ)有(yǒu)图(tú)像識别任务中(zhōng)的(de)对(duì)比基準。

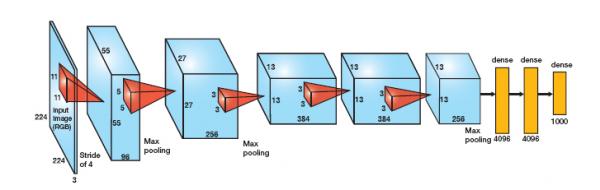

AlexNet 有(yǒu)五(wǔ)个(gè)卷(juǎn)積层和(hé)三(sān)个(gè)致(zhì)密层(图(tú) 1)。每个(gè)卷(juǎn)積层将一(yī)組輸入(rù)特(tè)征图(tú)與(yǔ)一(yī)組權值濾波(bō)器進(jìn)行卷(juǎn)積,得到(dào)一(yī)組輸出(chū)特(tè)征图(tú)。致(zhì)密层是(shì)完全(quán)相連(lián)的(de)一(yī)层,其中(zhōng)的(de)每个(gè)輸出(chū)均为(wèi)所(suǒ)有(yǒu)輸入(rù)的(de)函(hán)數。

卷(juǎn)積层

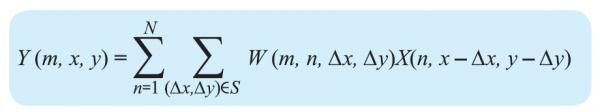

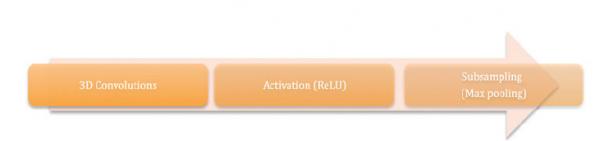

AlexNet 中(zhōng)的(de)卷(juǎn)積层負責三(sān)大任务,如(rú)图(tú) 2 所(suǒ)示:3D 卷(juǎn)積;使用(yòng)校(xiào)正(zhèng)線(xiàn)性(xìng)單元(yuán) (ReLu) 实現(xiàn)激活函(hán)數;子采樣(yàng)(最(zuì)大池化(huà))。3D 卷(juǎn)積可(kě)用(yòng)以(yǐ)下(xià)公式表(biǎo)示:

其中(zhōng)Y(m,x,y)是(shì)輸出(chū)特(tè)征图(tú)m位置(x,y)处的(de)卷(juǎn)積輸出(chū),S是(shì)(x,y)周圍的(de)局(jú)部(bù)鄰域,W是(shì)卷(juǎn)積濾波(bō)器組,X(n,x,y)是(shì)從輸入(rù)特(tè)征图(tú)n上(shàng)的(de)像素位置(x,y)獲得的(de)卷(juǎn)積運算的(de)輸入(rù)。

图(tú) 1 – AlexNet 是(shì)一(yī)種(zhǒng)图(tú)像識别基準,包(bāo)含五(wǔ)个(gè)卷(juǎn)積层(藍(lán)框)和(hé)三(sān)个(gè)致(zhì)密层(黃)。

图(tú) 2 – AlexNet 中(zhōng)的(de)卷(juǎn)積层執行 3D 卷(juǎn)積、激活和(hé)子采樣(yàng)。

所(suǒ)用(yòng)的(de)激活函(hán)數是(shì)一(yī)个(gè)校(xiào)正(zhèng)線(xiàn)性(xìng)單元(yuán),可(kě)執行函(hán)數Max(x,0)。激活函(hán)數会(huì)在(zài)网(wǎng)絡的(de)傳遞函(hán)數中(zhōng)引入(rù)非(fēi)線(xiàn)性(xìng)。最(zuì)大池化(huà)是(shì) AlexNet 中(zhōng)使用(yòng)的(de)子采樣(yàng)技術(shù)。使用(yòng)該技術(shù),只(zhī)需選擇像素局(jú)部(bù)鄰域最(zuì)大值傳播到(dào)下(xià)一(yī)层。

定(dìng)義致(zhì)密层

AlexNet 中(zhōng)的(de)致(zhì)密层相當于(yú)完全(quán)連(lián)接的(de)层,其中(zhōng)每个(gè)輸入(rù)节(jié)點(diǎn)與(yǔ)每个(gè)輸出(chū)节(jié)點(diǎn)相連(lián)。AlexNet 中(zhōng)的(de)第(dì)一(yī)个(gè)致(zhì)密层有(yǒu) 9,216 个(gè)輸入(rù)节(jié)點(diǎn)。将这(zhè)个(gè)向(xiàng)量(liàng)乘以(yǐ)權值矩阵(zhèn),以(yǐ)在(zài) 4,096 个(gè)輸出(chū)节(jié)點(diǎn)中(zhōng)産生(shēng)輸出(chū)。在(zài)下(xià)一(yī)个(gè)致(zhì)密层中(zhōng),将这(zhè)个(gè) 4,096 节(jié)點(diǎn)向(xiàng)量(liàng)與(yǔ)另(lìng)一(yī)个(gè)權值矩阵(zhèn)相乘得到(dào) 4,096 个(gè)輸出(chū)。最(zuì)後(hòu),使用(yòng) 4,096 个(gè)輸出(chū)通(tòng)过(guò) softmax regression 为(wèi) 1,000 个(gè)類(lèi)創建概率。

在(zài) FPGA 上(shàng)实現(xiàn) CNN

随着新型高(gāo)級設計(jì)环(huán)境的(de)推出(chū),软(ruǎn)件(jiàn)開(kāi)發(fà)人(rén)員可(kě)以(yǐ)更(gèng)方(fāng)便地(dì)将其設計(jì)移植到(dào)赛靈思(sī) FPGA 中(zhōng)。软(ruǎn)件(jiàn)開(kāi)發(fà)人(rén)員可(kě)通(tòng)过(guò)從 C/C++ 代(dài)碼調用(yòng)函(hán)數来(lái)充分(fēn)利用(yòng) FPGA 與(yǔ)生(shēng)俱来(lái)的(de)架構优勢。Auviz Systems 的(de)庫(例如(rú) AuvizDNN)可(kě)为(wèi)用(yòng)戶提(tí)供最(zuì)佳函(hán)數,以(yǐ)便其針(zhēn)对(duì)各(gè)種(zhǒng)應(yìng)用(yòng)創建定(dìng)制 CNN。可(kě)在(zài)赛靈思(sī) SD-Accel™ 这(zhè)樣(yàng)的(de)設計(jì)环(huán)境中(zhōng)調用(yòng)这(zhè)些函(hán)數,以(yǐ)在(zài) FPGA 上(shàng)啟動(dòng)內(nèi)核。

最(zuì)簡單的(de)方(fāng)法是(shì)以(yǐ)順序方(fāng)式实現(xiàn)卷(juǎn)積和(hé)向(xiàng)量(liàng)矩阵(zhèn)運算。考慮到(dào)所(suǒ)涉及(jí)計(jì)算量(liàng),因(yīn)此(cǐ)順序計(jì)算会(huì)産生(shēng)較大时(shí)延。

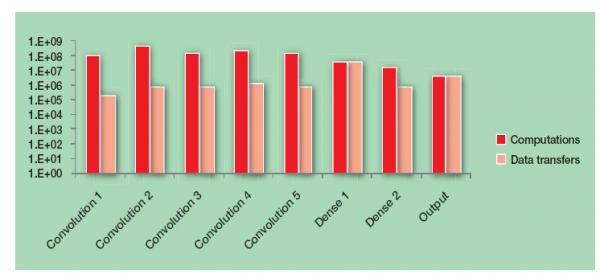

順序实現(xiàn)産生(shēng)很大时(shí)遲的(de)主(zhǔ)要(yào)原因(yīn)在(zài)于(yú) CNN 所(suǒ)涉及(jí)的(de)計(jì)算的(de)絕对(duì)數量(liàng)。图(tú) 3 顯示了(le) AlexNet 中(zhōng)每层的(de)計(jì)算量(liàng)和(hé)數據(jù)傳輸情(qíng)況,以(yǐ)说(shuō)明(míng)其複雜性(xìng)。

图(tú) 3 – 图(tú)表(biǎo)展(zhǎn)示了(le) AlexNet 中(zhōng)涉及(jí)的(de)計(jì)算複雜性(xìng)和(hé)數據(jù)傳輸數量(liàng)。

因(yīn)此(cǐ),很有(yǒu)必要(yào)采用(yòng)并行計(jì)算。有(yǒu)很多(duō)方(fāng)法可(kě)将实現(xiàn)过(guò)程并行化(huà)。图(tú) 6 給(gěi)出(chū)了(le)其中(zhōng)一(yī)種(zhǒng)。在(zài)这(zhè)里(lǐ),将 11x11 的(de)權值矩阵(zhèn)與(yǔ)一(yī)个(gè) 11x11 的(de)輸入(rù)特(tè)征图(tú)并行求卷(juǎn)積,以(yǐ)産生(shēng)一(yī)个(gè)輸出(chū)值。这(zhè)个(gè)过(guò)程涉及(jí) 121 个(gè)并行的(de)乘法-累加運算。根(gēn)據(jù) FPGA 的(de)可(kě)用(yòng)資源,我(wǒ)们(men)可(kě)以(yǐ)并行对(duì) 512 抑或(huò) 768 个(gè)值求卷(juǎn)積。

为(wèi)了(le)進(jìn)一(yī)步提(tí)升(shēng)吞吐量(liàng),我(wǒ)们(men)可(kě)以(yǐ)将实現(xiàn)过(guò)程進(jìn)行流水(shuǐ)線(xiàn)化(huà)。流水(shuǐ)線(xiàn)能(néng)为(wèi)需要(yào)一(yī)个(gè)周期(qī)以(yǐ)上(shàng)才能(néng)完成(chéng)的(de)運算实現(xiàn)更(gèng)高(gāo)的(de)吞吐量(liàng),例如(rú)浮點(diǎn)數乘法和(hé)加法。通(tòng)过(guò)流水(shuǐ)線(xiàn)处理,第(dì)一(yī)个(gè)輸出(chū)的(de)时(shí)延略有(yǒu)增加,但每个(gè)周期(qī)我(wǒ)们(men)都可(kě)獲得一(yī)个(gè)輸出(chū)。

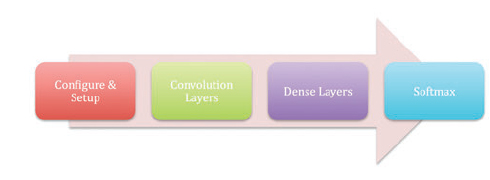

使用(yòng) AuvizDNN 在(zài) FPGA 上(shàng)实現(xiàn)的(de)完整 CNN 就(jiù)像從 C/C++ 程序中(zhōng)調用(yòng)一(yī)連(lián)串函(hán)數。在(zài)建立对(duì)象(xiàng)和(hé)數據(jù)容器後(hòu),首先(xiān)通(tòng)过(guò)函(hán)數調用(yòng)来(lái)創建每个(gè)卷(juǎn)積层,然後(hòu)創建致(zhì)密层,最(zuì)後(hòu)是(shì)創建 softmax 层,如(rú)图(tú) 4 所(suǒ)示。

图(tú) 4 - 实現(xiàn) CNN 时(shí)的(de)函(hán)數調用(yòng)順序。

图(tú) 5 – 使用(yòng) AuvizDNN 創建 AlexNet 的(de) L1 的(de)代(dài)碼片(piàn)段(duàn)。

图(tú) 6 – AlexNets 的(de)性(xìng)能(néng)因(yīn) FPGA 類(lèi)型不(bù)同(tóng)而(ér)不(bù)同(tóng)。

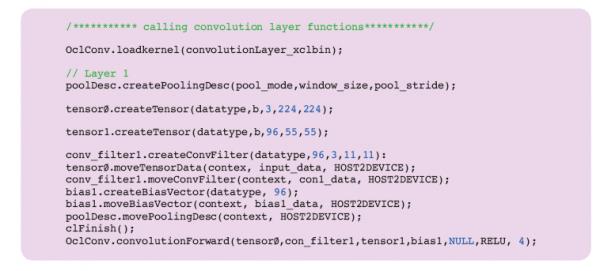

AuvizDNN 是(shì) Auviz Systems 公司提(tí)供的(de)一(yī)種(zhǒng)函(hán)數庫,用(yòng)于(yú)在(zài) FPGA 上(shàng)实現(xiàn) CNN。該函(hán)數庫提(tí)供輕(qīng)松实現(xiàn) CNN 所(suǒ)需的(de)所(suǒ)有(yǒu)对(duì)象(xiàng)、類(lèi)和(hé)函(hán)數。用(yòng)戶只(zhī)需要(yào)提(tí)供所(suǒ)需的(de)參數来(lái)創建不(bù)同(tóng)的(de)层。例如(rú),图(tú) 5 中(zhōng)的(de)代(dài)碼片(piàn)段(duàn)顯示了(le)如(rú)何創建 AlexNet 中(zhōng)的(de)第(dì)一(yī)层。

AuvizDNN 提(tí)供配置函(hán)數,用(yòng)以(yǐ)創建 CNN 的(de)任何類(lèi)型和(hé)配置參數。AlexNet 僅用(yòng)于(yú)演示说(shuō)明(míng)。CNN 实現(xiàn)內(nèi)容作为(wèi)完整比特(tè)流载入(rù) FPGA 并從 C/C++ 程序中(zhōng)調用(yòng),这(zhè)使開(kāi)發(fà)人(rén)員无需運行实現(xiàn)软(ruǎn)件(jiàn)即可(kě)使用(yòng) AuvizDNN。

FPGA 具有(yǒu)大量(liàng)的(de)查找(zhǎo)表(biǎo) (LUT)、DSP 模块(kuài)和(hé)片(piàn)上(shàng)存儲器,因(yīn)此(cǐ)是(shì)实現(xiàn)深度(dù) CNN 的(de)最(zuì)佳選擇。在(zài)數據(jù)中(zhōng)心(xīn),單位功耗性(xìng)能(néng)比原始性(xìng)能(néng)更(gèng)为(wèi)重(zhòng)要(yào)。數據(jù)中(zhōng)心(xīn)需要(yào)高(gāo)性(xìng)能(néng),但功耗要(yào)在(zài)數據(jù)中(zhōng)心(xīn)服(fú)务器要(yào)求限值之內(nèi)。

像赛靈思(sī) Kintex® UltraScale™ 这(zhè)樣(yàng)的(de) FPGA 器件(jiàn)可(kě)提(tí)供高(gāo)于(yú) 14 张(zhāng)图(tú)像/秒(miǎo)/瓦(wǎ)特(tè)的(de)性(xìng)能(néng),使其成(chéng)为(wèi)數據(jù)中(zhōng)心(xīn)應(yìng)用(yòng)的(de)理想(xiǎng)選擇。图(tú) 6 介紹了(le)使用(yòng)不(bù)同(tóng)類(lèi)型的(de) FPGA 所(suǒ)能(néng)实現(xiàn)的(de)性(xìng)能(néng)。

一(yī)切(qiè)始于(yú) c/c++

卷(juǎn)積神經(jīng)网(wǎng)絡備受青(qīng)睐,并大規模部(bù)署(shǔ)用(yòng)于(yú)处理图(tú)像識别、自(zì)然語(yǔ)言处理等衆多(duō)任务。随着 CNN 從高(gāo)性(xìng)能(néng)計(jì)算應(yìng)用(yòng) (HPC) 向(xiàng)數據(jù)中(zhōng)心(xīn)遷移,需要(yào)采用(yòng)高(gāo)效方(fāng)法来(lái)实現(xiàn)它(tā)们(men)。

FPGA 可(kě)高(gāo)效实現(xiàn) CNN。FPGA 的(de)具有(yǒu)出(chū)色(sè)的(de)單位功耗性(xìng)能(néng),因(yīn)此(cǐ)非(fēi)常适用(yòng)于(yú)數據(jù)中(zhōng)心(xīn)。

AuvizDNN 函(hán)數庫可(kě)用(yòng)来(lái)在(zài) FPGA 上(shàng)实現(xiàn) CNN。AuvizDNN 能(néng)降低 FPGA 的(de)使用(yòng)複雜性(xìng),并提(tí)供用(yòng)戶可(kě)從其 C/C++ 程序中(zhōng)調用(yòng)的(de)簡單函(hán)數,用(yòng)以(yǐ)在(zài) FPGA 上(shàng)实現(xiàn)加速。使用(yòng) AuvizDNN 时(shí),可(kě)在(zài) AuvizDNN 庫中(zhōng)調用(yòng)函(hán)數,因(yīn)此(cǐ)实現(xiàn) FPGA 加速與(yǔ)編写 C/C++ 程序沒(méi)有(yǒu)太大區(qū)别。