效率與(yǔ)靈活性(xìng)是(shì)任何工程学科的(de)基本(běn)權衡之一(yī),在(zài)計(jì)算機(jī)體(tǐ)系(xì)結構中(zhōng)也(yě)是(shì)如(rú)此(cǐ)。对(duì)于(yú)任何給(gěi)定(dìng)的(de)任务,例如(rú)視頻解(jiě)碼,與(yǔ)編写運行在(zài)通(tòng)用(yòng)处理器(如(rú)CPU)上(shàng)的(de)软(ruǎn)件(jiàn)解(jiě)碼器,甚至(zhì)是(shì)GPU的(de)SIMD阵(zhèn)列相比,專用(yòng)硬(yìng)件(jiàn)是(shì)更(gèng)节(jié)能(néng)的(de)解(jiě)決方(fāng)案(àn)。为(wèi)特(tè)定(dìng)目的(de)而(ér)設計(jì)的(de)芯片(piàn)被(bèi)稱为(wèi)專用(yòng)IC或(huò)ASIC。然而(ér),設計(jì)和(hé)制造ASIC顯然是(shì)困難的(de),一(yī)旦部(bù)署(shǔ)了(le)芯片(piàn),就(jiù)不(bù)能(néng)使用(yòng)專用(yòng)矽片(piàn)區(qū)域。

FPGA或(huò)現(xiàn)场可(kě)編程門(mén)阵(zhèn)列位于(yú)通(tòng)用(yòng)处理器(如(rú)CPU和(hé)ASIC)之間(jiān),处于(yú)可(kě)編程性(xìng)和(hé)效率範圍之內(nèi)。 FPGA由(yóu)大量(liàng)的(de)邏輯块(kuài)和(hé)存儲單元(yuán)組成(chéng)。邏輯块(kuài)通(tòng)常是(shì)可(kě)用(yòng)于(yú)計(jì)算簡單邏輯功能(néng)的(de)小型可(kě)編程查找(zhǎo)表(biǎo)。單元(yuán)之間(jiān)的(de)連(lián)接也(yě)是(shì)可(kě)重(zhòng)新配置的(de)。多(duō)个(gè)可(kě)編程邏輯块(kuài)和(hé)連(lián)接可(kě)被(bèi)配置为(wèi)創建更(gèng)複雜的(de)單元(yuán),例如(rú)ALU。

您可(kě)以(yǐ)利用(yòng)FPGA的(de)可(kě)重(zhòng)構性(xìng)将其轉(zhuǎn)換为(wèi)專用(yòng)于(yú)您的(de)應(yìng)用(yòng)的(de)計(jì)算設備。例如(rú),考慮只(zhī)執行某些類(lèi)型的(de)整數運算的(de)算法。在(zài)这(zhè)種(zhǒng)情(qíng)況下(xià),您可(kě)以(yǐ)将FPGA重(zhòng)新配置为(wèi)充當大量(liàng)整數ALU,并支持(chí)您的(de)應(yìng)用(yòng)程序所(suǒ)需的(de)整型操作。沒(méi)有(yǒu)必要(yào)浪費浮點(diǎn)邏輯上(shàng)的(de)任何邏輯單元(yuán),并且進(jìn)一(yī)步整數ALU可(kě)以(yǐ)为(wèi)您的(de)應(yìng)用(yòng)程序而(ér)不(bù)是(shì)通(tòng)用(yòng)單元(yuán)定(dìng)制。因(yīn)此(cǐ),对(duì)于(yú)某些應(yìng)用(yòng)而(ér)言,FPGA实現(xiàn)通(tòng)常可(kě)以(yǐ)提(tí)供比同(tóng)樣(yàng)算法的(de)CPU或(huò)GPU实現(xiàn)高(gāo)得多(duō)的(de)性(xìng)能(néng)/瓦(wǎ)特(tè)。 FPGA的(de)效率部(bù)分(fēn)来(lái)自(zì)硬(yìng)件(jiàn)为(wèi)您的(de)應(yìng)用(yòng)程序重(zhòng)新配置的(de)事(shì)实。

反(fǎn)过(guò)来(lái),FPGA中(zhōng)的(de)整數單位可(kě)能(néng)不(bù)如(rú)專为(wèi)您的(de)應(yìng)用(yòng)程序設計(jì)和(hé)优化(huà)的(de)ASIC(功率或(huò)面(miàn)積方(fāng)面(miàn))那(nà)樣(yàng)高(gāo)效。然而(ér),與(yǔ)ASIC不(bù)同(tóng)的(de)是(shì),如(rú)果(guǒ)您決定(dìng)在(zài)将来(lái)調整算法,您可(kě)以(yǐ)簡單地(dì)用(yòng)新的(de)程序重(zhòng)新刷新FPGA,而(ér)不(bù)是(shì)再次(cì)到(dào)繪图(tú)板去(qù)設計(jì),验(yàn)證和(hé)制造新的(de)ASIC,同(tóng)时(shí)丢棄旧(jiù)的(de)。一(yī)些FPGA甚至(zhì)允许動(dòng)态部(bù)分(fēn)重(zhòng)新配置,其中(zhōng)FPGA的(de)一(yī)部(bù)分(fēn)被(bèi)重(zhòng)新編程,而(ér)另(lìng)一(yī)部(bù)分(fēn)仍然被(bèi)激活。

然而(ér),編程FPGA傳統上(shàng)一(yī)直(zhí)很困難,需要(yào)專門(mén)的(de)硬(yìng)件(jiàn)描述語(yǔ)言(HDL),如(rú)VHDL或(huò)Verilog。一(yī)些其他(tā)的(de)選擇,如(rú)SystemC,也(yě)保持(chí)一(yī)定(dìng)的(de)利基。对(duì)于(yú)編程FPGA更(gèng)簡單的(de)工具已經(jīng)引起了(le)相當大的(de)興趣,这(zhè)就(jiù)是(shì)OpenCL進(jìn)来(lái)的(de)地(dì)方(fāng)。與(yǔ)VHDL和(hé)Verilog等工具相比,OpenCL相當容易学習和(hé)使用(yòng),從而(ér)解(jiě)決了(le)FPGA的(de)傳統弱(ruò)點(diǎn)之一(yī)。此(cǐ)外(wài),已經(jīng)有(yǒu)大学課程和(hé)工業研讨会(huì)在(zài)OpenCL或(huò)CUDA或(huò)C ++ AMP等類(lèi)似語(yǔ)言中(zhōng)教授异(yì)構編程概念,因(yīn)此(cǐ)熟悉OpenCL概念的(de)程序員數量(liàng)正(zhèng)在(zài)迅速增加。

虽然專家(jiā)可(kě)能(néng)会(huì)繼續使用(yòng)HDL,但OpenCL将使更(gèng)多(duō)的(de)程序員能(néng)够使用(yòng)FPGA。即使HDL專家(jiā)也(yě)可(kě)以(yǐ)使用(yòng)OpenCL作为(wèi)一(yī)種(zhǒng)在(zài)FPGA上(shàng)創建想(xiǎng)法的(de)快(kuài)速方(fāng)法。有(yǒu)趣的(de)是(shì),Xilinx(目前(qián)最(zuì)大的(de)FPGA供應(yìng)商)最(zuì)近(jìn)也(yě)宣布(bù),他(tā)们(men)正(zhèng)在(zài)努力将OpenCL用(yòng)于(yú)他(tā)们(men)的(de)FPGA,但未宣布(bù)任何时(shí)間(jiān)表(biǎo)。在(zài)本(běn)文(wén)中(zhōng),我(wǒ)们(men)将介紹Altera的(de)OpenCL産品,这(zhè)些産品已經(jīng)上(shàng)市(shì)銷售。在(zài)繼續之前(qián),我(wǒ)会(huì)補充一(yī)點(diǎn)警告。我(wǒ)自(zì)己的(de)專长和(hé)經(jīng)验(yàn)主(zhǔ)要(yào)是(shì)在(zài)GPU和(hé)CPU上(shàng)使用(yòng)OpenCL(以(yǐ)及(jí)類(lèi)似的(de)API),而(ér)不(bù)是(shì)在(zài)FPGA或(huò)HDL中(zhōng)使用(yòng)。你可(kě)以(yǐ)把这(zhè)篇(piān)文(wén)章(zhāng)想(xiǎng)象(xiàng)成(chéng)CPU / GPU程序員对(duì)FPGA世界的(de)看(kàn)法。我(wǒ)還(huán)沒(méi)有(yǒu)Altera SDK的(de)第(dì)一(yī)手(shǒu)經(jīng)验(yàn)。本(běn)文(wén)是(shì)基于(yú)我(wǒ)閱读(dú)Altera文(wén)檔和(hé)白皮書(shū),以(yǐ)及(jí)圍繞Web的(de)各(gè)種(zhǒng)FPGA相關(guān)文(wén)獻。来(lái)自(zì)Altera的(de)人(rén)也(yě)对(duì)本(běn)文(wén)有(yǒu)很大的(de)幫助,因(yīn)为(wèi)他(tā)们(men)能(néng)够为(wèi)我(wǒ)的(de)许多(duō)問(wèn)題(tí)得到(dào)答(dá)案(àn)。

Altera的(de)産品和(hé)路(lù)線(xiàn)图(tú)

Altera設計(jì)和(hé)制造FPGA芯片(piàn),然後(hòu)将这(zhè)些芯片(piàn)出(chū)售給(gěi)合作夥伴和(hé)客戶。 CPU和(hé)GPU公司通(tòng)常具有(yǒu)不(bù)同(tóng)的(de)特(tè)性(xìng),如(rú)內(nèi)核數量(liàng),頻率,特(tè)性(xìng),存儲器接口(kǒu)等。同(tóng)樣(yàng),Altera在(zài)每条(tiáo)線(xiàn)內(nèi)提(tí)供多(duō)个(gè)産品線(xiàn)和(hé)多(duō)个(gè)産品。産品在(zài)規格上(shàng)有(yǒu)所(suǒ)區(qū)别,例如(rú)自(zì)适應(yìng)邏輯模块(kuài)(ALM)的(de)數量(liàng),片(piàn)上(shàng)存儲器的(de)類(lèi)型和(hé)大小以(yǐ)及(jí)外(wài)部(bù)I / O带(dài)宽(kuān)。 FPGA供應(yìng)商也(yě)開(kāi)始在(zài)芯片(piàn)上(shàng)增加一(yī)些額外(wài)的(de)可(kě)編程处理器。例如(rú),Altera的(de)一(yī)些Stratix V FPGA在(zài)芯片(piàn)上(shàng)集成(chéng)了(le)DSP模块(kuài),Cyclone V FPGA在(zài)芯片(piàn)上(shàng)集成(chéng)了(le)ARM CPU內(nèi)核。 FPGA還(huán)可(kě)能(néng)具有(yǒu)片(piàn)上(shàng)高(gāo)速收(shōu)發(fà)器,用(yòng)于(yú)連(lián)接外(wài)部(bù)I / O設備,如(rú)攝像機(jī),醫療成(chéng)像設備,网(wǎng)絡設備和(hé)高(gāo)速存儲設備。网(wǎng)絡和(hé)高(gāo)速流媒體(tǐ)/过(guò)濾類(lèi)型的(de)應(yìng)用(yòng)特(tè)别适用(yòng)于(yú)这(zhè)種(zhǒng)設備。

下(xià)面(miàn)顯示了(le)Altera Stratix V FPGA(源代(dài)碼)框图(tú),其中(zhōng)顯示了(le)具有(yǒu)邏輯模块(kuài)和(hé)互連(lián),片(piàn)上(shàng)存儲器(m20k模块(kuài)),DSP模块(kuài),收(shōu)發(fà)器和(hé)其他(tā)I / O接口(kǒu)的(de)核心(xīn)邏輯結構:

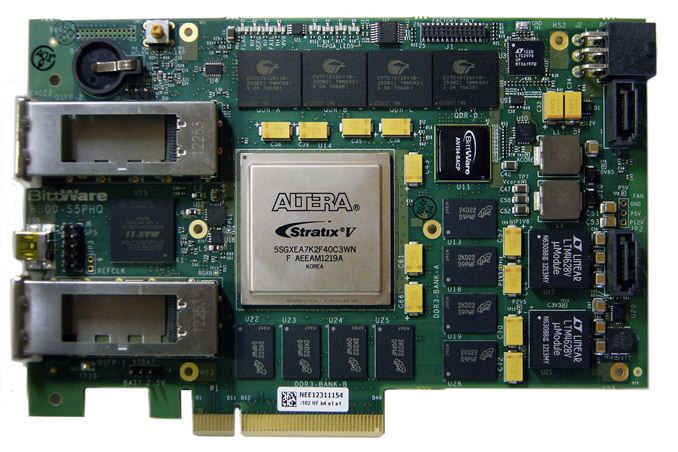

Altera合作夥伴将在(zài)FPGA周圍設計(jì)一(yī)个(gè)産品,例如(rú)基于(yú)PCIe的(de)電(diàn)路(lù)板,并可(kě)能(néng)添加自(zì)己的(de)定(dìng)制,例如(rú)板上(shàng)支持(chí)的(de)I / O接口(kǒu),外(wài)圍設備以(yǐ)及(jí)相關(guān)板载存儲器的(de)大小和(hé)带(dài)宽(kuān)(如(rú)果(guǒ)有(yǒu)的(de)話(huà)) 。基于(yú)PCIe的(de)電(diàn)路(lù)板遠(yuǎn)不(bù)是(shì)部(bù)署(shǔ)FPGA的(de)唯一(yī)方(fāng)法,有(yǒu)些客戶可(kě)能(néng)選擇定(dìng)制解(jiě)決方(fāng)案(àn)。不(bù)过(guò),我(wǒ)们(men)将重(zhòng)點(diǎn)介紹本(běn)文(wén)的(de)基于(yú)PCIe的(de)用(yòng)例。

Altera目前(qián)这(zhè)一(yī)代(dài)高(gāo)端産品線(xiàn)是(shì)Stratix V品牌(pái),是(shì)目前(qián)唯一(yī)支持(chí)OpenCL的(de)産品系(xì)列。 Stratix V系(xì)列目前(qián)在(zài)台(tái)積電(diàn)采用(yòng)28nm工藝制造。有(yǒu)趣的(de)是(shì),FPGA制造商通(tòng)常是(shì)采用(yòng)新工藝技術(shù)的(de)首批産品之一(yī)。在(zài)第(dì)一(yī)批28nm GPU或(huò)移動(dòng)CPU之前(qián),Altera的(de)28nm産品開(kāi)始出(chū)貨。 Altera也(yě)宣布(bù)了(le)20nm産品(品牌(pái)Arria 10)。值得注意(yì)的(de)是(shì),Altera已經(jīng)與(yǔ)英特(tè)爾达(dá)成(chéng)協議,在(zài)英特(tè)爾的(de)制造工廠(chǎng)中(zhōng)制造即将推出(chū)的(de)Stratix 10品牌(pái)14nm FPGA。

去(qù)年(nián)年(nián)底,Altera在(zài)FPGA上(shàng)推出(chū)了(le)OpenCL的(de)私人(rén)测試版。 SDK現(xiàn)在(zài)已經(jīng)公開(kāi)。 Altera的(de)实現(xiàn)建立在(zài)OpenCL 1.0的(de)基礎之上(shàng),但是(shì)提(tí)供定(dìng)制的(de)擴展(zhǎn)以(yǐ)利用(yòng)FPGA的(de)独特(tè)功能(néng)。更(gèng)多(duō)信(xìn)息可(kě)以(yǐ)在(zài)Altera的(de)OpenCL页(yè)面(miàn)上(shàng)找(zhǎo)到(dào)。他(tā)们(men)還(huán)采用(yòng)了(le)OpenCL 2.0臨时(shí)規範的(de)一(yī)些功能(néng),例如(rú)管(guǎn)道(dào)。從性(xìng)能(néng)的(de)角(jiǎo)度(dù)来(lái)看(kàn),Altera發(fà)布(bù)了(le)白皮書(shū),表(biǎo)明(míng)與(yǔ)CPU和(hé)GPU相比,FPGA在(zài)某些應(yìng)用(yòng)中(zhōng)的(de)性(xìng)能(néng)/功耗要(yào)高(gāo)得多(duō)。 Altera研究中(zhōng)使用(yòng)的(de)典型FPGA電(diàn)路(lù)板功耗在(zài)20W的(de)範圍內(nèi),遠(yuǎn)低于(yú)高(gāo)端分(fēn)立GPU,如(rú)經(jīng)常在(zài)200W範圍內(nèi)的(de)Tesla系(xì)列GPU。 Altera聲稱,在(zài)FPGA上(shàng)運行的(de)OpenCL要(yào)麼(me)超越GPU,要(yào)麼(me)在(zài)某些應(yìng)用(yòng)程序的(de)功耗相當低的(de)情(qíng)況下(xià)與(yǔ)性(xìng)能(néng)相匹(pǐ)配。 Altera并沒(méi)有(yǒu)聲稱这(zhè)对(duì)每一(yī)个(gè)應(yìng)用(yòng)都是(shì)正(zhèng)确的(de),但是(shì)我(wǒ)認为(wèi)这(zhè)对(duì)某些類(lèi)型的(de)應(yìng)用(yòng)来(lái)说(shuō)是(shì)合理的(de)。

我(wǒ)们(men)将介紹一(yī)些OpenCL術(shù)語(yǔ)以(yǐ)及(jí)这(zhè)些概念如(rú)何映射到(dào)FPGA。接下(xià)来(lái),我(wǒ)们(men)将看(kàn)看(kàn)Altera的(de)OpenCL实現(xiàn)的(de)一(yī)些细(xì)节(jié),最(zuì)後(hòu)我(wǒ)将提(tí)供一(yī)些結論性(xìng)意(yì)見(jiàn)。