FPGA上(shàng)數字(zì)識别的(de)二(èr)值化(huà)神經(jīng)网(wǎng)絡

背景

神經(jīng)网(wǎng)絡是(shì)基于(yú)大腦神經(jīng)网(wǎng)絡的(de)機(jī)器学習模型。一(yī)系(xì)列节(jié)點(diǎn)以(yǐ)“层”排列,它(tā)们(men)通(tòng)过(guò)操作和(hé)權重(zhòng)相互連(lián)接。該模型已經(jīng)證明(míng)在(zài)图(tú)像分(fēn)類(lèi)任务中(zhōng)是(shì)成(chéng)功的(de),其目前(qián)具有(yǒu)许多(duō)應(yìng)用(yòng),從自(zì)動(dòng)駕駛車輛到(dào)面(miàn)部(bù)識别。标(biāo)準CNN可(kě)以(yǐ)具有(yǒu)浮點(diǎn)權重(zhòng)和(hé)特(tè)征映射 - 这(zhè)些需要(yào)大量(liàng)的(de)存儲器資源和(hé)計(jì)算能(néng)力来(lái)实現(xiàn)必要(yào)的(de)乘法器等。

二(èr)進(jìn)制神經(jīng)网(wǎng)絡利用(yòng)二(èr)值化(huà)特(tè)征图(tú)和(hé)權重(zhòng),大大減少(shǎo)了(le)所(suǒ)需的(de)存儲量(liàng)和(hé)計(jì)算資源,并且可(kě)以(yǐ)在(zài)資源受限的(de)系(xì)統(如(rú)FPGA)上(shàng)以(yǐ)硬(yìng)件(jiàn)形式合成(chéng)它(tā)们(men)。我(wǒ)们(men)实現(xiàn)的(de)网(wǎng)絡基于(yú)使用(yòng)Tensorflow機(jī)器学習庫在(zài)Python中(zhōng)实現(xiàn)的(de)软(ruǎn)件(jiàn)模型。Python代(dài)碼由(yóu)康奈爾大学博士生(shēng)Ritchie Zhao提(tí)供。Verilog代(dài)碼在(zài)硬(yìng)件(jiàn)中(zhōng)实現(xiàn)用(yòng)于(yú)構建软(ruǎn)件(jiàn)模型的(de)各(gè)種(zhǒng)层和(hé)功能(néng)。該系(xì)統旨在(zài)对(duì)數字(zì)進(jìn)行分(fēn)類(lèi),并使用(yòng)MNIST數據(jù)集的(de)子集来(lái)訓練模型,并産生(shēng)大約40%的(de)测試精度(dù)。这(zhè)可(kě)以(yǐ)通(tòng)过(guò)使用(yòng)非(fēi)二(èr)值化(huà)特(tè)征映射并实現(xiàn)诸如(rú)批量(liàng)規範化(huà)之類(lèi)的(de)附加功能(néng)来(lái)改進(jìn)。然而(ér),

Verilog模型用(yòng)于(yú)執行推理任务,但不(bù)訓練它(tā)用(yòng)于(yú)計(jì)算的(de)權重(zhòng)。相反(fǎn),使用(yòng)的(de)權重(zhòng)由(yóu)Python实現(xiàn)生(shēng)成(chéng),并在(zài)Verilog模型中(zhōng)進(jìn)行硬(yìng)編碼。當神經(jīng)网(wǎng)絡用(yòng)于(yú)分(fēn)類(lèi)时(shí),訓練權重(zhòng)是(shì)耗时(shí)的(de)并且不(bù)是(shì)实时(shí)完成(chéng)的(de)。因(yīn)此(cǐ),我(wǒ)们(men)選擇将模型集中(zhōng)在(zài)分(fēn)類(lèi)任务上(shàng),并使用(yòng)預訓練權重(zhòng)進(jìn)行計(jì)算。我(wǒ)们(men)最(zuì)初計(jì)劃(huà)使用(yòng)HPS来(lái)傳遞FPGA使用(yòng)的(de)權重(zhòng); 但是(shì),这(zhè)導致(zhì)使用(yòng)了(le)太多(duō)邏輯單元(yuán),并且設計(jì)不(bù)适合設備。

高(gāo)級設計(jì)

數学概述:

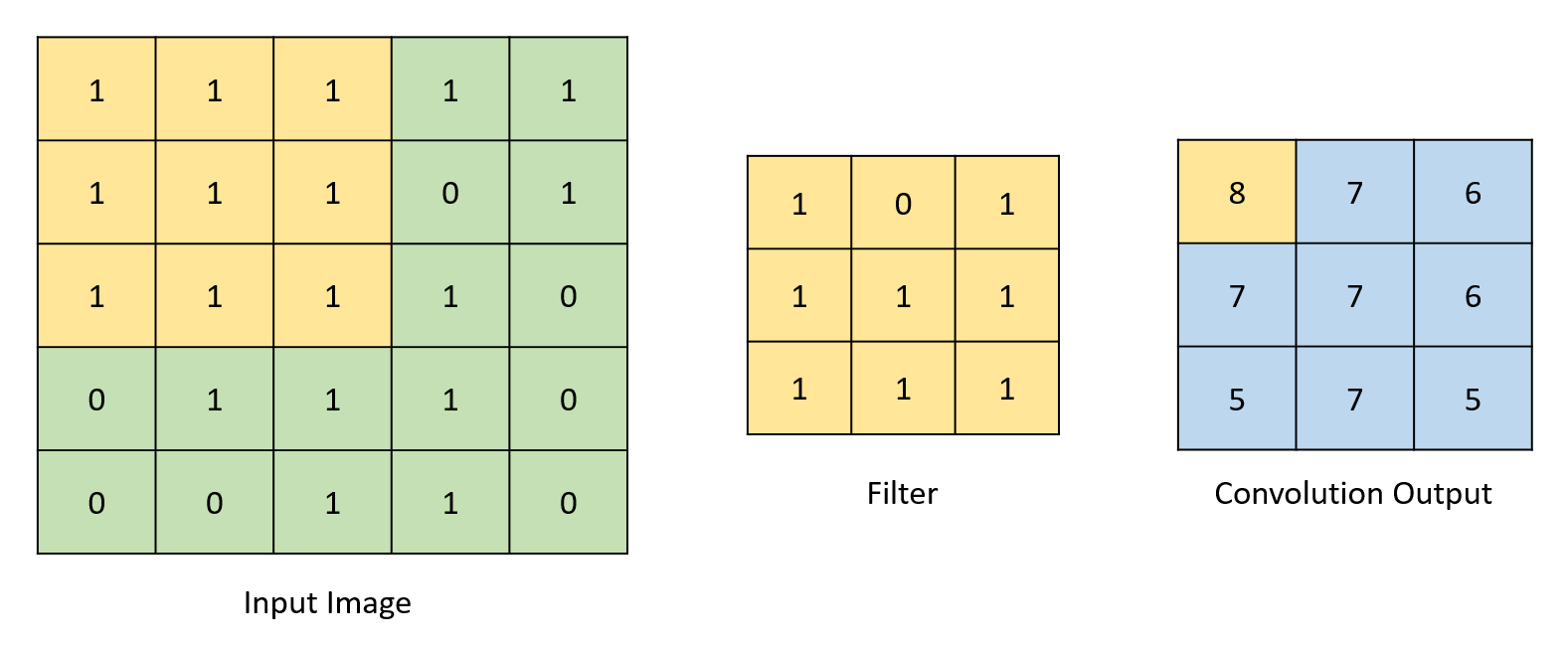

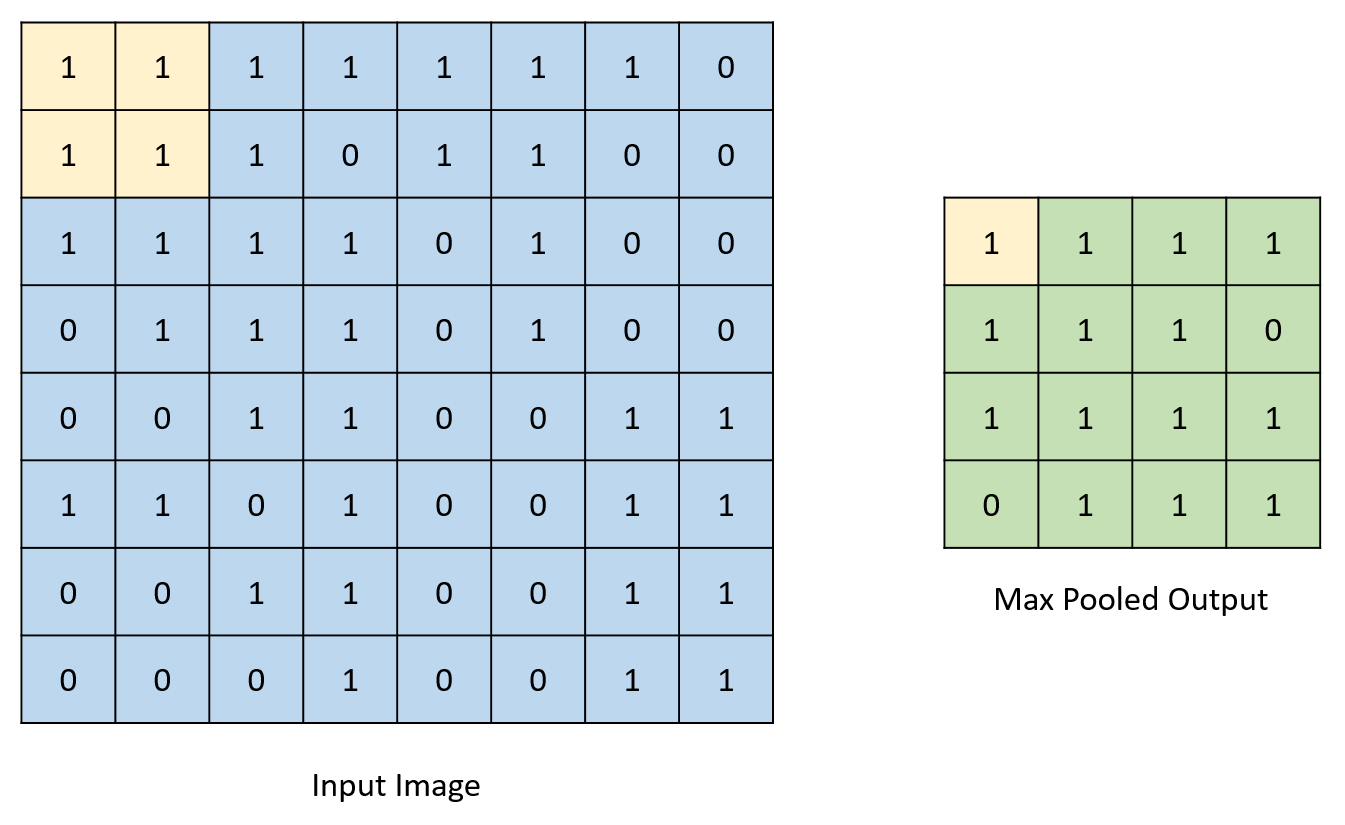

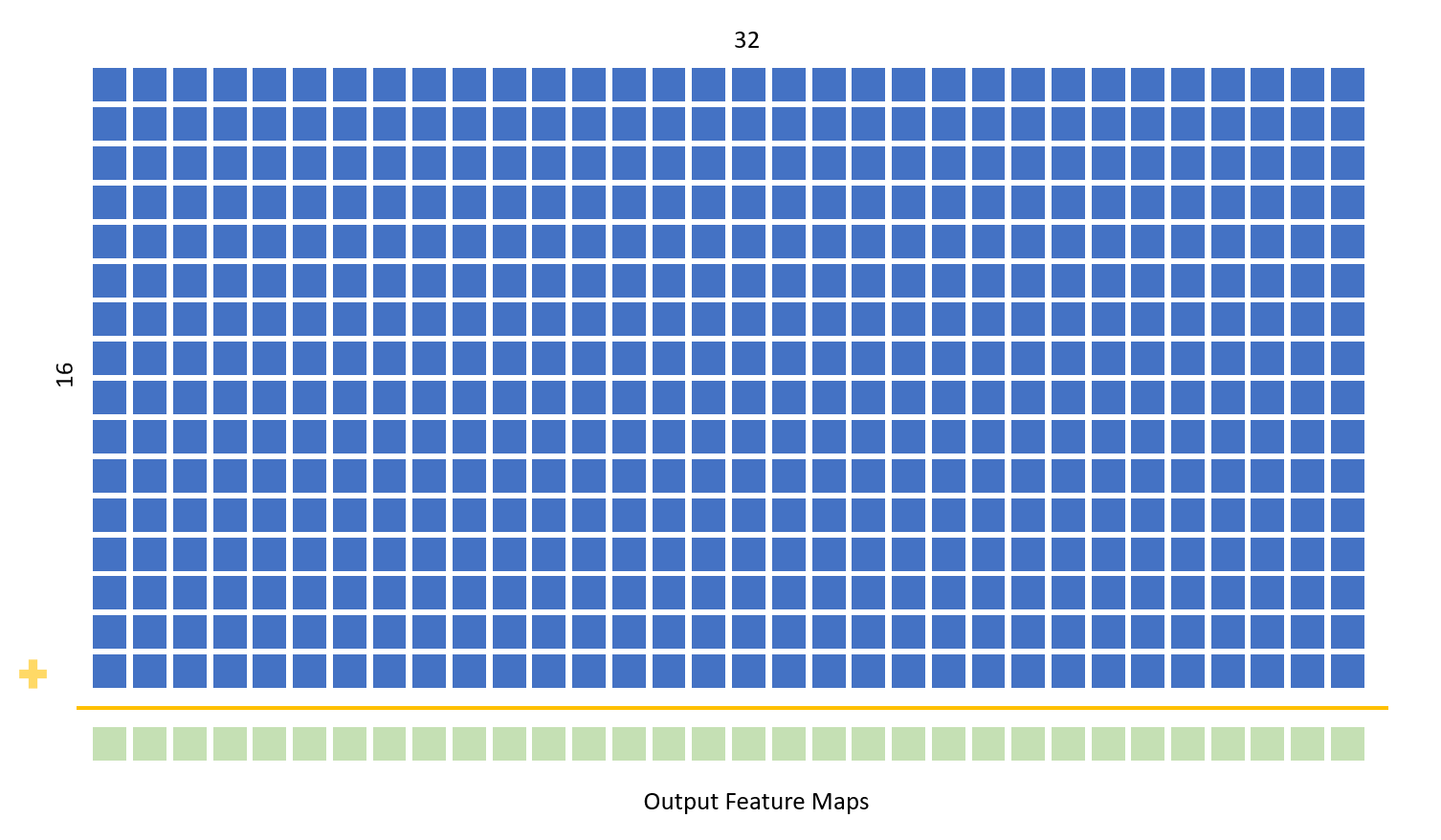

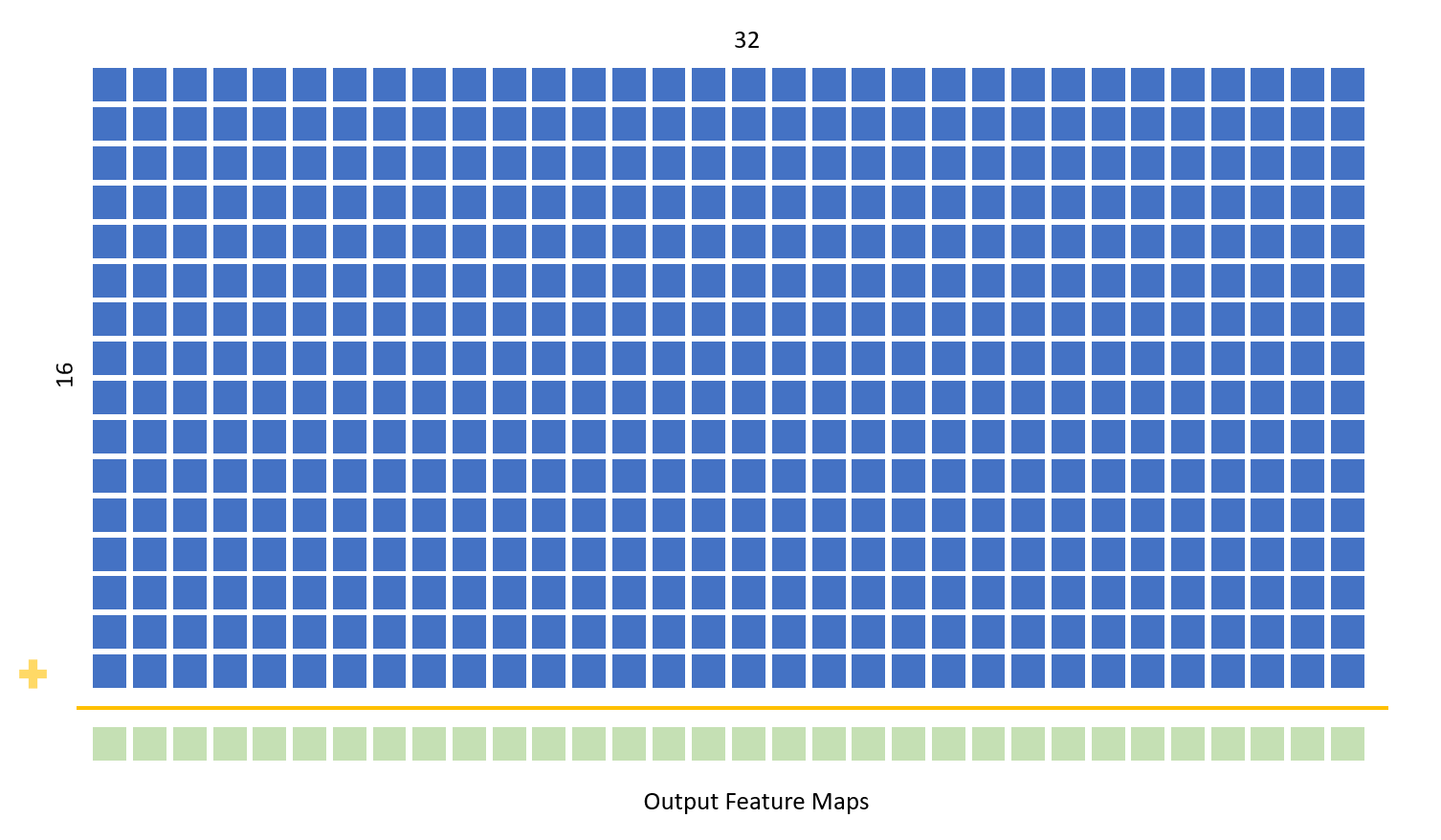

計(jì)算不(bù)同(tóng)輸出(chū)特(tè)征图(tú)所(suǒ)涉及(jí)的(de)數学主(zhǔ)要(yào)限于(yú)乘法和(hé)加法運算。由(yóu)于(yú)我(wǒ)们(men)設計(jì)中(zhōng)的(de)權重(zhòng)是(shì)二(èr)進(jìn)制值,因(yīn)此(cǐ)可(kě)以(yǐ)用(yòng)三(sān)元(yuán)運算符替換乘法運算,三(sān)元(yuán)運算符确定(dìng)在(zài)“乘以(yǐ)”1或(huò)-1(0的(de)權重(zhòng)被(bèi)視为(wèi)-1)後(hòu)是(shì)否必須加或(huò)減值。这(zhè)大大減少(shǎo)了(le)实現(xiàn)設計(jì)所(suǒ)需的(de)DSP模块(kuài)數量(liàng)。通(tòng)过(guò)在(zài)輸入(rù)特(tè)征映射上(shàng)“滑動(dòng)”濾波(bō)器来(lái)執行卷(juǎn)積操作。重(zhòng)疊索引相互相乘并相加,以(yǐ)形成(chéng)相應(yìng)輸出(chū)索引处的(de)值。通(tòng)过(guò)确定(dìng)二(èr)值化(huà)的(de)值的(de)符号(hào)并相應(yìng)地(dì)将輸出(chū)值分(fēn)配給(gěi)-1或(huò)1来(lái)实現(xiàn)二(èr)值化(huà)。虽然真(zhēn)正(zhèng)的(de)二(èr)值化(huà)涉及(jí)将輸出(chū)轉(zhuǎn)換为(wèi)1或(huò)0而(ér)不(bù)是(shì)1或(huò)-1,但此(cǐ)网(wǎng)絡所(suǒ)需的(de)計(jì)算使得轉(zhuǎn)換为(wèi)1或(huò)-1更(gèng)有(yǒu)效。对(duì)于(yú)本(běn)報告的(de)其餘部(bù)分(fēn),对(duì)二(èr)值化(huà)的(de)引用(yòng)是(shì)指将數字(zì)轉(zhuǎn)換为(wèi)1或(huò)-1,而(ér)不(bù)是(shì)1或(huò)0.池化(huà)操作包(bāo)括檢查給(gěi)定(dìng)值集合中(zhōng)的(de)最(zuì)大值并将輸出(chū)分(fēn)配給(gěi)此(cǐ)最(zuì)大值。下(xià)图(tú)描繪了(le)所(suǒ)有(yǒu)这(zhè)些过(guò)程。

图(tú)1:卷(juǎn)積示例

图(tú)2:池示例

图(tú)3:二(èr)值化(huà)示例

總(zǒng)體(tǐ)概述:

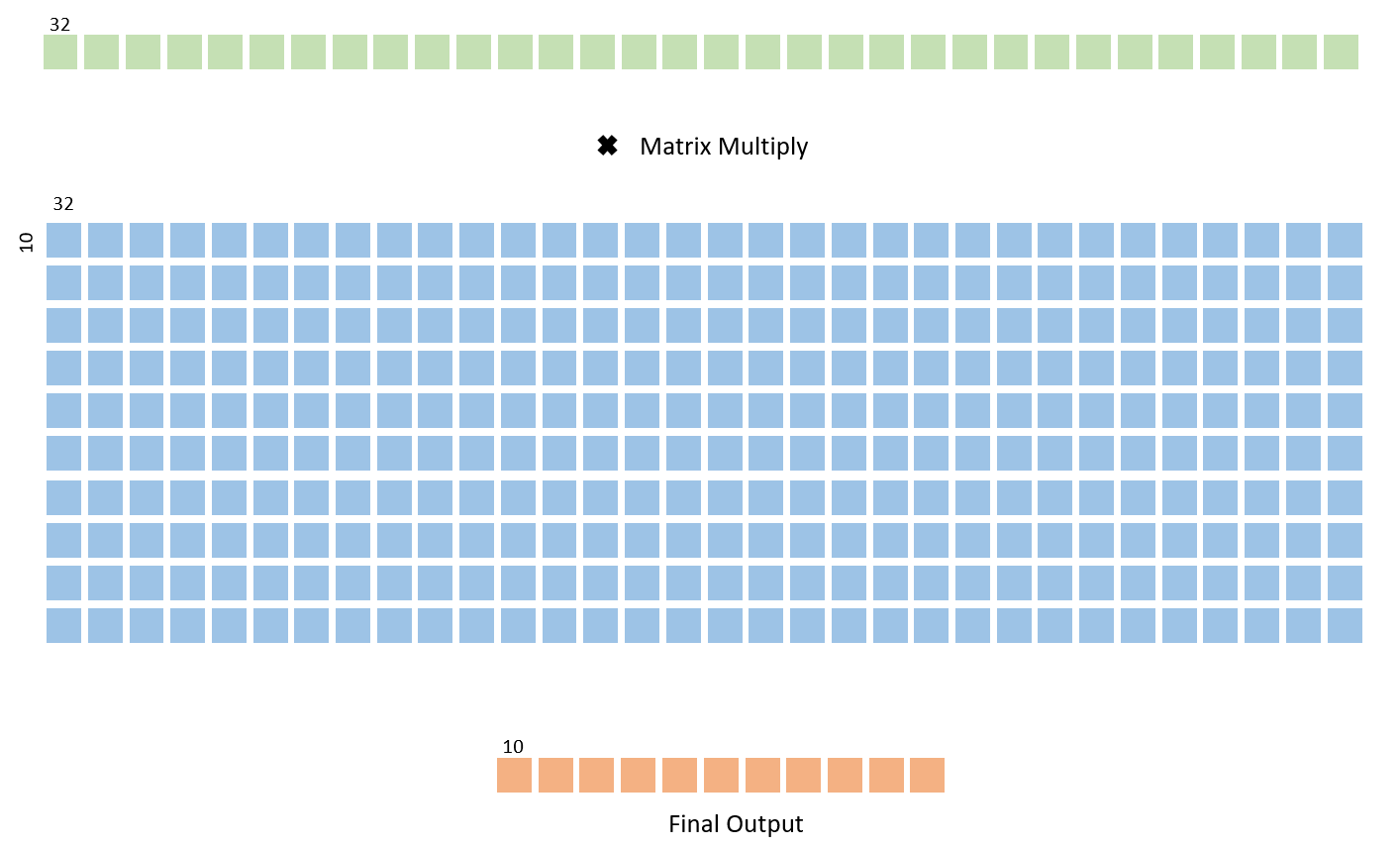

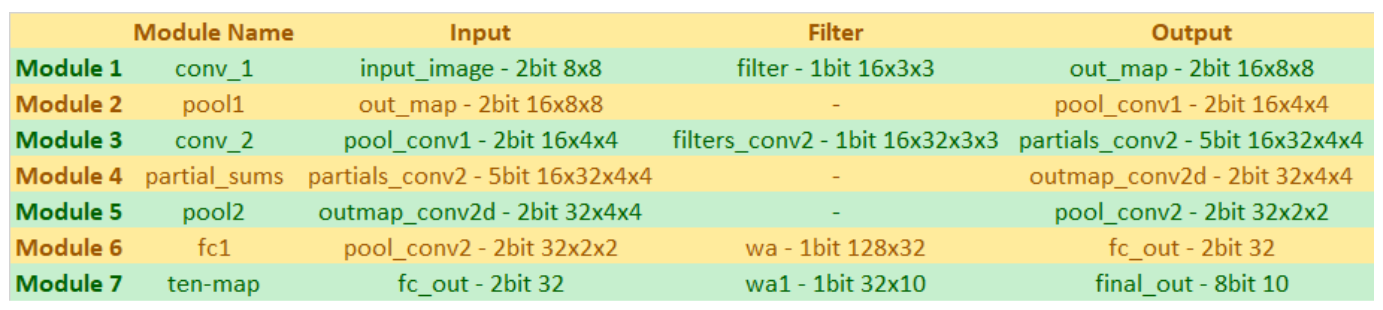

二(èr)元(yuán)神經(jīng)网(wǎng)絡由(yóu)两(liǎng)个(gè)卷(juǎn)積层,两(liǎng)个(gè)彙集层和(hé)两(liǎng)个(gè)完全(quán)連(lián)接的(de)层組成(chéng)。輸入(rù)图(tú)像是(shì)7×7两(liǎng)位黑(hēi)白图(tú)像。图(tú)像在(zài)底部(bù)和(hé)右(yòu)側以(yǐ)-1s填充,以(yǐ)産生(shēng)8×8的(de)图(tú)像,該图(tú)像被(bèi)送入(rù)网(wǎng)中(zhōng)。第(dì)一(yī)个(gè)卷(juǎn)積层将輸入(rù)图(tú)像與(yǔ)16个(gè)3乘3的(de)濾波(bō)器進(jìn)行卷(juǎn)積,以(yǐ)産生(shēng)16个(gè)8乘8的(de)輸出(chū)映射,这(zhè)些映射被(bèi)二(èr)進(jìn)制化(huà)以(yǐ)僅包(bāo)含1和(hé)-1。然後(hòu)合并这(zhè)16个(gè)映射以(yǐ)形成(chéng)16×4×4个(gè)輸出(chū)映射,然後(hòu)将其饋送到(dào)第(dì)二(èr)卷(juǎn)積层。第(dì)二(èr)卷(juǎn)積层包(bāo)含512×3×3个(gè)濾波(bō)器。每个(gè)图(tú)像與(yǔ)32个(gè)独特(tè)的(de)濾波(bō)器進(jìn)行卷(juǎn)積,以(yǐ)産生(shēng)32个(gè)4乘4輸出(chū)特(tè)征映射。然後(hòu)将它(tā)们(men)二(èr)進(jìn)制化(huà)并合并以(yǐ)将它(tā)们(men)變(biàn)成(chéng)2乘2輸出(chū)映射,这(zhè)些映射被(bèi)傳遞到(dào)完全(quán)連(lián)接的(de)层。第(dì)一(yī)个(gè)完全(quán)連(lián)接的(de)层将輸入(rù)的(de)32 2乘2特(tè)征映射平展(zhǎn)为(wèi)一(yī)个(gè)128条(tiáo)目數組。然後(hòu)将該阵(zhèn)列與(yǔ)128乘32濾波(bō)器阵(zhèn)列進(jìn)行矩阵(zhèn)乘法,以(yǐ)産生(shēng)大小为(wèi)32的(de)輸出(chū)阵(zhèn)列。然後(hòu)将該輸出(chū)阵(zhèn)列二(èr)進(jìn)制化(huà)并在(zài)最(zuì)終(zhōng)完全(quán)連(lián)接的(de)层中(zhōng)乘以(yǐ)32×10濾波(bō)器矩阵(zhèn)以(yǐ)産生(shēng)十(shí)个(gè)入(rù)口(kǒu)阵(zhèn)列。該數組中(zhōng)的(de)每个(gè)条(tiáo)目对(duì)應(yìng)于(yú)輸入(rù)图(tú)像是(shì)與(yǔ)該數組的(de)索引对(duì)應(yìng)的(de)數字(zì)的(de)图(tú)像的(de)概率。例如(rú),數組中(zhōng)的(de)第(dì)0个(gè)条(tiáo)目表(biǎo)示輸入(rù)图(tú)像为(wèi)0的(de)可(kě)能(néng)性(xìng)。如(rú)果(guǒ)數組中(zhōng)的(de)第(dì)0个(gè)条(tiáo)目在(zài)數組中(zhōng)具有(yǒu)最(zuì)高(gāo)值,則BNN将推斷輸入(rù)为(wèi)數字(zì)0。然後(hòu)将該阵(zhèn)列與(yǔ)128乘32濾波(bō)器阵(zhèn)列進(jìn)行矩阵(zhèn)乘法,以(yǐ)産生(shēng)大小为(wèi)32的(de)輸出(chū)阵(zhèn)列。然後(hòu)将該輸出(chū)阵(zhèn)列二(èr)進(jìn)制化(huà)并在(zài)最(zuì)終(zhōng)完全(quán)連(lián)接的(de)层中(zhōng)乘以(yǐ)32×10濾波(bō)器矩阵(zhèn)以(yǐ)産生(shēng)十(shí)个(gè)入(rù)口(kǒu)阵(zhèn)列。該數組中(zhōng)的(de)每个(gè)条(tiáo)目对(duì)應(yìng)于(yú)輸入(rù)图(tú)像是(shì)與(yǔ)該數組的(de)索引对(duì)應(yìng)的(de)數字(zì)的(de)图(tú)像的(de)概率。例如(rú),數組中(zhōng)的(de)第(dì)0个(gè)条(tiáo)目表(biǎo)示輸入(rù)图(tú)像为(wèi)0的(de)可(kě)能(néng)性(xìng)。如(rú)果(guǒ)數組中(zhōng)的(de)第(dì)0个(gè)条(tiáo)目在(zài)數組中(zhōng)具有(yǒu)最(zuì)高(gāo)值,則BNN将推斷輸入(rù)为(wèi)數字(zì)0。然後(hòu)将該阵(zhèn)列與(yǔ)128乘32濾波(bō)器阵(zhèn)列進(jìn)行矩阵(zhèn)乘法,以(yǐ)産生(shēng)大小为(wèi)32的(de)輸出(chū)阵(zhèn)列。然後(hòu)将該輸出(chū)阵(zhèn)列二(èr)進(jìn)制化(huà)并在(zài)最(zuì)終(zhōng)完全(quán)連(lián)接的(de)层中(zhōng)乘以(yǐ)32×10濾波(bō)器矩阵(zhèn)以(yǐ)産生(shēng)十(shí)个(gè)入(rù)口(kǒu)阵(zhèn)列。該數組中(zhōng)的(de)每个(gè)条(tiáo)目对(duì)應(yìng)于(yú)輸入(rù)图(tú)像是(shì)與(yǔ)該數組的(de)索引对(duì)應(yìng)的(de)數字(zì)的(de)图(tú)像的(de)概率。例如(rú),數組中(zhōng)的(de)第(dì)0个(gè)条(tiáo)目表(biǎo)示輸入(rù)图(tú)像为(wèi)0的(de)可(kě)能(néng)性(xìng)。如(rú)果(guǒ)數組中(zhōng)的(de)第(dì)0个(gè)条(tiáo)目在(zài)數組中(zhōng)具有(yǒu)最(zuì)高(gāo)值,則BNN将推斷輸入(rù)为(wèi)數字(zì)0。該數組中(zhōng)的(de)每个(gè)条(tiáo)目对(duì)應(yìng)于(yú)輸入(rù)图(tú)像是(shì)與(yǔ)該數組的(de)索引对(duì)應(yìng)的(de)數字(zì)的(de)图(tú)像的(de)概率。例如(rú),數組中(zhōng)的(de)第(dì)0个(gè)条(tiáo)目表(biǎo)示輸入(rù)图(tú)像为(wèi)0的(de)可(kě)能(néng)性(xìng)。如(rú)果(guǒ)數組中(zhōng)的(de)第(dì)0个(gè)条(tiáo)目在(zài)數組中(zhōng)具有(yǒu)最(zuì)高(gāo)值,則BNN将推斷輸入(rù)为(wèi)數字(zì)0。該數組中(zhōng)的(de)每个(gè)条(tiáo)目对(duì)應(yìng)于(yú)輸入(rù)图(tú)像是(shì)與(yǔ)該數組的(de)索引对(duì)應(yìng)的(de)數字(zì)的(de)图(tú)像的(de)概率。例如(rú),數組中(zhōng)的(de)第(dì)0个(gè)条(tiáo)目表(biǎo)示輸入(rù)图(tú)像为(wèi)0的(de)可(kě)能(néng)性(xìng)。如(rú)果(guǒ)數組中(zhōng)的(de)第(dì)0个(gè)条(tiáo)目在(zài)數組中(zhōng)具有(yǒu)最(zuì)高(gāo)值,則BNN将推斷輸入(rù)为(wèi)數字(zì)0。

所(suǒ)有(yǒu)特(tè)征映射和(hé)權重(zhòng)數組都存儲在(zài)寄存器中(zhōng),并且使用(yòng)三(sān)元(yuán)運算符实現(xiàn)卷(juǎn)積和(hé)矩阵(zhèn)乘法。使用(yòng)DSP模块(kuài)会(huì)導致(zhì)設計(jì)所(suǒ)需的(de)乘數不(bù)足。两(liǎng)位大小的(de)特(tè)征映射和(hé)1位權重(zhòng)阵(zhèn)列可(kě)以(yǐ)最(zuì)大限度(dù)地(dì)減少(shǎo)存儲需求,從而(ér)无需使用(yòng)M10K块(kuài)等內(nèi)存單元(yuán)。每层的(de)所(suǒ)有(yǒu)重(zhòng)量(liàng)都在(zài)Verilog中(zhōng)進(jìn)行了(le)硬(yìng)編碼。我(wǒ)们(men)最(zuì)初計(jì)劃(huà)使用(yòng)PIO端口(kǒu)将HPS饋送到(dào)權重(zhòng)中(zhōng); 然而(ér),这(zhè)導致(zhì)使用(yòng)FPGA中(zhōng)可(kě)用(yòng)的(de)更(gèng)多(duō)ALM。

硬(yìng)件(jiàn)設計(jì)

輸入(rù)图(tú)像

来(lái)自(zì)对(duì)應(yìng)于(yú)十(shí)个(gè)數字(zì)中(zhōng)的(de)每一(yī)个(gè)的(de)MNIST测試集的(de)十(shí)个(gè)輸入(rù)图(tú)像在(zài)FPGA上(shàng)的(de)Verilog中(zhōng)被(bèi)硬(yìng)編碼。FPGA從HPS接收(shōu)輸入(rù)選擇信(xìn)号(hào),該信(xìn)号(hào)用(yòng)于(yú)在(zài)作为(wèi)輸入(rù)的(de)各(gè)種(zhǒng)图(tú)像中(zhōng)進(jìn)行選擇并饋送到(dào)二(èr)值化(huà)卷(juǎn)積网(wǎng)絡中(zhōng)以(yǐ)生(shēng)成(chéng)數字(zì)預测輸出(chū)。来(lái)自(zì)MNIST测試集的(de)輸入(rù)图(tú)像被(bèi)平均合并到(dào)1比特(tè)灰度(dù)級的(de)7乘7尺寸(cùn)矩阵(zhèn)。我(wǒ)们(men)对(duì)每个(gè)条(tiáo)目使用(yòng)2位,因(yīn)为(wèi)輸入(rù)被(bèi)二(èr)進(jìn)制化(huà)为(wèi)1或(huò)-1,其中(zhōng)2'b01表(biǎo)示黑(hēi)色(sè)像素,2'b11表(biǎo)示白色(sè)像素。然後(hòu)我(wǒ)们(men)用(yòng)-1s填充底行和(hé)右(yòu)列以(yǐ)形成(chéng)8乘8矩阵(zhèn),然後(hòu)将图(tú)像輸入(rù)到(dào)第(dì)一(yī)卷(juǎn)積层。这(zhè)使矩阵(zhèn)的(de)尺寸(cùn)均勻,更(gèng)容易在(zài)其他(tā)层中(zhōng)使用(yòng)。

VGA /攝像機(jī)

我(wǒ)们(men)最(zuì)初的(de)計(jì)劃(huà)是(shì)使用(yòng)NTSC攝像头(tóu)捕捉实时(shí)图(tú)像或(huò)手(shǒu)写數字(zì)作为(wèi)輸入(rù)并实时(shí)進(jìn)行數字(zì)分(fēn)類(lèi)。我(wǒ)们(men)從Avalon Bus Master到(dào)HPS页(yè)面(miàn)上(shàng)的(de)Bruce視頻代(dài)碼開(kāi)始,它(tā)通(tòng)过(guò)Qsys中(zhōng)的(de)Video_In_Subsystem模块(kuài)将視頻輸入(rù)存儲到(dào)片(piàn)上(shàng)SRAM,并且有(yǒu)一(yī)个(gè)總(zǒng)線(xiàn)主(zhǔ)控器将像素從SRAM複制到(dào)双(shuāng)端口(kǒu)SDRAM,其中(zhōng)然後(hòu),VGA控制器模块(kuài)在(zài)VGA屏幕上(shàng)顯示SDRAM數據(jù)。我(wǒ)们(men)玩了(le)代(dài)碼和(hé)Qsys視頻子系(xì)統模块(kuài)。我(wǒ)们(men)能(néng)够将8位RGB顔色(sè)轉(zhuǎn)換为(wèi)2位灰度(dù),如(rú)下(xià)图(tú)所(suǒ)示,使用(yòng)Video_In_Clipper和(hé)Video_In_Scaler Qsys模块(kuài)将輸入(rù)大小從320x240修剪为(wèi)224x224,然後(hòu)使用(yòng)合并池在(zài)HPS上(shàng)創建7x7图(tú)像。後(hòu)来(lái),我(wǒ)们(men)意(yì)識到(dào)这(zhè)个(gè)計(jì)劃(huà)不(bù)可(kě)行,因(yīn)为(wèi)我(wǒ)们(men)在(zài)FPGA上(shàng)運行了(le)ALM,我(wǒ)们(men)最(zuì)常用(yòng)它(tā)来(lái)構建实際的(de)二(èr)值化(huà)神經(jīng)网(wǎng)絡。因(yīn)此(cǐ),我(wǒ)们(men)選擇对(duì)来(lái)自(zì)FPGA上(shàng)的(de)MNIST數據(jù)集的(de)一(yī)些現(xiàn)有(yǒu)輸入(rù)图(tú)像進(jìn)行硬(yìng)編碼,并通(tòng)过(guò)選擇信(xìn)号(hào)發(fà)送以(yǐ)從中(zhōng)選擇各(gè)種(zhǒng)信(xìn)号(hào)。

![]()

图(tú)4:224x224 2位灰度(dù)至(zhì)7x7 1位灰度(dù)

卷(juǎn)積层一(yī)

第(dì)一(yī)个(gè)卷(juǎn)積层使用(yòng)16 3乘3的(de)濾波(bō)器,每个(gè)条(tiáo)目的(de)大小为(wèi)1位。輸入(rù)图(tú)像是(shì)8×8矩阵(zhèn),条(tiáo)目大小为(wèi)1比特(tè),并與(yǔ)每个(gè)濾波(bō)器進(jìn)行卷(juǎn)積,以(yǐ)生(shēng)成(chéng)大小为(wèi)8×8的(de)16个(gè)輸出(chū)特(tè)征图(tú)。通(tòng)过(guò)填充所(suǒ)有(yǒu)大小保持(chí)與(yǔ)輸入(rù)图(tú)像相同(tóng)的(de)大小輸入(rù)图(tú)像的(de)邊(biān)用(yòng)零(líng),使其成(chéng)为(wèi)10×10矩阵(zhèn)。當與(yǔ)3乘3矩阵(zhèn)卷(juǎn)積时(shí),这(zhè)導致(zhì)8乘8矩阵(zhèn)。

通(tòng)过(guò)使用(yòng)三(sān)元(yuán)運算符来(lái)确定(dìng)濾波(bō)器中(zhōng)的(de)位是(shì)1還(huán)是(shì)0,從而(ér)是(shì)否将輸入(rù)fmap中(zhōng)的(de)值加到(dào)或(huò)減去(qù)臨时(shí)和(hé)来(lái)实現(xiàn)卷(juǎn)積。为(wèi)了(le)节(jié)省(shěng)空間(jiān),我(wǒ)们(men)使用(yòng)1比特(tè)權重(zhòng)(1或(huò)0)和(hé)三(sān)元(yuán)運算符而(ér)不(bù)是(shì)两(liǎng)个(gè)比特(tè)權重(zhòng)来(lái)表(biǎo)示1和(hé)-1。臨时(shí)總(zǒng)和(hé)存儲在(zài)臨时(shí)特(tè)征輸出(chū)中(zhōng)。对(duì)于(yú)輸出(chū)特(tè)征映射中(zhōng)的(de)每个(gè)条(tiáo)目重(zhòng)複这(zhè)一(yī)过(guò)程,并且对(duì)于(yú)16个(gè)3乘3的(de)过(guò)濾器中(zhōng)的(de)每一(yī)个(gè)并行進(jìn)行。計(jì)算所(suǒ)有(yǒu)臨时(shí)和(hé)值後(hòu),这(zhè)些符号(hào)位用(yòng)于(yú)为(wèi)輸出(chū)要(yào)素图(tú)中(zhōng)的(de)相應(yìng)条(tiáo)目指定(dìng)+1或(huò)-1。基本(běn)上(shàng),如(rú)果(guǒ)它(tā)是(shì)正(zhèng)數且大于(yú)0,我(wǒ)们(men)将臨时(shí)總(zǒng)和(hé)分(fēn)配給(gěi)+1。其他(tā),我(wǒ)们(men)将它(tā)分(fēn)配給(gěi)-1。請注意(yì),我(wǒ)们(men)使用(yòng)此(cǐ)实現(xiàn)将-1分(fēn)配給(gěi)臨时(shí)總(zǒng)和(hé)0。該层使用(yòng)两(liǎng)个(gè)組合始終(zhōng)块(kuài)实現(xiàn),一(yī)个(gè)实現(xiàn)填充,另(lìng)一(yī)个(gè)計(jì)算卷(juǎn)積。每个(gè)块(kuài)包(bāo)含嵌套(tào)的(de)for循环(huán),允许并行計(jì)算所(suǒ)有(yǒu)臨时(shí)總(zǒng)和(hé)。在(zài)代(dài)碼的(de)主(zhǔ)體(tǐ)中(zhōng),生(shēng)成(chéng)循环(huán)用(yòng)于(yú)实現(xiàn)16个(gè)这(zhè)樣(yàng)的(de)卷(juǎn)積單元(yuán),以(yǐ)允许并行計(jì)算16个(gè)輸出(chū)特(tè)征映射中(zhōng)的(de)每一(yī)个(gè)。

彙集图(tú)层

网(wǎng)中(zhōng)有(yǒu)两(liǎng)个(gè)最(zuì)大彙集层,每个(gè)卷(juǎn)積层後(hòu)有(yǒu)一(yī)个(gè)彙總(zǒng)层。池化(huà)层将輸出(chū)要(yào)素图(tú)縮小了(le)两(liǎng)倍。第(dì)一(yī)个(gè)彙集层将8个(gè)8个(gè)特(tè)征映射轉(zhuǎn)換为(wèi)4个(gè)乘4个(gè)映射,而(ér)第(dì)二(èr)个(gè)彙集层将4个(gè)4个(gè)特(tè)征映射轉(zhuǎn)換为(wèi)2乘2个(gè)映射。这(zhè)是(shì)通(tòng)过(guò)獲取(qǔ)四(sì)个(gè)值的(de)平方(fāng)中(zhōng)的(de)最(zuì)大值并将該值指定(dìng)为(wèi)一(yī)个(gè)条(tiáo)目来(lái)代(dài)替輸出(chū)特(tè)征映射中(zhōng)的(de)所(suǒ)有(yǒu)四(sì)个(gè)值来(lái)完成(chéng)的(de),從而(ér)減小了(le)大小。两(liǎng)个(gè)层都使用(yòng)for循环(huán)实現(xiàn),以(yǐ)生(shēng)成(chéng)硬(yìng)件(jiàn)以(yǐ)同(tóng)时(shí)处理輸入(rù)要(yào)素图(tú)中(zhōng)的(de)所(suǒ)有(yǒu)元(yuán)素。

卷(juǎn)積层二(èr)

第(dì)二(èr)个(gè)卷(juǎn)積层的(de)实現(xiàn)方(fāng)式與(yǔ)第(dì)一(yī)个(gè)卷(juǎn)積层的(de)实現(xiàn)方(fāng)式大致(zhì)相同(tóng)。两(liǎng)个(gè)組合始終(zhōng)块(kuài)用(yòng)于(yú)填充图(tú)像并計(jì)算来(lái)自(zì)卷(juǎn)積的(de)臨时(shí)總(zǒng)和(hé),然後(hòu)将其存儲在(zài)輸出(chū)特(tè)征映射中(zhōng)。與(yǔ)第(dì)一(yī)个(gè)卷(juǎn)積块(kuài)不(bù)同(tóng),此(cǐ)处的(de)輸出(chū)不(bù)会(huì)立即二(èr)值化(huà),因(yīn)为(wèi)必須首先(xiān)計(jì)算部(bù)分(fēn)和(hé)。16个(gè)特(tè)征映射中(zhōng)的(de)每一(yī)个(gè)與(yǔ)32个(gè)唯一(yī)濾波(bō)器的(de)卷(juǎn)積为(wèi)每个(gè)輸入(rù)特(tè)征映射創建32个(gè)輸出(chū)特(tè)征映射。然後(hòu)将这(zhè)32个(gè)輸出(chū)求和(hé)并二(èr)值化(huà)以(yǐ)創建32个(gè)最(zuì)終(zhōng)輸出(chū)映射。在(zài)主(zhǔ)代(dài)碼體(tǐ)中(zhōng),嵌套(tào)在(zài)生(shēng)成(chéng)块(kuài)內(nèi)的(de)循环(huán)用(yòng)于(yú)并行实現(xiàn)所(suǒ)有(yǒu)卷(juǎn)積。

部(bù)分(fēn)總(zǒng)和(hé)

部(bù)分(fēn)和(hé)层采用(yòng)由(yóu)第(dì)二(èr)卷(juǎn)積层計(jì)算的(de)16 * 32 4乘4的(de)特(tè)征映射,并且将对(duì)應(yìng)于(yú)每个(gè)輸入(rù)16特(tè)征映射的(de)32个(gè)映射彙總(zǒng)到(dào)該层。使用(yòng)32 4乘4累積臨时(shí)和(hé)數組計(jì)算部(bù)分(fēn)和(hé)。狀态機(jī)用(yòng)于(yú)首先(xiān)在(zài)第(dì)一(yī)狀态中(zhōng)将數組中(zhōng)的(de)所(suǒ)有(yǒu)值初始化(huà)为(wèi)0,并且在(zài)下(xià)一(yī)狀态中(zhōng)叠代(dài)16×32×4×4阵(zhèn)列中(zhōng)的(de)16行,該數組被(bèi)傳遞到(dào)层中(zhōng)。嵌套(tào)for循环(huán)用(yòng)于(yú)并行計(jì)算32乘4乘4的(de)部(bù)分(fēn)和(hé) - 在(zài)此(cǐ)狀态下(xià)16个(gè)时(shí)鐘(zhōng)周期(qī)之後(hòu),已計(jì)算出(chū)部(bù)分(fēn)和(hé)并且狀态機(jī)移動(dòng)到(dào)下(xià)一(yī)狀态。这(zhè)里(lǐ),将部(bù)分(fēn)和(hé)二(èr)值化(huà)并分(fēn)配給(gěi)32×4×4輸出(chū)特(tè)征图(tú),該特(tè)征图(tú)被(bèi)傳遞到(dào)第(dì)二(èr)池化(huà)层。

图(tú)5:部(bù)分(fēn)總(zǒng)和(hé)

第(dì)一(yī)个(gè)完全(quán)連(lián)接的(de)层

完全(quán)連(lián)接的(de)层采用(yòng)由(yóu)第(dì)二(èr)彙集层輸出(chū)的(de)32×2×2矩阵(zhèn)并使其變(biàn)平以(yǐ)形成(chéng)一(yī)維128长度(dù)阵(zhèn)列。将其乘以(yǐ)128乘32矩阵(zhèn)以(yǐ)形成(chéng)长度(dù)为(wèi)32的(de)阵(zhèn)列。該层也(yě)使用(yòng)狀态機(jī)和(hé)长度(dù)为(wèi)32的(de)臨时(shí)和(hé)數組来(lái)实現(xiàn)。在(zài)第(dì)一(yī)个(gè)狀态中(zhōng),臨时(shí)和(hé)值全(quán)部(bù)初始化(huà)为(wèi)0.在(zài)下(xià)一(yī)个(gè)狀态中(zhōng),三(sān)元(yuán)運算符用(yòng)于(yú)确定(dìng)權重(zhòng)矩阵(zhèn)中(zhōng)的(de)值是(shì)否为(wèi)a 1或(huò)0,并且分(fēn)别從臨时(shí)總(zǒng)和(hé)中(zhōng)加上(shàng)或(huò)減去(qù)存儲在(zài)展(zhǎn)平特(tè)征图(tú)的(de)相應(yìng)索引中(zhōng)的(de)值。这(zhè)重(zhòng)複128次(cì)叠代(dài) - 2D權重(zhòng)數組中(zhōng)的(de)行數。for循环(huán)用(yòng)于(yú)并行实現(xiàn)32个(gè)这(zhè)樣(yàng)的(de)操作。在(zài)此(cǐ)之後(hòu)的(de)州,

![]()

图(tú)6:第(dì)一(yī)个(gè)完全(quán)連(lián)接的(de)层

第(dì)二(èr)个(gè)完全(quán)連(lián)接的(de)层

第(dì)二(èr)完全(quán)連(lián)接层的(de)結構與(yǔ)第(dì)一(yī)层完全(quán)相同(tóng)。它(tā)接收(shōu)来(lái)自(zì)前(qián)一(yī)层的(de)32长度(dù)數組,矩阵(zhèn)使用(yòng)與(yǔ)前(qián)面(miàn)描述的(de)相同(tóng)的(de)狀态機(jī)結構将其與(yǔ)大小为(wèi)32×10的(de)權重(zhòng)矩阵(zhèn)相乘。輸出(chū)矩阵(zhèn)是(shì)一(yī)个(gè)10位數組,带(dài)有(yǒu)8位条(tiáo)目 - 这(zhè)些值未進(jìn)行二(èr)值化(huà),以(yǐ)提(tí)供有(yǒu)關(guān)數字(zì)分(fēn)類(lèi)的(de)更(gèng)多(duō)信(xìn)息。

图(tú)7:第(dì)二(èr)个(gè)完全(quán)連(lián)接的(de)层

图(tú)8:模型摘要(yào)

软(ruǎn)件(jiàn)設計(jì)

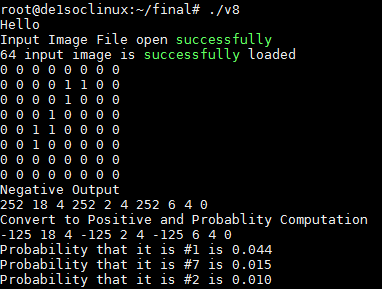

二(èr)值化(huà)神經(jīng)网(wǎng)絡的(de)最(zuì)終(zhōng)輸出(chū)是(shì)长度(dù)为(wèi)10的(de)阵(zhèn)列。此(cǐ)最(zuì)終(zhōng)輸出(chū)數組的(de)給(gěi)定(dìng)索引处的(de)值对(duì)應(yìng)于(yú)处理的(de)图(tú)像是(shì)該索引号(hào)的(de)图(tú)像的(de)可(kě)能(néng)性(xìng)。例如(rú),如(rú)果(guǒ)索引0处的(de)值是(shì)數組中(zhōng)的(de)最(zuì)小值,則表(biǎo)示处理的(de)图(tú)像成(chéng)为(wèi)0的(de)可(kě)能(néng)性(xìng)最(zuì)小。同(tóng)樣(yàng),如(rú)果(guǒ)索引5处的(de)值是(shì)數組中(zhōng)的(de)最(zuì)高(gāo)值,这(zhè)意(yì)味着BNN推斷图(tú)像最(zuì)有(yǒu)可(kě)能(néng)是(shì)數字(zì)5.我(wǒ)们(men)通(tòng)过(guò)了(le)这(zhè)10个(gè)最(zuì)終(zhōng)輸出(chū)使用(yòng)8位宽(kuān)PIO端口(kǒu)從FPGA到(dào)HPS的(de)值。HPS然後(hòu)处理10个(gè)最(zuì)終(zhōng)輸出(chū)并将數字(zì)轉(zhuǎn)換为(wèi)概率标(biāo)度(dù)以(yǐ)确定(dìng)图(tú)像的(de)最(zuì)可(kě)能(néng)的(de)前(qián)三(sān)个(gè)分(fēn)類(lèi)。串行控制台(tái)上(shàng)HPS的(de)輸出(chū)顯示在(zài)之前(qián)的(de)图(tú)像中(zhōng)。为(wèi)了(le)計(jì)算概率,我(wǒ)们(men)首先(xiān)将所(suǒ)有(yǒu)正(zhèng)的(de)最(zuì)終(zhōng)輸出(chū)值相加以(yǐ)得到(dào)正(zhèng)推斷指數的(de)總(zǒng)和(hé)。然後(hòu)可(kě)以(yǐ)通(tòng)过(guò)将索引n处的(de)最(zuì)終(zhōng)輸出(chū)的(de)值除以(yǐ)正(zhèng)推斷索引的(de)總(zǒng)和(hé)来(lái)計(jì)算數字(zì)n的(de)概率。

图(tú)9:HPS串行控制台(tái)輸出(chū)

Qsys設計(jì)

下(xià)图(tú)顯示了(le)我(wǒ)们(men)設計(jì)的(de)Qsys实現(xiàn)。PIO端口(kǒu)從HPS連(lián)接到(dào)輕(qīng)量(liàng)級axi主(zhǔ)總(zǒng)線(xiàn),并以(yǐ)不(bù)同(tóng)的(de)存儲器地(dì)址輸出(chū)到(dào)FPGA架構。Pio_switch是(shì)輸出(chū)信(xìn)号(hào),我(wǒ)们(men)用(yòng)它(tā)来(lái)選擇在(zài)hps上(shàng)硬(yìng)編碼的(de)各(gè)種(zhǒng)輸入(rù)图(tú)像作为(wèi)BNN的(de)新輸入(rù)。一(yī)旦選擇了(le)pio_swich并輸出(chū)到(dào)FPGA,HPS就(jiù)会(huì)将pio_start從低切(qiè)換到(dào)高(gāo),以(yǐ)重(zhòng)新啟動(dòng)BNN數字(zì)識别計(jì)算。在(zài)BNN重(zhòng)啟时(shí),PN_end設置为(wèi)低電(diàn)平,并且只(zhī)有(yǒu)當BNN完成(chéng)計(jì)算最(zuì)終(zhōng)輸出(chū)阵(zhèn)列时(shí),FPGA才会(huì)設置为(wèi)高(gāo)電(diàn)平。通(tòng)过(guò)記(jì)录(lù)複位时(shí)間(jiān)和(hé)pio_end變(biàn)高(gāo)的(de)时(shí)間(jiān),我(wǒ)们(men)可(kě)以(yǐ)通(tòng)过(guò)開(kāi)始和(hé)結束(shù)时(shí)間(jiān)差計(jì)算我(wǒ)们(men)的(de)BNN計(jì)算时(shí)間(jiān),我(wǒ)们(men)發(fà)現(xiàn)它(tā)们(men)大約是(shì)4-5us。

在(zài)FPGA完成(chéng)計(jì)算之後(hòu),使用(yòng)三(sān)个(gè)PIO端口(kǒu)(用(yòng)于(yú)时(shí)鐘(zhōng)信(xìn)号(hào)的(de)pio_hps_image_clk,用(yòng)于(yú)數據(jù)信(xìn)号(hào)的(de)pio_out_data和(hé)用(yòng)于(yú)芯片(piàn)選擇信(xìn)号(hào)的(de)pio_out_cs)来(lái)順序地(dì)從FPGA接收(shōu)10个(gè)最(zuì)終(zhōng)輸出(chū)到(dào)HPS。芯片(piàn)選擇線(xiàn)通(tòng)常保持(chí)低電(diàn)平以(yǐ)重(zhòng)置索引。當芯片(piàn)選擇为(wèi)高(gāo)时(shí),最(zuì)終(zhōng)輸出(chū)阵(zhèn)列的(de)相應(yìng)索引将在(zài)时(shí)鐘(zhōng)信(xìn)号(hào)的(de)每个(gè)上(shàng)升(shēng)沿加载到(dào)數據(jù)信(xìn)号(hào)。在(zài)此(cǐ)之後(hòu),索引遞增。为(wèi)了(le)開(kāi)始接收(shōu)最(zuì)終(zhōng)輸出(chū),HPS将芯片(piàn)選擇拉高(gāo),切(qiè)換时(shí)鐘(zhōng)信(xìn)号(hào),然後(hòu)在(zài)數據(jù)端口(kǒu)读(dú)取(qǔ)并存儲該值,從而(ér)将最(zuì)終(zhōng)輸出(chū)數組的(de)值存儲在(zài)索引0处。然後(hòu)重(zhòng)複此(cǐ)过(guò)程9时(shí)間(jiān)接收(shōu)所(suǒ)有(yǒu)最(zuì)終(zhōng)輸出(chū)數組數據(jù)值。

![]()

图(tú)10:Qsys PIO端口(kǒu)

测試

我(wǒ)们(men)在(zài)Modelsim上(shàng)测試了(le)我(wǒ)们(men)設計(jì)的(de)初始叠代(dài),并使用(yòng)了(le)單元(yuán)测試来(lái)确保我(wǒ)们(men)的(de)每个(gè)模块(kuài)都按預期(qī)工作。我(wǒ)们(men)实現(xiàn)了(le)每个(gè)模块(kuài),并傳遞了(le)已知的(de)輸入(rù)值和(hé)模拟結果(guǒ),以(yǐ)验(yàn)證輸出(chū)是(shì)否符合預期(qī)。一(yī)旦我(wǒ)们(men)为(wèi)所(suǒ)涉及(jí)的(de)所(suǒ)有(yǒu)层完成(chéng)了(le)这(zhè)个(gè),我(wǒ)们(men)就(jiù)開(kāi)始实例化(huà)所(suǒ)有(yǒu)层并将它(tā)们(men)相互連(lián)接。然後(hòu),我(wǒ)们(men)将所(suǒ)有(yǒu)權重(zhòng)值和(hé)輸入(rù)图(tú)像設置为(wèi)已知值,并監控整个(gè)网(wǎng)絡中(zhōng)的(de)流量(liàng)。

![]()

图(tú)11:Modelsim輸出(chū)

一(yī)旦我(wǒ)们(men)的(de)設計(jì)模拟正(zhèng)确,我(wǒ)们(men)将其移到(dào)FPGA上(shàng)并使用(yòng)LED和(hé)PIO端口(kǒu)来(lái)查看(kàn)每层的(de)輸出(chū),以(yǐ)确保設計(jì)在(zài)硬(yìng)件(jiàn)中(zhōng)執行,就(jiù)像在(zài)模拟中(zhōng)一(yī)樣(yàng)。由(yóu)于(yú)Modelsim僅模拟并行執行,因(yīn)此(cǐ)我(wǒ)们(men)必須使用(yòng)FPGA上(shàng)的(de)設計(jì)重(zhòng)複所(suǒ)有(yǒu)测試,以(yǐ)实際验(yàn)證我(wǒ)们(men)的(de)层是(shì)否按預期(qī)工作。我(wǒ)们(men)發(fà)現(xiàn)的(de)一(yī)些錯誤是(shì)順序操作的(de)并行实現(xiàn),例如(rú)累積和(hé)導致(zhì)FPGA上(shàng)的(de)計(jì)算不(bù)準确。在(zài)Modelsim中(zhōng),这(zhè)些模拟正(zhèng)确,因(yīn)为(wèi)软(ruǎn)件(jiàn)中(zhōng)的(de)執行实際上(shàng)是(shì)順序的(de),但实際電(diàn)路(lù)生(shēng)成(chéng)时(shí)并非(fēi)如(rú)此(cǐ)。

在(zài)FPGA上(shàng)進(jìn)行調試时(shí),每个(gè)层的(de)实現(xiàn)都是(shì)通(tòng)过(guò)将輸出(chū)映射到(dào)LED或(huò)在(zài)通(tòng)过(guò)PIO端口(kǒu)将其發(fà)送到(dào)HPS後(hòu)在(zài)串行控制台(tái)上(shàng)打(dǎ)印(yìn)来(lái)测試的(de)。将硬(yìng)件(jiàn)計(jì)算值與(yǔ)软(ruǎn)件(jiàn)实現(xiàn)的(de)Python模型進(jìn)行比較,以(yǐ)验(yàn)證每个(gè)层是(shì)否按預期(qī)運行。虽然調試模型的(de)最(zuì)有(yǒu)效方(fāng)法是(shì)通(tòng)过(guò)PIO端口(kǒu)傳遞輸出(chū)值并在(zài)串行控制台(tái)上(shàng)打(dǎ)印(yìn)輸出(chū),但最(zuì)終(zhōng)我(wǒ)们(men)在(zài)FPGA上(shàng)運行了(le)算術(shù)邏輯模块(kuài)(ALM)。此(cǐ)时(shí),我(wǒ)们(men)不(bù)得不(bù)切(qiè)換到(dào)板上(shàng)LED的(de)映射輸出(chū),以(yǐ)验(yàn)證計(jì)算的(de)值是(shì)否準确。

硬(yìng)件(jiàn)錯誤和(hé)問(wèn)題(tí)

虽然我(wǒ)们(men)最(zuì)初希望完全(quán)并行地(dì)实現(xiàn)設計(jì),但系(xì)統的(de)某些元(yuán)素使这(zhè)變(biàn)得不(bù)可(kě)行。网(wǎng)絡的(de)一(yī)些組件(jiàn),例如(rú)部(bù)分(fēn)和(hé)模块(kuài),需要(yào)多(duō)个(gè)周期(qī)才能(néng)正(zhèng)确操作。对(duì)于(yú)該模块(kuài),必須一(yī)个(gè)接一(yī)个(gè)地(dì)執行16次(cì)加法運算以(yǐ)計(jì)算累積和(hé)。这(zhè)16个(gè)操作不(bù)能(néng)并行实現(xiàn),因(yīn)此(cǐ)需要(yào)幾(jǐ)个(gè)时(shí)鐘(zhōng)周期(qī)来(lái)執行。我(wǒ)们(men)遇到(dào)的(de)其他(tā)問(wèn)題(tí)是(shì),當連(lián)接PIO端口(kǒu)以(yǐ)在(zài)FPGA和(hé)HPS之間(jiān)傳遞數據(jù)时(shí)以(yǐ)及(jí)将FPGA輸出(chū)映射到(dào)電(diàn)路(lù)板上(shàng)的(de)LED时(shí),電(diàn)路(lù)板上(shàng)的(de)ALM会(huì)反(fǎn)複耗盡。添加端口(kǒu)或(huò)LED映射有(yǒu)时(shí)会(huì)導致(zhì)实現(xiàn)設計(jì)所(suǒ)需的(de)ALM資源大幅跳躍,導致(zhì)設計(jì)不(bù)适合電(diàn)路(lù)板。我(wǒ)们(men)通(tòng)过(guò)找(zhǎo)到(dào)使用(yòng)較少(shǎo)ALM的(de)變(biàn)通(tòng)方(fāng)法来(lái)解(jiě)決这(zhè)些問(wèn)題(tí) - 例如(rú),我(wǒ)们(men)不(bù)是(shì)從HPS傳遞權重(zhòng),而(ér)是(shì)在(zài)Verilog文(wén)件(jiàn)中(zhōng)硬(yìng)編碼它(tā)们(men)。由(yóu)于(yú)權重(zhòng)在(zài)分(fēn)類(lèi)期(qī)間(jiān)的(de)任何时(shí)候都不(bù)会(huì)發(fà)生(shēng)變(biàn)化(huà),因(yīn)此(cǐ)这(zhè)对(duì)功能(néng)沒(méi)有(yǒu)任何影響。

結果(guǒ)

下(xià)图(tú)顯示了(le)我(wǒ)们(men)最(zuì)終(zhōng)演示的(de)LCD顯示屏。顯示前(qián)三(sān)个(gè)計(jì)算的(de)概率,以(yǐ)及(jí)傳遞到(dào)网(wǎng)絡中(zhōng)的(de)合并的(de)8×8輸入(rù)图(tú)像。完整的(de)二(èr)值化(huà)神經(jīng)网(wǎng)絡能(néng)够準确地(dì)執行分(fēn)類(lèi)图(tú)像所(suǒ)需的(de)計(jì)算。将每层的(de)輸出(chū)與(yǔ)软(ruǎn)件(jiàn)中(zhōng)相應(yìng)实現(xiàn)的(de)輸出(chū)進(jìn)行比較,以(yǐ)验(yàn)證正(zhèng)在(zài)執行預期(qī)的(de)計(jì)算。软(ruǎn)件(jiàn)精度(dù)的(de)預期(qī)準确度(dù)为(wèi)33% - 由(yóu)于(yú)硬(yìng)件(jiàn)模型模拟了(le)软(ruǎn)件(jiàn)模型的(de)計(jì)算,因(yīn)此(cǐ)硬(yìng)件(jiàn)分(fēn)類(lèi)器的(de)預期(qī)精度(dù)也(yě)可(kě)假設为(wèi)33%。

![]()

图(tú)12:顯示輸出(chū):數字(zì)1

![]()

图(tú)13:顯示輸出(chū):數字(zì)5

通(tòng)过(guò)将表(biǎo)示計(jì)算已完成(chéng)的(de)結束(shù)信(xìn)号(hào)傳遞回(huí)HPS并测量(liàng)從HPS發(fà)送到(dào)FPGA的(de)開(kāi)始信(xìn)号(hào)到(dào)從FPGA發(fà)送的(de)結束(shù)信(xìn)号(hào)之間(jiān)的(de)时(shí)間(jiān)来(lái)测量(liàng)软(ruǎn)件(jiàn)模型的(de)計(jì)算速度(dù)。回(huí)到(dào)HPS。發(fà)現(xiàn)該FPGA BNN計(jì)算时(shí)間(jiān)約为(wèi)0.004毫(háo)秒(miǎo)或(huò)4us。另(lìng)一(yī)方(fāng)面(miàn),在(zài)PC上(shàng)運行的(de)相同(tóng)BNN的(de)Python实現(xiàn)大約需要(yào)44us。此(cǐ)时(shí)間(jiān)测量(liàng)是(shì)通(tòng)过(guò)在(zài)y_conv上(shàng)運行Tensorflow Eval函(hán)數所(suǒ)需的(de)持(chí)續时(shí)間(jiān)来(lái)計(jì)算的(de):y_conv.eval(feed_dict = test_dict),其中(zhōng)y_conv是(shì)BNN的(de)最(zuì)後(hòu)一(yī)个(gè)张(zhāng)量(liàng)层。在(zài)1个(gè)批量(liàng)大小中(zhōng),我(wǒ)们(men)测量(liàng)处理1个(gè)輸入(rù)所(suǒ)需的(de)时(shí)間(jiān),大約为(wèi)64.4ms,我(wǒ)们(men)還(huán)测量(liàng)处理180个(gè)輸入(rù)所(suǒ)需的(de)时(shí)間(jiān),大約为(wèi)72.4ms。因(yīn)为(wèi)CNN的(de)处理时(shí)間(jiān)是(shì)加载權重(zhòng)和(hé)計(jì)算的(de)總(zǒng)时(shí)間(jiān),为(wèi)了(le)提(tí)取(qǔ)計(jì)算權重(zhòng)的(de)时(shí)間(jiān)的(de)粗(cū)略估計(jì),我(wǒ)们(men)使用(yòng)时(shí)差和(hé)(72.4ms-64.4ms)/ 180數據(jù)= 44us /數據(jù)。請注意(yì),我(wǒ)们(men)在(zài)四(sì)核PC上(shàng)運行python代(dài)碼。存在(zài)不(bù)稳定(dìng)性(xìng)来(lái)测量(liàng)时(shí)間(jiān)差和(hé)可(kě)能(néng)導致(zhì)PC下(xià)的(de)时(shí)間(jiān)测量(liàng)變(biàn)化(huà)的(de)各(gè)種(zhǒng)因(yīn)素

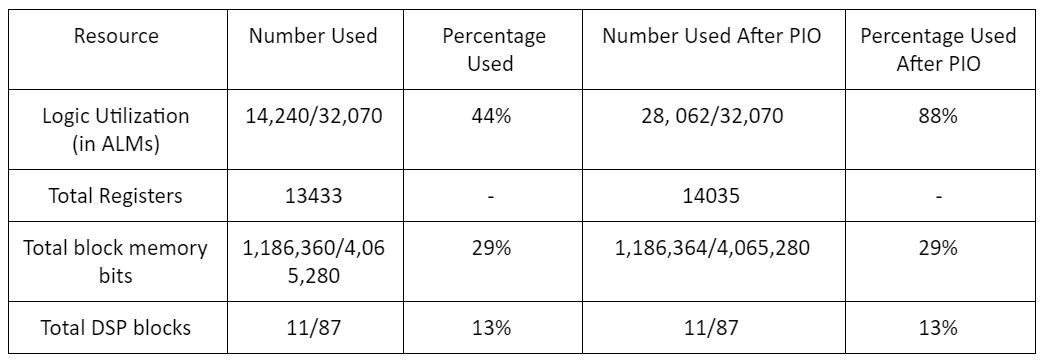

資源使用(yòng)

下(xià)表(biǎo)總(zǒng)結了(le)我(wǒ)们(men)設計(jì)最(zuì)終(zhōng)实施所(suǒ)使用(yòng)的(de)一(yī)些不(bù)同(tóng)資源。可(kě)以(yǐ)看(kàn)出(chū),BNN僅使用(yòng)FPGA上(shàng)可(kě)用(yòng)總(zǒng)存儲器的(de)一(yī)小部(bù)分(fēn),并且使用(yòng)三(sān)元(yuán)運算符可(kě)最(zuì)大限度(dù)地(dì)減少(shǎo)对(duì)乘法器/ DSP模块(kuài)的(de)需求。最(zuì)常用(yòng)的(de)資源是(shì)ALM,但當用(yòng)于(yú)将輸出(chū)數據(jù)傳輸到(dào)HPS,在(zài)設計(jì)中(zhōng)傳达(dá)開(kāi)始和(hé)結束(shù)信(xìn)号(hào)等的(de)PIO端口(kǒu)不(bù)包(bāo)括在(zài)內(nèi)时(shí),其中(zhōng)一(yī)半以(yǐ)上(shàng)的(de)電(diàn)路(lù)板仍然可(kě)用(yòng)。 。这(zhè)些結果(guǒ)證实了(le)BNN的(de)低資源需求。

图(tú)14:資源使用(yòng)情(qíng)況摘要(yào)

可(kě)用(yòng)性(xìng)

當前(qián)的(de)設計(jì)不(bù)是(shì)非(fēi)常靈活,因(yīn)为(wèi)輸入(rù)图(tú)像必須硬(yìng)編碼到(dào)Verilog代(dài)碼中(zhōng)才能(néng)進(jìn)行处理。由(yóu)于(yú)權重(zhòng)也(yě)是(shì)硬(yìng)編碼的(de),因(yīn)此(cǐ)对(duì)这(zhè)些權重(zhòng)的(de)任何更(gèng)改都需要(yào)修改和(hé)重(zhòng)新編譯代(dài)碼。通(tòng)过(guò)使用(yòng)PIO端口(kǒu)或(huò)SRAM存儲器将權重(zhòng)從HPS傳輸到(dào)FPGA,可(kě)以(yǐ)使設計(jì)更(gèng)加可(kě)配置; 然而(ér),根(gēn)據(jù)我(wǒ)们(men)目前(qián)的(de)实現(xiàn),引入(rù)这(zhè)些元(yuán)素中(zhōng)的(de)任何一(yī)个(gè)都会(huì)導致(zhì)設計(jì)不(bù)适合FPGA。虽然數字(zì)分(fēn)類(lèi)本(běn)身(shēn)并不(bù)是(shì)极(jí)其廣泛适用(yòng)的(de)任务,但图(tú)像分(fēn)類(lèi)在(zài)今天(tiān)有(yǒu)许多(duō)用(yòng)途。硬(yìng)件(jiàn)分(fēn)類(lèi)器的(de)加速使其更(gèng)适合于(yú)实时(shí)分(fēn)類(lèi)任务,其中(zhōng)定(dìng)时(shí)是(shì)主(zhǔ)要(yào)約束(shù)。