一(yī)、前(qián)言

在(zài)实时(shí)性(xìng)要(yào)求較高(gāo)的(de)场合中(zhōng),CPU软(ruǎn)件(jiàn)執行的(de)方(fāng)式顯然不(bù)能(néng)滿足需求,这(zhè)时(shí)需要(yào)硬(yìng)件(jiàn)邏輯实現(xiàn)部(bù)分(fēn)功能(néng)。要(yào)想(xiǎng)使自(zì)定(dìng)義IP核被(bèi)CPU訪問(wèn),就(jiù)必須带(dài)有(yǒu)總(zǒng)線(xiàn)接口(kǒu)。ZYNQ采用(yòng)AXI BUS实現(xiàn)PS和(hé)PL之間(jiān)的(de)數據(jù)交互。本(běn)文(wén)以(yǐ)PWM为(wèi)例設計(jì)了(le)自(zì)定(dìng)義AXI總(zǒng)線(xiàn)IP,来(lái)演示如(rú)何靈活運用(yòng)ARM+FPGA的(de)架構。

功能(néng)定(dìng)義:在(zài)上(shàng)一(yī)篇(piān)ZYNQ入(rù)門(mén)实例博文(wén)講解(jiě)的(de)系(xì)統中(zhōng)添加自(zì)定(dìng)義IP核,其輸出(chū)驅動(dòng)LED等实現(xiàn)呼吸燈(dēng)效果(guǒ)。并且软(ruǎn)件(jiàn)通(tòng)过(guò)配置寄存器方(fāng)式对(duì)其進(jìn)行使能(néng)、打(dǎ)開(kāi)/關(guān)閉配置以(yǐ)及(jí)選擇占空比變(biàn)化(huà)步长。另(lìng)外(wài),可(kě)以(yǐ)按鍵操作完成(chéng)占空比變(biàn)化(huà)步长的(de)增減。

平台(tái):米(mǐ)聯客 MIZ702N (ZYNQ-7020)

软(ruǎn)件(jiàn):VIVADO+SDK 2017

注:自(zì)定(dìng)義IP邏輯設計(jì)采用(yòng)明(míng)德揚至(zhì)簡設計(jì)法

二(èr)、PWM IP設計(jì)

PWM无非(fēi)就(jiù)是(shì)通(tòng)过(guò)控制周期(qī)脈沖信(xìn)号(hào)的(de)占空比,也(yě)就(jiù)是(shì)改變(biàn)高(gāo)電(diàn)平在(zài)一(yī)段(duàn)固定(dìng)周期(qī)內(nèi)的(de)持(chí)續时(shí)間(jiān)来(lái)达(dá)到(dào)控制目的(de)。脈沖周期(qī)需要(yào)一(yī)个(gè)計(jì)數器来(lái)定(dìng)时(shí),占空比由(yóu)低變(biàn)高(gāo)和(hé)由(yóu)高(gāo)變(biàn)低两(liǎng)種(zhǒng)模式同(tóng)樣(yàng)需要(yào)一(yī)个(gè)計(jì)數器来(lái)指示,因(yīn)此(cǐ)这(zhè)里(lǐ)使用(yòng)两(liǎng)个(gè)嵌套(tào)的(de)計(jì)數器cnt_cyc和(hé)cnt_mode。cnt_mode的(de)加一(yī)条(tiáo)件(jiàn)除了(le)要(yào)等待cnt_cyc計(jì)數完成(chéng),還(huán)要(yào)考慮占空比的(de)變(biàn)化(huà)。

我(wǒ)们(men)可(kě)以(yǐ)使用(yòng)下(xià)降沿位置表(biǎo)示占空比,位置越靠近(jìn)周期(qī)值占空比越高(gāo)。在(zài)模式0中(zhōng)下(xià)降沿位置按照步长增大直(zhí)至(zhì)大于(yú)等于(yú)周期(qī)值,模式1中(zhōng)下(xià)降沿位置則按照步长遞減直(zhí)到(dào)小于(yú)步长。使用(yòng)两(liǎng)个(gè)信(xìn)号(hào)up_stage和(hé)down_stage分(fēn)别指示模式0和(hé)模式1。至(zhì)于(yú)步长值,在(zài)配置有(yǒu)效时(shí)被(bèi)更(gèng)新,否則使用(yòng)默認值。模块(kuài)最(zuì)終(zhōng)的(de)輸出(chū)信(xìn)号(hào)在(zài)周期(qī)計(jì)數器小于(yú)下(xià)降沿位置为(wèi)1,反(fǎn)之为(wèi)零(líng)。

<PWM IP邏輯代(dài)碼>

VIVADO綜合、布(bù)局(jú)布(bù)線(xiàn)比較慢(màn),且软(ruǎn)硬(yìng)件(jiàn)級聯調試費时(shí)費力,所(suǒ)以(yǐ)仿真(zhēn)是(shì)极(jí)其重(zhòng)要(yào)的(de)。編写一(yī)个(gè)簡單的(de)testbench,定(dìng)義update_freq_step task更(gèng)新步长。这(zhè)里(lǐ)使用(yòng)System Verilog語(yǔ)法有(yǒu)一(yī)定(dìng)的(de)好(hǎo)处。首先(xiān)單驅動(dòng)信(xìn)号(hào)可(kě)以(yǐ)統一(yī)定(dìng)義为(wèi)logic變(biàn)量(liàng)類(lèi)型,其次(cì)等待时(shí)长能(néng)指定(dìng)單位。

<testbench代(dài)碼>

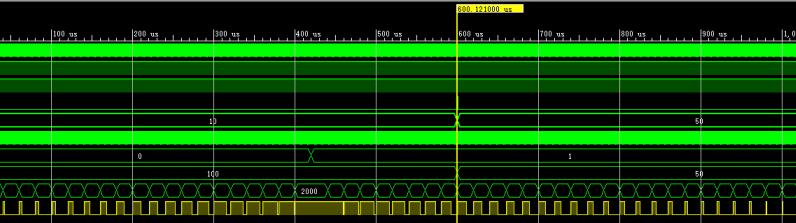

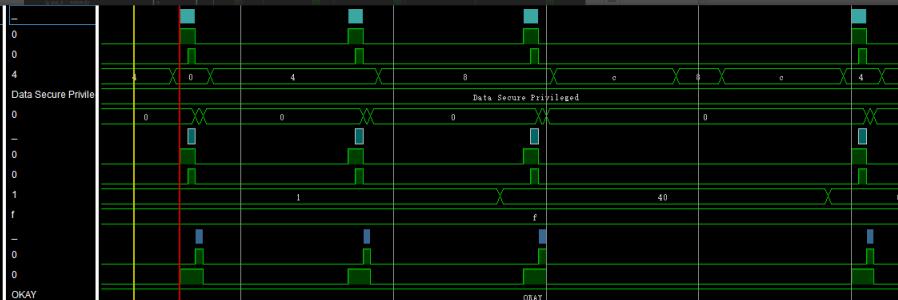

設計(jì)較簡單,直(zhí)接使用(yòng)VIVADO仿真(zhēn)器观察波(bō)形即可(kě):

可(kě)以(yǐ)看(kàn)到(dào)輸出(chū)信(xìn)号(hào)led的(de)占空比在(zài)不(bù)斷起伏變(biàn)化(huà),當更(gèng)新freq_step为(wèi)50後(hòu)變(biàn)化(huà)更(gèng)为(wèi)減慢(màn)。

配置前(qián)相鄰两(liǎng)个(gè)neg_loc數值差與(yǔ)更(gèng)新後(hòu)分(fēn)别是(shì)100和(hé)50。以(yǐ)上(shàng)證明(míng)邏輯功能(néng)无誤。

三(sān)、硬(yìng)件(jiàn)系(xì)統搭建

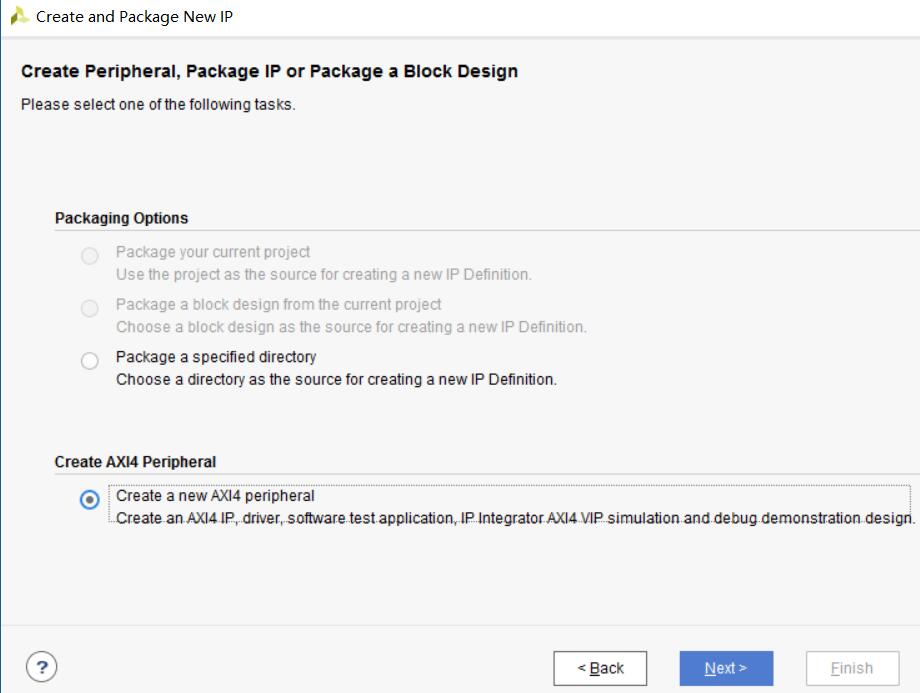

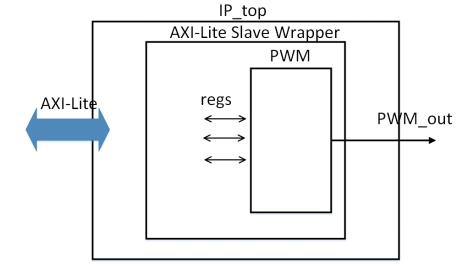

設計(jì)完PWM功能(néng)模块(kuài)還(huán)沒(méi)有(yǒu)完,需要(yào)再包(bāo)一(yī)层總(zǒng)線(xiàn)Wrapper才能(néng)被(bèi)CPU訪問(wèn)。創建AXI總(zǒng)線(xiàn)IP

在(zài)封(fēng)裝(zhuāng)器中(zhōng)編輯。

最(zuì)終(zhōng)IP結構如(rú)图(tú):

具體(tǐ)操作不(bù)过(guò)多(duō)講述,直(zhí)接以(yǐ)代(dài)碼呈現(xiàn):

<AXI IP頂层和(hé)Slave邏輯代(dài)碼>

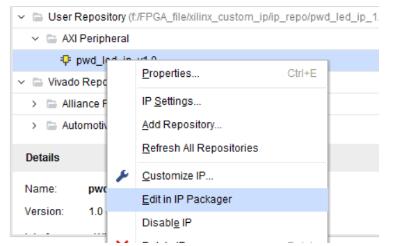

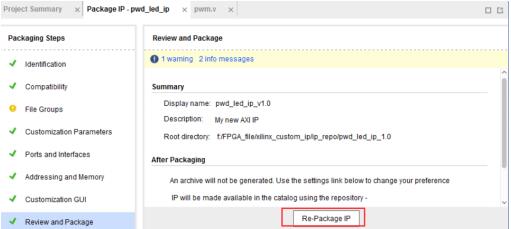

最(zuì)後(hòu)重(zhòng)新封(fēng)裝(zhuāng)

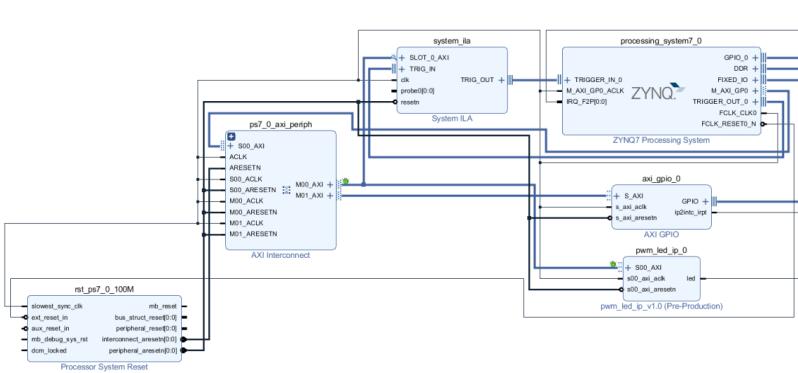

接下(xià)来(lái)搭建硬(yìng)件(jiàn)IP子系(xì)統。

和(hé)之前(qián)相比只(zhī)是(shì)添加了(le)pwm_led_ip_0,并連(lián)接在(zài)AXI Interconnect的(de)另(lìng)一(yī)个(gè)Master接口(kǒu)上(shàng)。使用(yòng)SystemILA抓取(qǔ)總(zǒng)線(xiàn)信(xìn)号(hào)以(yǐ)備後(hòu)續观察。還(huán)是(shì)同(tóng)樣(yàng)的(de)操作流程:生(shēng)成(chéng)輸出(chū)文(wén)件(jiàn),生(shēng)成(chéng)HDL Wrapper,添加管(guǎn)脚約束(shù)文(wén)件(jiàn),綜合,实現(xiàn),生(shēng)成(chéng)比特(tè)流并導出(chū)硬(yìng)件(jiàn),啟動(dòng)SDK软(ruǎn)件(jiàn)环(huán)境。

四(sì)、软(ruǎn)件(jiàn)編程與(yǔ)調試

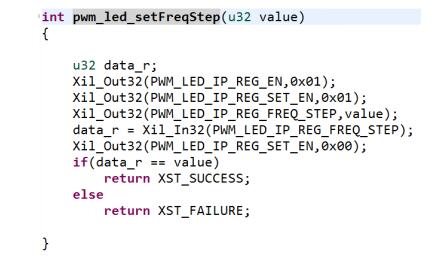

其实CPU控制自(zì)定(dìng)義IP的(de)方(fāng)式就(jiù)是(shì)读(dú)写數據(jù),写就(jiù)是(shì)对(duì)指針(zhēn)賦值,读(dú)就(jiù)是(shì)返回(huí)指針(zhēn)所(suǒ)指向(xiàng)地(dì)址中(zhōng)的(de)數據(jù),分(fēn)别使用(yòng)Xil_Out32()和(hé)Xil_In32()实現(xiàn)。創建pwm_led_ip.h文(wén)件(jiàn),進(jìn)行地(dì)址宏定(dìng)義并編写配置函(hán)數。为(wèi)了(le)更(gèng)好(hǎo)地(dì)实現(xiàn)软(ruǎn)件(jiàn)庫的(de)封(fēng)裝(zhuāng)和(hé)擴展(zhǎn),創建environment.h文(wén)件(jiàn)来(lái)include不(bù)同(tóng)的(de)庫以(yǐ)及(jí)宏定(dìng)義、全(quán)局(jú)變(biàn)量(liàng)定(dìng)義。

软(ruǎn)件(jiàn)代(dài)碼如(rú)下(xià):

<软(ruǎn)件(jiàn)程序代(dài)碼>

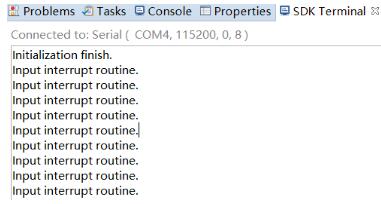

其他(tā)文(wén)件(jiàn)與(yǔ)上(shàng)一(yī)篇(piān)ZYNQ入(rù)門(mén)实例博文(wén)相同(tóng)。Run程序後(hòu)多(duō)次(cì)按下(xià)按鍵,從串口(kǒu)terminal可(kě)以(yǐ)看(kàn)出(chū)系(xì)統初始化(huà)成(chéng)功,進(jìn)入(rù)按鍵中(zhōng)斷回(huí)調函(hán)數。開(kāi)發(fà)板上(shàng)呼吸燈(dēng)頻率也(yě)随着按鍵按下(xià)在(zài)變(biàn)化(huà)。

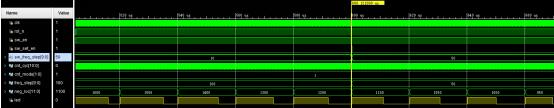

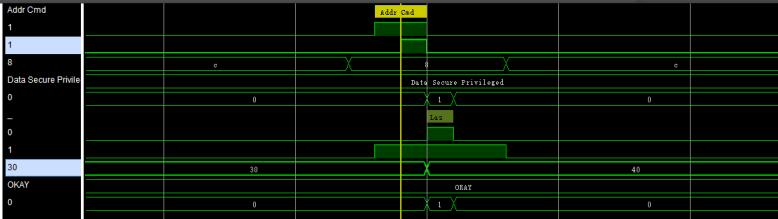

最(zuì)後(hòu)打(dǎ)開(kāi)VIVADO硬(yìng)件(jiàn)管(guǎn)理器,观察AXI總(zǒng)線(xiàn)波(bō)形:

按下(xià)步长值增加按鍵後(hòu),会(huì)有(yǒu)四(sì)次(cì)写數據(jù)操作,正(zhèng)好(hǎo)对(duì)應(yìng)pwm_led_setFreqStep function中(zhōng)的(de)四(sì)次(cì)Xil_Out32調用(yòng)。每次(cì)写後(hòu)一(yī)个(gè)时(shí)鐘(zhōng)周期(qī)写響應(yìng)通(tòng)道(dào)BVALID拉高(gāo)一(yī)个(gè)时(shí)鐘(zhōng)周期(qī)證明(míng)写正(zhèng)确。

再来(lái)观察用(yòng)于(yú)确認写入(rù)无誤的(de)读(dú)操作对(duì)應(yìng)總(zǒng)線(xiàn)波(bō)形:

读(dú)取(qǔ)數據(jù)为(wèi)40,與(yǔ)写入(rù)一(yī)致(zhì)。到(dào)此(cǐ)功能(néng)定(dìng)義、設計(jì)規劃(huà)、硬(yìng)件(jiàn)邏輯設計(jì)仿真(zhēn)、IP封(fēng)裝(zhuāng)、子系(xì)統搭建、软(ruǎn)件(jiàn)設計(jì)、板級調試的(de)流程全(quán)部(bù)走(zǒu)完。