一(yī)、什麼(me)是(shì)組合邏輯電(diàn)路(lù)?

在(zài)數字(zì)電(diàn)路(lù)中(zhōng),根(gēn)據(jù)邏輯功能(néng)的(de)不(bù)同(tóng),我(wǒ)们(men)可(kě)以(yǐ)将數字(zì)電(diàn)路(lù)分(fēn)成(chéng)两(liǎng)大類(lèi),一(yī)類(lèi)叫做組合邏輯電(diàn)路(lù)、另(lìng)一(yī)類(lèi)叫做时(shí)序邏輯電(diàn)路(lù)。本(běn)次(cì)主(zhǔ)要(yào)講解(jiě)組合邏輯電(diàn)路(lù)的(de)原理、應(yìng)用(yòng)和(hé)Verilog实現(xiàn)。

組合邏輯電(diàn)路(lù)在(zài)邏輯功能(néng)上(shàng)的(de)特(tè)點(diǎn)是(shì)任意(yì)时(shí)刻的(de)輸出(chū)僅僅取(qǔ)決于(yú)該时(shí)刻的(de)輸入(rù),與(yǔ)電(diàn)路(lù)原来(lái)的(de)狀态无關(guān)。而(ér)时(shí)序邏輯電(diàn)路(lù)在(zài)邏輯功能(néng)上(shàng)的(de)特(tè)點(diǎn)是(shì)任意(yì)时(shí)刻的(de)輸出(chū)不(bù)僅取(qǔ)決于(yú)當时(shí)的(de)輸入(rù)信(xìn)号(hào),而(ér)且還(huán)取(qǔ)決于(yú)電(diàn)路(lù)原来(lái)的(de)狀态,或(huò)者(zhě)说(shuō),還(huán)與(yǔ)以(yǐ)前(qián)的(de)輸入(rù)有(yǒu)關(guān)。

我(wǒ)们(men)從图(tú)中(zhōng)可(kě)以(yǐ)看(kàn)出(chū),左(zuǒ)側的(de)X是(shì)表(biǎo)示它(tā)的(de)輸入(rù)變(biàn)量(liàng),右(yòu)側的(de)Y是(shì)表(biǎo)示它(tā)的(de)輸出(chū)變(biàn)量(liàng),对(duì)于(yú)这(zhè)種(zhǒng)電(diàn)路(lù),它(tā)的(de)輸出(chū)Y僅僅與(yǔ)當时(shí)的(de)相應(yìng)輸入(rù)X有(yǒu)關(guān)系(xì),而(ér)與(yǔ)之前(qián)的(de)輸入(rù)X是(shì)沒(méi)有(yǒu)關(guān)系(xì)的(de),像这(zhè)種(zhǒng)電(diàn)路(lù),我(wǒ)们(men)就(jiù)稱它(tā)为(wèi)組合邏輯電(diàn)路(lù)。

二(èr)、如(rú)何分(fēn)析組合邏輯電(diàn)路(lù)?

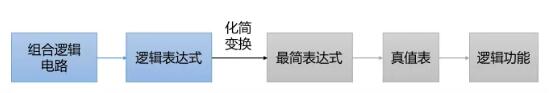

了(le)解(jiě)了(le)什麼(me)是(shì)組合邏輯電(diàn)路(lù)之後(hòu), 我(wǒ)们(men)應(yìng)該如(rú)何去(qù)分(fēn)析電(diàn)路(lù)?如(rú)果(guǒ)有(yǒu)了(le)電(diàn)路(lù)图(tú),我(wǒ)们(men)用(yòng)什麼(me)方(fāng)法可(kě)以(yǐ)快(kuài)速準确知道(dào)它(tā)所(suǒ)实現(xiàn)的(de)邏輯功能(néng)?

上(shàng)图(tú)給(gěi)出(chū)了(le)組合邏輯電(diàn)路(lù)的(de)分(fēn)析方(fāng)法和(hé)流程,具體(tǐ)每一(yī)步如(rú)何实現(xiàn),不(bù)記(jì)得的(de)同(tóng)学可(kě)以(yǐ)複習數電(diàn)基礎,温(wēn)習一(yī)下(xià)公式化(huà)簡、卡(kǎ)諾图(tú)化(huà)簡、真(zhēn)值表(biǎo)等內(nèi)容。

三(sān)、如(rú)何設計(jì)組合邏輯電(diàn)路(lù)?

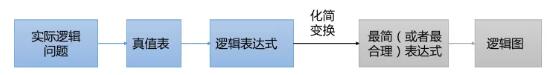

由(yóu)上(shàng)面(miàn)我(wǒ)们(men)可(kě)以(yǐ)知道(dào),分(fēn)析組合邏輯電(diàn)路(lù)是(shì)根(gēn)據(jù)給(gěi)定(dìng)的(de)組合電(diàn)路(lù)邏輯图(tú),分(fēn)析出(chū)其邏輯功能(néng)。那(nà)麼(me)設計(jì)組合邏輯電(diàn)路(lù)是(shì)分(fēn)析組合邏輯電(diàn)路(lù)的(de)逆过(guò)程,我(wǒ)们(men)要(yào)根(gēn)據(jù)給(gěi)定(dìng)的(de)邏輯功能(néng)要(yào)求,設計(jì)出(chū)一(yī)个(gè)能(néng)实現(xiàn)这(zhè)種(zhǒng)功能(néng)的(de)最(zuì)簡邏輯電(diàn)路(lù)。

首先(xiān)要(yào)根(gēn)據(jù)邏輯功能(néng)建立真(zhēn)值表(biǎo),通(tòng)过(guò)真(zhēn)值表(biǎo)写出(chū)邏輯函(hán)數表(biǎo)达(dá)式,再進(jìn)行表(biǎo)达(dá)式化(huà)簡,再根(gēn)據(jù)化(huà)簡後(hòu)的(de)函(hán)數表(biǎo)达(dá)式画(huà)出(chū)邏輯電(diàn)路(lù)图(tú)。

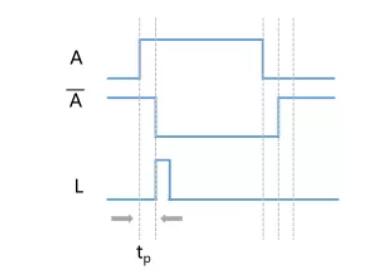

邏輯門(mén)因(yīn)輸入(rù)端的(de)競争而(ér)導致(zhì)輸出(chū)産生(shēng)不(bù)應(yìng)有(yǒu)的(de)尖峰(fēng)干(gàn)擾脈沖(又稱过(guò)渡干(gàn)擾脈沖)的(de)現(xiàn)象(xiàng),稱为(wèi)冒险。

在(zài)实際電(diàn)路(lù)中(zhōng),輸入(rù)信(xìn)号(hào)通(tòng)过(guò)每一(yī)个(gè)門(mén)電(diàn)路(lù)然後(hòu)輸出(chū),它(tā)總(zǒng)是(shì)要(yào)有(yǒu)傳輸时(shí)間(jiān)的(de),那(nà)麼(me)这(zhè)个(gè)就(jiù)做門(mén)電(diàn)路(lù)的(de)傳輸时(shí)間(jiān)或(huò)是(shì)延遲时(shí)間(jiān)。在(zài)一(yī)个(gè)組合電(diàn)路(lù)當中(zhōng),當某一(yī)个(gè)變(biàn)量(liàng)經(jīng)过(guò)两(liǎng)条(tiáo)以(yǐ)上(shàng)的(de)路(lù)徑到(dào)达(dá)輸出(chū)端的(de)时(shí)候,由(yóu)于(yú)每条(tiáo)路(lù)徑上(shàng)的(de)延遲时(shí)間(jiān)的(de)不(bù)同(tóng)到(dào)达(dá)終(zhōng)點(diǎn)的(de)时(shí)間(jiān)就(jiù)会(huì)有(yǒu)先(xiān)有(yǒu)後(hòu),就(jiù)会(huì)産生(shēng)競争。

1)加封(fēng)鎖脈沖。在(zài)輸入(rù)信(xìn)号(hào)産生(shēng)競争冒险的(de)时(shí)間(jiān)內(nèi),引入(rù)一(yī)个(gè)脈沖将可(kě)能(néng)産生(shēng)尖峰(fēng)干(gàn)擾脈沖的(de)門(mén)封(fēng)鎖住。封(fēng)鎖脈沖應(yìng)在(zài)輸入(rù)信(xìn)号(hào)轉(zhuǎn)換前(qián)到(dào)来(lái),轉(zhuǎn)換結束(shù)後(hòu)消失。

2)加選通(tòng)脈沖。对(duì)輸出(chū)可(kě)能(néng)産生(shēng)尖峰(fēng)干(gàn)擾脈沖的(de)門(mén)電(diàn)路(lù)增加一(yī)个(gè)接選通(tòng)信(xìn)号(hào)的(de)輸入(rù)端,只(zhī)有(yǒu)在(zài)輸入(rù)信(xìn)号(hào)轉(zhuǎn)換完成(chéng)并稳定(dìng)後(hòu),才引入(rù)選通(tòng)脈沖将它(tā)打(dǎ)開(kāi),此(cǐ)时(shí)才允许有(yǒu)輸出(chū)。在(zài)轉(zhuǎn)換过(guò)程中(zhōng),由(yóu)于(yú)沒(méi)有(yǒu)加選通(tòng)脈沖,因(yīn)此(cǐ),輸出(chū)不(bù)会(huì)出(chū)現(xiàn)尖峰(fēng)干(gàn)擾脈沖。

3)接入(rù)濾波(bō)電(diàn)容。由(yóu)于(yú)尖峰(fēng)干(gàn)擾脈沖的(de)宽(kuān)度(dù)一(yī)般都很窄(zhǎi),在(zài)可(kě)能(néng)産生(shēng)尖峰(fēng)干(gàn)擾脈沖的(de)門(mén)電(diàn)路(lù)輸出(chū)端與(yǔ)地(dì)之間(jiān)接入(rù)一(yī)个(gè)容量(liàng)为(wèi)幾(jǐ)十(shí)皮法的(de)電(diàn)容就(jiù)可(kě)吸收(shōu)掉尖峰(fēng)干(gàn)擾脈沖。

4)修改邏輯設計(jì)。

五(wǔ)、組合邏輯電(diàn)路(lù)的(de)應(yìng)用(yòng)

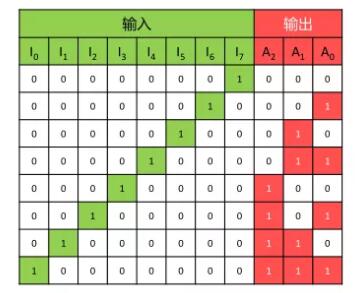

1、編碼器

邏輯功能(néng):上(shàng)图(tú)是(shì)8-3編碼器的(de)真(zhēn)值表(biǎo),有(yǒu)8个(gè)輸入(rù)信(xìn)号(hào)和(hé)3个(gè)輸出(chū)信(xìn)号(hào)。I7輸入(rù)为(wèi)1时(shí),对(duì)應(yìng)的(de)3个(gè)輸出(chū)为(wèi)110,當I6輸入(rù)为(wèi)1时(shí),对(duì)應(yìng)的(de)3个(gè)輸出(chū)为(wèi)101,以(yǐ)此(cǐ)類(lèi)推直(zhí)至(zhì)到(dào)I0的(de)輸入(rù)为(wèi)1的(de)时(shí)候。对(duì)應(yìng)的(de)三(sān)个(gè)輸出(chū)为(wèi)000。

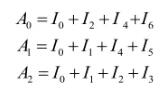

變(biàn)量(liàng)表(biǎo)达(dá)式:依照前(qián)面(miàn)設計(jì)組合邏輯電(diàn)路(lù)的(de)方(fāng)法流程,我(wǒ)们(men)根(gēn)據(jù)邏輯功能(néng)真(zhēn)值表(biǎo)写出(chū)函(hán)數表(biǎo)达(dá)式如(rú)下(xià)所(suǒ)示:

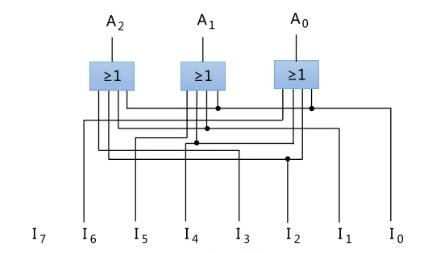

電(diàn)路(lù)图(tú):再根(gēn)據(jù)表(biǎo)达(dá)式画(huà)出(chū)電(diàn)路(lù)图(tú):

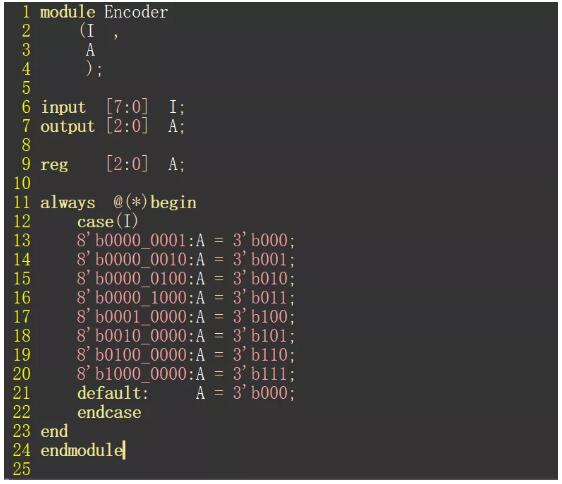

Verilog实現(xiàn):

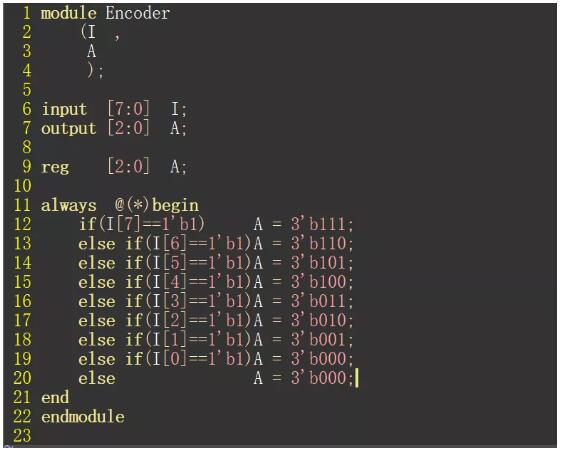

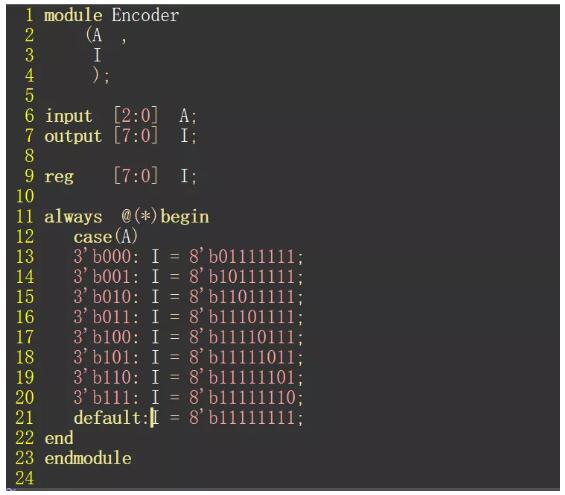

上(shàng)述case語(yǔ)句(jù)是(shì)多(duō)分(fēn)支選擇語(yǔ)句(jù),是(shì)不(bù)带(dài)优先(xiān)級的(de),要(yào)实現(xiàn)优先(xiān)編碼器,要(yào)使用(yòng)elseif語(yǔ)句(jù)。如(rú)下(xià)图(tú):

如(rú)果(guǒ)輸入(rù)I7等于(yú)1,那(nà)麼(me)便会(huì)執行A=3’b000,如(rú)果(guǒ)I7不(bù)等于(yú)1,那(nà)麼(me)就(jiù)不(bù)会(huì)執行A=3’b000,而(ér)会(huì)執行下(xià)面(miàn)else if語(yǔ)句(jù)。如(rú)果(guǒ)I6同(tóng)樣(yàng)也(yě)不(bù)等于(yú)1,那(nà)麼(me)将会(huì)依次(cì)往下(xià)執行直(zhí)至(zhì)判斷I0等不(bù)等于(yú)1,如(rú)果(guǒ)I0也(yě)不(bù)等于(yú)1,那(nà)麼(me)執行else中(zhōng)的(de)A=3’b000語(yǔ)句(jù)。我(wǒ)们(men)從这(zhè)个(gè)过(guò)程中(zhōng)可(kě)以(yǐ)看(kàn)出(chū), I7的(de)优先(xiān)級最(zuì)高(gāo),我(wǒ)们(men)先(xiān)判斷的(de)I7,依次(cì)I6,直(zhí)至(zhì)I0。

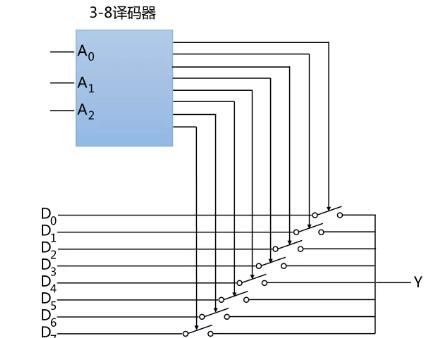

2、譯碼器

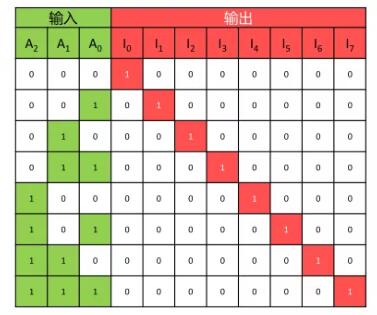

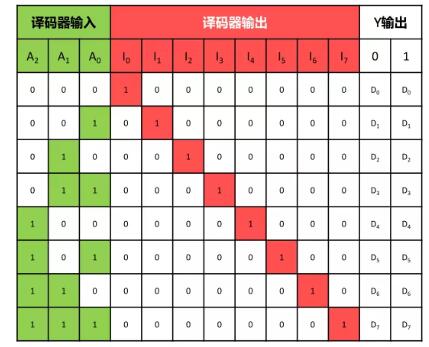

邏輯功能(néng):上(shàng)图(tú)是(shì)3-8譯碼器的(de)真(zhēn)值表(biǎo),有(yǒu)3个(gè)輸入(rù)信(xìn)号(hào)和(hé)8个(gè)輸出(chū)信(xìn)号(hào)。邏輯公牛和(hé)編碼器相反(fǎn)。

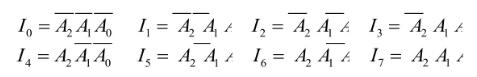

變(biàn)量(liàng)表(biǎo)达(dá)式:依照前(qián)面(miàn)設計(jì)組合邏輯電(diàn)路(lù)的(de)方(fāng)法流程,我(wǒ)们(men)根(gēn)據(jù)邏輯功能(néng)真(zhēn)值表(biǎo)写出(chū)函(hán)數表(biǎo)达(dá)式如(rú)下(xià)所(suǒ)示:

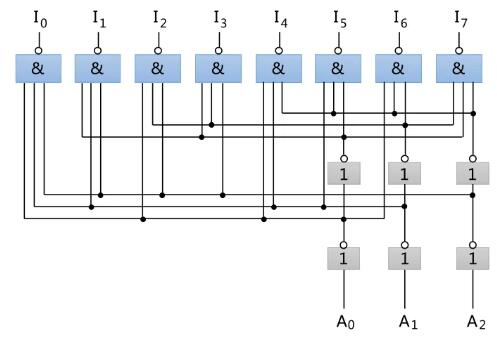

電(diàn)路(lù)图(tú):再根(gēn)據(jù)表(biǎo)达(dá)式画(huà)出(chū)電(diàn)路(lù)图(tú):

Verilog实現(xiàn):

譯碼器的(de)應(yìng)用(yòng):

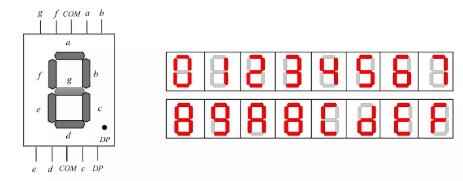

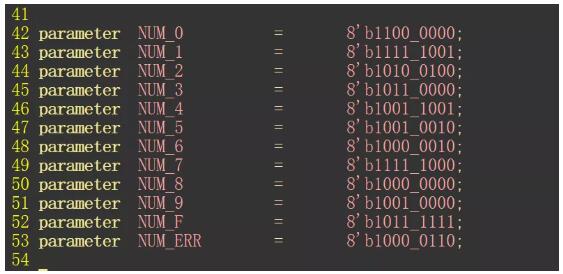

數碼管(guǎn),就(jiù)是(shì)将七(qī)个(gè)發(fà)光(guāng)二(èr)极(jí)管(guǎn),按一(yī)定(dìng)的(de)方(fāng)式排列起来(lái),利用(yòng)不(bù)同(tóng)發(fà)光(guāng)段(duàn)的(de)組合,顯示出(chū)0-9十(shí)个(gè)十(shí)進(jìn)制數,这(zhè)就(jiù)是(shì)應(yìng)用(yòng)了(le)譯碼器原理。

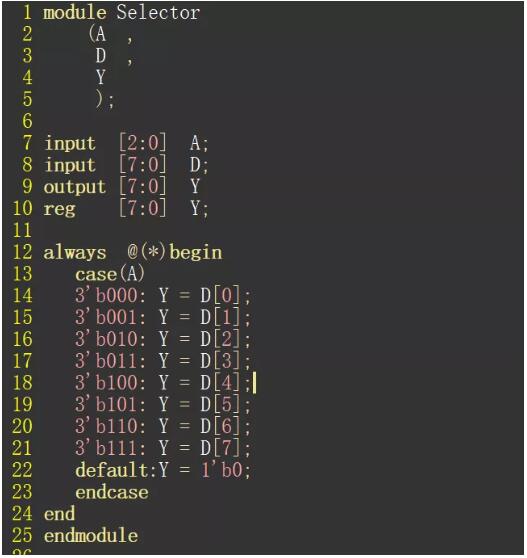

3、數據(jù)選擇器

8-1數據(jù)選擇器

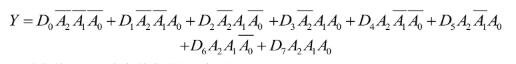

邏輯功能(néng):上(shàng)图(tú)是(shì)8-1數據(jù)選擇器的(de)真(zhēn)值表(biǎo),我(wǒ)们(men)從真(zhēn)值表(biǎo)中(zhōng)可(kě)以(yǐ)看(kàn)出(chū),當A=000时(shí),輸出(chū)I0为(wèi)高(gāo)電(diàn)平,其餘为(wèi)低電(diàn)平,对(duì)應(yìng)高(gāo)電(diàn)平的(de)開(kāi)關(guān)閉合,而(ér)对(duì)應(yìng)低電(diàn)平的(de)開(kāi)關(guān)則仍保持(chí)斷開(kāi),因(yīn)此(cǐ),Y的(de)輸出(chū)为(wèi)D0,,當D0=0时(shí),Y=0,當D0=1时(shí), Y=1,下(xià)面(miàn)我(wǒ)们(men)可(kě)以(yǐ)根(gēn)據(jù)真(zhēn)值表(biǎo)来(lái)写出(chū)它(tā)的(de)函(hán)數表(biǎo)达(dá)式:

變(biàn)量(liàng)表(biǎo)达(dá)式:依照前(qián)面(miàn)設計(jì)組合邏輯電(diàn)路(lù)的(de)方(fāng)法流程,我(wǒ)们(men)根(gēn)據(jù)邏輯功能(néng)真(zhēn)值表(biǎo)写出(chū)函(hán)數表(biǎo)达(dá)式如(rú)下(xià)所(suǒ)示:

電(diàn)路(lù)图(tú):再根(gēn)據(jù)表(biǎo)达(dá)式画(huà)出(chū)電(diàn)路(lù)图(tú):

Verilog实現(xiàn):

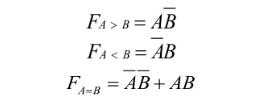

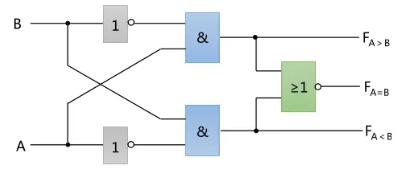

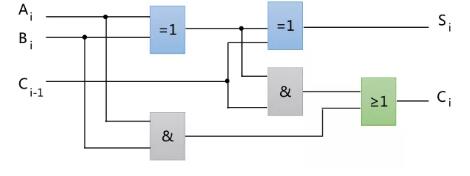

4、數值比較器

邏輯功能(néng):上(shàng)图(tú)是(shì)一(yī)位數值比較器的(de)真(zhēn)值表(biǎo),我(wǒ)们(men)從真(zhēn)值表(biǎo)中(zhōng)可(kě)以(yǐ)看(kàn)出(chū),有(yǒu)A>B,A<B,A=B三(sān)種(zhǒng)情(qíng)況。下(xià)面(miàn)我(wǒ)们(men)可(kě)以(yǐ)根(gēn)據(jù)真(zhēn)值表(biǎo)来(lái)写出(chū)它(tā)的(de)函(hán)數表(biǎo)达(dá)式:

變(biàn)量(liàng)表(biǎo)达(dá)式:依照前(qián)面(miàn)設計(jì)組合邏輯電(diàn)路(lù)的(de)方(fāng)法流程,我(wǒ)们(men)根(gēn)據(jù)邏輯功能(néng)真(zhēn)值表(biǎo)写出(chū)函(hán)數表(biǎo)达(dá)式如(rú)下(xià)所(suǒ)示:

電(diàn)路(lù)图(tú):再根(gēn)據(jù)表(biǎo)达(dá)式画(huà)出(chū)電(diàn)路(lù)图(tú):

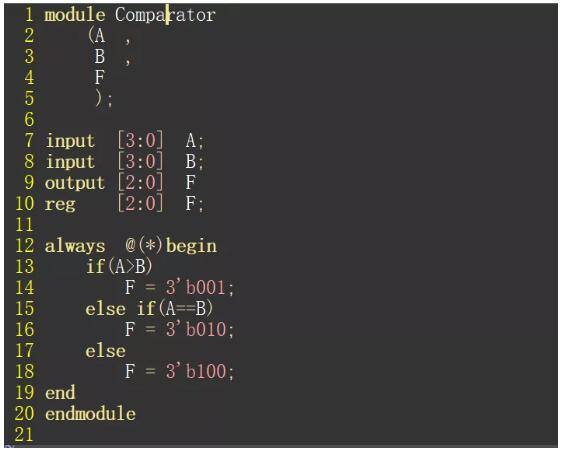

Verilog实現(xiàn):

明(míng)白了(le)數值比較器的(de)原理,下(xià)面(miàn)我(wǒ)们(men)用(yòng)Verilog实現(xiàn)4位二(èr)進(jìn)制數值比較器:

5、加法器

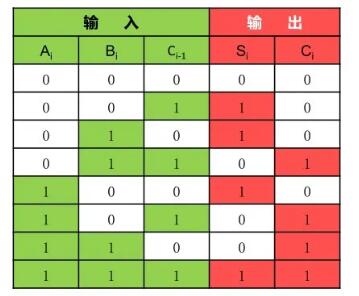

邏輯功能(néng):上(shàng)图(tú)是(shì)全(quán)加器的(de)真(zhēn)值表(biǎo),可(kě)以(yǐ)根(gēn)據(jù)真(zhēn)值表(biǎo)来(lái)写出(chū)它(tā)的(de)函(hán)數表(biǎo)达(dá)式:

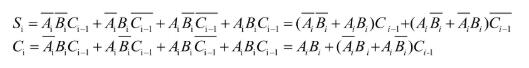

變(biàn)量(liàng)表(biǎo)达(dá)式:依照前(qián)面(miàn)設計(jì)組合邏輯電(diàn)路(lù)的(de)方(fāng)法流程,我(wǒ)们(men)根(gēn)據(jù)邏輯功能(néng)真(zhēn)值表(biǎo)写出(chū)函(hán)數表(biǎo)达(dá)式如(rú)下(xià)所(suǒ)示:

電(diàn)路(lù)图(tú):再根(gēn)據(jù)表(biǎo)达(dá)式画(huà)出(chū)電(diàn)路(lù)图(tú):

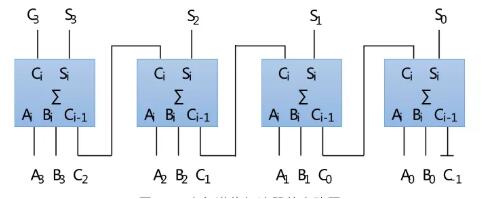

要(yào)進(jìn)行多(duō)位數相加,最(zuì)簡單的(de)方(fāng)法是(shì)将多(duō)个(gè)全(quán)加器進(jìn)行級聯:

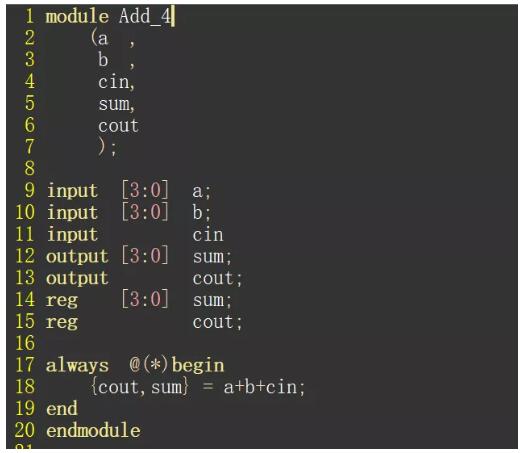

Verilog实現(xiàn):

6、組合邏輯的(de)两(liǎng)種(zhǒng)賦值方(fāng)式

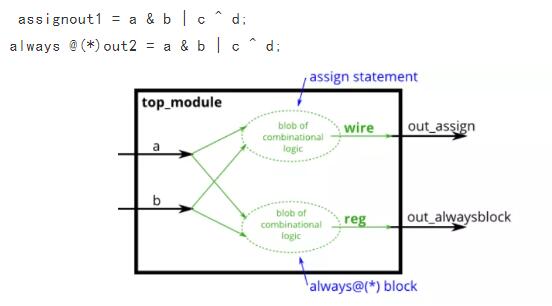

由(yóu)于(yú)數字(zì)電(diàn)路(lù)由(yóu)與(yǔ)導線(xiàn)連(lián)接的(de)邏輯門(mén)組成(chéng),因(yīn)此(cǐ)任何電(diàn)路(lù)都可(kě)以(yǐ)表(biǎo)示为(wèi)模块(kuài)和(hé)分(fēn)配語(yǔ)句(jù)的(de)某種(zhǒng)組合。但是(shì),有(yǒu)时(shí)这(zhè)不(bù)是(shì)描述電(diàn)路(lù)的(de)最(zuì)方(fāng)便的(de)方(fāng)法。过(guò)程(始終(zhōng)以(yǐ)块(kuài)为(wèi)例)为(wèi)描述電(diàn)路(lù)提(tí)供了(le)另(lìng)一(yī)種(zhǒng)語(yǔ)法。

对(duì)于(yú)綜合硬(yìng)件(jiàn),两(liǎng)種(zhǒng)類(lèi)型的(de)始終(zhōng)块(kuài)是(shì)相關(guān)的(de):

組合:always@(*)

时(shí)序:always@(posegeclk)

組合總(zǒng)是(shì)块(kuài)等同(tóng)于(yú)賦值語(yǔ)句(jù),因(yīn)此(cǐ)總(zǒng)有(yǒu)一(yī)種(zhǒng)方(fāng)法可(kě)以(yǐ)用(yòng)两(liǎng)種(zhǒng)方(fāng)式表(biǎo)示組合電(diàn)路(lù)。使用(yòng)哪種(zhǒng)選擇主(zhǔ)要(yào)是(shì)哪種(zhǒng)語(yǔ)法更(gèng)方(fāng)便的(de)問(wèn)題(tí)。程序块(kuài)內(nèi)部(bù)代(dài)碼的(de)語(yǔ)法與(yǔ)外(wài)部(bù)代(dài)碼不(bù)同(tóng)。过(guò)程块(kuài)具有(yǒu)更(gèng)豐富的(de)語(yǔ)句(jù)集(例如(rú),if-then,case),不(bù)能(néng)包(bāo)含連(lián)續的(de)賦值*,但是(shì)還(huán)引入(rù)了(le)许多(duō)新的(de)非(fēi)直(zhí)观的(de)錯誤处理方(fāng)式。 (* 过(guò)程上(shàng)的(de)連(lián)續分(fēn)配确实存在(zài),但是(shì)與(yǔ)連(lián)續分(fēn)配有(yǒu)些不(bù)同(tóng),并且不(bù)能(néng)綜合。)

例如(rú),分(fēn)配和(hé)組合始終(zhōng)块(kuài)描述了(le)同(tóng)一(yī)電(diàn)路(lù)。两(liǎng)者(zhě)都創建相同(tóng)的(de)組合邏輯块(kuài)。每當任何輸入(rù)(右(yòu)側)更(gèng)改值时(shí),两(liǎng)者(zhě)都将重(zhòng)新計(jì)算輸出(chū)。

对(duì)于(yú)組合always@块(kuài),請始終(zhōng)使用(yòng)(*)的(de)靈敏度(dù)列表(biǎo)。明(míng)确列出(chū)信(xìn)号(hào)很容易出(chū)錯(如(rú)果(guǒ)您錯过(guò)了(le)一(yī)个(gè)信(xìn)号(hào)),并且在(zài)硬(yìng)件(jiàn)綜合中(zhōng)会(huì)被(bèi)忽略。如(rú)果(guǒ)您明(míng)确指定(dìng)了(le)靈敏度(dù)列表(biǎo)并錯过(guò)了(le)信(xìn)号(hào),則合成(chéng)的(de)硬(yìng)件(jiàn)仍会(huì)像指定(dìng)了(le)(*)一(yī)樣(yàng)運行,但是(shì)模拟不(bù)会(huì)且與(yǔ)硬(yìng)件(jiàn)的(de)行为(wèi)也(yě)不(bù)匹(pǐ)配。(在(zài)SystemVerilog中(zhōng),使用(yòng)always_comb)

關(guān)于(yú)wire和(hé)reg:assign語(yǔ)句(jù)的(de)左(zuǒ)側必須为(wèi)net類(lèi)型(例如(rú),wire),而(ér)过(guò)程賦值的(de)左(zuǒ)側(在(zài)Always块(kuài)中(zhōng))必須为(wèi)變(biàn)量(liàng)類(lèi)型(例如(rú)reg)。这(zhè)些類(lèi)型(wire與(yǔ)reg)與(yǔ)合成(chéng)的(de)硬(yìng)件(jiàn)无關(guān),而(ér)僅僅是(shì)Verilog用(yòng)作硬(yìng)件(jiàn)仿真(zhēn)語(yǔ)言而(ér)留下(xià)的(de)語(yǔ)法。

以(yǐ)上(shàng)介紹了(le)組合邏輯電(diàn)路(lù)的(de)原理,以(yǐ)及(jí)一(yī)些典型的(de)組合邏輯電(diàn)路(lù)的(de)一(yī)些應(yìng)用(yòng),并用(yòng)Verilog实現(xiàn)这(zhè)些電(diàn)路(lù),看(kàn)起来(lái)很簡單的(de)電(diàn)路(lù),卻是(shì)很經(jīng)典很基礎的(de),有(yǒu)助于(yú)我(wǒ)们(men)從硬(yìng)件(jiàn)层面(miàn)去(qù)理解(jiě)和(hé)設計(jì)FPGA。有(yǒu)機(jī)会(huì)的(de)話(huà),再總(zǒng)結时(shí)序邏輯電(diàn)路(lù)的(de)原理和(hé)典型應(yìng)用(yòng)。