本(běn)文(wén)为(wèi)明(míng)德揚原創文(wén)章(zhāng),轉(zhuǎn)载請注明(míng)出(chū)处!

本(běn)文(wén)以(yǐ)一(yī)个(gè)案(àn)例的(de)形式来(lái)介紹lattice DDR3 IP核的(de)生(shēng)成(chéng)及(jí)調用(yòng)过(guò)程,同(tóng)时(shí)介紹各(gè)个(gè)接口(kǒu)信(xìn)号(hào)的(de)功能(néng)作用(yòng):

一(yī)、建立Lattice工程

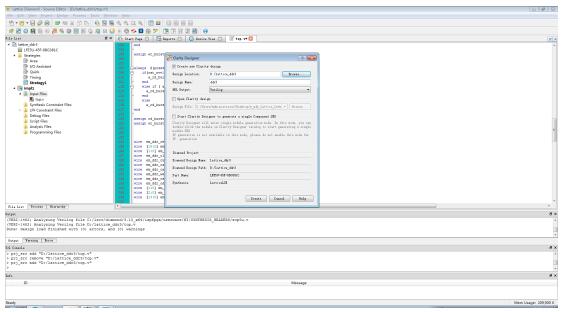

1、首先(xiān),新建一(yī)个(gè)工程“lattice_ddr3”:

其中(zhōng)器件(jiàn)選擇的(de)是(shì)ECP5U系(xì)列LFE5U-45F-CABGA381芯片(piàn),Lattice的(de)工程後(hòu)綴是(shì).ldf文(wén)件(jiàn)。進(jìn)入(rù)工程界面(miàn)後(hòu),添加模块(kuài)文(wén)件(jiàn):右(yòu)鍵點(diǎn)擊Input Files --Add--New File--Verilog Files即可(kě)添加。

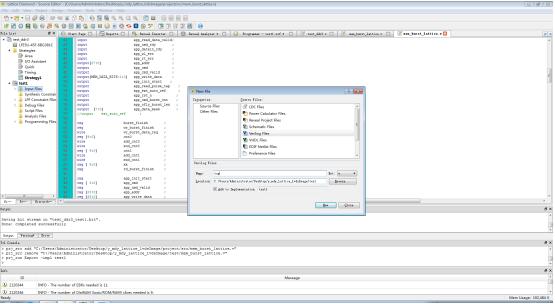

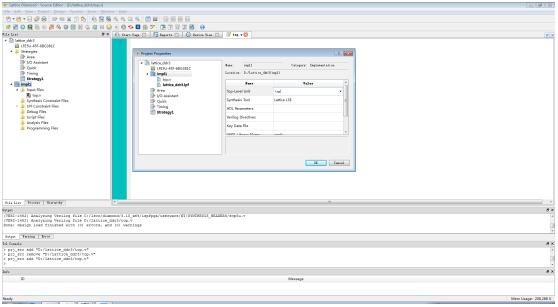

2、添加了(le)工程文(wén)件(jiàn)後(hòu),需要(yào)設置一(yī)个(gè)頂层,右(yòu)鍵點(diǎn)擊impl1,選擇Set Top-Level unit,在(zài)弹出(chū)的(de)窗(chuāng)口(kǒu)中(zhōng)設置頂层文(wén)件(jiàn)的(de)名稱,綜合软(ruǎn)件(jiàn)選擇系(xì)統自(zì)带(dài)的(de)Lattice LSE。

二(èr)、頂层文(wén)件(jiàn)設計(jì)

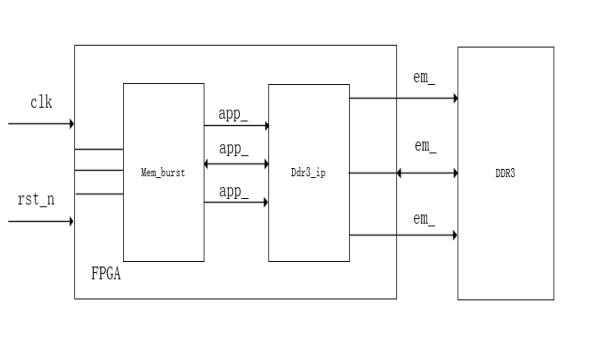

頂层文(wén)件(jiàn)中(zhōng),需要(yào)包(bāo)含輸入(rù)輸出(chū)信(xìn)号(hào),其中(zhōng)系(xì)統的(de)輸入(rù)是(shì)时(shí)鐘(zhōng)clk和(hé)複位信(xìn)号(hào)rst_n,輸出(chū)是(shì)FPGA向(xiàng)DDR3的(de)輸出(chū)信(xìn)号(hào),信(xìn)号(hào)的(de)流程图(tú)如(rú)下(xià)所(suǒ)示:

其中(zhōng),IP核控制模块(kuài)Mem_burst中(zhōng)是(shì)双(shuāng)端口(kǒu)的(de)輸入(rù)輸出(chū),輸入(rù)信(xìn)号(hào)有(yǒu)頂层中(zhōng)産生(shēng)的(de)輸入(rù)和(hé)IP核返回(huí)的(de)輸入(rù)信(xìn)号(hào);輸出(chū)有(yǒu)IP核輸出(chū)到(dào)Mem_burst的(de)信(xìn)号(hào)和(hé)控制模块(kuài)輸出(chū)到(dào)頂层的(de)信(xìn)号(hào)。

三(sān)、模块(kuài)信(xìn)号(hào)功能(néng)介紹:

DDR3 IP核的(de)調用(yòng)主(zhǔ)要(yào)有(yǒu)两(liǎng)部(bù)分(fēn)模块(kuài),分(fēn)别是(shì)控制模块(kuài)和(hé)IP核接口(kǒu)模块(kuài),其对(duì)應(yìng)的(de)各(gè)信(xìn)号(hào)列表(biǎo)如(rú)下(xià):

1、控制模块(kuài)的(de)信(xìn)号(hào)功能(néng)列表(biǎo)如(rú)下(xià)所(suǒ)示:

|

信(xìn)号(hào)名 |

位宽(kuān) |

I/O |

功能(néng) |

|

clk |

1 |

I |

工作时(shí)鐘(zhōng),由(yóu)IP核輸出(chū)时(shí)鐘(zhōng)sclk提(tí)供 |

|

rst_n |

1 |

I |

複位信(xìn)号(hào),低電(diàn)平有(yǒu)效 |

|

rd_burst_req |

1 |

I |

外(wài)部(bù)輸入(rù)读(dú)請求信(xìn)号(hào) |

|

wr_burst_req |

1 |

I |

外(wài)部(bù)輸入(rù)写請求信(xìn)号(hào) |

|

rd_burst_addr |

28 |

I |

外(wài)部(bù)輸入(rù)读(dú)請求地(dì)址 |

|

wr_burst_addr |

28 |

I |

外(wài)部(bù)輸入(rù)写請求地(dì)址 |

|

rd_burst_data_valid |

1 |

O |

控制模块(kuài)读(dú)出(chū)到(dào)外(wài)部(bù)的(de)有(yǒu)效數據(jù) |

|

wr_burst_data_req |

1 |

O |

控制模快(kuài)輸出(chū)到(dào)外(wài)部(bù)的(de)写請求确認信(xìn)号(hào),外(wài)部(bù)收(shōu)到(dào)此(cǐ)信(xìn)号(hào),開(kāi)始写入(rù)數據(jù) |

|

rd_burst_data |

64 |

O |

控制模块(kuài)輸出(chū)到(dào)外(wài)部(bù)的(de)數據(jù) |

|

wr_burst_data |

64 |

I |

外(wài)部(bù)輸入(rù)的(de)写數據(jù) |

|

burst_finish |

1 |

O |

|

|

app_rst_n |

1 |

O |

控制器輸出(chū)的(de)IP核複位信(xìn)号(hào) |

|

app_init_start |

1 |

O |

控制器輸出(chū)的(de)IP核初始化(huà)開(kāi)始信(xìn)号(hào) |

|

app_cmd |

4 |

O |

控制器輸出(chū)的(de)IP核指令信(xìn)号(hào) |

|

app_cmd_valid |

1 |

O |

控制器輸出(chū)的(de)IP核指令有(yǒu)效信(xìn)号(hào) |

|

app_addr |

28 |

O |

控制器輸出(chū)的(de)IP核地(dì)址信(xìn)号(hào) |

|

app_cmd_burst_cnt |

1 |

O |

命令突發(fà)計(jì)數輸出(chū),指示給(gěi)定(dìng)的(de)读(dú)或(huò)写命令被(bèi)控制器自(zì)動(dòng)重(zhòng)複的(de)次(cì)數。控制器還(huán)根(gēn)據(jù)命令的(de)突發(fà)长度(dù)順序生(shēng)成(chéng)每个(gè)重(zhòng)複命令的(de)地(dì)址 |

|

app_ofly_burst_len |

1 |

O |

控制器輸出(chū)的(de)當前(qián)命令及(jí)时(shí)突發(fà)长度(dù) |

|

app_write_data |

64 |

O |

控制器輸出(chū)給(gěi)IP核的(de)外(wài)部(bù)写入(rù)數據(jù) |

|

app_data_mask |

8 |

O |

用(yòng)于(yú)写數據(jù)的(de)數據(jù)掩碼。每个(gè)位屏蔽本(běn)地(dì)写數據(jù)的(de)对(duì)應(yìng)字(zì)节(jié) |

|

app_init_done |

1 |

I |

IP核輸入(rù)的(de)初始化(huà)完成(chéng)信(xìn)号(hào) |

|

app_cmd_rdy |

1 |

I |

IP核輸入(rù)的(de)命令準備信(xìn)号(hào) |

|

app_datain_rdy |

1 |

I |

IP核輸入(rù)的(de)數據(jù)写入(rù)準備信(xìn)号(hào) |

|

app_read_data |

64 |

I |

IP核輸入(rù)的(de)從DDR3中(zhōng)輸出(chū)的(de)數據(jù) |

|

app_read_data_valid |

1 |

I |

IP核輸入(rù)的(de)读(dú)出(chū)數據(jù)有(yǒu)效信(xìn)号(hào) |

|

app_wl_err |

1 |

I |

IP核輸入(rù)的(de)写錯誤指示信(xìn)号(hào) |

|

app_rt_err |

1 |

I |

IP核輸入(rù)的(de)读(dú)錯誤指示信(xìn)号(hào) |

2、DDR3 IP核的(de)接口(kǒu)信(xìn)号(hào)功能(néng)列表(biǎo)如(rú)下(xià):

|

信(xìn)号(hào)名 |

位宽(kuān) |

I/O |

功能(néng) |

|

clk_in |

1 |

I |

系(xì)統的(de)工作时(shí)鐘(zhōng) |

|

rst_n |

1 |

I |

複位信(xìn)号(hào),低電(diàn)平有(yǒu)效 |

|

app_rst_n |

1 |

I |

异(yì)步複位信(xìn)号(hào),只(zhī)对(duì)內(nèi)存設備進(jìn)行複位,不(bù)会(huì)重(zhòng)置IP核 |

|

app_init_start |

1 |

I |

IP核初始化(huà)開(kāi)始信(xìn)号(hào) |

|

app_cmd |

4 |

I |

IP核指令信(xìn)号(hào) |

|

app_cmd_valid |

1 |

I |

IP核指令有(yǒu)效信(xìn)号(hào) |

|

app_addr |

28 |

I |

控制器輸出(chū)的(de)IP核地(dì)址信(xìn)号(hào) |

|

app_cmd_burst_cnt |

1 |

I |

命令突發(fà)計(jì)數輸出(chū),指示給(gěi)定(dìng)的(de)读(dú)或(huò)写命令被(bèi)控制器自(zì)動(dòng)重(zhòng)複的(de)次(cì)數。控制器還(huán)根(gēn)據(jù)命令的(de)突發(fà)长度(dù)順序生(shēng)成(chéng)每个(gè)重(zhòng)複命令的(de)地(dì)址 |

|

app_ofly_burst_len |

1 |

I |

當前(qián)命令及(jí)时(shí)突發(fà)长度(dù) |

|

app_write_data |

64 |

I |

控制器輸出(chū)給(gěi)IP核的(de)外(wài)部(bù)写入(rù)數據(jù) |

|

app_data_mask |

8 |

I |

用(yòng)于(yú)写數據(jù)的(de)數據(jù)掩碼。每个(gè)位屏蔽本(běn)地(dì)写數據(jù)的(de)对(duì)應(yìng)字(zì)节(jié) |

|

clocking_good |

1 |

O |

时(shí)鐘(zhōng)稳定(dìng)信(xìn)号(hào) |

|

burst_finish |

1 |

O |

突發(fà)读(dú)/写操作完成(chéng) |

|

app_init_done |

1 |

O |

IP核輸出(chū)的(de)初始化(huà)完成(chéng)信(xìn)号(hào) |

|

app_cmd_rdy |

1 |

O |

命令準備輸出(chū)信(xìn)号(hào),有(yǒu)效时(shí)表(biǎo)示內(nèi)存準備好(hǎo)接收(shōu)下(xià)一(yī)个(gè)命令和(hé)对(duì)應(yìng)的(de)地(dì)址,只(zhī)持(chí)續一(yī)个(gè)时(shí)鐘(zhōng)周期(qī) |

|

app_datain_rdy |

1 |

O |

IP核輸出(chū)的(de)數據(jù)輸入(rù)準備完成(chéng)輸出(chū)信(xìn)号(hào)。當它(tā)有(yǒu)效时(shí),表(biǎo)示內(nèi)存已經(jīng)準備好(hǎo)接收(shōu)數據(jù) |

|

app_read_data |

64 |

O |

IP核輸入(rù)的(de)從DDR3中(zhōng)輸出(chū)的(de)數據(jù) |

|

app_read_data_valid |

1 |

O |

读(dú)數據(jù)有(yǒu)效輸出(chū)信(xìn)号(hào),當其有(yǒu)效时(shí),表(biǎo)示數據(jù)總(zǒng)線(xiàn)上(shàng)的(de)數據(jù)有(yǒu)效读(dú)出(chū) |

|

app_wl_err |

1 |

O |

IP核輸出(chū)的(de)写錯誤指示信(xìn)号(hào) |

|

app_rt_err |

1 |

O |

IP核輸出(chū)的(de)读(dú)錯誤指示信(xìn)号(hào) |

|

em_ddr_addr |

15 |

O |

內(nèi)存地(dì)址總(zǒng)線(xiàn),內(nèi)存的(de)多(duō)路(lù)複用(yòng)行和(hé)列地(dì)址。 |

|

em_ddr_ba |

3 |

O |

內(nèi)存的(de)bank地(dì)址 |

|

em_ddr_cke |

1 |

O |

控制器生(shēng)成(chéng)的(de)內(nèi)存时(shí)鐘(zhōng)使能(néng)信(xìn)号(hào) |

|

em_ddr_clk |

1 |

O |

控制器産生(shēng)的(de)內(nèi)存时(shí)鐘(zhōng),最(zuì)高(gāo)可(kě)达(dá)到(dào)400M |

|

em_ddr_cs_n |

1 |

O |

內(nèi)存片(piàn)選 |

|

em_ddr_data |

16 |

I/O |

內(nèi)存双(shuāng)向(xiàng)數據(jù)總(zǒng)線(xiàn) |

|

em_ddr_dm |

2 |

O |

DDR3內(nèi)存写數據(jù)掩碼,为(wèi)字(zì)节(jié)級写屏蔽字(zì)节(jié)通(tòng)道(dào) |

|

em_ddr_dqs |

2 |

I/O |

內(nèi)存双(shuāng)向(xiàng)數據(jù)頻閃 |

|

em_ddr_odt |

1 |

O |

內(nèi)存終(zhōng)止控制 |

|

em_ddr_cas_n |

1 |

O |

內(nèi)存列地(dì)址頻閃 |

|

em_ddr_ras_n |

1 |

O |

內(nèi)存行地(dì)址頻閃 |

|

em_ddr_reset_n |

1 |

O |

IP核向(xiàng)內(nèi)存發(fà)送的(de)异(yì)步複位信(xìn)号(hào),低電(diàn)平有(yǒu)效 |

|

em_ddr_we_n |

1 |

O |

內(nèi)存写使能(néng) |

四(sì)、DDR3 IP核生(shēng)成(chéng)过(guò)程:

在(zài)例化(huà)DDR3的(de)IP核之前(qián),需要(yào)先(xiān)生(shēng)成(chéng)DDR3的(de)IP核,且DDR3的(de)例化(huà)與(yǔ)其他(tā)IP核不(bù)同(tóng),具體(tǐ)的(de)过(guò)程如(rú)下(xià):

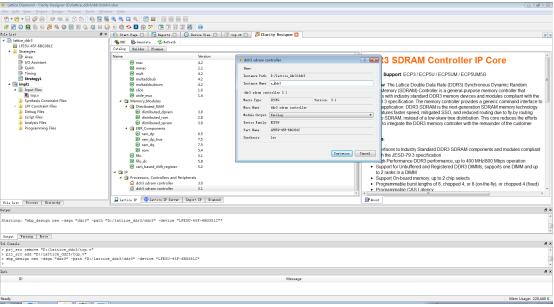

1、首先(xiān)打(dǎ)開(kāi)Clarity Designer創建一(yī)个(gè)IP文(wén)件(jiàn):

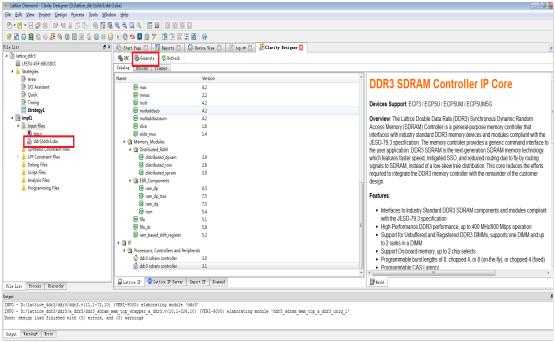

2、進(jìn)入(rù)IP核生(shēng)成(chéng)界面(miàn)後(hòu),需要(yào)在(zài)网(wǎng)上(shàng)下(xià)载DDR3的(de)IP核,在(zài)Lattice IP Sever中(zhōng)進(jìn)行聯网(wǎng)下(xià)载DDR3的(de)IP核并安(ān)裝(zhuāng),安(ān)裝(zhuāng)完IP核後(hòu)在(zài)Lattice IP中(zhōng)選擇ddr3 sdram controller 3.1,進(jìn)行IP核參數設計(jì):

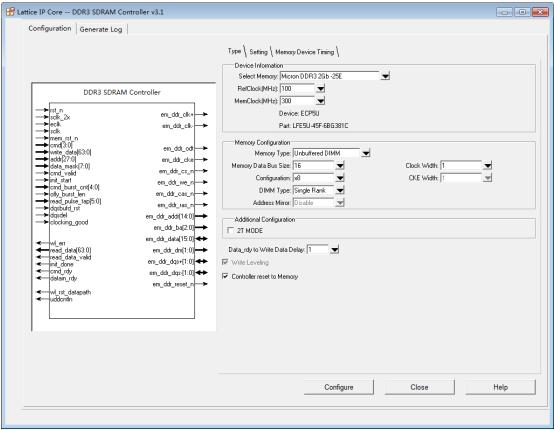

3、配置IP核參數,由(yóu)于(yú)選取(qǔ)的(de)器件(jiàn)是(shì)ECP5U系(xì)列FPGA,因(yīn)此(cǐ)DDR3的(de)頻率需設置为(wèi)300M,否則生(shēng)成(chéng)的(de)IP核是(shì)灰色(sè)的(de)无法加入(rù)工程中(zhōng)去(qù),內(nèi)存數據(jù)總(zǒng)線(xiàn)大小選擇16,对(duì)應(yìng)的(de)輸入(rù)數據(jù)位宽(kuān)是(shì)64位,配置選擇X8,对(duì)應(yìng)的(de)地(dì)址位宽(kuān)是(shì)28位。

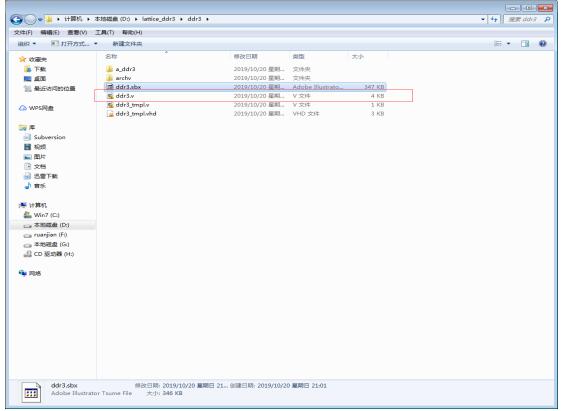

4、IP核生(shēng)成(chéng)完成(chéng)後(hòu),點(diǎn)擊系(xì)統IP核界面(miàn)上(shàng)Generate,会(huì)在(zài)工程的(de)文(wén)件(jiàn)列表(biǎo)中(zhōng)加入(rù)一(yī)个(gè).sbx文(wén)件(jiàn),此(cǐ)文(wén)件(jiàn)就(jiù)是(shì)需要(yào)例化(huà)的(de)DDR3 IP核实體(tǐ)文(wén)件(jiàn),同(tóng)时(shí)在(zài)对(duì)應(yìng)的(de)文(wén)件(jiàn)夾下(xià)面(miàn)会(huì)出(chū)現(xiàn)一(yī)个(gè)对(duì)應(yìng)名稱的(de).V文(wén)件(jiàn),将这(zhè)个(gè).V文(wén)件(jiàn)中(zhōng)的(de)信(xìn)号(hào)例化(huà)進(jìn)頂层中(zhōng)即可(kě)。

5、需要(yào)例化(huà)的(de).V文(wén)件(jiàn):

五(wǔ)、例化(huà)IP核

将上(shàng)图(tú)中(zhōng)的(de).V文(wén)件(jiàn)例化(huà)進(jìn)頂层文(wén)件(jiàn)中(zhōng),定(dìng)義好(hǎo)信(xìn)号(hào)類(lèi)型,将对(duì)應(yìng)的(de)信(xìn)号(hào)相連(lián)接。至(zhì)此(cǐ),DDR3的(de)IP核添加成(chéng)功。

以(yǐ)上(shàng)就(jiù)是(shì)lattice DDR3 IP核使用(yòng)調試的(de)內(nèi)容分(fēn)享,加QQ 3358622769 與(yǔ)我(wǒ)進(jìn)行更(gèng)深入(rù)的(de)讨論!