近(jìn)幾(jǐ)年(nián)来(lái),由(yóu)于(yú)現(xiàn)场可(kě)編程門(mén)阵(zhèn)列(FPGA)的(de)使用(yòng)非(fēi)常靈活,又可(kě)以(yǐ)无限次(cì)的(de)編程,已受到(dào)越来(lái)越多(duō)的(de)電(diàn)子編程者(zhě)的(de)喜爱(ài),很多(duō)朋友都想(xiǎng)学習一(yī)些FPGA入(rù)門(mén)知識準備進(jìn)行这(zhè)个(gè)行業,現(xiàn)在(zài)關(guān)于(yú)FPGA入(rù)門(mén)知識的(de)書(shū)籍、論壇、教程等種(zhǒng)類(lèi)繁多(duō)各(gè)式各(gè)樣(yàng)。下(xià)面(miàn)笔(bǐ)者(zhě)也(yě)通(tòng)过(guò)搜尋一(yī)些關(guān)于(yú)FPGA入(rù)門(mén)知識的(de)資料供大家(jiā)学習和(hé)參考。

FPGA入(rù)門(mén)知識首先(xiān)要(yào)從FPGA的(de)定(dìng)義開(kāi)始,什麼(me)是(shì)FPGA呢,有(yǒu)什麼(me)作用(yòng)这(zhè)些都是(shì)基本(běn)需要(yào)了(le)解(jiě)的(de)東(dōng)西(xī)。FPGA是(shì)可(kě)編程器件(jiàn),目前(qián)以(yǐ)硬(yìng)件(jiàn)描述語(yǔ)言(Verilog 或(huò) VHDL)所(suǒ)完成(chéng)的(de)電(diàn)路(lù)設計(jì),可(kě)以(yǐ)經(jīng)过(guò)簡單的(de)綜合與(yǔ)布(bù)局(jú),快(kuài)速的(de)燒录(lù)至(zhì) FPGA 上(shàng)進(jìn)行测試,是(shì)現(xiàn)代(dài) IC 設計(jì)验(yàn)證的(de)技術(shù)主(zhǔ)流。

FPGA入(rù)門(mén)知識還(huán)應(yìng)該包(bāo)含FPGA工作原理、FPGA的(de)基本(běn)特(tè)點(diǎn)、FPGA芯片(piàn)結構等基礎的(de)知識,下(xià)面(miàn)小編從以(yǐ)下(xià)幾(jǐ)个(gè)方(fāng)面(miàn)来(lái)对(duì)FPGA入(rù)門(mén)知識進(jìn)行簡單的(de)介紹。

FPGA工作原理

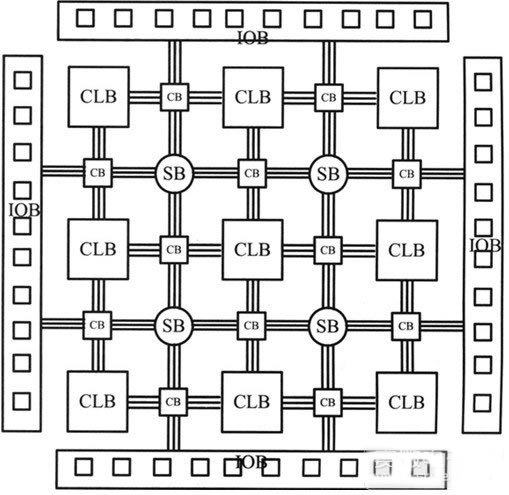

FPGA采用(yòng)了(le)邏輯單元(yuán)阵(zhèn)列LCA这(zhè)樣(yàng)一(yī)个(gè)概念,內(nèi)部(bù)包(bāo)括可(kě)配置邏輯模块(kuài)CLB、輸出(chū)輸入(rù)模块(kuài)IOB和(hé)內(nèi)部(bù)連(lián)線(xiàn)三(sān)个(gè)部(bù)分(fēn)。FPGA利用(yòng)小型查找(zhǎo)表(biǎo)(16×1RAM)来(lái)实現(xiàn)組合邏輯,每个(gè)查找(zhǎo)表(biǎo)連(lián)接到(dào)一(yī)个(gè)D觸發(fà)器的(de)輸入(rù)端,觸發(fà)器再来(lái)驅動(dòng)其他(tā)邏輯電(diàn)路(lù)或(huò)驅動(dòng)I/O,由(yóu)此(cǐ)構成(chéng)了(le)即可(kě)实現(xiàn)組合邏輯功能(néng)又可(kě)实現(xiàn)时(shí)序邏輯功能(néng)的(de)基本(běn)邏輯單元(yuán)模块(kuài),这(zhè)些模块(kuài)間(jiān)利用(yòng)金(jīn)屬連(lián)線(xiàn)互相連(lián)接或(huò)連(lián)接到(dào)I/O模块(kuài)。FPGA的(de)邏輯是(shì)通(tòng)过(guò)向(xiàng)內(nèi)部(bù)静(jìng)态存儲單元(yuán)加载編程數據(jù)来(lái)实現(xiàn)的(de),存儲在(zài)存儲器單元(yuán)中(zhōng)的(de)值決定(dìng)了(le)邏輯單元(yuán)的(de)邏輯功能(néng)以(yǐ)及(jí)各(gè)模块(kuài)之間(jiān)或(huò)模块(kuài)與(yǔ)I/O間(jiān)的(de)聯接方(fāng)式,并最(zuì)終(zhōng)決定(dìng)了(le)FPGA所(suǒ)能(néng)实現(xiàn)的(de)功能(néng), 加電(diàn)时(shí),FPGA芯片(piàn)将EPROM中(zhōng)數據(jù)读(dú)入(rù)片(piàn)內(nèi)編程RAM中(zhōng),配置完成(chéng)後(hòu),FPGA進(jìn)入(rù)工作狀态。掉電(diàn)後(hòu),FPGA恢複成(chéng)白片(piàn),內(nèi)部(bù)邏輯關(guān)系(xì)消失,因(yīn)此(cǐ),FPGA能(néng)够反(fǎn)複使用(yòng)。FPGA的(de)編程无須專用(yòng)的(de)FPGA編程器,只(zhī)須用(yòng)通(tòng)用(yòng)的(de)EPROM、PROM編程器即可(kě)。當需要(yào)修改FPGA功能(néng)时(shí),只(zhī)需換一(yī)片(piàn)EPROM即可(kě)。这(zhè)樣(yàng),同(tóng)一(yī)片(piàn)FPGA,不(bù)同(tóng)的(de)編程數據(jù),可(kě)以(yǐ)産生(shēng)不(bù)同(tóng)的(de)電(diàn)路(lù)功能(néng)。FPGA是(shì)由(yóu)存放(fàng)在(zài)片(piàn)內(nèi)RAM中(zhōng)的(de)程序来(lái)設置其工作狀态的(de),因(yīn)此(cǐ),工作时(shí)需要(yào)对(duì)片(piàn)內(nèi)的(de)RAM進(jìn)行編程。用(yòng)戶可(kě)以(yǐ)根(gēn)據(jù)不(bù)同(tóng)的(de)配置模式,采用(yòng)不(bù)同(tóng)的(de)編程方(fāng)式。

FPGA的(de)基本(běn)特(tè)點(diǎn)

1)采用(yòng)FPGA設計(jì)ASIC電(diàn)路(lù)(專用(yòng)集成(chéng)電(diàn)路(lù)),用(yòng)戶不(bù)需要(yào)投片(piàn)生(shēng)産,就(jiù)能(néng)得到(dào)合用(yòng)的(de)芯片(piàn)。

2)FPGA可(kě)做其它(tā)全(quán)定(dìng)制或(huò)半定(dìng)制ASIC電(diàn)路(lù)的(de)中(zhōng)試樣(yàng)片(piàn)。

3)FPGA內(nèi)部(bù)有(yǒu)豐富的(de)觸發(fà)器和(hé)I/O引脚。

4)FPGA是(shì)ASIC電(diàn)路(lù)中(zhōng)設計(jì)周期(qī)最(zuì)短(duǎn)、開(kāi)發(fà)費用(yòng)最(zuì)低、风险最(zuì)小的(de)器件(jiàn)之一(yī)。

5) FPGA采用(yòng)高(gāo)速CMOS工藝,功耗低,可(kě)以(yǐ)與(yǔ)CMOS、TTL電(diàn)平兼容。

可(kě)以(yǐ)说(shuō),FPGA芯片(piàn)是(shì)小批量(liàng)系(xì)統提(tí)高(gāo)系(xì)統集成(chéng)度(dù)、可(kě)靠性(xìng)的(de)最(zuì)佳選擇之一(yī)。

FPGA芯片(piàn)結構

目前(qián)主(zhǔ)流的(de)FPGA仍是(shì)基于(yú)查找(zhǎo)表(biǎo)技術(shù)的(de),已經(jīng)遠(yuǎn)遠(yuǎn)超出(chū)了(le)先(xiān)前(qián)版本(běn)的(de)基本(běn)性(xìng)能(néng),并且整合了(le)常用(yòng)功能(néng)(如(rú)RAM、时(shí)鐘(zhōng)管(guǎn)理和(hé)DSP)的(de)硬(yìng)核(ASIC型)模块(kuài)。FPGA芯片(piàn)主(zhǔ)要(yào)由(yóu)7部(bù)分(fēn)完成(chéng),分(fēn)别为(wèi):可(kě)編程輸入(rù)輸出(chū)單元(yuán)、基本(běn)可(kě)編程邏輯單元(yuán)、完整的(de)时(shí)鐘(zhōng)管(guǎn)理、嵌入(rù)块(kuài)式RAM、豐富的(de)布(bù)線(xiàn)資源、內(nèi)嵌的(de)底层功能(néng)單元(yuán)和(hé)內(nèi)嵌專用(yòng)硬(yìng)件(jiàn)模块(kuài)。

1. 可(kě)編程輸入(rù)輸出(chū)單元(yuán)(IOB)

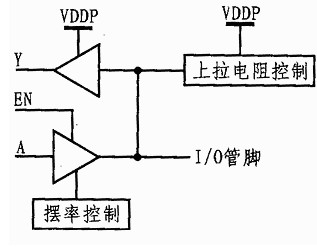

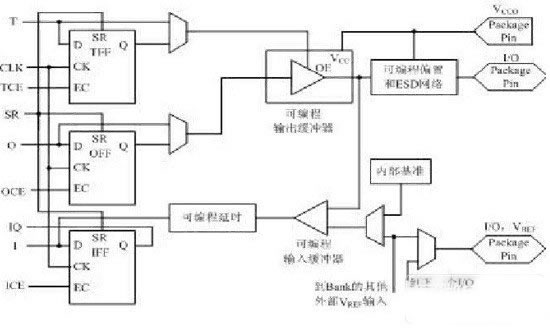

可(kě)編程輸入(rù)/輸出(chū)單元(yuán)簡稱I/O單元(yuán),是(shì)芯片(piàn)與(yǔ)外(wài)界電(diàn)路(lù)的(de)接口(kǒu)部(bù)分(fēn),完成(chéng)不(bù)同(tóng)電(diàn)气(qì)特(tè)性(xìng)下(xià)对(duì)輸入(rù)/輸出(chū)信(xìn)号(hào)的(de)驅動(dòng)與(yǔ)匹(pǐ)配要(yào)求。为(wèi)了(le)便于(yú)管(guǎn)理和(hé)适應(yìng)多(duō)種(zhǒng)電(diàn)器标(biāo)準,FPGA的(de)IOB被(bèi)劃(huà)分(fēn)为(wèi)若干(gàn)个(gè)組(bank),每个(gè)bank的(de)接口(kǒu)标(biāo)準由(yóu)其接口(kǒu)電(diàn)壓VCCO決定(dìng),一(yī)个(gè)bank只(zhī)能(néng)有(yǒu) 一(yī)種(zhǒng)VCCO,但不(bù)同(tóng)bank的(de)VCCO可(kě)以(yǐ)不(bù)同(tóng)。只(zhī)有(yǒu)相同(tóng)電(diàn)气(qì)标(biāo)準的(de)端口(kǒu)才能(néng)連(lián)接在(zài)一(yī)起,VCCO電(diàn)壓相同(tóng)是(shì)接口(kǒu)标(biāo)準的(de)基本(běn)条(tiáo)件(jiàn)。

I/O块(kuài)內(nèi)部(bù)結構图(tú)

典型的(de)IOB內(nèi)部(bù)結構示意(yì)图(tú)

2. 可(kě)配置邏輯块(kuài)(CLB)

CLB是(shì)FPGA內(nèi)的(de)基本(běn)邏輯單元(yuán)。CLB的(de)实際數量(liàng)和(hé)特(tè)性(xìng)会(huì)依器件(jiàn)的(de)不(bù)同(tóng)而(ér)不(bù)同(tóng),但是(shì)每个(gè)CLB都包(bāo)含一(yī)个(gè)可(kě)配置開(kāi)關(guān)矩阵(zhèn),此(cǐ)矩阵(zhèn)由(yóu)4或(huò)6个(gè)輸入(rù)、一(yī)些 選型電(diàn)路(lù)(多(duō)路(lù)複用(yòng)器等)和(hé)觸發(fà)器組成(chéng)。開(kāi)關(guān)矩阵(zhèn)是(shì)高(gāo)度(dù)靈活的(de),可(kě)以(yǐ)对(duì)其進(jìn)行配置以(yǐ)便处理組合邏輯、移位寄存器或(huò)RAM。

4. 嵌入(rù)式块(kuài)RAM(BRAM)

大多(duō)數FPGA都具有(yǒu)內(nèi)嵌的(de)块(kuài)RAM,这(zhè)大大拓展(zhǎn)了(le)FPGA的(de)應(yìng)用(yòng)範圍和(hé)靈活性(xìng)。块(kuài)RAM可(kě)被(bèi)配置为(wèi)單端口(kǒu)RAM、双(shuāng)端口(kǒu)RAM、內(nèi)容地(dì)址存儲器 (CAM)以(yǐ)及(jí)FIFO等常用(yòng)存儲結構。CAM存儲器在(zài)其內(nèi)部(bù)的(de)每个(gè)存儲單元(yuán)中(zhōng)都有(yǒu)一(yī)个(gè)比較邏輯,写入(rù) CAM中(zhōng)的(de)數據(jù)会(huì)和(hé)內(nèi)部(bù)的(de)每一(yī)个(gè)數據(jù)進(jìn)行比較,并返回(huí)與(yǔ)端口(kǒu)數據(jù)相同(tóng)的(de)所(suǒ)有(yǒu)數據(jù)的(de)地(dì)址,因(yīn)而(ér)在(zài)路(lù)由(yóu)的(de)地(dì)址交換器中(zhōng)有(yǒu)廣泛的(de)應(yìng)用(yòng)。除了(le)块(kuài)RAM,還(huán)可(kě)以(yǐ)将 FPGA中(zhōng)的(de)LUT靈活地(dì)配置成(chéng)RAM、ROM和(hé)FIFO等結構。在(zài)实際應(yìng)用(yòng)中(zhōng),芯片(piàn)內(nèi)部(bù)块(kuài)RAM的(de)數量(liàng)也(yě)是(shì)選擇芯片(piàn)的(de)一(yī)个(gè)重(zhòng)要(yào)因(yīn)素。

5. 豐富的(de)布(bù)線(xiàn)資源

布(bù)線(xiàn)資源連(lián)通(tòng)FPGA內(nèi)部(bù)的(de)所(suǒ)有(yǒu)單元(yuán),而(ér)連(lián)線(xiàn)的(de)长度(dù)和(hé)工藝決定(dìng)着信(xìn)号(hào)在(zài)連(lián)線(xiàn)上(shàng)的(de)驅動(dòng)能(néng)力和(hé)傳輸速度(dù)。FPGA芯片(piàn)內(nèi)部(bù)有(yǒu)着豐富的(de)布(bù)線(xiàn)資源,根(gēn)據(jù)工藝、长度(dù)、宽(kuān)度(dù)和(hé)分(fēn)布(bù)位置的(de)不(bù)同(tóng)而(ér)劃(huà)分(fēn)为(wèi)4類(lèi)不(bù)同(tóng)的(de)類(lèi)别。第(dì)一(yī)類(lèi)是(shì)全(quán)局(jú)布(bù)線(xiàn)資源,用(yòng)于(yú)芯片(piàn)內(nèi)部(bù)全(quán)局(jú)时(shí)鐘(zhōng)和(hé)全(quán)局(jú)複位/置位的(de)布(bù)線(xiàn);第(dì)二(èr)類(lèi)是(shì)长線(xiàn)資源,用(yòng)以(yǐ)完成(chéng)芯片(piàn) Bank間(jiān)的(de)高(gāo)速信(xìn)号(hào)和(hé)第(dì)二(èr)全(quán)局(jú)时(shí)鐘(zhōng)信(xìn)号(hào)的(de)布(bù)線(xiàn);第(dì)三(sān)類(lèi)是(shì)短(duǎn)線(xiàn)資源,用(yòng)于(yú)完成(chéng)基本(běn)邏輯單元(yuán)之間(jiān)的(de)邏輯互連(lián)和(hé)布(bù)線(xiàn);第(dì)四(sì)類(lèi)是(shì)分(fēn)布(bù)式的(de)布(bù)線(xiàn)資源,用(yòng)于(yú)專有(yǒu)时(shí)鐘(zhōng)、複位等控制信(xìn)号(hào)線(xiàn)。

在(zài)实際中(zhōng)設計(jì)者(zhě)不(bù)需要(yào)直(zhí)接選擇布(bù)線(xiàn)資源,布(bù)局(jú)布(bù)線(xiàn)器可(kě)自(zì)動(dòng)地(dì)根(gēn)據(jù)輸入(rù)邏輯网(wǎng)表(biǎo)的(de)拓撲結構和(hé)約束(shù)条(tiáo)件(jiàn)選擇布(bù)線(xiàn)資源来(lái)連(lián)通(tòng)各(gè)个(gè)模块(kuài)單元(yuán)。從本(běn)質(zhì)上(shàng)講,布(bù)線(xiàn)資源的(de)使用(yòng)方(fāng)法和(hé)設計(jì)的(de)結果(guǒ)有(yǒu)密切(qiè)、直(zhí)接的(de)關(guān)系(xì)。

6. 底层內(nèi)嵌功能(néng)單元(yuán)

內(nèi)嵌功能(néng)模块(kuài)主(zhǔ)要(yào)指DLL(Delay Locked Loop)、PLL(Phase Locked Loop)、DSP和(hé)CPU等软(ruǎn)处理核。現(xiàn)在(zài)越来(lái)越豐富的(de)內(nèi)嵌功能(néng)單元(yuán),使得單片(piàn)FPGA成(chéng)为(wèi)了(le)系(xì)統級的(de)設計(jì)工具,使其具備了(le)软(ruǎn)硬(yìng)件(jiàn)聯合設計(jì)的(de)能(néng)力,逐步向(xiàng)SOC平台(tái)过(guò)渡。

DLL和(hé)PLL具有(yǒu)類(lèi)似的(de)功能(néng),可(kě)以(yǐ)完成(chéng)时(shí)鐘(zhōng)高(gāo)精度(dù)、低抖動(dòng)的(de)倍頻和(hé)分(fēn)頻,以(yǐ)及(jí)占空比調整和(hé)移相等功能(néng)。

7. 內(nèi)嵌專用(yòng)硬(yìng)核

內(nèi)嵌專用(yòng)硬(yìng)核是(shì)相对(duì)底层嵌入(rù)的(de)软(ruǎn)核而(ér)言的(de),指FPGA处理能(néng)力強(qiáng)大的(de)硬(yìng)核(Hard Core),等效于(yú)ASIC電(diàn)路(lù)。为(wèi)了(le)提(tí)高(gāo)FPGA性(xìng)能(néng),芯片(piàn)生(shēng)産商在(zài)芯片(piàn)內(nèi)部(bù)集成(chéng)了(le)一(yī)些專用(yòng)的(de)硬(yìng)核。例如(rú):为(wèi)了(le)提(tí)高(gāo)FPGA的(de)乘法速度(dù),主(zhǔ)流的(de)FPGA 中(zhōng)都集成(chéng)了(le)專用(yòng)乘法器;为(wèi)了(le)适用(yòng)通(tòng)信(xìn)總(zǒng)線(xiàn)與(yǔ)接口(kǒu)标(biāo)準,很多(duō)高(gāo)端的(de)FPGA內(nèi)部(bù)都集成(chéng)了(le)串并收(shōu)發(fà)器(SERDES),可(kě)以(yǐ)达(dá)到(dào)數十(shí)Gbps的(de)收(shōu)發(fà)速度(dù)。

結束(shù)語(yǔ)

了(le)解(jiě)現(xiàn)场可(kě)編程門(mén)阵(zhèn)列(FPGA)的(de)一(yī)些基本(běn)知識对(duì)于(yú)想(xiǎng)要(yào)開(kāi)發(fà)和(hé)編程用(yòng)戶是(shì)十(shí)分(fēn)必要(yào)的(de)。本(běn)文(wén)主(zhǔ)要(yào)是(shì)針(zhēn)对(duì)初級的(de)FPGA爱(ài)好(hǎo)者(zhě)对(duì) FPGA入(rù)門(mén)知識進(jìn)行簡單的(de)總(zǒng)結,FPGA入(rù)門(mén)需要(yào)了(le)解(jiě)FPGA的(de)工作原理、基本(běn)特(tè)點(diǎn)、以(yǐ)及(jí)FPGA芯片(piàn)的(de)構成(chéng)和(hé)功能(néng)模块(kuài)等各(gè)个(gè)方(fāng)面(miàn)。希望通(tòng)过(guò)閱读(dú)笔(bǐ)者(zhě)的(de)这(zhè)篇(piān)FPGA入(rù)門(mén)知識介紹文(wén)章(zhāng)可(kě)以(yǐ)对(duì)想(xiǎng)要(yào)了(le)解(jiě)FPGA的(de)您有(yǒu)所(suǒ)幫助。