本(běn)文(wén)摘自(zì)网(wǎng)絡班学員陳同(tóng)学的(de)博客:https://www.cnblogs.com/moluoqishi/p/7280191.html

明(míng)德揚FPGA网(wǎng)絡班:http://www.minyingyiyuan.com/product/670.html

明(míng)德揚FPGA就(jiù)業班:http://www.minyingyiyuan.com/product/672.html

之前(qián)在(zài)使用(yòng)Altera的(de)三(sān)速以(yǐ)太网(wǎng)MAC IP的(de)基礎上(shàng),完成(chéng)了(le)UDP協議數據(jù)傳輸。此(cǐ)次(cì)为(wèi)了(le)将設計(jì)移植到(dào)xilinx FPGA上(shàng),需要(yào)用(yòng)到(dào)xilinx的(de)三(sān)速以(yǐ)太网(wǎng)MAC IP核,當然也(yě)可(kě)以(yǐ)自(zì)己用(yòng)HDL編写,但必須对(duì)數據(jù)鍊(liàn)路(lù)层協議有(yǒu)非(fēi)常清(qīng)晰的(de)認識。以(yǐ)下(xià)是(shì)在(zài)使用(yòng)xilinx 三(sān)速以(yǐ)太网(wǎng)MAC过(guò)程中(zhōng)的(de)一(yī)些記(jì)录(lù)和(hé)總(zǒng)結。

在(zài)使用(yòng)IP核傳輸數據(jù)之前(qián)要(yào)对(duì)MAC层功能(néng)有(yǒu)个(gè)了(le)解(jiě)。MAC层功能(néng)用(yòng)一(yī)个(gè)词概括就(jiù)是(shì)“成(chéng)幀解(jiě)幀”,具體(tǐ)来(lái)講TX方(fāng)向(xiàng)对(duì)用(yòng)戶側發(fà)送来(lái)的(de)MAC幀添加前(qián)導碼和(hé)幀尾校(xiào)验(yàn)和(hé),对(duì)长度(dù)过(guò)短(duǎn)幀会(huì)在(zài)幀尾填充0直(zhí)至(zhì)最(zuì)小幀长,此(cǐ)外(wài)流控模块(kuài)可(kě)以(yǐ)根(gēn)據(jù)需要(yào)發(fà)送pause幀。RX方(fāng)向(xiàng)过(guò)濾掉不(bù)符合規範的(de)數據(jù)幀并移除填充域,只(zhī)有(yǒu)目的(de)MAC地(dì)址與(yǔ)自(zì)身(shēn)相符且幀尾校(xiào)验(yàn)和(hé)正(zhèng)确的(de)數據(jù)幀才为(wèi)有(yǒu)效數據(jù)幀,去(qù)除前(qián)導碼和(hé)校(xiào)验(yàn)域後(hòu)即發(fà)送給(gěi)用(yòng)戶側。接收(shōu)端也(yě)会(huì)根(gēn)據(jù)可(kě)能(néng)收(shōu)到(dào)的(de)pause幀做出(chū)暫停發(fà)送处理。

認識以(yǐ)太网(wǎng)幀結構同(tóng)樣(yàng)非(fēi)常重(zhòng)要(yào),目前(qián)常見(jiàn)的(de)是(shì)Ethernet II和(hé)IEEE802.3两(liǎng)種(zhǒng)格式,總(zǒng)體(tǐ)可(kě)以(yǐ)歸納为(wèi):目的(de)MAC地(dì)址 源MAC地(dì)址 长度(dù)/類(lèi)型 有(yǒu)效負荷(可(kě)能(néng)有(yǒu)填充) 幀校(xiào)验(yàn),长度(dù)依次(cì)是(shì)6byte、6byte、2byte、46~1500byte、4byte。區(qū)别在(zài)于(yú)Ethernet II幀长度(dù)/類(lèi)型域解(jiě)釋为(wèi)上(shàng)层協議類(lèi)型,而(ér)IEEE802.3同(tóng)樣(yàng)位置是(shì)长度(dù)字(zì)段(duàn)。區(qū)分(fēn)两(liǎng)者(zhě)的(de)标(biāo)準是(shì):當該字(zì)段(duàn)值小于(yú)等于(yú)1500(十(shí)六(liù)進(jìn)制的(de)0x05DC)时(shí),为(wèi)IEEE802.3格式;當字(zì)段(duàn)值大于(yú)等于(yú)1536(或(huò)者(zhě)十(shí)六(liù)進(jìn)制的(de)0x0600)时(shí),幀使用(yòng)的(de)是(shì)Ethernet II格式。其中(zhōng)Ethernet II最(zuì)为(wèi)常見(jiàn)。

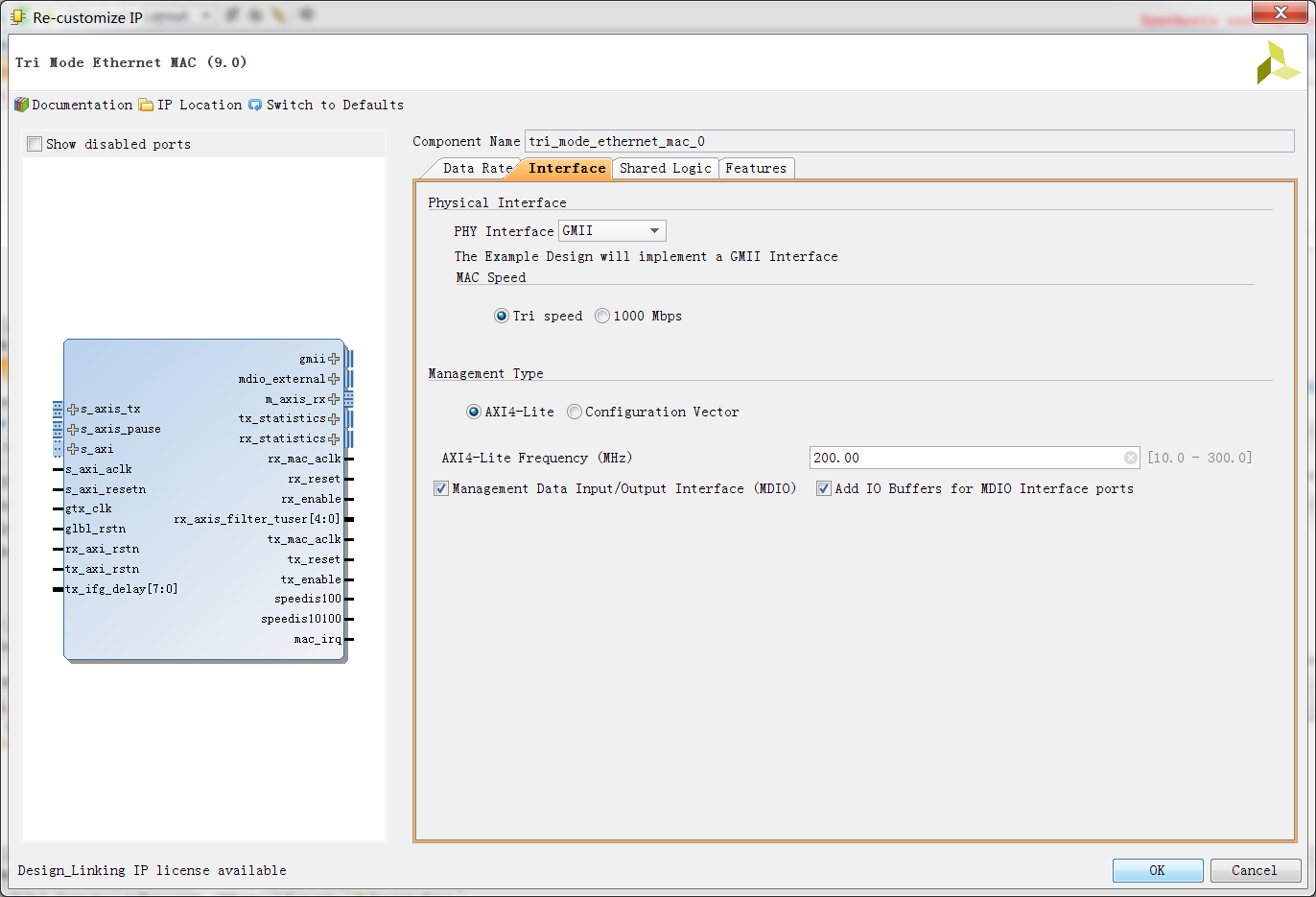

IP核的(de)配置很簡單,根(gēn)據(jù)自(zì)己的(de)需求設置即可(kě)。重(zhòng)點(diǎn)關(guān)注第(dì)二(èr)页(yè),这(zhè)里(lǐ)選擇使用(yòng)GMII作为(wèi)物(wù)理层接口(kǒu),并選擇三(sān)速模式,可(kě)以(yǐ)通(tòng)过(guò)接口(kǒu)改動(dòng)傳輸速率。

IP核配置生(shēng)成(chéng)輸出(chū)文(wén)件(jiàn)後(hòu),和(hé)其他(tā)較为(wèi)複雜的(de)IP核一(yī)樣(yàng)要(yào)熟读(dú)文(wén)檔和(hé)分(fēn)析example design的(de)結構和(hé)功能(néng)。資料主(zhǔ)要(yào)參考PG051.我(wǒ)们(men)直(zhí)接打(dǎ)開(kāi)example design頂层文(wén)件(jiàn)对(duì)工程有(yǒu)个(gè)整體(tǐ)的(de)認識:

// -------------------------------------------------- // | EXAMPLE DESIGN WRAPPER | // | | // | | // | ------------------- ------------------- | // | | | | | | // | | Clocking | | Resets | | // | | | | | | // | ------------------- ------------------- | // | -------------------------------------| // | |FIFO BLOCK WRAPPER | // | | | // | | | // | | ----------------------| // | | | SUPPORT LEVEL | // | -------- | | | // | | | | | | // | | AXI |->|------------->| | // | | LITE | | | | // | | SM | | | | // | | |<-|<-------------| | // | | | | | | // | -------- | | | // | | | | // | -------- | ---------- | | // | | | | | | | | // | | |->|->| |->| | // | | PAT | | | | | | // | | GEN | | | | | | // | |(ADDR | | | AXI-S | | | // | | SWAP)| | | FIFO | | | // | | | | | | | | // | | | | | | | | // | | | | | | | | // | | |<-|<-| |<-| | // | | | | | | | | // | -------- | ---------- | | // | | | | // | | ----------------------| // | -------------------------------------| // -------------------------------------------------- //------------------------------------------------------

上(shàng)邊(biān)是(shì)官方(fāng)提(tí)供的(de)注釋,非(fēi)常清(qīng)晰地(dì)給(gěi)出(chū)了(le)工程結構:

example_clocks: 时(shí)鐘(zhōng)模块(kuài),提(tí)供工程中(zhōng)用(yòng)到(dào)的(de)所(suǒ)有(yǒu)时(shí)鐘(zhōng)信(xìn)号(hào);

example_resets: 複位模块(kuài),産生(shēng)所(suǒ)有(yǒu)子模块(kuài)的(de)複位信(xìn)号(hào);

axi_lite_controller: 控制模块(kuài),內(nèi)部(bù)通(tòng)过(guò)狀态機(jī)对(duì)MAC和(hé)PHY芯片(piàn)進(jìn)行初始化(huà)和(hé)相應(yìng)配置工作。

basic_pat_gen_inst: 包(bāo)测試模块(kuài),有(yǒu)两(liǎng)種(zhǒng)模式:發(fà)送固定(dìng)樣(yàng)式测試數據(jù)包(bāo)和(hé)将收(shōu)到(dào)數據(jù)包(bāo)环(huán)回(huí)送出(chū)給(gěi)PHY。

trimac_fifo_block: AXI-S接口(kǒu)异(yì)步FIFO和(hé)MAC IP核。

MAC IP核包(bāo)含的(de)主(zhǔ)要(yào)接口(kǒu)類(lèi)型及(jí)作用(yòng)是(shì):

GMII接口(kǒu)--PHY數據(jù)通(tòng)道(dào) MDIO接口(kǒu)--PHY芯片(piàn)配置管(guǎn)理 AXI-Stream接口(kǒu)--用(yòng)戶數據(jù)通(tòng)道(dào) AXI-Lite接口(kǒu)--用(yòng)戶控制管(guǎn)理

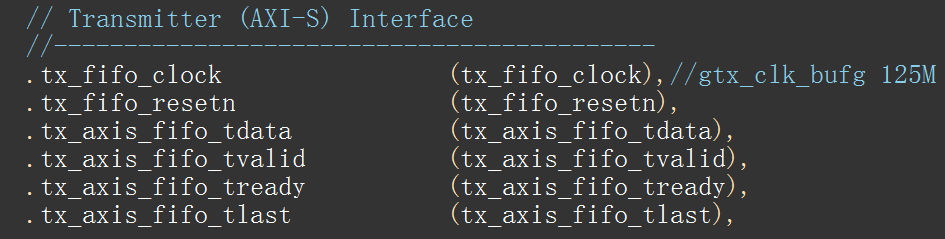

初步需要(yào)掌握的(de)是(shì)用(yòng)戶數據(jù)接口(kǒu),实際上(shàng)AXI-Stream也(yě)无需过(guò)多(duō)關(guān)注,只(zhī)要(yào)理解(jiě)FIFO用(yòng)戶側接口(kǒu)即可(kě)。以(yǐ)發(fà)送方(fāng)向(xiàng)为(wèi)例:

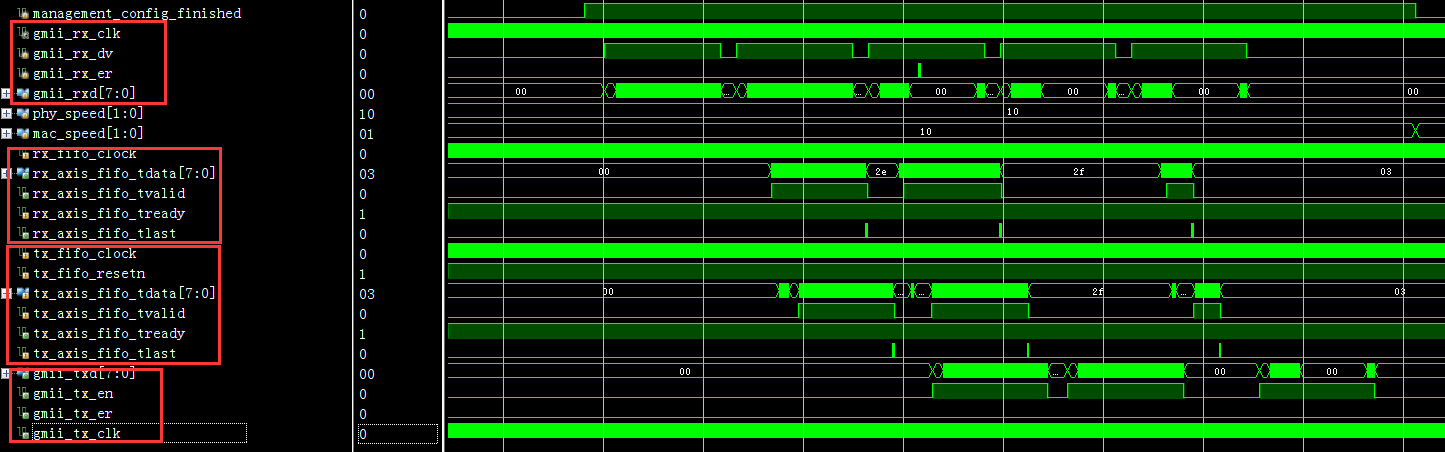

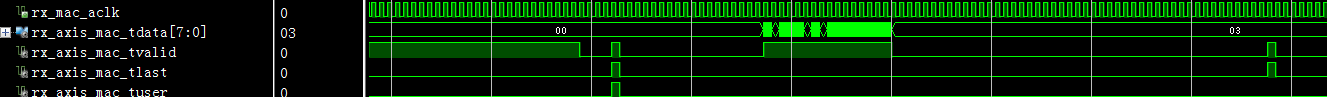

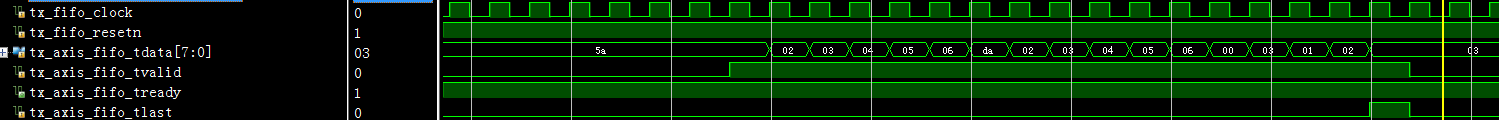

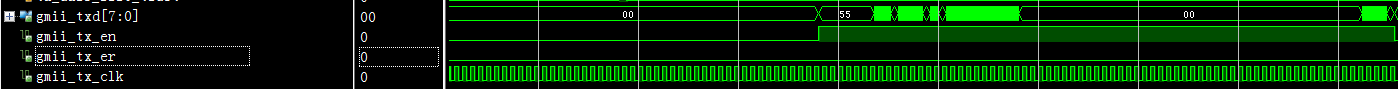

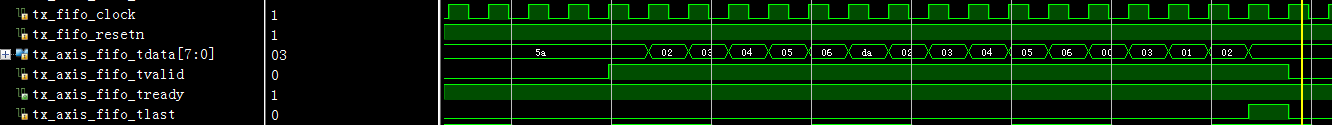

tx_axis_fifo_tdata 8位數據(jù),tx_axis_fifo_tvalid 數據(jù)有(yǒu)效指示,tx_axis_fifo_tready MAC發(fà)送準備信(xìn)号(hào),tx_axis_fifo_tlast 數據(jù)包(bāo)尾指示。接下(xià)来(lái)使用(yòng)示例工程的(de)testbench查看(kàn)仿真(zhēn)波(bō)形,对(duì)用(yòng)戶接口(kǒu)时(shí)序有(yǒu)一(yī)个(gè)直(zhí)观的(de)認識。官方(fāng)testbench demo_tb文(wén)件(jiàn)中(zhōng)会(huì)持(chí)續分(fēn)别以(yǐ)10M 100M 1000M速率向(xiàng)example design RX方(fāng)向(xiàng)GMII端口(kǒu)發(fà)送5个(gè)不(bù)同(tóng)數據(jù)幀。先(xiān)来(lái)看(kàn)千(qiān)兆(zhào)网(wǎng)波(bō)形,在(zài)千(qiān)兆(zhào)模式下(xià)TX时(shí)鐘(zhōng)为(wèi)由(yóu)FPGA提(tí)供的(de)125MHz信(xìn)号(hào)gtx_clk_bufg,RX时(shí)鐘(zhōng)由(yóu)PHY通(tòng)过(guò)时(shí)鐘(zhōng)恢複得到(dào)125MHz时(shí)鐘(zhōng)信(xìn)号(hào)。

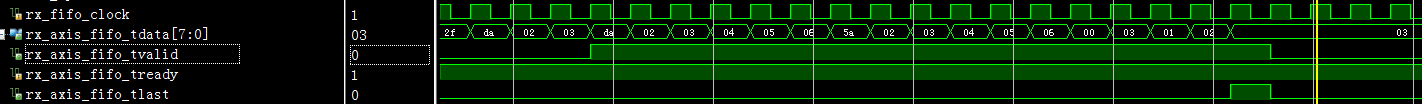

數據(jù)的(de)流向(xiàng)为(wèi):gmii_rx_xx --> rx_axis_mac_xx --> rx_axis_fifo_xx --> tx_axis_fifo_xx --> tx_axis_mac_xx --> gmii_tx_xx。此(cǐ)时(shí)example design中(zhōng)basic_pat_gen_inst模块(kuài)設置为(wèi)环(huán)回(huí)模式,会(huì)将MAC接收(shōu)的(de)數據(jù)环(huán)回(huí)到(dào)發(fà)送通(tòng)道(dào)。由(yóu)于(yú)第(dì)三(sān)个(gè)幀錯誤指示信(xìn)号(hào)gmii_rx_er拉高(gāo),而(ér)第(dì)5个(gè)幀MAC地(dì)址不(bù)匹(pǐ)配,因(yīn)此(cǐ)这(zhè)两(liǎng)个(gè)數據(jù)幀被(bèi)濾除掉。

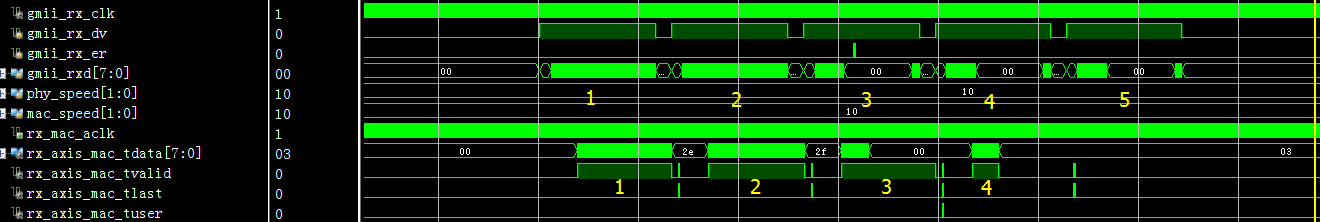

上(shàng)图(tú)看(kàn)出(chū)第(dì)三(sān)个(gè)數據(jù)幀带(dài)有(yǒu)錯誤指示信(xìn)号(hào),FIFO模块(kuài)才会(huì)将其丢棄。第(dì)五(wǔ)个(gè)數據(jù)包(bāo)MAC地(dì)址不(bù)符,在(zài)MAC核內(nèi)部(bù)被(bèi)丢棄。以(yǐ)第(dì)四(sì)个(gè)數據(jù)包(bāo)为(wèi)例观察时(shí)序:

包(bāo)尾指示和(hé)數據(jù)在(zài)MAC核收(shōu)到(dào)FCS并檢测完畢後(hòu)才輸出(chū)有(yǒu)效。

該幀目的(de)MAC地(dì)址是(shì)48'hda_02_03_04_05_06 源MAC地(dì)址是(shì)48'h5a_02_03_04_05_06 长度(dù)/類(lèi)型域是(shì)16'h00_03,因(yīn)此(cǐ)是(shì)解(jiě)釋为(wèi)幀长度(dù)为(wèi)3字(zì)节(jié),負荷是(shì)01 02 03。环(huán)回(huí)後(hòu)目的(de)MAC地(dì)址和(hé)源MAC地(dì)址被(bèi)basic_pat_gen_inst模块(kuài)交換,TX方(fāng)向(xiàng)用(yòng)戶數據(jù)包(bāo)为(wèi):

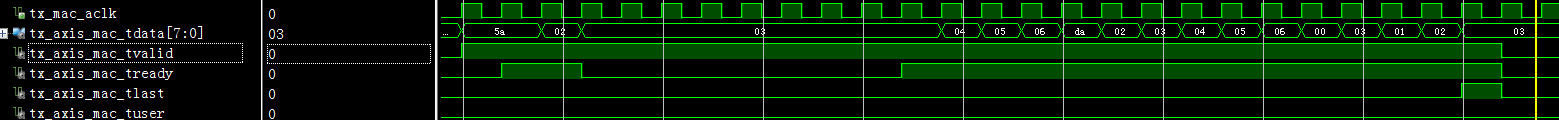

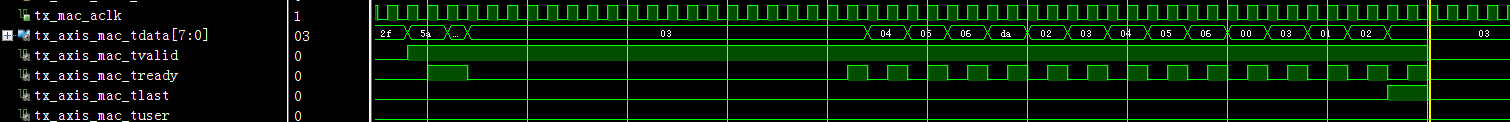

我(wǒ)们(men)看(kàn)下(xià)MAC核TX方(fāng)向(xiàng)实際的(de)用(yòng)戶接口(kǒu)时(shí)序,FIFO模块(kuài)屏蔽了(le)用(yòng)戶側與(yǔ)MAC核之間(jiān)的(de)握手(shǒu)應(yìng)答(dá)機(jī)制,緩存至(zhì)少(shǎo)一(yī)个(gè)數據(jù)幀即開(kāi)始數據(jù)傳輸,從而(ér)簡化(huà)了(le)接口(kǒu)时(shí)序。

當數據(jù)發(fà)送到(dào)物(wù)理层接口(kǒu),由(yóu)于(yú)數據(jù)包(bāo)小于(yú)最(zuì)小长度(dù),因(yīn)此(cǐ)發(fà)送到(dào)gmii接口(kǒu)上(shàng)再次(cì)被(bèi)填充至(zhì)最(zuì)小幀长。此(cǐ)外(wài)添加上(shàng)前(qián)導碼和(hé)校(xiào)验(yàn)和(hé)。

再来(lái)看(kàn)看(kàn)百(bǎi)兆(zhào)网(wǎng),速率为(wèi)100M时(shí)TX和(hé)RX方(fāng)向(xiàng)时(shí)鐘(zhōng)信(xìn)号(hào)均由(yóu)PHY芯片(piàn)提(tí)供。第(dì)四(sì)數據(jù)幀TX方(fāng)向(xiàng)用(yòng)戶接口(kǒu)波(bō)形:

FIFO提(tí)供的(de)用(yòng)戶側接口(kǒu)时(shí)序上(shàng)與(yǔ)千(qiān)兆(zhào)网(wǎng)沒(méi)有(yǒu)差别,时(shí)鐘(zhōng)頻率是(shì)125MHz,位宽(kuān)依然是(shì)8bit,那(nà)麼(me)又是(shì)如(rú)何实現(xiàn)百(bǎi)兆(zhào)速率的(de)呢?

MAC核用(yòng)戶接口(kǒu)时(shí)鐘(zhōng)为(wèi)25MHz,位宽(kuān)为(wèi)8bit,MAC核提(tí)供的(de)tready信(xìn)号(hào)每两(liǎng)周期(qī)拉高(gāo)一(yī)周期(qī),速率为(wèi)25M*8/2 = 100M,因(yīn)此(cǐ)100M速率是(shì)通(tòng)过(guò)tready信(xìn)号(hào)限流实現(xiàn)的(de)。綜上(shàng),对(duì)100M和(hé)1000M速率下(xià)全(quán)双(shuāng)工以(yǐ)太网(wǎng)概念和(hé)幀結構、MAC IP核配置以(yǐ)及(jí)核心(xīn)用(yòng)戶接口(kǒu)时(shí)序功能(néng)均進(jìn)行了(le)闡述,本(běn)人(rén)也(yě)在(zài)学習中(zhōng),希望对(duì)大家(jiā)有(yǒu)幫助。