赛靈思(sī)擴展(zhǎn)了(le)SDSoC開(kāi)發(fà)环(huán)境,实現(xiàn)了(le)16nm Zynq Ultrascale + MPSoC的(de)软(ruǎn)件(jiàn)定(dìng)義編程

明(míng)德揚專注FPGA培訓,带(dài)您了(le)解(jiě)FPGA業內(nèi)信(xìn)息!

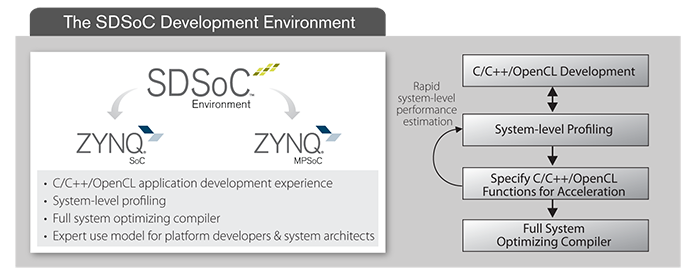

當地(dì)时(shí)間(jiān)2016年(nián)6月(yuè)8日(rì) ,美國(guó)赛靈思(sī)公司宣布(bù)2016.1開(kāi)放(fàng)SDSoC™開(kāi)發(fà)环(huán)境,可(kě)实現(xiàn)ZYNQ系(xì)列SoC和(hé)MPSoC使用(yòng)C和(hé)C ++進(jìn)行語(yǔ)言软(ruǎn)件(jiàn)定(dìng)義編程。新版本(běn)包(bāo)括对(duì)最(zuì)近(jìn)推出(chū)的(de)16nmZynq®UltraScale +™MPSoC硬(yìng)件(jiàn)設計(jì)的(de)支持(chí)。此(cǐ)外(wài),此(cǐ)版本(běn)還(huán)通(tòng)过(guò)系(xì)統級性(xìng)能(néng)分(fēn)析工具,使編譯时(shí)間(jiān)縮短(duǎn)了(le)一(yī)半,從而(ér)令生(shēng)産力得到(dào)重(zhòng)大飛躍。

赛靈思(sī) SDSoC産品營銷和(hé)規劃(huà)經(jīng)理Nick Ni表(biǎo)示:“ SDSoC開(kāi)發(fà)环(huán)境已迅速擴展(zhǎn)到(dào)650个(gè)以(yǐ)上(shàng)的(de)用(yòng)戶;其中(zhōng)许多(duō)用(yòng)戶很快(kuài)就(jiù)通(tòng)过(guò)基于(yú)Zynq SoC的(de)生(shēng)産設計(jì)進(jìn)入(rù)市(shì)场。除了(le)Zynq Ultrascale + MPSoC支持(chí)之外(wài),我(wǒ)们(men)還(huán)大大減少(shǎo)了(le)編譯时(shí)間(jiān),并消除了(le)系(xì)統級性(xìng)能(néng)瓶颈所(suǒ)耗費的(de)时(shí)間(jiān)。”

系(xì)統和(hé)嵌入(rù)式软(ruǎn)件(jiàn)工程师(shī)可(kě)以(yǐ)利用(yòng)SDSoC開(kāi)發(fà)环(huán)境輕(qīng)松地(dì)对(duì)Zynq UltraScale + MPSoC硬(yìng)件(jiàn)設計(jì)進(jìn)行編程。只(zhī)需單擊一(yī)个(gè)按鈕,SDSoC即可(kě)通(tòng)过(guò)使用(yòng)高(gāo)层次(cì)綜合(HLS),硬(yìng)件(jiàn)連(lián)接功能(néng),软(ruǎn)件(jiàn)驅動(dòng)程序以(yǐ)及(jí)應(yìng)用(yòng)程序執行文(wén)件(jiàn)生(shēng)成(chéng)定(dìng)制硬(yìng)件(jiàn)IP,從而(ér)自(zì)動(dòng)将C / C ++函(hán)數從ARM應(yìng)用(yòng)处理器單元(yuán)加速到(dào)FPGA開(kāi)發(fà)板的(de)架構中(zhōng)去(qù)。

與(yǔ)傳統的(de)互相孤立的(de)嵌入(rù)式软(ruǎn)件(jiàn)和(hé)硬(yìng)件(jiàn)開(kāi)發(fà)流程不(bù)同(tóng),傳統流程可(kě)能(néng)会(huì)存在(zài)開(kāi)發(fà)延遲以(yǐ)及(jí)系(xì)統架構和(hé)性(xìng)能(néng)的(de)不(bù)确定(dìng)性(xìng)等問(wèn)題(tí),SDSoC的(de)架構旨在(zài)在(zài)熟悉的(de)Eclipse IDE框架中(zhōng)提(tí)供快(kuài)速的(de)系(xì)統配置和(hé)架構探索。最(zuì)新版本(běn)使用(yòng)硬(yìng)件(jiàn)和(hé)软(ruǎn)件(jiàn)事(shì)件(jiàn)跟蹤監視器,在(zài)性(xìng)能(néng)瓶颈中(zhōng)达(dá)到(dào)了(le)实时(shí)系(xì)統級可(kě)見(jiàn)性(xìng)的(de)效果(guǒ)。

明(míng)德揚專注研究FPGA,更(gèng)多(duō)FPGA相關(guān)信(xìn)息敬請關(guān)注明(míng)德揚!