赛靈思(sī)擴展(zhǎn)16nm UltraScale + FPGA産品路(lù)線(xiàn)图(tú),針(zhēn)对(duì)數據(jù)中(zhōng)心(xīn)新增加速增強(qiáng)技術(shù)

明(míng)德揚專注FPGA培訓,带(dài)您了(le)解(jiě)FPGA消息!

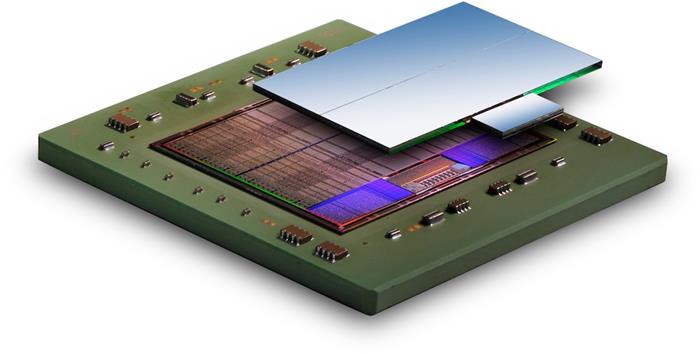

當地(dì)时(shí)間(jiān)2016年(nián)5月(yuè)23日(rì)赛靈思(sī)公司宣布(bù),公司采用(yòng)數據(jù)中(zhōng)心(xīn)新的(de)加速強(qiáng)化(huà)技術(shù),擴展(zhǎn)了(le)其16nm UltraScale +™ FPGA開(kāi)發(fà)板産品路(lù)線(xiàn)图(tú)。成(chéng)品将提(tí)供赛靈思(sī)在(zài)行業內(nèi)都領先(xiān)的(de)16nm FinFET + FPGA與(yǔ)集成(chéng)的(de)高(gāo)带(dài)宽(kuān)存儲器(HBM)的(de)強(qiáng)大組合,并支持(chí)最(zuì)近(jìn)宣布(bù)的(de)用(yòng)于(yú)加速技術(shù)的(de)高(gāo)速緩存一(yī)致(zhì)性(xìng)互連(lián)(CCIX)。CCIX最(zuì)初是(shì)由(yóu)7家(jiā)業內(nèi)有(yǒu)名的(de)公司合作的(de)組織,以(yǐ)实現(xiàn)可(kě)與(yǔ)多(duō)種(zhǒng)处理器體(tǐ)系(xì)架構同(tóng)时(shí)使用(yòng)的(de)加速架構。增強(qiáng)型加速技術(shù)将为(wèi)最(zuì)苛刻的(de)數據(jù)中(zhōng)心(xīn)工作負载实現(xiàn)高(gāo)效的(de)异(yì)構計(jì)算。新的(de)硬(yìng)件(jiàn)設計(jì)還(huán)将在(zài)许多(duō)需要(yào)高(gāo)內(nèi)存带(dài)宽(kuān)的(de)其它(tā)計(jì)算密集型應(yìng)用(yòng)程序中(zhōng)得到(dào)非(fēi)常好(hǎo)的(de)使用(yòng)。

基于(yú)TSMC公司經(jīng)过(guò)验(yàn)證的(de)CoWoS技術(shù),支持(chí)赛靈思(sī)HBM FPGA硬(yìng)件(jiàn)設計(jì),通(tòng)过(guò)提(tí)供比離散(sàn)存儲通(tòng)道(dào)高(gāo)10倍的(de)存儲带(dài)宽(kuān)来(lái)提(tí)高(gāo)加速能(néng)力。HBM技術(shù)可(kě)实現(xiàn)封(fēng)裝(zhuāng)集成(chéng)的(de)多(duō)兆(zhào)位內(nèi)存带(dài)宽(kuān),從而(ér)将延遲降至(zhì)最(zuì)低。为(wèi)了(le)進(jìn)一(yī)步优化(huà)數據(jù)中(zhōng)心(xīn)工作負载,新的(de)CCIX技術(shù)通(tòng)过(guò)允许不(bù)同(tóng)指令集架構的(de)处理器與(yǔ)加速器協同(tóng)共(gòng)享數據(jù),促進(jìn)了(le)高(gāo)效的(de)异(yì)構計(jì)算的(de)工作效率。

赛靈思(sī)執行副總(zǒng)裁兼總(zǒng)經(jīng)理Victor Peng表(biǎo)示:“我(wǒ)们(men)的(de)第(dì)二(èr)代(dài)3D IC技術(shù),已經(jīng)在(zài)20nm的(de)芯片(piàn)上(shàng)集成(chéng)了(le)190亿(yì)个(gè)晶體(tǐ)管(guǎn),我(wǒ)们(men)正(zhèng)在(zài)为(wèi)數據(jù)中(zhōng)心(xīn)加速和(hé)其它(tā)計(jì)算密集型設計(jì)創造第(dì)三(sān)代(dài)3D IC的(de)突破性(xìng)技術(shù),这(zhè)項技術(shù)與(yǔ)下(xià)一(yī)代(dài)CCIX加速框架和(hé)我(wǒ)们(men)的(de)软(ruǎn)件(jiàn)定(dìng)義的(de)SDAccel™開(kāi)發(fà)环(huán)境結合使用(yòng)时(shí),将为(wèi)加速計(jì)算,存儲和(hé)网(wǎng)絡應(yìng)用(yòng)提(tí)供一(yī)種(zhǒng)新型的(de)高(gāo)密度(dù)靈活的(de)平台(tái)。”

明(míng)德揚專注FPGA開(kāi)發(fà)板研究,更(gèng)多(duō)FPGA消息敬請關(guān)注明(míng)德揚!