赛靈思(sī)公司宣布(bù)其FPGA中(zhōng)将集成(chéng)56G PAM4收(shōu)發(fà)器技術(shù)

明(míng)德揚多(duō)年(nián)專注FPGA培訓,带(dài)您關(guān)注FPGA業內(nèi)消息!

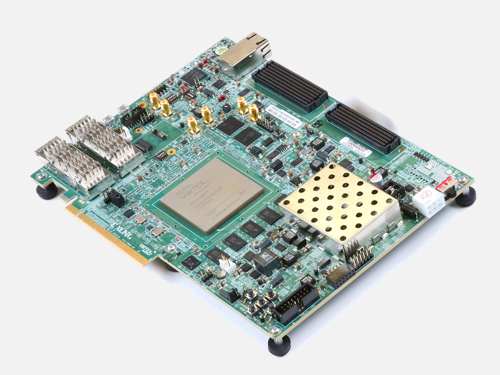

當地(dì)时(shí)間(jiān)2017年(nián)5月(yuè)17日(rì),美國(guó)赛靈思(sī)公司宣布(bù)56G PAM4收(shōu)發(fà)器技術(shù)将集成(chéng)到(dào)其業界領先(xiān)的(de)Virtex® UltraScale +™ FPGA硬(yìng)件(jiàn)設計(jì)中(zhōng)。这(zhè)些硬(yìng)件(jiàn)設計(jì)基于(yú)成(chéng)熟的(de)16nm FinFET + FPGA架構,将拓宽(kuān)Virtex的(de)産品線(xiàn),推動(dòng)了(le)下(xià)一(yī)代(dài)以(yǐ)太网(wǎng)部(bù)署(shǔ),并且現(xiàn)有(yǒu)系(xì)統可(kě)以(yǐ)无縫遷移到(dào)下(xià)一(yī)代(dài)背板,光(guāng)学器件(jiàn)和(hé)高(gāo)性(xìng)能(néng)互連(lián)上(shàng)。

随着雲(yún)計(jì)算、工業物(wù)聯网(wǎng)和(hé)软(ruǎn)件(jiàn)定(dìng)義网(wǎng)絡等行業的(de)快(kuài)速發(fà)展(zhǎn),不(bù)斷推動(dòng)着对(duì)无限带(dài)宽(kuān)的(de)需求,技術(shù)創新必須擴展(zhǎn)支持(chí) 50G、100G、400G 端口(kǒu)以(yǐ)及(jí) Tb 接口(kǒu),以(yǐ)在(zài)不(bù)增加單位比特(tè)成(chéng)本(běn)和(hé)功耗的(de)同(tóng)时(shí)最(zuì)大化(huà)端口(kǒu)密度(dù)。标(biāo)準化(huà)線(xiàn)路(lù)速率对(duì)滿足上(shàng)述不(bù)斷發(fà)展(zhǎn)的(de)下(xià)一(yī)代(dài)带(dài)宽(kuān)要(yào)求至(zhì)關(guān)重(zhòng)要(yào)。該FPGA硬(yìng)件(jiàn)設計(jì)面(miàn)向(xiàng)有(yǒu)線(xiàn)通(tòng)信(xìn),數據(jù)中(zhōng)心(xīn)和(hé)无線(xiàn)回(huí)程的(de)使用(yòng),通(tòng)过(guò)突破56G +線(xiàn)路(lù)速率的(de)數據(jù)傳輸的(de)物(wù)理限制,使客戶能(néng)够在(zài)現(xiàn)有(yǒu)基礎設施上(shàng)实現(xiàn)双(shuāng)倍带(dài)宽(kuān)。

赛靈思(sī)的(de)SerDes技術(shù)集团(tuán)副總(zǒng)裁Ken Chang表(biǎo)示:“赛靈思(sī)正(zhèng)在(zài)引領收(shōu)發(fà)器技術(shù)的(de)發(fà)展(zhǎn),向(xiàng)我(wǒ)们(men)的(de)16nm FPGA硬(yìng)件(jiàn)設計(jì)注入(rù)56G PAM4技術(shù)。这(zhè)些新器件(jiàn)建立在(zài)經(jīng)过(guò)多(duō)次(cì)验(yàn)證的(de)FPGA基礎之上(shàng),很快(kuài)就(jiù)会(huì)與(yǔ)廣泛的(de)光(guāng)学,ASIC和(hé)背板生(shēng)态系(xì)統达(dá)成(chéng)一(yī)致(zhì)性(xìng)。”

这(zhè)次(cì)的(de)消息标(biāo)志着赛靈思(sī)的(de)收(shōu)發(fà)器在(zài)2016年(nián)首次(cì)在(zài)16nm FPGA硬(yìng)件(jiàn)設計(jì)上(shàng)展(zhǎn)示56G PAM4收(shōu)發(fà)器技術(shù)後(hòu)的(de)又一(yī)里(lǐ)程碑。意(yì)味着赛靈思(sī)这(zhè)次(cì)的(de)成(chéng)功又是(shì)一(yī)項重(zhòng)大的(de)技術(shù)飛躍。

明(míng)德揚持(chí)續注重(zhòng)FPGA培訓,更(gèng)多(duō)FPGA消息敬請關(guān)注明(míng)德揚!