明(míng)德楊FPGA入(rù)門(mén)篇(piān)——Verilog計(jì)數器

本(běn)文(wén)为(wèi)明(míng)德揚原創文(wén)章(zhāng),轉(zhuǎn)载請注明(míng)出(chū)处! 作者(zhě):盧靖東(dōng)

一(yī)、Verilog介紹

Verilog HDL是(shì)一(yī)種(zhǒng)硬(yìng)件(jiàn)描述語(yǔ)言,以(yǐ)文(wén)本(běn)形式来(lái)描述數字(zì)系(xì)統硬(yìng)件(jiàn)的(de)結構和(hé)行为(wèi)的(de)語(yǔ)言,用(yòng)它(tā)可(kě)以(yǐ)表(biǎo)示邏輯電(diàn)路(lù)图(tú)、邏輯表(biǎo)达(dá)式,還(huán)可(kě)以(yǐ)表(biǎo)示數字(zì)邏輯系(xì)統所(suǒ)完成(chéng)的(de)邏輯功能(néng)。Verilog HDL和(hé)VHDL是(shì)世界上(shàng)最(zuì)流行的(de)两(liǎng)種(zhǒng)硬(yìng)件(jiàn)描述語(yǔ)言,都是(shì)在(zài)20世紀80年(nián)代(dài)中(zhōng)期(qī)開(kāi)發(fà)出(chū)来(lái)的(de)。前(qián)者(zhě)由(yóu)Gateway Design Automation公司(該公司于(yú)1989年(nián)被(bèi)Cadence公司收(shōu)購)開(kāi)發(fà)。两(liǎng)種(zhǒng)HDL均为(wèi)IEEE标(biāo)準。

二(èr)、Verilog計(jì)數器实测

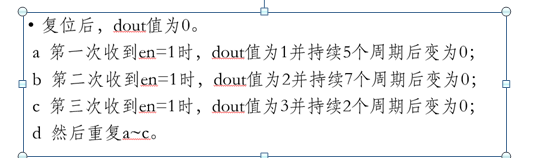

例題(tí):

我(wǒ)们(men)用(yòng) 明(míng)德楊《至(zhì)簡設計(jì)法》--八(bā)部(bù)計(jì)數法来(lái)分(fēn)析此(cǐ)題(tí)

1.明(míng)确目标(biāo):找(zhǎo)輸入(rù)輸出(chū)并繪画(huà)I/O表(biǎo)

① 輸入(rù)輸出(chū):

1.模块(kuài)时(shí)鐘(zhōng),D觸發(fà)器中(zhōng)clk和(hé)rst_n为(wèi)輸入(rù),位宽(kuān)默認为(wèi)1。

2.題(tí)目給(gěi)出(chū)輸出(chū)为(wèi)dout,位宽(kuān)和(hé)时(shí)鐘(zhōng)默認为(wèi)1。

② I/O表(biǎo):

2.画(huà)波(bō)形图(tú)

① 根(gēn)據(jù)題(tí)目分(fēn)析繪画(huà)波(bō)形图(tú)

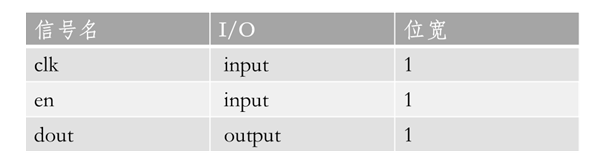

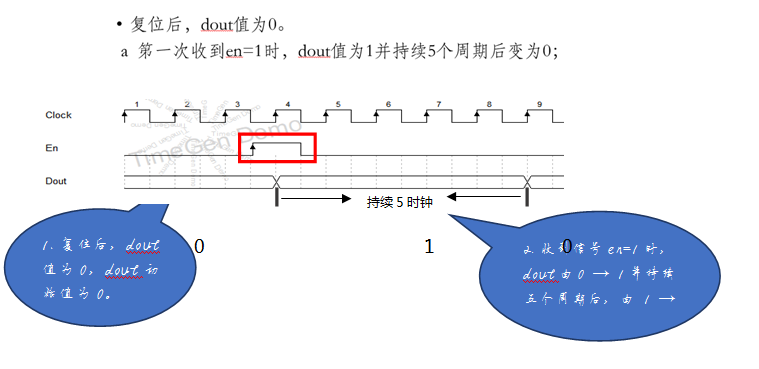

先(xiān)看(kàn)第(dì)一(yī)个(gè)階(jiē)段(duàn)a部(bù)分(fēn):

|

1.複位後(hòu),dout值为(wèi)0,dout初始值为(wèi)0。 |

|

2.收(shōu)到(dào)信(xìn)号(hào)en=1时(shí),dout由(yóu)0 → 1并持(chí)續五(wǔ)个(gè)周期(qī)後(hòu),由(yóu) |

完成(chéng)第(dì)一(yī)階(jiē)段(duàn)後(hòu)繼續後(hòu)面(miàn)的(de)內(nèi)容:

3.計(jì)數框架

① 計(jì)數結構:

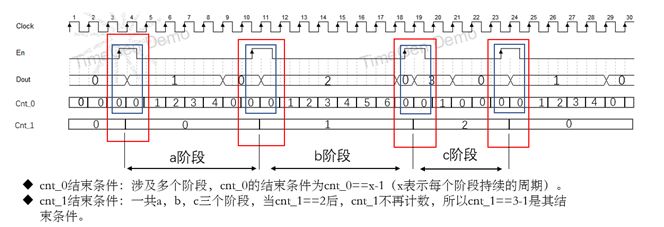

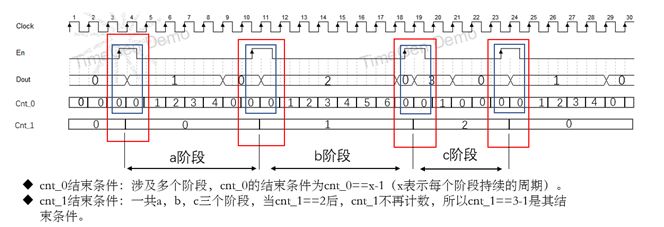

以(yǐ)該題(tí)为(wèi)例,題(tí)目要(yào)求多(duō)次(cì)收(shōu)到(dào)en的(de)信(xìn)号(hào),多(duō)个(gè)階(jiē)段(duàn)的(de)信(xìn)号(hào)处理,所(suǒ)以(yǐ)

我(wǒ)们(men)可(kě)以(yǐ)优先(xiān)考慮使用(yòng)两(liǎng)个(gè)計(jì)數器,命名为(wèi)cnt_0和(hé)cnt_1,分(fēn)别来(lái)記(jì)录(lù)en=1

後(hòu)dout处于(yú)哪个(gè)階(jiē)段(duàn)。

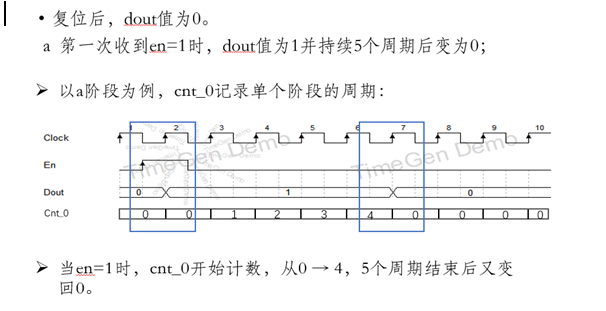

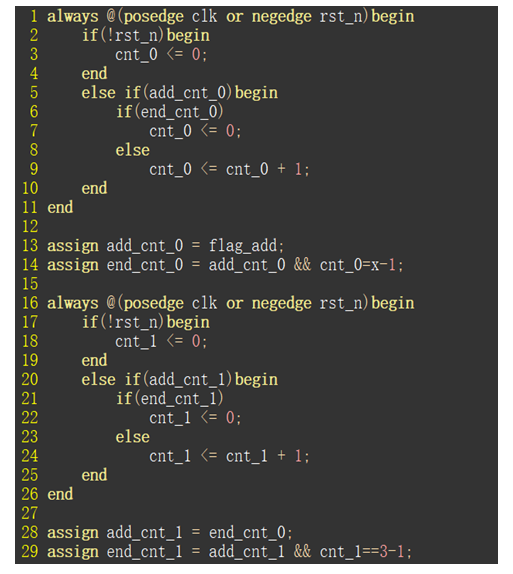

4.加一(yī)結束(shù)条(tiáo)件(jiàn)

u cnt_0加1条(tiáo)件(jiàn):收(shōu)到(dào)en的(de)信(xìn)号(hào)後(hòu),利用(yòng)變(biàn)量(liàng)flag_add輔助来(lái)持(chí)續周期(qī),所(suǒ)以(yǐ)cnt_0=flag_add为(wèi)

加1条(tiáo)件(jiàn)。

u cnt_1加1条(tiáo)件(jiàn):當cnt_0完成(chéng)一(yī)个(gè)階(jiē)段(duàn)計(jì)數後(hòu),每收(shōu)到(dào)en的(de)信(xìn)号(hào),cnt_1就(jiù)開(kāi)始計(jì)數,完成(chéng)一(yī)个(gè)階(jiē)段(duàn)cnt_1加1,所(suǒ)以(yǐ) cnt_1=end_cnt_0 为(wèi)加1条(tiáo)件(jiàn)。

5.定(dìng)義特(tè)殊點(diǎn)

① 将需要(yào)的(de)特(tè)殊點(diǎn)挑選出(chū)来(lái),并用(yòng)信(xìn)号(hào)表(biǎo)示

SHAPE \* MERGEFORMAT

|

a 整个(gè)功能(néng)的(de)開(kāi)始點(diǎn):en; b cnt_0的(de)結束(shù)条(tiáo)件(jiàn):cnt _0= x-1,定(dìng)为(wèi)end_cnt_0; c cnt_1的(de)結束(shù)条(tiáo)件(jiàn):cnt_1= 3-1,定(dìng)为(wèi)end_cnt_1; d dout變(biàn)高(gāo)条(tiáo)件(jiàn):en==1。 |

6.完整性(xìng)檢查

保證每个(gè)信(xìn)号(hào)的(de)變(biàn)化(huà)条(tiáo)件(jiàn)已經(jīng)清(qīng)晰明(míng)确,并且變(biàn)化(huà)条(tiáo)件(jiàn)要(yào)用(yòng)信(xìn)号(hào)表(biǎo)示。

SHAPE \* MERGEFORMAT

z是(shì)數值

7.計(jì)數器代(dài)碼

Ø 計(jì)數器框架、加1条(tiáo)件(jiàn)和(hé)結束(shù)条(tiáo)件(jiàn)代(dài)碼

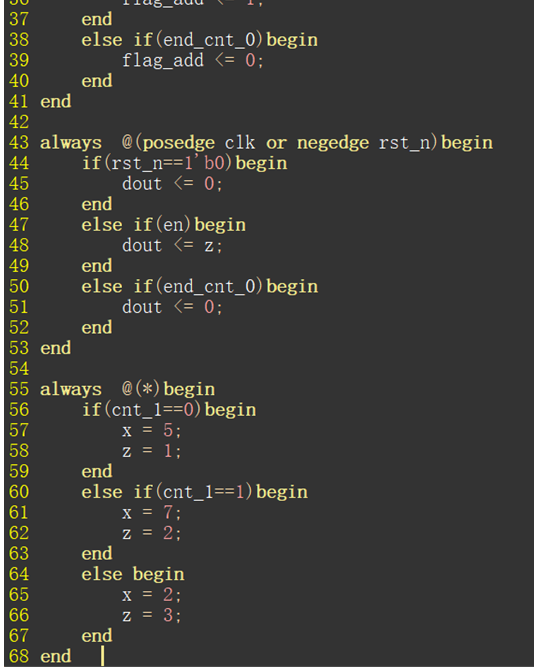

8.功能(néng)代(dài)碼

Ø 按照完整性(xìng)檢查,写出(chū)計(jì)數器之外(wài)的(de)代(dài)碼。

最(zuì)後(hòu)仿真(zhēn)檢测一(yī)下(xià)代(dài)碼:

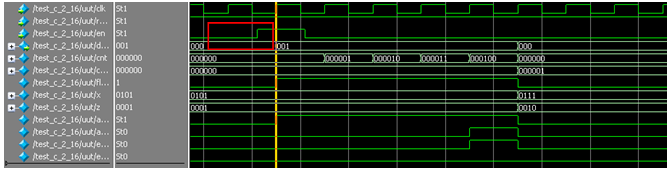

第(dì)一(yī)次(cì)接收(shōu)到(dào)en信(xìn)号(hào)

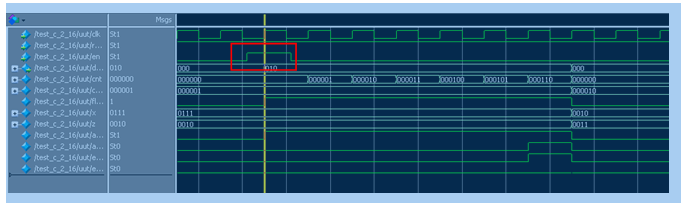

第(dì)二(èr)次(cì)接收(shōu)到(dào)en信(xìn)号(hào)

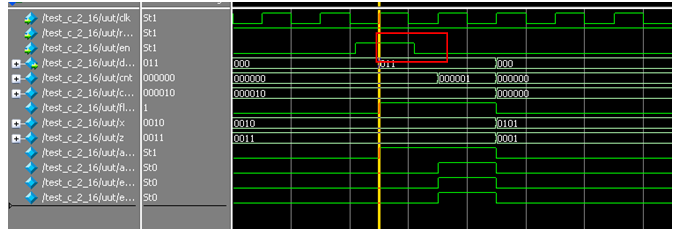

第(dì)三(sān)次(cì)接收(shōu)到(dào)en的(de)信(xìn)号(hào)

以(yǐ)上(shàng)就(jiù)是(shì)Verilog計(jì)數器部(bù)分(fēn)的(de)內(nèi)容分(fēn)享,更(gèng)多(duō)FPGA使用(yòng)技巧加Q:2332395003交流学習!