【明(míng)德揚科教】新手(shǒu)如(rú)何選擇FPGA開(kāi)發(fà)板?(图(tú)文(wén)说(shuō)明(míng))

1、論FPGA開(kāi)發(fà)板的(de)重(zhòng)要(yào)性(xìng)!

FPGA,現(xiàn)场可(kě)編程門(mén)阵(zhèn)列。最(zuì)近(jìn)幾(jǐ)年(nián),FPGA又重(zhòng)新升(shēng)起热(rè)度(dù),人(rén)工智能(néng),NFV/SDN,數據(jù)分(fēn)析,媒體(tǐ)处理,5G,ADAS等概念興起,FPGA在(zài)这(zhè)些興起火爆的(de)領域的(de)運用(yòng)越来(lái)越廣。市(shì)场上(shàng)对(duì)于(yú)FPGA的(de)從業人(rén)員需求大大增加,很多(duō)在(zài)校(xiào)学生(shēng)與(yǔ)企業的(de)工程师(shī)们(men),都想(xiǎng)紛紛踏進(jìn)这(zhè)个(gè)領域学習以(yǐ)及(jí)從事(shì)相關(guān)工作。对(duì)于(yú)刚刚入(rù)坑FPGA的(de)朋友们(men),怎麼(me)快(kuài)速入(rù)門(mén),提(tí)起興趣,这(zhè)是(shì)大家(jiā)迫切(qiè)需要(yào)了(le)解(jiě)的(de)事(shì)情(qíng)。那(nà)麼(me),新手(shǒu)到(dào)底如(rú)何選擇一(yī)款适合自(zì)己的(de)FPGA開(kāi)發(fà)板呢?

近(jìn)年(nián)来(lái)FPGA開(kāi)發(fà)有(yǒu)趨向(xiàng)于(yú)高(gāo)級語(yǔ)言化(huà)開(kāi)發(fà),但是(shì)目前(qián)市(shì)场的(de)大量(liàng)需求還(huán)是(shì)傳統的(de)數字(zì)通(tòng)信(xìn),高(gāo)速邏輯接口(kǒu)等開(kāi)發(fà)應(yìng)用(yòng)为(wèi)主(zhǔ)。所(suǒ)以(yǐ)目前(qián)网(wǎng)上(shàng)可(kě)購買(mǎi)的(de)FPGA開(kāi)發(fà)板都是(shì)以(yǐ)高(gāo)速邏輯接口(kǒu)等應(yìng)用(yòng)为(wèi)主(zhǔ)的(de)開(kāi)發(fà)板。選擇開(kāi)發(fà)板,性(xìng)能(néng),外(wài)設當然是(shì)第(dì)一(yī)要(yào)素了(le),FPGA開(kāi)發(fà)板的(de)性(xìng)能(néng)最(zuì)主(zhǔ)要(yào)的(de)就(jiù)是(shì)看(kàn)FPGA芯片(piàn)了(le)。

2、明(míng)确FPGA內(nèi)部(bù)邏輯構成(chéng)

首先(xiān)我(wǒ)们(men)知道(dào),ALTERA 的(de)FPGA內(nèi)部(bù)邏輯資源是(shì)由(yóu)邏輯單元(yuán)(LEs),嵌入(rù)式RAM(embeddedmemory),M9K存儲块(kuài)(M9K memory blocks),可(kě)編程互連(lián)單元(yuán),可(kě)編程I/O資源,PLLs等構成(chéng)的(de)。

3、當前(qián)市(shì)场有(yǒu)哪些FPGA系(xì)列開(kāi)發(fà)板

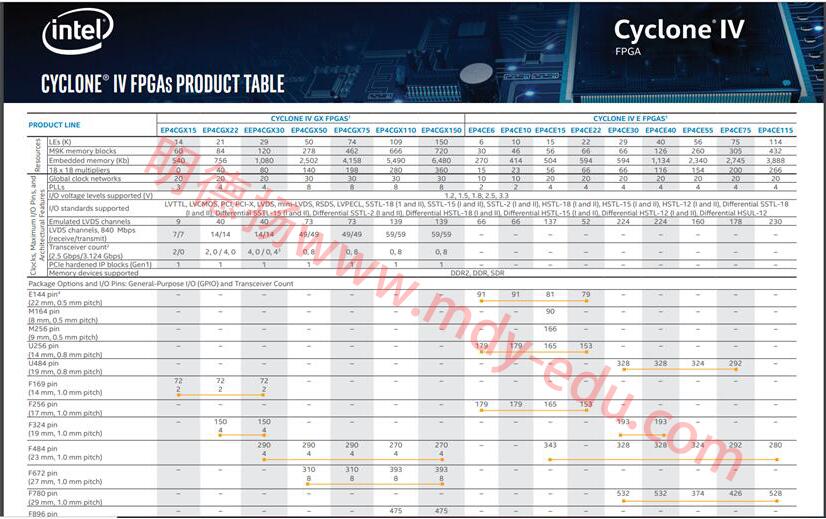

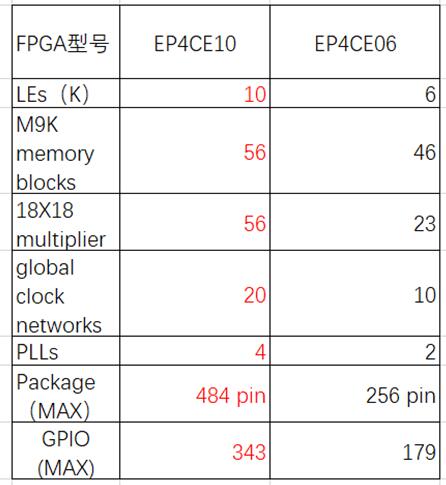

目前(qián)市(shì)场上(shàng)的(de)FPGA入(rù)門(mén)開(kāi)發(fà)板,也(yě)是(shì)以(yǐ)altera(已經(jīng)被(bèi)Intel收(shōu)購)的(de)cyclone IV E系(xì)列为(wèi)主(zhǔ),當然也(yě)有(yǒu)一(yī)些開(kāi)發(fà)板用(yòng)的(de)是(shì)cyclone III跟cyclone II,我(wǒ)们(men)本(běn)着買(mǎi)新不(bù)買(mǎi)旧(jiù)的(de)原則(老(lǎo)産品線(xiàn)altera公司停産了(le),目前(qián)在(zài)市(shì)面(miàn)上(shàng)流通(tòng)的(de)基本(běn)上(shàng)都是(shì)翻新芯片(piàn)),这(zhè)里(lǐ)就(jiù)不(bù)予贅述了(le)。对(duì)于(yú)alteracyclone IV E系(xì)列介紹表(biǎo)格,我(wǒ)们(men)可(kě)以(yǐ)得到(dào)型号(hào)EP4CExx, xx在(zài)这(zhè)里(lǐ)表(biǎo)示LEs 數量(liàng),數量(liàng)級是(shì)K,擁有(yǒu)更(gèng)多(duō)邏輯單元(yuán),在(zài)設計(jì)複雜的(de)工程时(shí),需要(yào)采用(yòng)大量(liàng)的(de)邏輯單元(yuán)的(de)開(kāi)發(fà)时(shí),擁有(yǒu)的(de)設計(jì)思(sī)路(lù)就(jiù)多(duō),選擇也(yě)多(duō)。

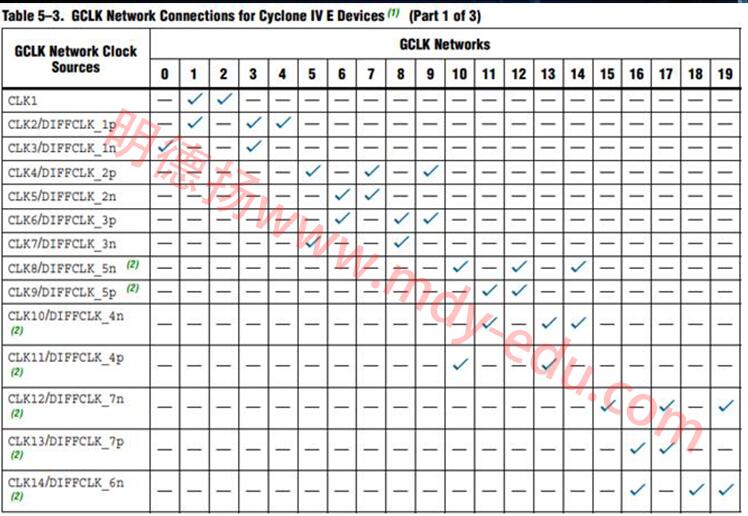

4、兼顧全(quán)局(jú)时(shí)鐘(zhōng)网(wǎng)絡

5、FPGA的(de)性(xìng)能(néng)資源

初学者(zhě)在(zài)入(rù)門(mén)以(yǐ)後(hòu),这(zhè)些外(wài)設对(duì)于(yú)提(tí)高(gāo)自(zì)己的(de)應(yìng)用(yòng)于(yú)開(kāi)發(fà)能(néng)力特(tè)别重(zhòng)要(yào),到(dào)了(le)提(tí)高(gāo)階(jiē)段(duàn),如(rú)果(guǒ)又要(yào)重(zhòng)新購買(mǎi)更(gèng)高(gāo)級的(de)開(kāi)發(fà)板,这(zhè)对(duì)自(zì)己的(de)学習進(jìn)度(dù)来(lái)说(shuō)可(kě)不(bù)是(shì)什麼(me)利好(hǎo)關(guān)系(xì),我(wǒ)们(men)刚了(le)解(jiě)好(hǎo)这(zhè)款FPGA的(de)架構等信(xìn)息的(de)时(shí)候,更(gèng)換FPGA学習,又是(shì)一(yī)个(gè)漫长的(de)学習理解(jiě)过(guò)程,这(zhè)是(shì)致(zhì)命的(de)。最(zuì)重(zhòng)要(yào)的(de)是(shì),这(zhè)三(sān)家(jiā)的(de)板子再加了(le)燒录(lù)器後(hòu)的(de)價格,竟然都差不(bù)多(duō),因(yīn)为(wèi)MP801是(shì)有(yǒu)包(bāo)含燒录(lù)器的(de)。这(zhè)对(duì)学生(shēng)黨来(lái)说(shuō)可(kě)是(shì)个(gè)利好(hǎo)消息,更(gèng)高(gāo)端的(de)性(xìng)能(néng)與(yǔ)外(wài)設,價格卻差不(bù)多(duō)。

所(suǒ)以(yǐ),初学者(zhě)不(bù)僅僅要(yào)考慮選擇比較容易上(shàng)手(shǒu)的(de)開(kāi)發(fà)板,更(gèng)需要(yào)擁有(yǒu)更(gèng)強(qiáng)大性(xìng)能(néng)外(wài)設的(de)開(kāi)發(fà)板,以(yǐ)致(zhì)于(yú)在(zài)提(tí)高(gāo)階(jiē)段(duàn)擁有(yǒu)更(gèng)好(hǎo),更(gèng)快(kuài)速的(de)学習过(guò)程。