JESD204B时(shí)鐘(zhōng)网(wǎng)絡

本(běn)文(wén)为(wèi)明(míng)德揚原創文(wén)章(zhāng),轉(zhuǎn)载請注明(míng)出(chū)处!作者(zhě):陳刀(dāo)刀(dāo)

明(míng)德揚的(de)JESD204B采集卡(kǎ)項目綜合上(shàng)板後(hòu),可(kě)以(yǐ)使用(yòng)上(shàng)位機(jī)通(tòng)过(guò)千(qiān)兆(zhào)网(wǎng)来(lái)配置AD9144和(hé)AD9516板卡(kǎ),实現(xiàn)高(gāo)速ad采集。最(zuì)終(zhōng)可(kě)以(yǐ)在(zài)示波(bō)器和(hé)上(shàng)位機(jī)上(shàng)采集到(dào)設定(dìng)頻率的(de)正(zhèng)弦波(bō)。本(běn)文(wén)重(zhòng)點(diǎn)介紹JESD204B时(shí)鐘(zhōng)网(wǎng)絡。

一(yī),JESD204B时(shí)鐘(zhōng)网(wǎng)絡原理概述

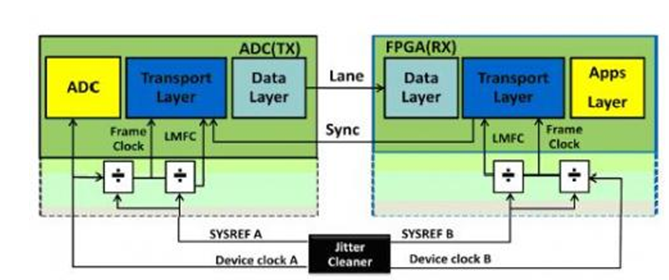

本(běn)文(wén)以(yǐ)JESD204B subclass1来(lái)讨論时(shí)鐘(zhōng)的(de)时(shí)序需要(yào)以(yǐ)及(jí)TI时(shí)鐘(zhōng)芯片(piàn)方(fāng)案(àn)的(de)实現(xiàn)。任何一(yī)个(gè)串行協議都離不(bù)開(kāi)幀和(hé)同(tóng)步,JESD204B也(yě)不(bù)例外(wài),也(yě)需要(yào)收(shōu)發(fà)双(shuāng)方(fāng)有(yǒu)相同(tóng)的(de)幀結構,然後(hòu)以(yǐ)一(yī)種(zhǒng)方(fāng)式来(lái)同(tóng)步,即辨别起始。JESD204B是(shì)以(yǐ)时(shí)鐘(zhōng)信(xìn)号(hào)的(de)沿来(lái)辨别同(tóng)步的(de)開(kāi)始,以(yǐ)及(jí)通(tòng)过(guò)一(yī)定(dìng)的(de)握手(shǒu)信(xìn)号(hào)使得收(shōu)發(fà)双(shuāng)方(fāng)能(néng)够正(zhèng)确識别幀的(de)长度(dù)和(hé)邊(biān)界,因(yīn)此(cǐ)时(shí)鐘(zhōng)信(xìn)号(hào)及(jí)其时(shí)序關(guān)系(xì)对(duì)于(yú)JESD204B就(jiù)顯得极(jí)其重(zhòng)要(yào)。下(xià)图(tú)是(shì)典型的(de)JESD204B系(xì)統的(de)系(xì)統連(lián)接:

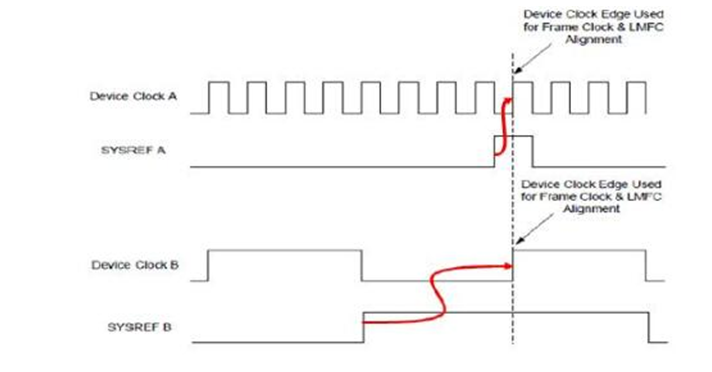

Device Clock是(shì)器件(jiàn)工作的(de)主(zhǔ)时(shí)鐘(zhōng),一(yī)般在(zài)數模轉(zhuǎn)換器里(lǐ)为(wèi)其采樣(yàng)时(shí)鐘(zhōng)或(huò)者(zhě)整數倍頻的(de)时(shí)鐘(zhōng),其協議本(běn)身(shēn)的(de)幀和(hé)多(duō)幀的(de)时(shí)鐘(zhōng)也(yě)是(shì)基于(yú)Device Clock.SYSREF是(shì)用(yòng)于(yú)指示不(bù)同(tóng)轉(zhuǎn)換器或(huò)者(zhě)邏輯的(de)Device Clock的(de)沿,或(huò)者(zhě)不(bù)同(tóng)器件(jiàn)間(jiān)Deterministic latency的(de)參考。如(rú)下(xià)图(tú)所(suǒ)示,Device Clock和(hé)SYSREF必須滿足的(de)时(shí)序關(guān)系(xì)。

SYSREF的(de)第(dì)一(yī)个(gè)上(shàng)升(shēng)沿要(yào)非(fēi)常容易的(de)能(néng)被(bèi)Device Clock捕捉到(dào),这(zhè)樣(yàng)就(jiù)需要(yào)SYSREF和(hé)Device Clock滿足上(shàng)图(tú)的(de)时(shí)序關(guān)系(xì)。通(tòng)常会(huì)因(yīn)为(wèi)PCB的(de)線(xiàn)长以(yǐ)及(jí)时(shí)鐘(zhōng)器件(jiàn)不(bù)同(tóng)通(tòng)道(dào)輸出(chū)时(shí)的(de)Skew,会(huì)带(dài)来(lái)一(yī)定(dìng)的(de)誤差,Device Clock的(de)上(shàng)升(shēng)沿不(bù)一(yī)定(dìng)正(zhèng)好(hǎo)在(zài)SYSREF的(de)脈沖的(de)正(zhèng)中(zhōng)間(jiān),工程上(shàng)只(zhī)要(yào)在(zài)一(yī)定(dìng)範圍內(nèi)就(jiù)能(néng)保證JESD204收(shōu)發(fà)正(zhèng)常工作。

二(èr),明(míng)德揚JESD204B項目时(shí)鐘(zhōng)网(wǎng)絡介紹

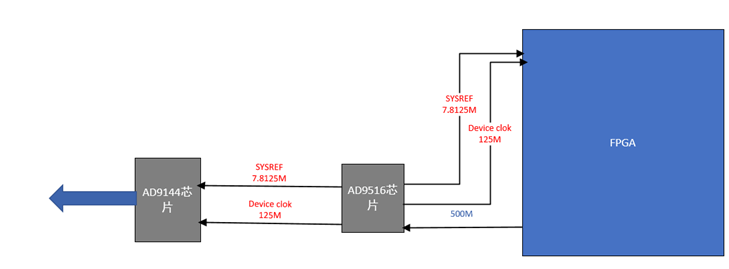

明(míng)德揚JESD204B采集卡(kǎ)項目使用(yòng)Xilinx的(de)KC705開(kāi)發(fà)板,外(wài)接的(de)DA板卡(kǎ)包(bāo)含ad9144芯片(piàn)和(hé)ad9516时(shí)鐘(zhōng)芯片(piàn)。

該項目由(yóu)FPGA發(fà)送一(yī)个(gè)源时(shí)鐘(zhōng)到(dào)ad9516芯片(piàn),接着由(yóu)ad9516芯片(piàn)輸出(chū)4个(gè)时(shí)鐘(zhōng),其中(zhōng)2个(gè)时(shí)鐘(zhōng)輸送到(dào)FPGA,另(lìng)外(wài)2个(gè)时(shí)鐘(zhōng)輸送到(dào)ad9144芯片(piàn)。具體(tǐ)架構如(rú)下(xià)图(tú):

AD9516介紹

AD9516,这(zhè)是(shì)一(yī)个(gè)由(yóu)ADI公司設計(jì)的(de)14路(lù)輸出(chū)时(shí)鐘(zhōng)發(fà)生(shēng)器,具有(yǒu)亞皮秒(miǎo)級抖動(dòng)性(xìng)能(néng),還(huán)配有(yǒu)片(piàn)內(nèi)集成(chéng)鎖相环(huán)(PLL)和(hé)電(diàn)壓控制振蕩器(VCO)。片(piàn)內(nèi)VCO的(de)調諧頻率範圍为(wèi)2.55 GHz至(zhì)2.95 GHz。或(huò)者(zhě),也(yě)可(kě)以(yǐ)使用(yòng)最(zuì)高(gāo)2.4 GHz的(de)外(wài)部(bù)VCO/VCXO。

AD9516有(yǒu)6路(lù)(3对(duì))LVPECL輸出(chū),4路(lù)(2对(duì))LVDS輸出(chū)以(yǐ)及(jí)8路(lù)LVCMOS(每个(gè)LVDS可(kě)以(yǐ)作为(wèi)2路(lù)LVCMOS)輸出(chū)。每对(duì)之間(jiān)共(gòng)享數值为(wèi)1-32的(de)分(fēn)頻數值,因(yīn)此(cǐ),每对(duì)LVPECL或(huò)者(zhě)LVDS輸出(chū)的(de)时(shí)鐘(zhōng)頻率是(shì)相同(tóng)的(de)。LVPECL輸出(chū)可(kě)达(dá)1.6GHz,LVDS輸出(chū)可(kě)达(dá)800MHz,LVCMOS可(kě)达(dá)250MHz。輸入(rù)參考时(shí)鐘(zhōng)頻率和(hé)VCO工作頻率有(yǒu)如(rú)關(guān)系(xì): Fvco=(Fref/R)*(P*B+A)

每路(lù)輸出(chū)還(huán)有(yǒu)單路(lù)的(de)分(fēn)頻因(yīn)子(1-32)可(kě)以(yǐ)配置,通(tòng)过(guò)參考时(shí)鐘(zhōng)的(de)選擇,內(nèi)部(bù)P、B、A寄存器以(yǐ)及(jí)每路(lù)分(fēn)頻寄存器的(de)配置,可(kě)以(yǐ)得到(dào)我(wǒ)们(men)想(xiǎng)要(yào)的(de)时(shí)鐘(zhōng)。

以(yǐ)上(shàng)就(jiù)是(shì)關(guān)于(yú)明(míng)德揚JESD204B的(de)时(shí)鐘(zhōng)网(wǎng)絡的(de)介紹,明(míng)德揚可(kě)承接基于(yú)JESD204B的(de)高(gāo)速數據(jù)傳輸項目,若想(xiǎng)了(le)解(jiě)更(gèng)多(duō),可(kě)聯系(xì)Q1277642036陳刀(dāo)刀(dāo)。