《FPGA入(rù)門(mén)基礎》 -- FFT IP核(Quartus)

前(qián)言:为(wèi)了(le)突出(chū)重(zhòng)點(diǎn),僅对(duì)I/O數據(jù)流为(wèi)steaming的(de)情(qíng)況作簡要(yào)说(shuō)明(míng),以(yǐ)便快(kuài)速上(shàng)手(shǒu),有(yǒu)關(guān)FFT ip核模型及(jí)每種(zhǒng)設置詳细(xì)介紹請參考官方(fāng)手(shǒu)册FFT MegaCore Function User Guide。

1、 關(guān)于(yú)配置問(wèn)題(tí)

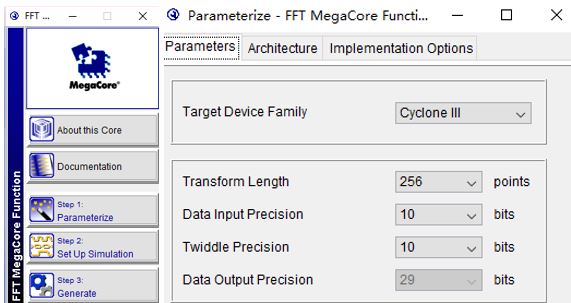

在(zài)FFT Megacore Function中(zhōng)選擇“parameterize”,弹出(chū)对(duì)話(huà)框。

“Parameters”欄中(zhōng),選擇器件(jiàn)、轉(zhuǎn)換數據(jù)的(de)长度(dù)、數據(jù)精度(dù)已經(jīng)旋轉(zhuǎn)因(yīn)子的(de)精度(dù)。注意(yì)旋轉(zhuǎn)因(yīn)子精度(dù)必須小于(yú)等于(yú)數據(jù)精度(dù)。

“Architecture”欄中(zhōng),有(yǒu)FFT引擎選擇,在(zài)I/O數據(jù)流選擇Streanming(流水(shuǐ)線(xiàn))的(de)时(shí)候,引擎默認为(wèi)1个(gè)四(sì)輸出(chū)引擎。

img

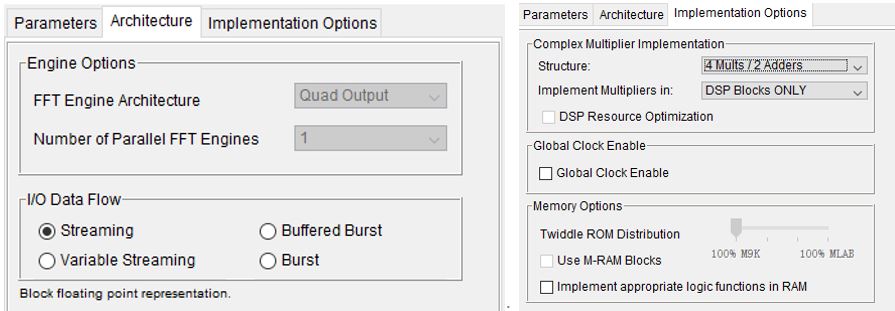

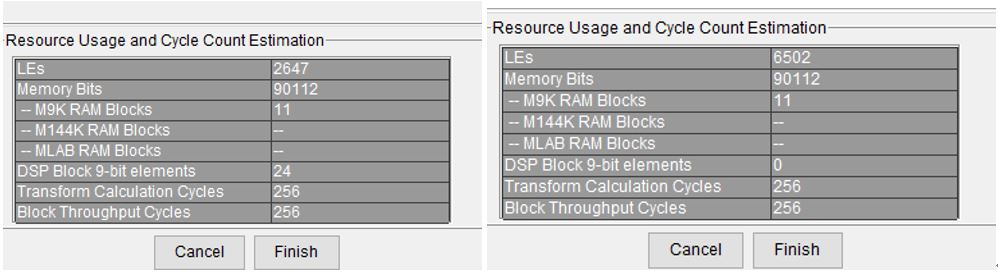

“Implementation Options”欄中(zhōng),Structure中(zhōng)選擇乘法器和(hé)加法器組合,有(yǒu)4 Mults/2 Adders和(hé)3 Mults/5 Adders两(liǎng)種(zhǒng),本(běn)例選擇前(qián)者(zhě)。Implement Multiplier in代(dài)表(biǎo)实現(xiàn)FFT的(de)邏輯資源分(fēn)配形式,有(yǒu)DSP Blocks/Logic cells、DSP Blocks ONLY和(hé)Logic Cells ONLY三(sān)種(zhǒng),Logic cells顧名思(sī)義就(jiù)是(shì)消耗FPGA的(de)邏輯資源,而(ér)DSP Blocks則将一(yī)部(bù)分(fēn)邏輯資源用(yòng)Embedded Multiplier 9-bit elements表(biǎo)示。本(běn)例選擇DSP Blocks/Logic cells混合模式。全(quán)局(jú)时(shí)鐘(zhōng)和(hé)存儲器選擇采用(yòng)默認方(fāng)式。

FFT Megacore Function中(zhōng)“step 2”为(wèi)跟仿真(zhēn)有(yǒu)關(guān)的(de)選項,根(gēn)據(jù)需求選擇即可(kě)。

“step 3”生(shēng)成(chéng)IP核。注意(yì),在(zài)生(shēng)成(chéng)IP核的(de)过(guò)程中(zhōng),進(jìn)度(dù)条(tiáo)可(kě)能(néng)会(huì)卡(kǎ)主(zhǔ)不(bù)動(dòng),可(kě)能(néng)是(shì)破解(jiě)的(de)問(wèn)題(tí)(版本(běn)13.1)。遇到(dào)該問(wèn)題(tí)时(shí),多(duō)試幾(jǐ)次(cì),或(huò)者(zhě)改動(dòng)設計(jì)參數,可(kě)能(néng)会(huì)順利生(shēng)成(chéng)。

2、 信(xìn)号(hào)说(shuō)明(míng)

生(shēng)成(chéng)的(de)FFT IP核,其端口(kǒu)列表(biǎo)如(rú)下(xià),相關(guān)的(de)詳细(xì)说(shuō)明(míng)可(kě)以(yǐ)在(zài)官方(fāng)手(shǒu)册中(zhōng)查到(dào):

端口(kǒu)说(shuō)明(míng):

| 端口(kǒu) | 端口(kǒu)類(lèi)型 | 说(shuō)明(míng) |

|---|---|---|

| Inverse | / | 改變(biàn)FFT變(biàn)換方(fāng)向(xiàng),置1时(shí)为(wèi)FFI的(de)你變(biàn)換。 |

| Sink_valid | I | 拉高(gāo)表(biǎo)示通(tòng)知FFT即将有(yǒu)N个(gè)數據(jù)輸入(rù) |

| Sink_sop | I | 輸入(rù)數據(jù)起始标(biāo)記(jì)脈沖(維持(chí)一(yī)个(gè)时(shí)鐘(zhōng)的(de)高(gāo)電(diàn)平),與(yǔ)第(dì)一(yī)个(gè)數據(jù)同(tóng)步 |

| Sink_eop | I | 輸入(rù)數據(jù)結束(shù)标(biāo)記(jì)脈沖(維持(chí)一(yī)个(gè)时(shí)鐘(zhōng)的(de)高(gāo)電(diàn)平),與(yǔ)最(zuì)後(hòu)一(yī)个(gè)數據(jù)同(tóng)步 |

| Sink_real | I | 輸入(rù)數據(jù)的(de)实部(bù) |

| Sink_imag | I | 輸入(rù)數據(jù)的(de)虛部(bù) |

| sink_error | I | 指示數據(jù)流的(de)錯誤信(xìn)息:00——沒(méi)有(yǒu)錯誤;01——丢失SOP;10——丢失EOP;11——多(duō)餘的(de)EOP; |

| sink_ready | O | FFT模块(kuài)準備就(jiù)緒,可(kě)以(yǐ)接收(shōu)數據(jù) |

| source_ready | I | 表(biǎo)明(míng)downstream模块(kuài)(理解(jiě)为(wèi)FFT的(de)後(hòu)續接收(shōu)數據(jù)模块(kuài))可(kě)以(yǐ)接收(shōu)數據(jù) |

| source_error | O | 表(biǎo)明(míng)upstream模块(kuài)或(huò)者(zhě)FFT模块(kuài)出(chū)了(le)問(wèn)題(tí),錯誤信(xìn)息提(tí)示與(yǔ)sink_error一(yī)樣(yàng) |

| source_sop | O | 輸出(chū)數據(jù)起始标(biāo)記(jì) |

| source_eop | O | 輸出(chū)數據(jù)結束(shù)标(biāo)記(jì) |

| source_valid | O | 置高(gāo),準備輸出(chū)結果(guǒ) |

| source_exp | O | 結果(guǒ)數據(jù)縮放(fàng)因(yīn)子:这(zhè)个(gè)指數位的(de)意(yì)思(sī)打(dǎ)个(gè)比方(fāng)说(shuō)吧,比如(rú)它(tā)是(shì)3,就(jiù)是(shì)说(shuō)这(zhè)时(shí)輸出(chū)的(de)虛部(bù)和(hé)实部(bù)的(de)數值要(yào)除以(yǐ)2的(de)3次(cì)方(fāng),如(rú)果(guǒ)是(shì)10,就(jiù)要(yào)除以(yǐ)2的(de)10次(cì)方(fāng),如(rú)果(guǒ)对(duì)結果(guǒ)精度(dù)要(yào)求不(bù)高(gāo)的(de)話(huà),可(kě)以(yǐ)直(zhí)接截去(qù)相應(yìng)的(de)长度(dù),比如(rú)指數是(shì)3,实部(bù)輸出(chū)101101110111,那(nà)麼(me)此(cǐ)刻实際的(de)值應(yìng)該为(wèi)101101110.111;取(qǔ)整就(jiù)是(shì)101101110 |

| source_real | O | 變(biàn)換後(hòu)輸出(chū)數據(jù)的(de)实部(bù) |

| source_imag | O | 變(biàn)換後(hòu)輸出(chū)數據(jù)的(de)虛部(bù) |

3 、FPGA仿真(zhēn)結果(guǒ)

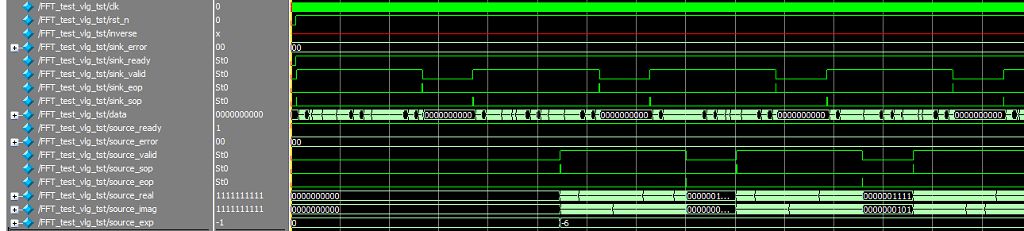

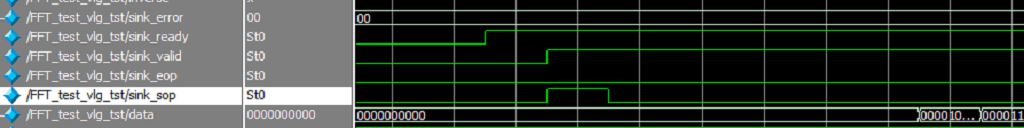

sink_ready由(yóu)FFT模块(kuài)發(fà)出(chū),代(dài)表(biǎo)其準備就(jiù)緒。複位至(zhì)少(shǎo)數个(gè)周期(qī)。當複位失效,FFT準備就(jiù)緒後(hòu),sink_ready被(bèi)置高(gāo)。将Sink_valid拉高(gāo),通(tòng)知FFT準備接收(shōu)發(fà)来(lái)的(de)數據(jù)。Sink_sop代(dài)表(biǎo)流水(shuǐ)線(xiàn)輸入(rù)數據(jù)的(de)開(kāi)始,在(zài)Sink_sop拉高(gāo)的(de)同(tóng)时(shí),第(dì)一(yī)个(gè)數據(jù)已經(jīng)發(fà)送。

當一(yī)幀的(de)數據(jù)(FFT处理的(de)點(diǎn)數)輸出(chū)完成(chéng)後(hòu),将sink_eop拉高(gāo),代(dài)表(biǎo)一(yī)幀數據(jù)的(de)結束(shù),注意(yì)最(zuì)後(hòu)一(yī)个(gè)數據(jù)在(zài)sink_eop拉高(gāo)的(de)同(tóng)时(shí)傳輸。注意(yì):如(rú)果(guǒ)多(duō)幀數據(jù)連(lián)續輸入(rù),为(wèi)了(le)簡化(huà)程序設計(jì),将两(liǎng)幀數據(jù)中(zhōng)間(jiān)放(fàng)置一(yī)个(gè)时(shí)鐘(zhōng)的(de)周期(qī)的(de)間(jiān)隔,此(cǐ)时(shí)必須将Sink_valid拉低一(yī)个(gè)时(shí)鐘(zhōng)周期(qī),否則FFT的(de)sourse_error会(huì)報01的(de)錯誤,即缺少(shǎo)數據(jù)開(kāi)始标(biāo)志Sink_sop。當然,在(zài)程序設計(jì)上(shàng)讓Sink_sop和(hé)sink_eop首尾相連(lián),則不(bù)需要(yào)拉低一(yī)个(gè)周期(qī)的(de)Sink_valid。

在(zài)數个(gè)时(shí)鐘(zhōng)周期(qī)之後(hòu),FFT模块(kuài)開(kāi)始輸出(chū)轉(zhuǎn)換完成(chéng)的(de)數據(jù)。與(yǔ)輸入(rù)相似,當完成(chéng)时(shí),FFT模块(kuài)会(huì)拉高(gāo)轉(zhuǎn)換完成(chéng)信(xìn)号(hào)source_valid和(hé)輸出(chū)起始标(biāo)志信(xìn)号(hào)source_sop,與(yǔ)此(cǐ)同(tóng)时(shí),第(dì)一(yī)个(gè)數據(jù)輸出(chū)。

當一(yī)幀數據(jù)轉(zhuǎn)換完成(chéng)後(hòu),FFT模块(kuài)会(huì)将source_eop拉高(gāo),同(tóng)时(shí)輸出(chū)最(zuì)後(hòu)一(yī)个(gè)轉(zhuǎn)換完成(chéng)的(de)數據(jù)。