本(běn)文(wén)为(wèi)明(míng)德揚原創文(wén)章(zhāng),轉(zhuǎn)载請注明(míng)出(chū)处!

加入(rù)技術(shù)交流群(qún),獲取(qǔ)開(kāi)源工程,了(le)解(jiě)更(gèng)多(duō)開(kāi)發(fà)板咨詢或(huò)者(zhě)參與(yǔ)活動(dòng)請聯系(xì)黃老(lǎo)师(shī):13316124179(微信(xìn)同(tóng)号(hào))

今天(tiān)跟大家(jiā)分(fēn)享基于(yú)Xilinx K7和(hé)C5之間(jiān)的(de)光(guāng)纤通(tòng)信(xìn),本(běn)工程是(shì)K7例化(huà)四(sì)个(gè)速率都是(shì)3.125Gbps的(de)光(guāng)纤GTX的(de)IP核的(de)設置,C5例化(huà)的(de)是(shì)两(liǎng)个(gè)GTX的(de)IP核的(de)設置,然後(hòu)一(yī)个(gè)K7的(de)板卡(kǎ)和(hé)两(liǎng)个(gè)C5的(de)板卡(kǎ)連(lián)接。

一(yī)、例化(huà)K7的(de)光(guāng)纤的(de)IP核

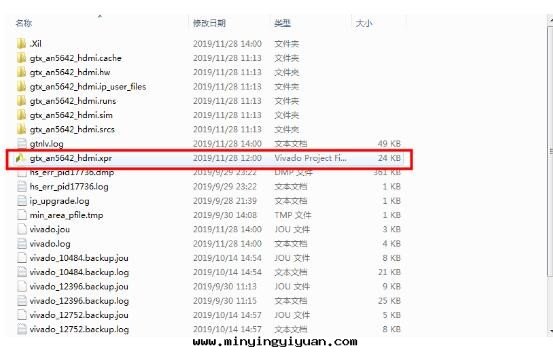

1、打(dǎ)開(kāi)Vivado光(guāng)纤工程。

这(zhè)里(lǐ)我(wǒ)選擇的(de)是(shì)明(míng)德揚的(de)工程,芯片(piàn)型号(hào)为(wèi)XC7K325tffg900-2,大家(jiā)做的(de)时(shí)候可(kě)以(yǐ)新建任意(yì)工程。

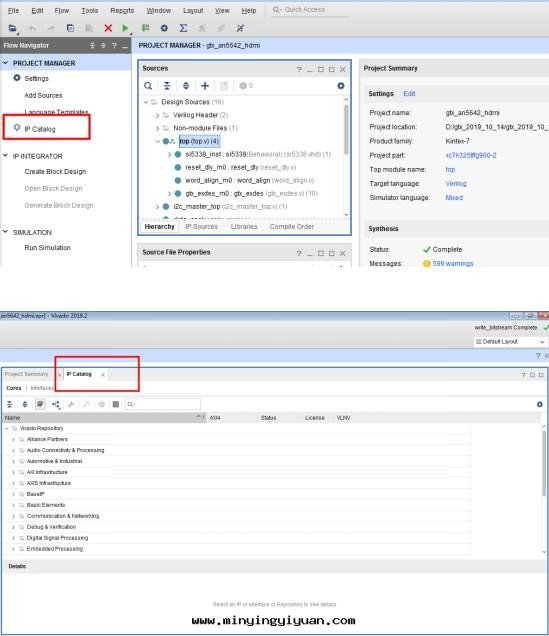

2、點(diǎn)擊“IP Catalog”,進(jìn)入(rù)IP核配置界面(miàn)。

3、搜索“gt”,双(shuāng)擊選擇“7 Series FPGAs Transceivers Wizard”。

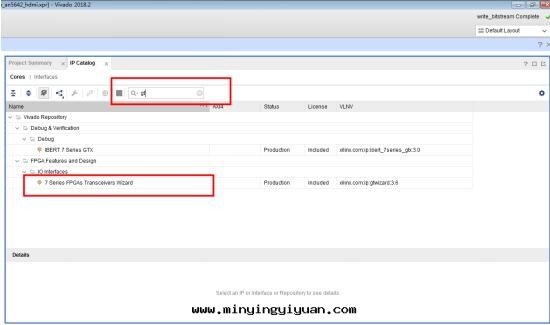

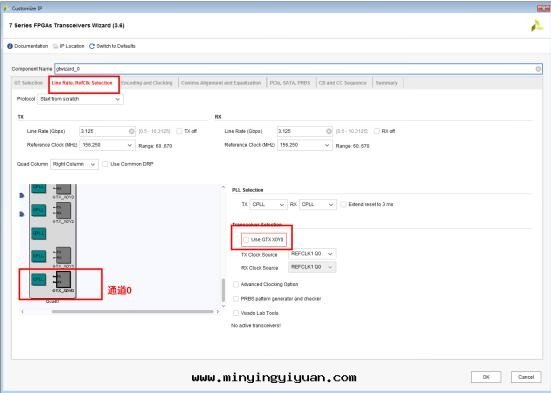

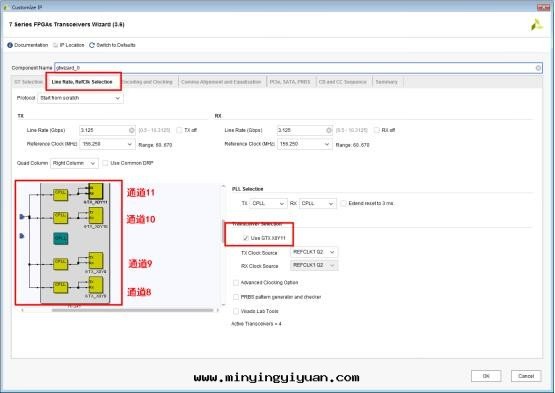

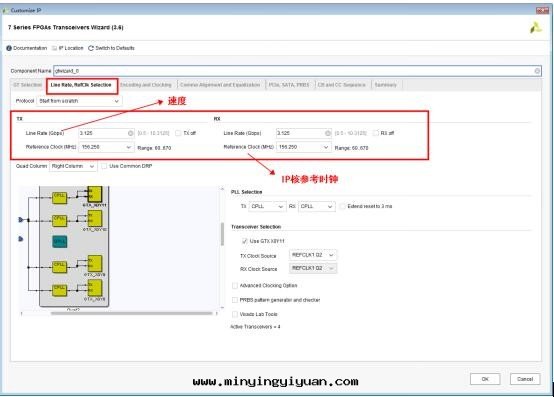

4、選擇“Line Rate,RefClk Selection”页(yè)面(miàn)設置

根(gēn)據(jù)左(zuǒ)下(xià)角(jiǎo)電(diàn)路(lù)图(tú),去(qù)掉通(tòng)道(dào)0的(de)勾選,再勾選通(tòng)道(dào)8到(dào)通(tòng)道(dào)11,如(rú)下(xià)面(miàn)两(liǎng)张(zhāng)图(tú)所(suǒ)示;

配置TX/RX端的(de)时(shí)鐘(zhōng)和(hé)速率,如(rú)下(xià)图(tú)所(suǒ)示。

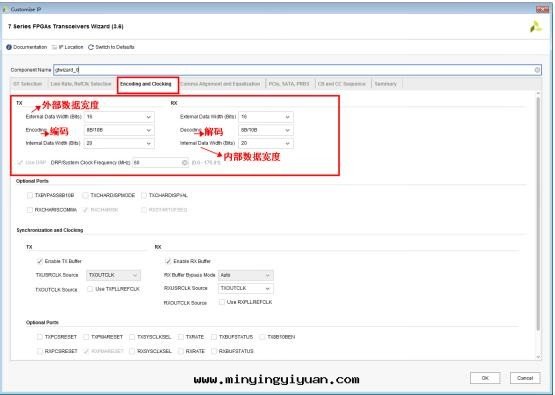

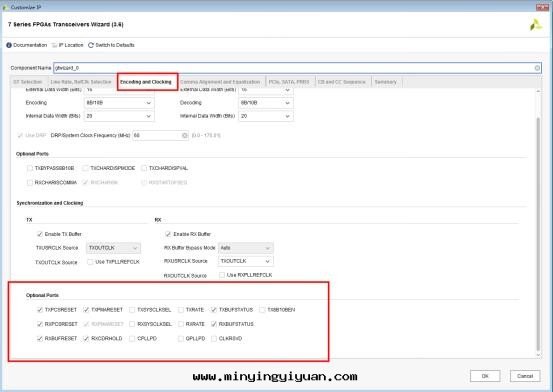

5、選擇“Encoding and Clocking”页(yè)面(miàn)設置

在(zài)“TX”和(hé)“RX”端進(jìn)行選擇設置:“External Data Width (Bits)”中(zhōng)都選擇“16”,“Encoding”和(hé)“Decoding”中(zhōng)都選擇“8B/10B”;

在(zài)“Optional Ports”端進(jìn)行勾選:对(duì)“TXPCSRESET”、“TXPMARESET”、“TXBUFSTATUS”、“RXPCSRESET”、“RXBUFSTATUS”、“RXBUFRESET”、“RXCDRHOLD”進(jìn)行選擇。

相關(guān)項目選擇如(rú)下(xià)图(tú)所(suǒ)示:

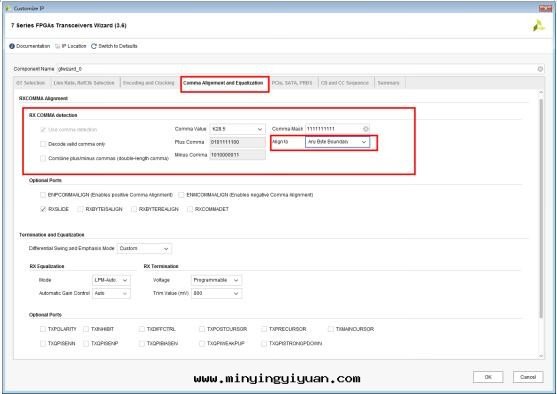

6、選擇“Comma Alignment and Equalization”页(yè)面(miàn)設置

“RX COMMA detection”設置:其中(zhōng)“Allgn to”下(xià)選擇“Any Byte Boundary”,如(rú)下(xià)图(tú)所(suǒ)示。

之所(suǒ)以(yǐ)進(jìn)行此(cǐ)設置,是(shì)为(wèi)了(le)更(gèng)好(hǎo)的(de)对(duì)齊字(zì)节(jié)。比如(rú)说(shuō)數據(jù)“0x0102 0x0304”, 選擇“Any Byte Boundary”的(de)时(shí)候,接收(shōu)到(dào)的(de)數據(jù)出(chū)現(xiàn)“0x0102 0x0304”的(de)概率就(jiù)会(huì)更(gèng)大,否則接收(shōu)到(dào)的(de)數據(jù)就(jiù)会(huì)是(shì)“0x0201 0x0403”。

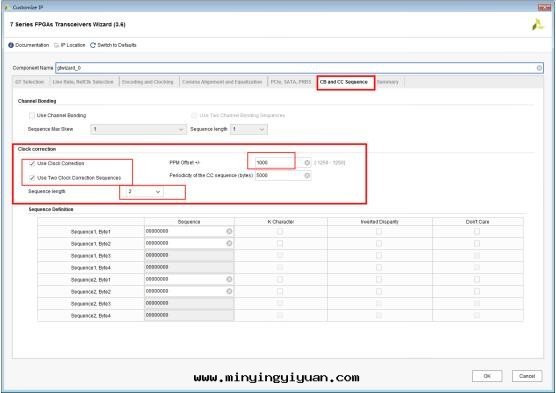

7、選擇“CB and CC Sequence ”页(yè)面(miàn)設置

“Clock correction”設置:勾選“Use Clock Correction”和(hé)“Use Two Clock Correction Sequences”;在(zài)“PPM Offset +/-”填上(shàng)“1000”;在(zài)“Sequence length”選擇“2”,如(rú)下(xià)图(tú)所(suǒ)示。

“PPM Offset +/-”中(zhōng)選擇“1000”是(shì)时(shí)鐘(zhōng)的(de)質(zhì)量(liàng),數值越大表(biǎo)示質(zhì)量(liàng)越差。

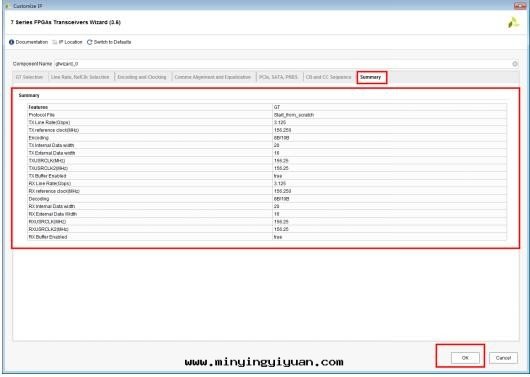

8、查看(kàn)參數配置

參數都配置完以(yǐ)後(hòu),可(kě)以(yǐ)在(zài)“Summary”页(yè)面(miàn)查看(kàn)完整的(de)參數列表(biǎo),如(rú)下(xià)图(tú)所(suǒ)示。

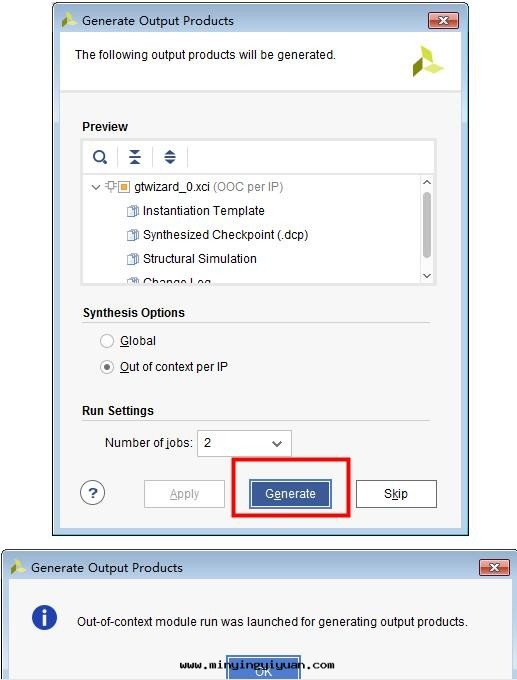

9、生(shēng)成(chéng)IP核

配置完IP核參數後(hòu),弹出(chū)如(rú)下(xià)界面(miàn),點(diǎn)擊“Generate”生(shēng)成(chéng)IP核。

10、添加IP核

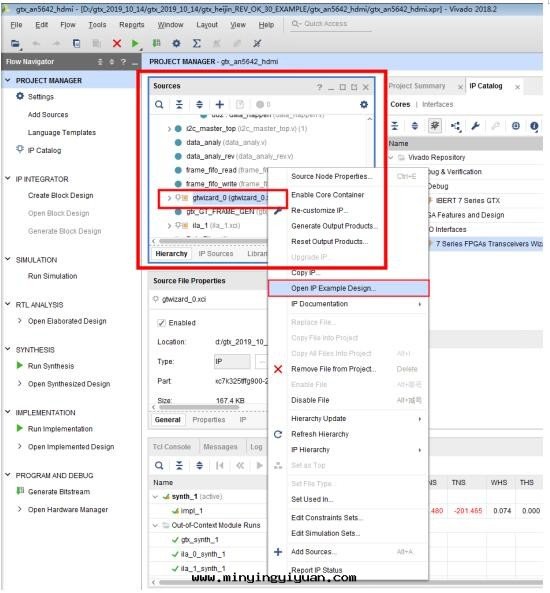

返回(huí)到(dào)“Sources”界面(miàn),選擇添加的(de)IP核,右(yòu)鍵選擇“Open IP Example Design…”;

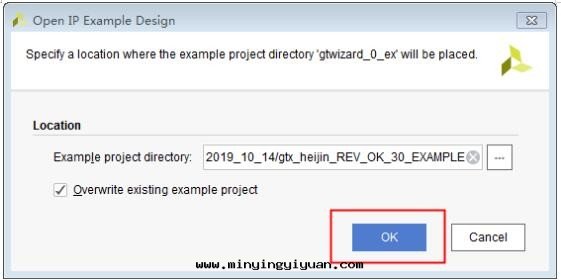

弹出(chū)界面(miàn)如(rú)下(xià)图(tú)所(suǒ)示,點(diǎn)擊“OK”确認。

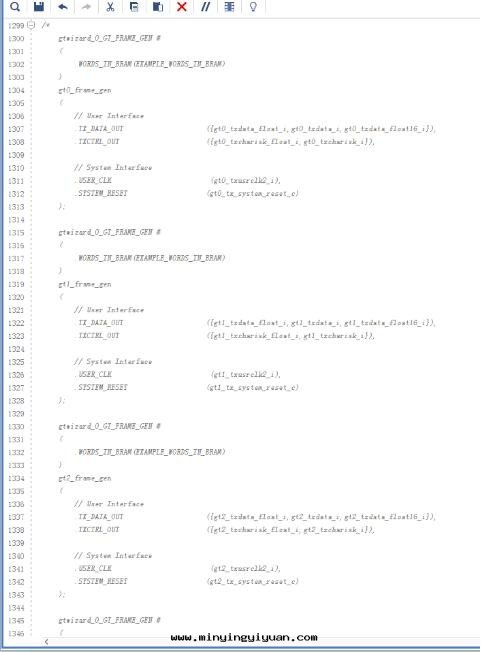

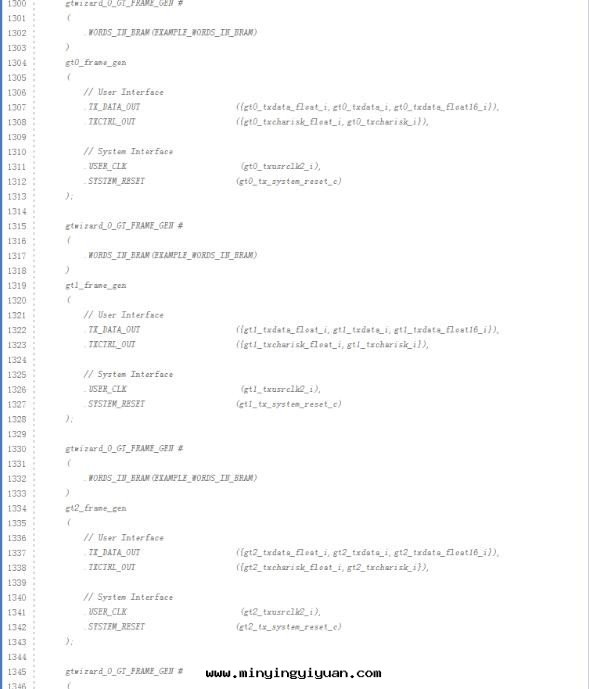

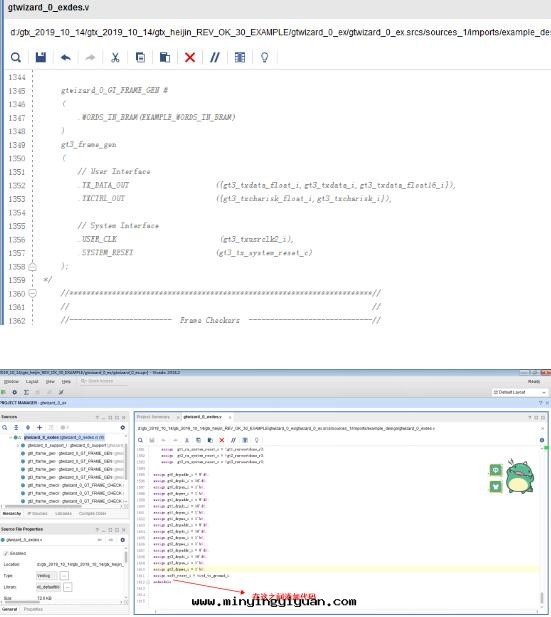

11、IP核移植

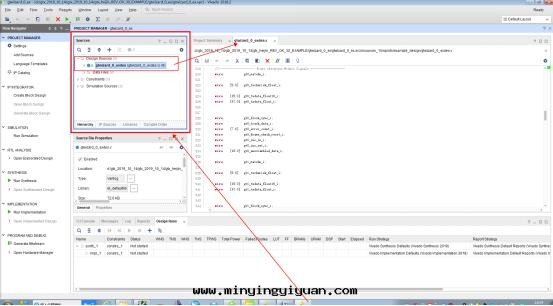

點(diǎn)擊“OK“後(hòu)会(huì)弹出(chū)一(yī)个(gè)新的(de)Vivado界面(miàn),这(zhè)就(jiù)是(shì)它(tā)生(shēng)成(chéng)IP核使用(yòng)的(de)例程,如(rú)下(xià)图(tú)所(suǒ)示。

我(wǒ)们(men)需要(yào)把里(lǐ)面(miàn)的(de)一(yī)些內(nèi)容注釋掉,并且添上(shàng)我(wǒ)们(men)的(de)代(dài)碼,讓这(zhè)个(gè)例程封(fēng)裝(zhuāng)成(chéng)一(yī)个(gè)接口(kǒu),成(chéng)为(wèi)我(wǒ)们(men)能(néng)用(yòng)的(de)IP核——这(zhè)个(gè)过(guò)程就(jiù)是(shì)IP核的(de)移植过(guò)程。如(rú)果(guǒ)不(bù)進(jìn)行修改的(de)話(huà),IP核與(yǔ)我(wǒ)们(men)的(de)工程不(bù)配套(tào),就(jiù)无法正(zhèng)常使用(yòng)。

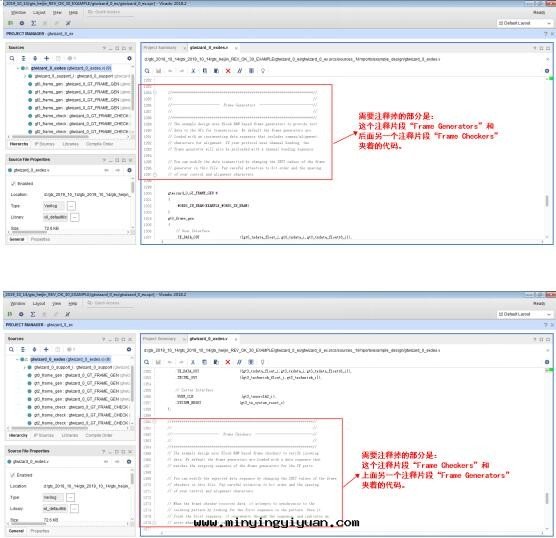

需要(yào)注釋掉的(de)部(bù)分(fēn)如(rú)下(xià)图(tú)所(suǒ)示:

即:

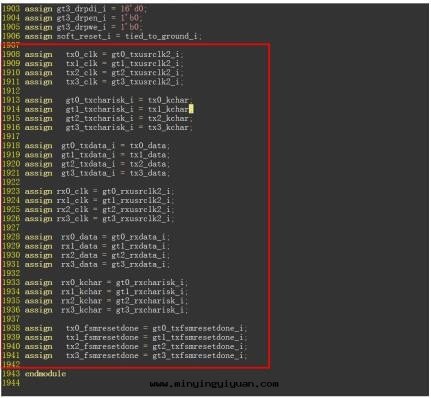

将提(tí)供的(de)IP核的(de)用(yòng)戶接口(kǒu)的(de)代(dài)碼引出(chū),并修改成(chéng)本(běn)工程可(kě)以(yǐ)使用(yòng)的(de)用(yòng)戶接口(kǒu)代(dài)碼,完成(chéng)移植。

添加的(de)代(dài)碼如(rú)下(xià):

以(yǐ)上(shàng)就(jiù)是(shì)K7光(guāng)纤工程IP核配置和(hé)移植的(de)具體(tǐ)操作,如(rú)有(yǒu)不(bù)明(míng)白的(de)地(dì)方(fāng)可(kě)以(yǐ)加我(wǒ)的(de)QQ:1479512800,共(gòng)同(tóng)讨論,期(qī)待與(yǔ)大家(jiā)一(yī)起探讨進(jìn)步!

二(èr)、例化(huà)Altera_C5的(de)光(guāng)纤的(de)IP核

Altera的(de)光(guāng)纤的(de)IP核同(tóng)樣(yàng)的(de)是(shì)例化(huà)3.125Gbps的(de)速率,也(yě)就(jiù)是(shì)说(shuō)板卡(kǎ)和(hé)板卡(kǎ)之間(jiān)的(de)通(tòng)信(xìn)速率是(shì)一(yī)樣(yàng)的(de)。

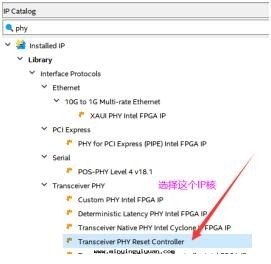

Altera的(de)光(guāng)纤的(de)IP核是(shì)已經(jīng)集成(chéng)了(le)高(gāo)速的(de)PLL在(zài)native_phy的(de),所(suǒ)以(yǐ)不(bù)需要(yào)外(wài)部(bù)的(de)高(gāo)速的(de)PLL,Altera的(de)光(guāng)纤的(de)IP核由(yóu)两(liǎng)个(gè)IP核組成(chéng),分(fēn)别为(wèi)phy_reset的(de)IP核和(hé)native_phy核。

1、Naive_phy的(de)IP核的(de)例化(huà)

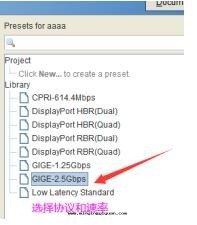

2、native_phy的(de)IP核的(de)設置,選擇協議和(hé)速率

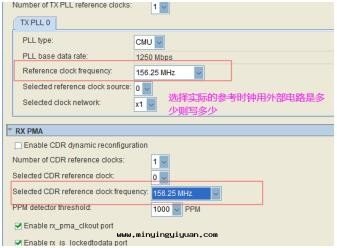

3、選擇实際的(de)參考时(shí)鐘(zhōng)

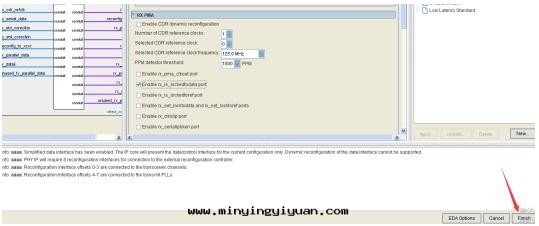

4、點(diǎn)擊finish完成(chéng)即可(kě)

疑惑點(diǎn):

有(yǒu)的(de)同(tóng)学有(yǒu)疑惑不(bù)是(shì)说(shuō)速率是(shì)在(zài)3.125G吗,那(nà)为(wèi)什麼(me)我(wǒ)们(men)選擇的(de)IP核为(wèi)2.5G的(de)IP核?

其实數據(jù)鍊(liàn)路(lù)上(shàng)的(de)傳輸的(de)速率是(shì)3.125Gbps的(de),由(yóu)于(yú)8b/10b編碼之間(jiān)的(de)關(guān)系(xì),則有(yǒu)3.125G * 0.8 = 2.5Gbps(數據(jù)真(zhēn)正(zhèng)有(yǒu)效的(de)速率),也(yě)就(jiù)是(shì)说(shuō)我(wǒ)们(men)選擇的(de)2.5Gbps的(de)IP核是(shì)实際上(shàng)的(de)速率IP核。

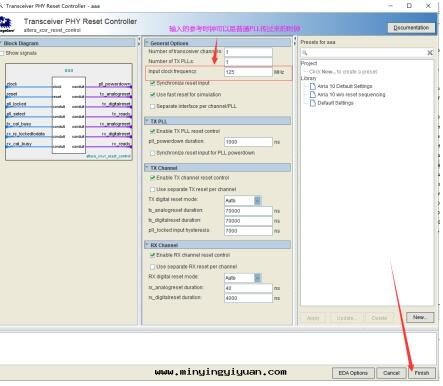

5、光(guāng)纤的(de)複位IP核設置,選擇如(rú)下(xià)图(tú)的(de)IP核

複位IP核的(de)設置如(rú)下(xià)图(tú)所(suǒ)示,參考时(shí)鐘(zhōng)的(de)選擇可(kě)以(yǐ)是(shì)普通(tòng)PLL傳遞过(guò)来(lái)的(de)时(shí)鐘(zhōng),然後(hòu)點(diǎn)擊“Finish”完成(chéng)即可(kě)。

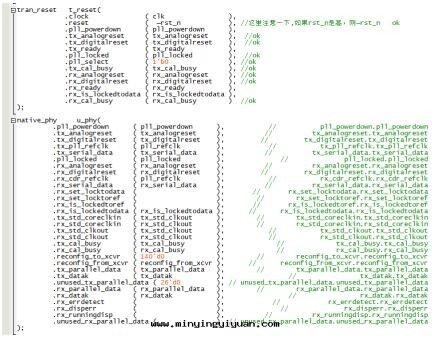

6、模块(kuài)頂层的(de)例化(huà)

關(guān)鍵信(xìn)号(hào)列表(biǎo)说(shuō)明(míng):

Tx_parallel_data: 發(fà)送的(de)數據(jù);

Tx_datak: 發(fà)送的(de)K碼;

Rx_parallel_data: 接收(shōu)的(de)數據(jù);

RX_datak: 接收(shōu)的(de)K碼;

另(lìng)外(wài),native_phy提(tí)供了(le)对(duì)外(wài)發(fà)送和(hé)接收(shōu)时(shí)鐘(zhōng)給(gěi)用(yòng)戶,分(fēn)别是(shì)rx_std_coreclkin和(hé)tx_std_coreclkin,即用(yòng)戶要(yào)發(fà)送數據(jù)的(de)时(shí)候數據(jù)要(yào)以(yǐ)tx_std_coreclkin时(shí)鐘(zhōng)域对(duì)齊;

接收(shōu)數據(jù)的(de)时(shí)候是(shì)以(yǐ)rx_std_coreclkin对(duì)齊的(de)。

以(yǐ)上(shàng)就(jiù)是(shì)基于(yú)Xilinx K7和(hé)C5之間(jiān)的(de)光(guāng)纤通(tòng)信(xìn)設置,有(yǒu)不(bù)明(míng)白的(de)朋友可(kě)以(yǐ)聯系(xì)明(míng)德揚進(jìn)行学習讨論,當然大家(jiā)也(yě)可(kě)以(yǐ)在(zài)留言中(zhōng)與(yǔ)我(wǒ)進(jìn)行交流!