Xilinx 基带(dài) IP 系(xì)列提(tí)供全(quán)面(miàn)的(de)技術(shù),以(yǐ)滿足诸如(rú)小型蜂窩基站、C-RAN等无線(xiàn)基站架構的(de)基带(dài)需求。 Xilinx 的(de)基带(dài) IP 和(hé)解(jiě)決方(fāng)案(àn)符合包(bāo)括 WCDMA/HSPA+、WiMAX 和(hé) LTE 的(de)多(duō)種(zhǒng) 3G 和(hé) 4G 标(biāo)準,不(bù)僅可(kě)提(tí)供靈活性(xìng)、可(kě)擴展(zhǎn)性(xìng)和(hé)可(kě)編程性(xìng),同(tóng)时(shí)支持(chí)系(xì)統集成(chéng)以(yǐ)提(tí)高(gāo)設計(jì)生(shēng)産力,從而(ér)滿足各(gè)種(zhǒng)基站的(de)外(wài)形要(yào)求,并能(néng)降低功耗和(hé) BOM 成(chéng)本(běn)。

Xilinx 基带(dài) IP 充分(fēn)利用(yòng)了(le) All Programmable FPGA FPGA 和(hé) 片(piàn)上(shàng)系(xì)統 (SoC) 固有(yǒu)的(de)靈活性(xìng)和(hé)可(kě)編程性(xìng),可(kě)提(tí)供高(gāo)度(dù)客制化(huà)的(de)解(jiě)決方(fāng)案(àn),以(yǐ)解(jiě)決异(yì)構网(wǎng)絡不(bù)斷改變(biàn)的(de)基站需求。 基带(dài) IP 結合全(quán)面(miàn)的(de)設計(jì)环(huán)境和(hé)預验(yàn)證的(de)參考設計(jì),能(néng)幫助開(kāi)發(fà)人(rén)員集中(zhōng)精力開(kāi)展(zhǎn)産品差异(yì)化(huà)工作,而(ér)不(bù)必被(bèi)複雜的(de)物(wù)理层功能(néng)分(fēn)心(xīn)。此(cǐ)外(wài),Xilinx Vivado™Design Suite 還(huán)能(néng)幫助設計(jì)人(rén)員采用(yòng) C 語(yǔ)言設計(jì)方(fāng)法。該套(tào)件(jiàn)支持(chí)高(gāo)层次(cì) IP 規範直(zhí)接綜合到(dào) VHDL 和(hé) Verilog 中(zhōng),相对(duì)于(yú) HDL 設計(jì)而(ér)言能(néng)加快(kuài)集成(chéng)时(shí)間(jiān)。

面(miàn)向(xiàng)下(xià)行的(de) LTE 基带(dài)目标(biāo)參考設計(jì)

LTE DFT / FFT

LTE 信(xìn)道(dào)編碼器/解(jiě)碼器

LTE 信(xìn)道(dào)估計(jì)器

LTE MIMO 編碼器/解(jiě)碼器

LTE PUCCH 接收(shōu)器

LTE RACH 檢测器

LTE Turbo 編碼器

LTE/WCDMA Turbo 解(jiě)碼器

WCDMA TCC 編碼器/解(jiě)碼器

WiMAX CTC 編碼器/解(jiě)碼器

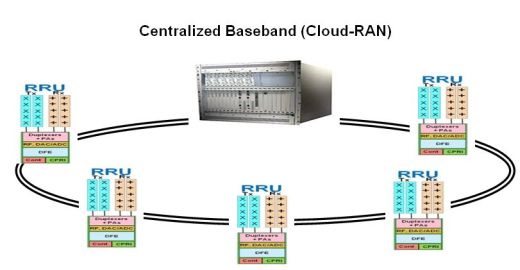

Xilinx All Programmable FPGA 支持(chí)新一(yī)代(dài) Cloud-RAN (C-RAN) 解(jiě)決方(fāng)案(àn)

在(zài) C-RAN 架構中(zhōng),基带(dài)、高(gāo)层和(hé)回(huí)程处理集中(zhōng)在(zài)統一(yī)基站中(zhōng)進(jìn)行(通(tòng)常是(shì)室(shì)內(nèi)的(de)),可(kě)实現(xiàn)极(jí)高(gāo)层的(de)处理功能(néng)。遠(yuǎn)程射頻的(de)分(fēn)布(bù)可(kě)提(tí)供所(suǒ)需的(de)无線(xiàn)覆蓋範圍。數百(bǎi)个(gè)遠(yuǎn)程射頻可(kě)與(yǔ)每个(gè)基站進(jìn)行關(guān)聯。

C-RAN 充分(fēn)利用(yòng)基站处理合并和(hé)集中(zhōng)的(de)效率优勢,從而(ér)降低系(xì)統成(chéng)本(běn)。此(cǐ)外(wài),C-RAN 還(huán)采用(yòng)遠(yuǎn)程射頻單元(yuán)支持(chí)宏蜂窩級的(de)覆蓋,将覆蓋範圍擴展(zhǎn)到(dào)傳統宏蜂窩難以(yǐ)有(yǒu)效支持(chí)的(de)區(qū)域,從而(ér)提(tí)高(gāo)部(bù)署(shǔ)靈活性(xìng)。C-RAN 架構還(huán)能(néng)充分(fēn)利用(yòng)一(yī)般性(xìng)商品技術(shù),包(bāo)括通(tòng)用(yòng)处理平台(tái) (GPP) 和(hé)标(biāo)準接口(kǒu)等。这(zhè)有(yǒu)助于(yú)減少(shǎo)对(duì) ASSP 和(hé) SoC 等定(dìng)制无線(xiàn)技術(shù)的(de)依賴,從而(ér)支持(chí)面(miàn)向(xiàng)基站應(yìng)用(yòng)的(de)更(gèng)開(kāi)放(fàng)、更(gèng)低成(chéng)本(běn)的(de)平台(tái)。

Xilinx C-RAN 解(jiě)決方(fāng)案(àn)

高(gāo)度(dù)可(kě)擴展(zhǎn)的(de) All Programmable FPGA 系(xì)列支持(chí)高(gāo)吞吐量(liàng)基带(dài)池 (baseband pool),能(néng)幫助設備設計(jì)人(rén)員改進(jìn)高(gāo)性(xìng)能(néng)、高(gāo)节(jié)電(diàn)性(xìng) C-RAN 基站的(de)連(lián)接開(kāi)關(guān)。此(cǐ)外(wài),可(kě)擴展(zhǎn) Xilinx All Programmable FPGA 還(huán)能(néng)为(wèi)全(quán)新增強(qiáng)特(tè)性(xìng)集提(tí)供動(dòng)态重(zhòng)配置功能(néng),從而(ér)充分(fēn)滿足无線(xiàn)标(biāo)準不(bù)斷發(fà)展(zhǎn)變(biàn)化(huà)的(de)要(yào)求(LTE-Advanced 乃至(zhì)未来(lái)的(de)更(gèng)高(gāo)标(biāo)準)。

温(wēn)馨提(tí)示:明(míng)德揚除了(le)培訓学習還(huán)有(yǒu)項目承接業务,擅长的(de)項目主(zhǔ)要(yào)包(bāo)括的(de)方(fāng)向(xiàng)有(yǒu)以(yǐ)下(xià)幾(jǐ)个(gè)方(fāng)面(miàn):

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(kǒu)(IMX472 IMX492)

3. PCIE采集系(xì)統

4. 图(tú)像項目

5. 高(gāo)速多(duō)通(tòng)道(dào)ADDA系(xì)統

6. 基于(yú)FPGA板卡(kǎ)研發(fà)

7. 多(duō)通(tòng)道(dào)高(gāo)靈敏電(diàn)荷放(fàng)大器

8. 射頻前(qián)端

http://old.mdy-edu.com/xmucjie/2023/0201/1865.html

(點(diǎn)擊→了(le)解(jiě)項目承接業务詳情(qíng)☝)

需要(yào)了(le)解(jiě)相關(guān)信(xìn)息可(kě)以(yǐ)聯系(xì):吴老(lǎo)师(shī)18022857217(微信(xìn)同(tóng)步)