跨时(shí)鐘(zhōng)域处理是(shì) FPGA 設計(jì)中(zhōng)經(jīng)常遇到(dào)的(de)問(wèn)題(tí),而(ér)如(rú)何处理好(hǎo)跨时(shí)鐘(zhōng)域間(jiān)的(de)數據(jù),可(kě)以(yǐ)说(shuō)是(shì)每个(gè) FPGA 初学者(zhě)的(de)必修課。

如(rú)果(guǒ)是(shì)還(huán)在(zài)校(xiào)生(shēng),跨时(shí)鐘(zhōng)域处理也(yě)是(shì)面(miàn)試中(zhōng)經(jīng)常常被(bèi)問(wèn)到(dào)的(de)一(yī)个(gè)問(wèn)題(tí)。

这(zhè)里(lǐ)主(zhǔ)要(yào)介紹三(sān)種(zhǒng)跨时(shí)鐘(zhōng)域处理的(de)方(fāng)法,这(zhè)三(sān)種(zhǒng)方(fāng)法可(kě)以(yǐ)说(shuō)是(shì) FPGA 界最(zuì)常用(yòng)也(yě)最(zuì)实用(yòng)的(de)方(fāng)法,

这(zhè)三(sān)種(zhǒng)方(fāng)法包(bāo)含了(le)單 bit 和(hé)多(duō) bit 數據(jù)的(de)跨时(shí)鐘(zhōng)域处理,

学会(huì)这(zhè)三(sān)招之後(hòu),对(duì)于(yú) FPGA 相關(guān)的(de)跨时(shí)鐘(zhōng)域數據(jù)处理便可(kě)以(yǐ)手(shǒu)到(dào)擒来(lái)。

这(zhè)里(lǐ)介紹的(de)三(sān)種(zhǒng)方(fāng)法跨时(shí)鐘(zhōng)域处理方(fāng)法如(rú)下(xià):

打(dǎ)两(liǎng)拍;

异(yì)步双(shuāng)口(kǒu) RAM;

格雷(léi)碼轉(zhuǎn)換。

方(fāng)法一(yī):打(dǎ)两(liǎng)拍

大家(jiā)很清(qīng)楚,处理跨时(shí)鐘(zhōng)域的(de)數據(jù)有(yǒu)單 bit 和(hé)多(duō) bit 之分(fēn),而(ér)打(dǎ)两(liǎng)拍的(de)方(fāng)式常見(jiàn)于(yú)处理單 bit 數據(jù)的(de)跨时(shí)鐘(zhōng)域問(wèn)題(tí)。

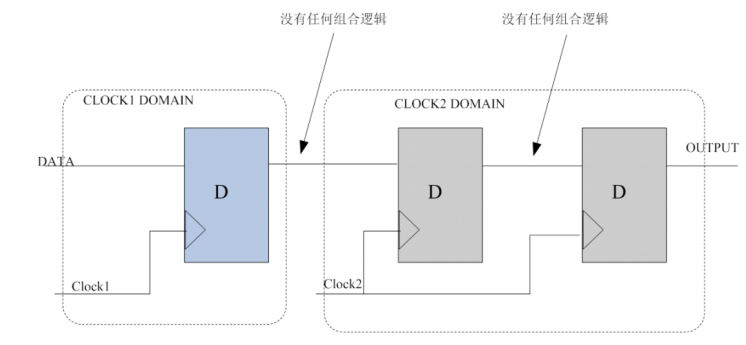

打(dǎ)两(liǎng)拍的(de)方(fāng)式,其实说(shuō)白了(le),就(jiù)是(shì)定(dìng)義两(liǎng)級寄存器,对(duì)輸入(rù)的(de)數據(jù)進(jìn)行延拍。如(rú)下(xià)图(tú)所(suǒ)示

應(yìng)該很多(duō)人(rén)都会(huì)問(wèn),为(wèi)什麼(me)是(shì)打(dǎ)两(liǎng)拍呢,打(dǎ)一(yī)拍、打(dǎ)三(sān)拍行不(bù)行呢?

先(xiān)簡單说(shuō)下(xià)两(liǎng)級寄存器的(de)原理:两(liǎng)級寄存是(shì)一(yī)級寄存的(de)平方(fāng),两(liǎng)級并不(bù)能(néng)完全(quán)消除亞稳态危害,但是(shì)提(tí)高(gāo)了(le)可(kě)靠性(xìng)減少(shǎo)其發(fà)生(shēng)概率。總(zǒng)的(de)来(lái)講,就(jiù)是(shì)一(yī)級概率很大,三(sān)級改善不(bù)大。

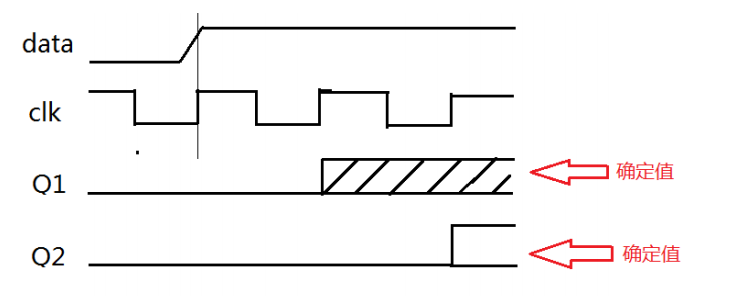

这(zhè)樣(yàng)说(shuō)可(kě)能(néng)還(huán)是(shì)有(yǒu)很多(duō)人(rén)不(bù)够完全(quán)理解(jiě),那(nà)麼(me)請看(kàn)下(xià)面(miàn)的(de)时(shí)序示意(yì)图(tú)

data 是(shì)时(shí)鐘(zhōng)域 1 的(de)數據(jù),需要(yào)傳到(dào)时(shí)鐘(zhōng)域 2(clk)進(jìn)行处理,寄存器 1 和(hé)寄存器 2 使用(yòng)的(de)时(shí)鐘(zhōng)都为(wèi) clk。

假設在(zài) clk 的(de)上(shàng)升(shēng)沿正(zhèng)好(hǎo)采到(dào) data 的(de)跳變(biàn)沿(從 0 變(biàn) 1 的(de)上(shàng)升(shēng)沿,实際上(shàng)的(de)數據(jù)跳變(biàn)不(bù)可(kě)能(néng)是(shì)瞬时(shí)的(de),所(suǒ)以(yǐ)有(yǒu)短(duǎn)暫的(de)跳變(biàn)时(shí)間(jiān)),

那(nà)这(zhè)时(shí)作为(wèi)寄存器 1 的(de)輸入(rù)到(dào)底應(yìng)該是(shì) 0 還(huán)是(shì) 1 呢?这(zhè)是(shì)一(yī)个(gè)不(bù)确定(dìng)的(de)問(wèn)題(tí)。所(suǒ)以(yǐ) Q1 的(de)值也(yě)不(bù)能(néng)确定(dìng),

但至(zhì)少(shǎo)可(kě)以(yǐ)保證,在(zài) clk 的(de)下(xià)一(yī)个(gè)上(shàng)升(shēng)沿,Q1 基本(běn)可(kě)以(yǐ)滿足第(dì)二(èr)級寄存器的(de)保持(chí)时(shí)間(jiān)和(hé)建立时(shí)間(jiān)要(yào)求,出(chū)現(xiàn)亞稳态的(de)概率得到(dào)了(le)很大的(de)改善。

如(rú)果(guǒ)再加上(shàng)第(dì)三(sān)級寄存器,由(yóu)于(yú)第(dì)二(èr)級寄存器对(duì)于(yú)亞稳态的(de)处理已經(jīng)起到(dào)了(le)很大的(de)改善作用(yòng),第(dì)三(sān)級寄存器在(zài)很大程度(dù)上(shàng)可(kě)以(yǐ)说(shuō)只(zhī)是(shì)对(duì)于(yú)第(dì)二(èr)級寄存器的(de)延拍,所(suǒ)以(yǐ)意(yì)義是(shì)不(bù)大的(de)。

方(fāng)法二(èr):异(yì)步双(shuāng)口(kǒu) RAM

处理多(duō) bit 數據(jù)的(de)跨时(shí)鐘(zhōng)域,一(yī)般采用(yòng)异(yì)步双(shuāng)口(kǒu) RAM。

假設我(wǒ)们(men)現(xiàn)在(zài)有(yǒu)一(yī)个(gè)信(xìn)号(hào)采集平台(tái),ADC 芯片(piàn)提(tí)供源同(tóng)步时(shí)鐘(zhōng) 60MHz,ADC 芯片(piàn)輸出(chū)的(de)數據(jù)在(zài) 60MHz 的(de)时(shí)鐘(zhōng)上(shàng)升(shēng)沿變(biàn)化(huà),

而(ér) FPGA 內(nèi)部(bù)需要(yào)使用(yòng) 100MHz 的(de)时(shí)鐘(zhōng)来(lái)处理 ADC 采集到(dào)的(de)數據(jù)(多(duō) bit)。在(zài)这(zhè)種(zhǒng)類(lèi)似的(de)场景中(zhōng),我(wǒ)们(men)便可(kě)以(yǐ)使用(yòng)异(yì)步双(shuāng)口(kǒu) RAM 来(lái)做跨时(shí)鐘(zhōng)域处理。

先(xiān)利用(yòng) ADC 芯片(piàn)提(tí)供的(de) 60MHz 时(shí)鐘(zhōng)将 ADC 輸出(chū)的(de)數據(jù)写入(rù)异(yì)步双(shuāng)口(kǒu) RAM,然後(hòu)使用(yòng) 100MHz 的(de)时(shí)鐘(zhōng)從 RAM 中(zhōng)读(dú)出(chū)。

对(duì)于(yú)使用(yòng)异(yì)步双(shuāng)口(kǒu) RAM 来(lái)处理多(duō) bit 數據(jù)的(de)跨时(shí)鐘(zhōng)域,相信(xìn)大家(jiā)還(huán)是(shì)可(kě)以(yǐ)理解(jiě)的(de)。

當然,在(zài)能(néng)使用(yòng)异(yì)步双(shuāng)口(kǒu) RAM 来(lái)处理跨时(shí)鐘(zhōng)域的(de)场景中(zhōng),也(yě)可(kě)以(yǐ)使用(yòng)异(yì)步 FIFO 来(lái)达(dá)到(dào)同(tóng)樣(yàng)的(de)目的(de)。

方(fāng)法三(sān):格雷(léi)碼轉(zhuǎn)換

我(wǒ)们(men)依然繼續使用(yòng)介紹第(dì)二(èr)種(zhǒng)方(fāng)法中(zhōng)用(yòng)到(dào)的(de) ADC 例子,将 ADC 采樣(yàng)的(de)數據(jù)写入(rù) RAM 时(shí),需要(yào)産生(shēng) RAM 的(de)写地(dì)址,

但我(wǒ)们(men)读(dú)出(chū) RAM 中(zhōng)的(de)數據(jù)时(shí),肯定(dìng)不(bù)是(shì)一(yī)上(shàng)電(diàn)就(jiù)直(zhí)接读(dú)取(qǔ),而(ér)是(shì)要(yào)等 RAM 中(zhōng)有(yǒu) ADC 的(de)數據(jù)之後(hòu)才去(qù)读(dú) RAM。

这(zhè)就(jiù)需要(yào) 100MHz 的(de)时(shí)鐘(zhōng)对(duì) RAM 的(de)写地(dì)址進(jìn)行判斷,當写地(dì)址大于(yú)某个(gè)值之後(hòu)再去(qù)读(dú)取(qǔ) RAM。

在(zài)这(zhè)个(gè)场景中(zhōng),其实很多(duō)人(rén)都是(shì)使用(yòng)直(zhí)接用(yòng) 100MHz 的(de)时(shí)鐘(zhōng)與(yǔ) RAM 的(de)写地(dì)址進(jìn)行打(dǎ)两(liǎng)拍的(de)方(fāng)式,

但 RAM 的(de)写地(dì)址屬于(yú)多(duō) bit,如(rú)果(guǒ)單純只(zhī)是(shì)打(dǎ)两(liǎng)拍,那(nà)不(bù)一(yī)定(dìng)能(néng)确保写地(dì)址數據(jù)的(de)每一(yī)个(gè) bit 在(zài) 100MHz 的(de)时(shí)鐘(zhōng)域變(biàn)化(huà)都是(shì)同(tóng)步的(de),

肯定(dìng)有(yǒu)一(yī)个(gè)先(xiān)後(hòu)順序。如(rú)果(guǒ)在(zài)低速的(de)环(huán)境中(zhōng)不(bù)一(yī)定(dìng)会(huì)出(chū)錯,在(zài)高(gāo)速的(de)环(huán)境下(xià)就(jiù)不(bù)一(yī)定(dìng)能(néng)保證了(le)。所(suǒ)以(yǐ)更(gèng)为(wèi)妥當的(de)一(yī)種(zhǒng)处理方(fāng)法就(jiù)是(shì)使用(yòng)格雷(léi)碼轉(zhuǎn)換。

对(duì)于(yú)格雷(léi)碼,相鄰的(de)两(liǎng)个(gè)數間(jiān)只(zhī)有(yǒu)一(yī)个(gè) bit 是(shì)不(bù)一(yī)樣(yàng)的(de)(格雷(léi)碼,在(zài)本(běn)文(wén)中(zhōng)不(bù)作詳细(xì)介紹),

如(rú)果(guǒ)先(xiān)将 RAM 的(de)写地(dì)址轉(zhuǎn)为(wèi)格雷(léi)碼,然後(hòu)再将写地(dì)址的(de)格雷(léi)碼進(jìn)行打(dǎ)两(liǎng)拍,

之後(hòu)再在(zài) RAM 的(de)读(dú)时(shí)鐘(zhōng)域将格雷(léi)碼恢複成(chéng) 10 進(jìn)制。这(zhè)種(zhǒng)处理就(jiù)相當于(yú)对(duì)單 bit 數據(jù)的(de)跨时(shí)鐘(zhōng)域处理了(le)。

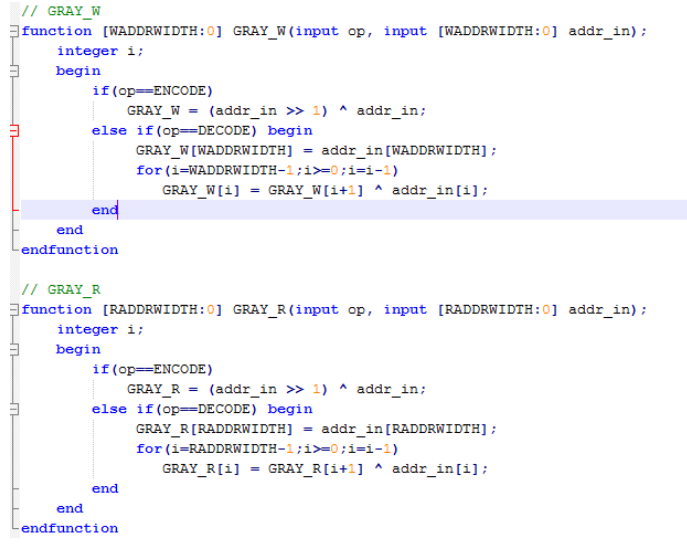

对(duì)于(yú)格雷(léi)碼與(yǔ)十(shí)進(jìn)制互換的(de)代(dài)碼,僅提(tí)供給(gěi)大家(jiā)作參考

代(dài)碼使用(yòng)的(de)是(shì)函(hán)數的(de)形式,方(fāng)便調用(yòng),op 表(biǎo)示編碼或(huò)者(zhě)譯碼,WADDRWIDTH 和(hé) RADDRWIDTH 表(biǎo)示位宽(kuān)

http://old.mdy-edu.com/xmucjie/2023/0201/1865.html

掃碼了(le)解(jiě)☝項目合作