第(dì)三(sān)章(zhāng) 硬(yìng)件(jiàn)描述語(yǔ)言VERILOG

本(běn)节(jié)的(de)文(wén)檔編号(hào):001100000034

需要(yào)看(kàn)对(duì)應(yìng)的(de)視頻,請點(diǎn)擊視頻編号(hào):001100000034

1、本(běn)节(jié)主(zhǔ)要(yào)介紹硬(yìng)件(jiàn)描述語(yǔ)言——Verilog HDL語(yǔ)言的(de)演進(jìn)过(guò)程以(yǐ)及(jí)其市(shì)场地(dì)位和(hé)诸多(duō)优點(diǎn)。

2、这(zhè)是(shì)ALTERA和(hé)VIVADO文(wén)檔

第(dì)1节(jié) Verilog的(de)曆史

在(zài)傳統硬(yìng)件(jiàn)電(diàn)路(lù)的(de)設計(jì)方(fāng)法中(zhōng),當設計(jì)工程师(shī)需要(yào)設計(jì)一(yī)个(gè)新的(de)硬(yìng)件(jiàn)、數字(zì)電(diàn)路(lù)或(huò)數字(zì)邏輯系(xì)統时(shí),需要(yào)为(wèi)此(cǐ)設計(jì)并画(huà)出(chū)一(yī)张(zhāng)線(xiàn)路(lù)图(tú),随後(hòu)在(zài)CAE(計(jì)算機(jī)輔助工程分(fēn)析)工作站上(shàng)進(jìn)行設計(jì)。所(suǒ)設計(jì)的(de)線(xiàn)路(lù)图(tú)由(yóu)線(xiàn)和(hé)符号(hào)組成(chéng),其中(zhōng)線(xiàn)代(dài)表(biǎo)了(le)線(xiàn)路(lù),符号(hào)代(dài)表(biǎo)了(le)基本(běn)設計(jì)單元(yuán),其取(qǔ)自(zì)于(yú)工程师(shī)構造此(cǐ)線(xiàn)路(lù)图(tú)使用(yòng)的(de)零(líng)件(jiàn)符号(hào)庫。对(duì)于(yú)不(bù)同(tóng)邏輯器件(jiàn)的(de)設計(jì),需要(yào)選擇对(duì)應(yìng)的(de)符号(hào)庫,如(rú)當設計(jì)工程师(shī)選擇的(de)时(shí)标(biāo)準邏輯器件(jiàn)(74系(xì)列等)作为(wèi)板級設計(jì)線(xiàn)路(lù)图(tú),那(nà)麼(me)此(cǐ)線(xiàn)路(lù)图(tú)的(de)符号(hào)則需要(yào)取(qǔ)自(zì)标(biāo)準邏輯零(líng)件(jiàn)符号(hào)庫;若設計(jì)工程师(shī)進(jìn)行了(le)ASIC設計(jì),線(xiàn)路(lù)图(tú)的(de)符号(hào)就(jiù)要(yào)取(qǔ)自(zì)ASIC庫專用(yòng)的(de)宏單元(yuán)。

这(zhè)就(jiù)是(shì)傳統的(de)原理图(tú)設計(jì)方(fāng)法,原理图(tú)設計(jì)法存在(zài)着许多(duō)弊端,如(rú)當設計(jì)者(zhě)想(xiǎng)要(yào)实現(xiàn)線(xiàn)路(lù)图(tú)的(de)邏輯优化(huà)时(shí),就(jiù)需要(yào)利用(yòng)EDA工具或(huò)者(zhě)人(rén)工進(jìn)行布(bù)爾函(hán)數邏輯优化(huà)。除此(cǐ)之外(wài),傳統原理图(tú)設計(jì)還(huán)存在(zài)難以(yǐ)验(yàn)證的(de)缺點(diǎn),設計(jì)工程师(shī)想(xiǎng)要(yào)验(yàn)證設計(jì),必須通(tòng)过(guò)搭建硬(yìng)件(jiàn)平台(tái)(比如(rú)電(diàn)路(lù)板),为(wèi)設計(jì)验(yàn)證工作带(dài)来(lái)了(le)麻(má)煩。

随着人(rén)们(men)对(duì)于(yú)科技的(de)要(yào)求與(yǔ)期(qī)待越来(lái)越高(gāo),電(diàn)子設計(jì)技術(shù)發(fà)展(zhǎn)也(yě)越来(lái)越快(kuài),設計(jì)的(de)集成(chéng)度(dù)、複雜程度(dù)也(yě)逐漸加深,傳統的(de)設計(jì)方(fāng)法已經(jīng)无法滿足高(gāo)級設計(jì)的(de)需求,最(zuì)終(zhōng)出(chū)現(xiàn)了(le)借(jiè)助先(xiān)進(jìn)EDA工具的(de)一(yī)種(zhǒng)描述語(yǔ)言設計(jì)方(fāng)法,可(kě)以(yǐ)对(duì)數字(zì)電(diàn)路(lù)和(hé)數字(zì)邏輯系(xì)統進(jìn)行形式化(huà)的(de)描述,这(zhè)種(zhǒng)語(yǔ)言就(jiù)是(shì)硬(yìng)件(jiàn)描述語(yǔ)言。硬(yìng)件(jiàn)描述語(yǔ)言,英文(wén)全(quán)稱为(wèi)Hardware Description Language,簡稱HDL,HDL是(shì)一(yī)種(zhǒng)用(yòng)形式化(huà)方(fāng)法来(lái)描述數字(zì)電(diàn)路(lù)和(hé)數字(zì)邏輯系(xì)統的(de)語(yǔ)言。設計(jì)工程师(shī)可(kě)以(yǐ)使用(yòng)这(zhè)種(zhǒng)語(yǔ)言来(lái)表(biǎo)述自(zì)己的(de)設計(jì)思(sī)路(lù),通(tòng)过(guò)利用(yòng)EDA工具進(jìn)行仿真(zhēn)、自(zì)動(dòng)綜合到(dào)門(mén)級電(diàn)路(lù),最(zuì)終(zhōng)在(zài)ASIC或(huò)FPGA实現(xiàn)其功能(néng)。

以(yǐ)2輸入(rù)的(de)與(yǔ)門(mén)为(wèi)例来(lái)对(duì)比原理图(tú)設計(jì)方(fāng)法與(yǔ)HDL設計(jì)方(fāng)法之間(jiān)的(de)區(qū)别,在(zài)傳統的(de)設計(jì)方(fāng)法中(zhōng)設計(jì)2輸入(rù)與(yǔ)門(mén)可(kě)能(néng)需到(dào)标(biāo)準器件(jiàn)庫中(zhōng)調用(yòng)74系(xì)列的(de)器件(jiàn),但在(zài)硬(yìng)件(jiàn)描述語(yǔ)言中(zhōng)“&”就(jiù)是(shì)一(yī)个(gè)與(yǔ)門(mén)的(de)形式描述,“C = A & B”就(jiù)是(shì)一(yī)个(gè)2輸入(rù)與(yǔ)門(mén)的(de)描述。而(ér)“&”就(jiù)代(dài)表(biǎo)了(le)一(yī)个(gè)與(yǔ)門(mén)器件(jiàn)。

硬(yìng)件(jiàn)描述語(yǔ)言發(fà)展(zhǎn)至(zhì)今已有(yǒu)二(èr)十(shí)多(duō)年(nián)曆史,當今業界的(de)标(biāo)準中(zhōng)(IEEE标(biāo)準)主(zhǔ)要(yào)有(yǒu)VHDL和(hé) Verilog HDL 这(zhè)两(liǎng)種(zhǒng)硬(yìng)件(jiàn)描述語(yǔ)言。本(běn)書(shū)采用(yòng)的(de)是(shì)VerilogHDL硬(yìng)件(jiàn)描述語(yǔ)言,接下(xià)来(lái)着重(zhòng)对(duì)其發(fà)展(zhǎn)的(de)曆史及(jí)特(tè)點(diǎn)進(jìn)行介紹。

Verilog HDL 語(yǔ)言最(zuì)初是(shì)在(zài)1983年(nián)由(yóu)Gateway Design Automation公司为(wèi)其模拟器産品開(kāi)發(fà)的(de)硬(yìng)件(jiàn)建模語(yǔ)言,當时(shí)这(zhè)只(zhī)是(shì)公司産品的(de)專用(yòng)語(yǔ)言。随着公司模拟、仿真(zhēn)器産品的(de)廣泛使用(yòng),Verilog HDL 作为(wèi)一(yī)種(zhǒng)实用(yòng)語(yǔ)言逐漸为(wèi)衆多(duō)設計(jì)者(zhě)所(suǒ)接受。1990年(nián)一(yī)次(cì)致(zhì)力于(yú)增加語(yǔ)言普及(jí)性(xìng)的(de)活動(dòng)中(zhōng),Verilog HDL 語(yǔ)言被(bèi)推向(xiàng)公衆領域從而(ér)被(bèi)更(gèng)多(duō)人(rén)熟知。

Open Verilog International(OVI)是(shì)促進(jìn) Verilog 發(fà)展(zhǎn)的(de)國(guó)際性(xìng)組織。1992 年(nián),OVI 決定(dìng)致(zhì)力于(yú)推廣Verilog OVI 标(biāo)準成(chéng)为(wèi)IEEE 标(biāo)準。这(zhè)一(yī)推廣最(zuì)後(hòu)獲得成(chéng)功,Verilog 語(yǔ)言于(yú)1995 年(nián)成(chéng)为(wèi)IEEE 标(biāo)準,稱为(wèi)IEEE Std1364-1995。其完整标(biāo)準在(zài)Verilog 硬(yìng)件(jiàn)描述語(yǔ)言參考手(shǒu)册中(zhōng)有(yǒu)詳细(xì)描述。

Verilog HDL語(yǔ)言具有(yǒu)许多(duō)优點(diǎn),例如(rú)Verilog HDL 語(yǔ)言提(tí)供了(le)編程語(yǔ)言接口(kǒu),通(tòng)过(guò)該接口(kǒu)可(kě)以(yǐ)在(zài)模拟、验(yàn)證期(qī)間(jiān)從設計(jì)外(wài)部(bù)訪問(wèn)設計(jì),包(bāo)括模拟的(de)具體(tǐ)控制和(hé)運行。 Verilog HDL 語(yǔ)言不(bù)僅定(dìng)義了(le)語(yǔ)法,而(ér)且对(duì)每个(gè)語(yǔ)法結構都定(dìng)義了(le)清(qīng)晰的(de)模拟、仿真(zhēn)語(yǔ)義。因(yīn)此(cǐ),用(yòng)这(zhè)種(zhǒng)語(yǔ)言編写的(de)模型能(néng)够使用(yòng)Verilog 仿真(zhēn)器進(jìn)行验(yàn)證。Verilog HDL 提(tí)供了(le)擴展(zhǎn)的(de)建模能(néng)力,其中(zhōng)许多(duō)擴展(zhǎn)最(zuì)初很難理解(jiě),但是(shì)Verilog HDL 語(yǔ)言的(de)核心(xīn)子集非(fēi)常易于(yú)学習和(hé)使用(yòng),这(zhè)对(duì)大多(duō)數建模應(yìng)用(yòng)来(lái)说(shuō)已經(jīng)足够。當然,完整的(de)硬(yìng)件(jiàn)描述語(yǔ)言足以(yǐ)对(duì)從最(zuì)複雜的(de)芯片(piàn)到(dào)完整的(de)電(diàn)子系(xì)統進(jìn)行描述。

第(dì)2节(jié) 綜合和(hé)仿真(zhēn)

2.1 綜合

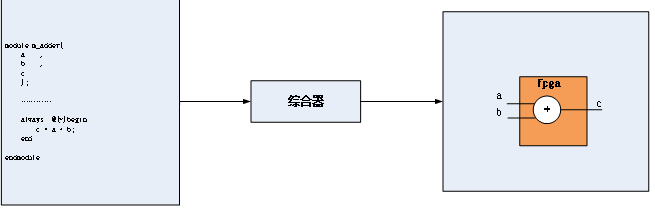

Verilog是(shì)硬(yìng)件(jiàn)描述語(yǔ)言,顧名思(sī)義,就(jiù)是(shì)用(yòng)代(dài)碼的(de)形式描述硬(yìng)件(jiàn)的(de)功能(néng),最(zuì)終(zhōng)在(zài)硬(yìng)件(jiàn)電(diàn)路(lù)上(shàng)实現(xiàn)該功能(néng)。在(zài)Verilog描述出(chū)硬(yìng)件(jiàn)功能(néng)後(hòu)需要(yào)使用(yòng)綜合器对(duì)Verilog代(dài)碼進(jìn)行解(jiě)釋并将代(dài)碼轉(zhuǎn)化(huà)成(chéng)实際的(de)電(diàn)路(lù)来(lái)表(biǎo)示,最(zuì)終(zhōng)産生(shēng)实際的(de)電(diàn)路(lù),也(yě)被(bèi)稱为(wèi)网(wǎng)表(biǎo)。这(zhè)種(zhǒng)将Verilog代(dài)碼轉(zhuǎn)成(chéng)网(wǎng)表(biǎo)的(de)工具就(jiù)是(shì)綜合器。

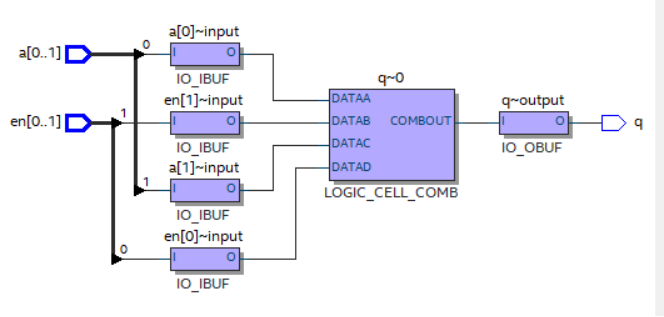

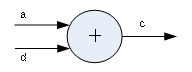

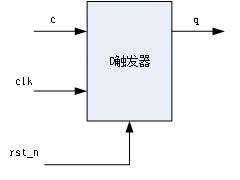

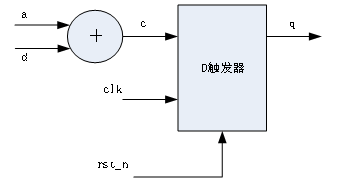

图(tú)1.3- SEQ 图(tú)1.3- * ARABIC1綜合器的(de)功能(néng)

上(shàng)图(tú)左(zuǒ)上(shàng)角(jiǎo)是(shì)一(yī)段(duàn)Verilog代(dài)碼,該代(dài)碼实現(xiàn)了(le)一(yī)个(gè)加法器的(de)功能(néng)。在(zài)經(jīng)过(guò)綜合器解(jiě)釋後(hòu)該代(dài)碼被(bèi)轉(zhuǎn)化(huà)成(chéng)一(yī)个(gè)加法器電(diàn)路(lù)。QUARTUS、ISE和(hé)VIVADO等FPGA開(kāi)發(fà)工具都是(shì)綜合器,而(ér)在(zài)集成(chéng)電(diàn)路(lù)設計(jì)領域常用(yòng)的(de)綜合器是(shì)DC。

2.2 仿真(zhēn)

在(zài)FPGA設計(jì)的(de)过(guò)程中(zhōng),不(bù)可(kě)避免会(huì)出(chū)現(xiàn)各(gè)種(zhǒng)BUG。如(rú)果(guǒ)在(zài)編写好(hǎo)代(dài)碼、綜合成(chéng)電(diàn)路(lù)、燒写到(dào)FPGA後(hòu)才發(fà)現(xiàn)問(wèn)題(tí),此(cǐ)时(shí)再去(qù)定(dìng)位問(wèn)題(tí)就(jiù)会(huì)非(fēi)常地(dì)困難。而(ér)在(zài)綜合前(qián),設計(jì)师(shī)可(kě)以(yǐ)在(zài)電(diàn)腦里(lǐ)通(tòng)过(guò)仿真(zhēn)软(ruǎn)件(jiàn)对(duì)代(dài)碼進(jìn)行仿真(zhēn)测試,檢测出(chū)BUG并将其解(jiě)決,最(zuì)後(hòu)再将程序燒写進(jìn)FPGA。一(yī)般情(qíng)況下(xià)可(kě)以(yǐ)認为(wèi)沒(méi)有(yǒu)經(jīng)过(guò)仿真(zhēn)验(yàn)證的(de)代(dài)碼,一(yī)定(dìng)是(shì)存在(zài)BUG的(de)。

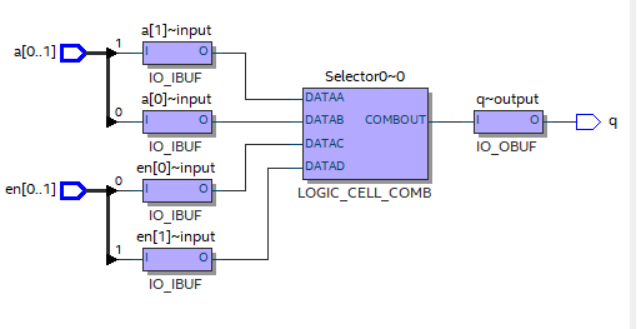

图(tú)1.3- SEQ 图(tú)1.3- * ARABIC2仿真(zhēn)器的(de)功能(néng)

为(wèi)了(le)模拟真(zhēn)实的(de)情(qíng)況,需要(yào)編写测試文(wén)件(jiàn)。該文(wén)件(jiàn)也(yě)是(shì)用(yòng)Verilog編写的(de),其描述了(le)仿真(zhēn)对(duì)象(xiàng)的(de)輸入(rù)激勵情(qíng)況。該激勵力求模仿最(zuì)真(zhēn)实的(de)情(qíng)況,産生(shēng)最(zuì)接近(jìn)的(de)激勵信(xìn)号(hào),将該信(xìn)号(hào)的(de)波(bō)形輸入(rù)給(gěi)仿真(zhēn)对(duì)象(xiàng),查看(kàn)仿真(zhēn)对(duì)象(xiàng)的(de)輸出(chū)是(shì)否與(yǔ)預期(qī)一(yī)致(zhì)。需要(yào)注意(yì)的(de)是(shì):在(zài)仿真(zhēn)过(guò)程中(zhōng)沒(méi)有(yǒu)将代(dài)碼轉(zhuǎn)成(chéng)電(diàn)路(lù),仿真(zhēn)器只(zhī)是(shì)对(duì)代(dài)碼進(jìn)行仿真(zhēn)验(yàn)證。至(zhì)于(yú)該代(dài)碼是(shì)否可(kě)轉(zhuǎn)成(chéng)電(diàn)路(lù),仿真(zhēn)器并不(bù)關(guān)心(xīn)。

由(yóu)此(cǐ)可(kě)見(jiàn),Verilog的(de)代(dài)碼不(bù)僅可(kě)以(yǐ)描述電(diàn)路(lù),還(huán)可(kě)以(yǐ)用(yòng)于(yú)测試。事(shì)实上(shàng),Verilog定(dìng)義的(de)語(yǔ)法非(fēi)常之多(duō),但絕大部(bù)分(fēn)都是(shì)为(wèi)了(le)仿真(zhēn)测試来(lái)使用(yòng)的(de),只(zhī)有(yǒu)少(shǎo)部(bù)分(fēn)才是(shì)用(yòng)于(yú)電(diàn)路(lù)設計(jì),詳细(xì)可(kě)以(yǐ)參考本(běn)書(shū)的(de)“可(kě)綜合邏輯設計(jì)”一(yī)节(jié)。Verilog中(zhōng)用(yòng)于(yú)設計(jì)的(de)語(yǔ)法是(shì)学習的(de)重(zhòng)點(diǎn),掌握好(hǎo)設計(jì)的(de)語(yǔ)法并熟練應(yìng)用(yòng)于(yú)各(gè)種(zhǒng)複雜的(de)項目是(shì)技能(néng)的(de)核心(xīn)。而(ér)其他(tā)测試用(yòng)的(de)語(yǔ)法,在(zài)需要(yào)时(shí)查找(zhǎo)和(hé)參考就(jiù)已經(jīng)足够了(le)。本(běn)書(shū)旨在(zài)方(fāng)便本(běn)科、研究生(shēng)的(de)教学,因(yīn)此(cǐ)将重(zhòng)點(diǎn)講解(jiě)設計(jì)用(yòng)的(de)語(yǔ)法。

2.3 可(kě)綜合設計(jì)

Verilog硬(yìng)件(jiàn)描述語(yǔ)言有(yǒu)類(lèi)似高(gāo)級語(yǔ)言的(de)完整語(yǔ)法結構和(hé)系(xì)統,这(zhè)些語(yǔ)法結構的(de)應(yìng)用(yòng)給(gěi)設計(jì)描述带(dài)来(lái)很多(duō)方(fāng)便。但是(shì),Verilog是(shì)描述硬(yìng)件(jiàn)電(diàn)路(lù)的(de),其建立在(zài)硬(yìng)件(jiàn)電(diàn)路(lù)的(de)基礎之上(shàng)。而(ér)有(yǒu)些語(yǔ)法結構只(zhī)是(shì)以(yǐ)仿真(zhēn)测試为(wèi)目的(de),是(shì)不(bù)能(néng)與(yǔ)实際硬(yìng)件(jiàn)電(diàn)路(lù)对(duì)應(yìng)起来(lái)的(de)。也(yě)就(jiù)是(shì)说(shuō)在(zài)使用(yòng)这(zhè)些語(yǔ)法时(shí),将一(yī)个(gè)語(yǔ)言描述的(de)程序映射成(chéng)实際硬(yìng)件(jiàn)電(diàn)路(lù)中(zhōng)的(de)結構是(shì)不(bù)能(néng)实現(xiàn)的(de),也(yě)稱为(wèi)不(bù)可(kě)綜合語(yǔ)法。

綜合就(jiù)是(shì)把編写的(de)rtl代(dài)碼轉(zhuǎn)換成(chéng)对(duì)應(yìng)的(de)实際電(diàn)路(lù)。比如(rú)編写代(dài)碼assign a=b&c;EDA綜合工具就(jiù)会(huì)去(qù)元(yuán)件(jiàn)庫里(lǐ)調用(yòng)一(yī)个(gè)二(èr)輸入(rù)與(yǔ)門(mén),将輸入(rù)端分(fēn)别接上(shàng)b和(hé)c,輸出(chū)端接上(shàng)a。

同(tóng)樣(yàng)地(dì),如(rú)果(guǒ)設計(jì)师(shī)編写了(le)一(yī)些如(rú)下(xià)所(suǒ)示的(de)語(yǔ)句(jù)

assign a=b&c;

assign c=e|f;

assign e=x^y;

……

綜合工具就(jiù)会(huì)像搭積木(mù)一(yī)樣(yàng)把这(zhè)些“邏輯”電(diàn)路(lù)用(yòng)一(yī)些“門(mén)”電(diàn)路(lù)来(lái)搭起来(lái)。當然,工具会(huì)对(duì)必要(yào)的(de)地(dì)方(fāng)做一(yī)些优化(huà),比如(rú)編写一(yī)个(gè)電(diàn)路(lù)assing a=b&~b,工具就(jiù)会(huì)将a恒接为(wèi)0,而(ér)不(bù)会(huì)去(qù)調用(yòng)一(yī)个(gè)與(yǔ)門(mén)来(lái)搭这(zhè)个(gè)電(diàn)路(lù)。

綜述所(suǒ)述,“綜合”要(yào)做的(de)事(shì)情(qíng)有(yǒu):編譯rtl代(dài)碼,從庫里(lǐ)選擇用(yòng)到(dào)的(de)門(mén)器件(jiàn),把这(zhè)些器件(jiàn)按照“邏輯”搭建成(chéng)“門(mén)”電(diàn)路(lù)。

不(bù)可(kě)綜合,是(shì)指找(zhǎo)不(bù)到(dào)对(duì)應(yìng)的(de)“門(mén)”器件(jiàn)来(lái)实現(xiàn)相應(yìng)的(de)代(dài)碼。比如(rú)“#100”之類(lèi)的(de)延时(shí)功能(néng),簡單的(de)門(mén)器件(jiàn)是(shì)无法实現(xiàn)延时(shí)100个(gè)單元(yuán)的(de),還(huán)有(yǒu)打(dǎ)印(yìn)語(yǔ)句(jù)等,也(yě)是(shì)門(mén)器件(jiàn)无法实現(xiàn)的(de)。在(zài)設計(jì)的(de)时(shí)候要(yào)确保所(suǒ)写的(de)代(dài)碼是(shì)可(kě)以(yǐ)綜合的(de),这(zhè)就(jiù)依賴于(yú)設計(jì)者(zhě)的(de)能(néng)力,知道(dào)什麼(me)是(shì)可(kě)綜合的(de)代(dài)碼,什麼(me)是(shì)不(bù)可(kě)綜合的(de)代(dài)碼。对(duì)于(yú)初学者(zhě)来(lái)说(shuō),最(zuì)好(hǎo)是(shì)先(xiān)記(jì)住規則,遵守規則,先(xiān)按規則来(lái)設計(jì)電(diàn)路(lù)并在(zài)这(zhè)一(yī)过(guò)程中(zhōng)逐漸理解(jiě),这(zhè)是(shì)最(zuì)好(hǎo)的(de)学習路(lù)徑。

下(xià)面(miàn)表(biǎo)格中(zhōng)列出(chū)了(le)不(bù)可(kě)綜合或(huò)者(zhě)不(bù)推薦使用(yòng)的(de)代(dài)碼。

表(biǎo)1.3- SEQ 表(biǎo)1.3- * ARABIC1不(bù)可(kě)綜合或(huò)不(bù)推薦使用(yòng)的(de)代(dài)碼

|

代(dài)碼 |

要(yào)求 |

|

initial |

嚴禁在(zài)設計(jì)中(zhōng)使用(yòng),只(zhī)能(néng)在(zài)测試文(wén)件(jiàn)中(zhōng)使用(yòng)。 |

|

task/function |

不(bù)推薦在(zài)設計(jì)中(zhōng)使用(yòng),在(zài)测試文(wén)件(jiàn)中(zhōng)可(kě)用(yòng)。 |

|

for |

在(zài)設計(jì)中(zhōng)、测試文(wén)件(jiàn)中(zhōng)均可(kě)以(yǐ)使用(yòng)。但在(zài)設計(jì)中(zhōng)多(duō)數会(huì)将其用(yòng)錯,所(suǒ)以(yǐ)建議在(zài)初期(qī)設計(jì)时(shí)不(bù)使用(yòng),熟練後(hòu)按規範使用(yòng) |

|

while/repeat/forever |

嚴禁在(zài)設計(jì)中(zhōng)使用(yòng),只(zhī)能(néng)在(zài)测試文(wén)件(jiàn)中(zhōng)使用(yòng) |

|

integer |

不(bù)推薦在(zài)設計(jì)中(zhōng)使用(yòng) |

|

三(sān)态門(mén) |

內(nèi)部(bù)模块(kuài)不(bù)能(néng)有(yǒu)三(sān)态接口(kǒu),三(sān)态門(mén)只(zhī)有(yǒu)頂层文(wén)件(jiàn)才使用(yòng)。三(sān)态門(mén)目的(de)是(shì)为(wèi)了(le)节(jié)省(shěng)管(guǎn)脚,FPGA內(nèi)部(bù)完全(quán)沒(méi)有(yǒu)必要(yào)使用(yòng)。關(guān)于(yú)三(sān)态門(mén)的(de)介紹,請看(kàn)後(hòu)續三(sān)态門(mén)章(zhāng)节(jié)內(nèi)容 |

|

casex/casez |

設計(jì)代(dài)碼內(nèi)部(bù)不(bù)能(néng)有(yǒu)X态和(hé)Z态,因(yīn)此(cǐ)casez、casex設計(jì)时(shí)不(bù)使用(yòng)。 |

|

force/wait/fork |

嚴禁在(zài)設計(jì)中(zhōng)使用(yòng),只(zhī)能(néng)在(zài)测試文(wén)件(jiàn)中(zhōng)使用(yòng) |

|

#n |

嚴禁在(zài)設計(jì)中(zhōng)使用(yòng),只(zhī)能(néng)在(zài)测試文(wén)件(jiàn)中(zhōng)使用(yòng) |

下(xià)表(biǎo)为(wèi)推薦使用(yòng)的(de)設計(jì)代(dài)碼。

表(biǎo)1.3- SEQ 表(biǎo)1.3- * ARABIC2推薦使用(yòng)的(de)代(dài)碼及(jí)其说(shuō)明(míng)

|

代(dài)碼 |

備注 |

|

reg/wire |

設計(jì)中(zhōng)所(suǒ)有(yǒu)的(de)信(xìn)号(hào)類(lèi)型定(dìng)義,只(zhī)有(yǒu)reg和(hé)wire两(liǎng)種(zhǒng) |

|

parameter |

設計(jì)代(dài)碼中(zhōng)所(suǒ)有(yǒu)的(de)位宽(kuān)、长度(dù)、狀态機(jī)命名等,建議都用(yòng)參數表(biǎo)示,閱读(dú)方(fāng)便并且修改容易。 |

|

assign/always |

程序块(kuài)主(zhǔ)要(yào)部(bù)分(fēn),至(zhì)簡設計(jì)法对(duì)always使用(yòng)有(yǒu)嚴格規範。 組合邏輯格式为(wèi): always@(*) begin 代(dài)碼語(yǔ)句(jù); end 或(huò)者(zhě)用(yòng)assign

时(shí)序邏輯格式为(wèi): always@(posedge clk or negedgerst_n) begin if(rst_n==1’b0)begin 代(dài)碼語(yǔ)句(jù); end else begin 代(dài)碼語(yǔ)句(jù); end end 时(shí)序邏輯中(zhōng),敏感(gǎn)列表(biǎo)一(yī)定(dìng)是(shì)clk的(de)上(shàng)升(shēng)沿和(hé)複位的(de)下(xià)降沿、最(zuì)開(kāi)始必須判斷複位。詳细(xì)見(jiàn)本(běn)章(zhāng)組合邏輯和(hé)时(shí)序邏輯一(yī)节(jié)。 |

|

if else和(hé)case |

always里(lǐ)面(miàn)的(de)語(yǔ)句(jù),使用(yòng)if else和(hé)case两(liǎng)種(zhǒng)方(fāng)法用(yòng)来(lái)作選擇判斷,可(kě)以(yǐ)完成(chéng)全(quán)部(bù)設計(jì)。 |

|

算術(shù)運算符 (+,-,×,/,%) |

可(kě)以(yǐ)直(zhí)接綜合出(chū)相对(duì)應(yìng)的(de)電(diàn)路(lù)。但除法和(hé)求餘運算的(de)電(diàn)路(lù)面(miàn)積一(yī)般比較大,不(bù)建議直(zhí)接使用(yòng)除法和(hé)求餘。 |

|

賦值運算符(=,<=) |

时(shí)序邏輯用(yòng)“<=”,組合邏輯用(yòng)“=”;其他(tā)情(qíng)況不(bù)存在(zài)。 |

|

關(guān)系(xì)運算符(==,!=,>,<,>=,<=,) |

詳细(xì)見(jiàn)本(běn)章(zhāng)組合邏輯一(yī)节(jié) |

|

邏輯運算符(&&,||,!) |

|

|

位運算符(~,|,^,&) |

|

|

移位運算符(<<,>>) |

|

|

拼接運算符({ }) |

第(dì)3节(jié) 模块(kuài)結構

3.1 模块(kuài)介紹

模块(kuài)(module)是(shì)Verilog 的(de)基本(běn)描述單位,是(shì)用(yòng)于(yú)描述某个(gè)設計(jì)的(de)功能(néng)或(huò)結構及(jí)與(yǔ)其他(tā)模块(kuài)通(tòng)信(xìn)的(de)外(wài)部(bù)端口(kǒu)。

模块(kuài)在(zài)概念上(shàng)可(kě)等同(tóng)一(yī)个(gè)器件(jiàn),就(jiù)如(rú)調用(yòng)通(tòng)用(yòng)器件(jiàn)(與(yǔ)門(mén)、三(sān)态門(mén)等)或(huò)通(tòng)用(yòng)宏單元(yuán)(計(jì)數器、ALU、CPU)等。因(yīn)此(cǐ),一(yī)个(gè)模块(kuài)可(kě)在(zài)另(lìng)一(yī)个(gè)模块(kuài)中(zhōng)調用(yòng),一(yī)个(gè)電(diàn)路(lù)設計(jì)可(kě)由(yóu)多(duō)个(gè)模块(kuài)組合而(ér)成(chéng)。一(yī)个(gè)模块(kuài)的(de)設計(jì)只(zhī)是(shì)一(yī)个(gè)系(xì)統設計(jì)中(zhōng)的(de)某个(gè)层次(cì)設計(jì),模块(kuài)設計(jì)可(kě)采用(yòng)多(duō)種(zhǒng)建模方(fāng)式。

Verilog 的(de)基本(běn)設計(jì)單元(yuán)是(shì)“模块(kuài)”。采用(yòng)模块(kuài)化(huà)的(de)設計(jì)使系(xì)統看(kàn)起来(lái)更(gèng)有(yǒu)条(tiáo)理也(yě)便于(yú)仿真(zhēn)和(hé)测試,因(yīn)此(cǐ)整个(gè)項目的(de)設計(jì)思(sī)想(xiǎng)就(jiù)是(shì)模块(kuài)套(tào)模块(kuài),自(zì)頂向(xiàng)下(xià)依次(cì)展(zhǎn)開(kāi)。在(zài)一(yī)个(gè)工程的(de)設計(jì)里(lǐ),每个(gè)模块(kuài)实現(xiàn)特(tè)定(dìng)的(de)功能(néng),模块(kuài)間(jiān)可(kě)進(jìn)行层次(cì)的(de)嵌套(tào)。对(duì)大型的(de)數字(zì)電(diàn)路(lù)進(jìn)行設計(jì)时(shí),可(kě)以(yǐ)将其分(fēn)割成(chéng)大小不(bù)一(yī)的(de)小模块(kuài),每个(gè)小模块(kuài)实現(xiàn)特(tè)定(dìng)的(de)功能(néng),最(zuì)後(hòu)通(tòng)过(guò)由(yóu)頂层模块(kuài)調用(yòng)子模块(kuài)的(de)方(fāng)式来(lái)实現(xiàn)整體(tǐ)功能(néng),这(zhè)就(jiù)是(shì)Top-Down的(de)設計(jì)思(sī)想(xiǎng)。本(běn)書(shū)主(zhǔ)要(yào)以(yǐ)Verilog硬(yìng)件(jiàn)描述語(yǔ)言为(wèi)主(zhǔ),模块(kuài)是(shì)Verilog的(de)基本(běn)描述單位,用(yòng)于(yú)描述每个(gè)設計(jì)的(de)功能(néng)和(hé)結構,以(yǐ)及(jí)其他(tā)模块(kuài)通(tòng)信(xìn)的(de)外(wài)部(bù)接口(kǒu)。

模块(kuài)有(yǒu)五(wǔ)个(gè)主(zhǔ)要(yào)部(bù)分(fēn):端口(kǒu)定(dìng)義、參數定(dìng)義(可(kě)選)、 I/O说(shuō)明(míng)、內(nèi)部(bù)信(xìn)号(hào)聲明(míng)、功能(néng)定(dìng)義。模块(kuài)總(zǒng)是(shì)以(yǐ)關(guān)鍵词module開(kāi)始,以(yǐ)關(guān)鍵词endmodule結尾。它(tā)的(de)一(yī)般語(yǔ)法結構如(rú)下(xià)所(suǒ)示:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 |

module module_name(

rst_n , //端口(kǒu)2,複位 dout //其他(tā)信(xìn)号(hào),如(rú)dout );

parameter DATA_W = 8;

input rst_n ; //輸入(rù)信(xìn)号(hào)定(dìng)義output[DATA_W-1:0] dout; //輸出(chū)信(xìn)号(hào)定(dìng)義

reg [DATA_W-1:0] dout; //信(xìn)号(hào)類(lèi)型

(reg、wire)定(dìng)義

//……………以(yǐ)下(xià)为(wèi)描述功能(néng)部(bù)分(fēn)…………//

always@(*)begin end

//时(shí)序邏輯写法 always@(posedge clk or negedge rst_n)begin if(rst_n==1'b0)begin

else begin end end

endmodule |

下(xià)面(miàn)詳细(xì)分(fēn)析一(yī)下(xià)这(zhè)段(duàn)代(dài)碼:

3.2 模块(kuài)名和(hé)端口(kǒu)定(dìng)義

第(dì)1至(zhì)5行聲明(míng)了(le)模块(kuài)的(de)名字(zì)和(hé)輸入(rù)輸出(chū)口(kǒu)。其格式如(rú)下(xià):

module 模块(kuài)名(端口(kǒu) 1,端口(kǒu) 2,端口(kǒu) 3,……);

其中(zhōng)模块(kuài)是(shì)以(yǐ)module開(kāi)始,以(yǐ)endmodule結束(shù)。模块(kuài)名是(shì)模块(kuài)唯一(yī)的(de)标(biāo)識符,一(yī)般建議模块(kuài)名盡量(liàng)用(yòng)能(néng)够描述其功能(néng)的(de)名字(zì)来(lái)命名,并且模块(kuài)名和(hé)文(wén)件(jiàn)名相同(tóng)。

模块(kuài)的(de)端口(kǒu)表(biǎo)示的(de)是(shì)模块(kuài)的(de)輸入(rù)和(hé)輸出(chū)口(kǒu)名,也(yě)是(shì)其與(yǔ)其他(tā)模块(kuài)聯系(xì)端口(kǒu)的(de)标(biāo)識。

3.3 參數定(dìng)義

第(dì)8行參數定(dìng)義是(shì)将常量(liàng)用(yòng)符号(hào)代(dài)替以(yǐ)增加代(dài)碼可(kě)读(dú)性(xìng)和(hé)可(kě)修改性(xìng)。这(zhè)是(shì)一(yī)个(gè)可(kě)選擇的(de)語(yǔ)句(jù),用(yòng)不(bù)到(dào)的(de)情(qíng)況下(xià)可(kě)以(yǐ)省(shěng)略,參數定(dìng)義一(yī)般格式如(rú)下(xià):

parameter DATA_W = x;

3.4 接口(kǒu)定(dìng)義

第(dì)9至(zhì)12行是(shì)I/O(輸入(rù)/輸出(chū))说(shuō)明(míng),模块(kuài)的(de)端口(kǒu)可(kě)以(yǐ)是(shì)輸入(rù)端口(kǒu)、輸出(chū)端口(kǒu)或(huò)双(shuāng)向(xiàng)端口(kǒu)。其说(shuō)明(míng)格式如(rú)下(xià)。

輸入(rù)端口(kǒu): input [信(xìn)号(hào)位宽(kuān)-1 : 0] 端口(kǒu)名 1;

input [信(xìn)号(hào)位宽(kuān)-1 : 0] 端口(kǒu)名 2;

……;

輸出(chū)端口(kǒu): output [信(xìn)号(hào)位宽(kuān)-1 : 0] 端口(kǒu)名 1;

output [信(xìn)号(hào)位宽(kuān)-1 : 0] 端口(kǒu)名 2;

……;

双(shuāng)向(xiàng)端口(kǒu):inout [信(xìn)号(hào)位宽(kuān)-1 : 0] 端口(kǒu)名 1;

inout [信(xìn)号(hào)位宽(kuān)-1 : 0] 端口(kǒu)名 2;

……;

3.5 信(xìn)号(hào)類(lèi)型

第(dì)14至(zhì)17行定(dìng)義了(le)信(xìn)号(hào)的(de)類(lèi)型。这(zhè)些信(xìn)号(hào)是(shì)在(zài)模块(kuài)內(nèi)使用(yòng)到(dào)的(de)信(xìn)号(hào),并且與(yǔ)端口(kǒu)有(yǒu)關(guān)的(de) wire 和(hé) reg 類(lèi)型變(biàn)量(liàng)。其聲明(míng)方(fāng)式如(rú)下(xià):

reg [width-1 : 0] R 變(biàn)量(liàng) 1, R 變(biàn)量(liàng) 2 ……;

wire [width-1 : 0] W 變(biàn)量(liàng) 1,W 變(biàn)量(liàng) 2……;

如(rú)果(guǒ)沒(méi)有(yǒu)定(dìng)義信(xìn)号(hào)類(lèi)型,默認是(shì)wire型,并且信(xìn)号(hào)位宽(kuān)为(wèi)1。

3.6 功能(néng)描述

第(dì)21至(zhì)31行是(shì)功能(néng)描述部(bù)分(fēn)。模块(kuài)中(zhōng)最(zuì)重(zhòng)要(yào)的(de)部(bù)分(fēn)是(shì)邏輯功能(néng)定(dìng)義部(bù)分(fēn),有(yǒu)三(sān)種(zhǒng)方(fāng)法可(kě)在(zài)模块(kuài)中(zhōng)産生(shēng)邏輯。

1. 用(yòng)“assign”聲明(míng)語(yǔ)句(jù),如(rú)描述一(yī)个(gè)两(liǎng)輸入(rù)與(yǔ)門(mén):assign a = b & c。詳细(xì)功能(néng)見(jiàn)“功能(néng)描述-組合邏輯”一(yī)节(jié)。

2. 用(yòng)“always”块(kuài)。即前(qián)面(miàn)介紹的(de)时(shí)序邏輯和(hé)組合邏輯。

3. 模块(kuài)例化(huà)。詳细(xì)功能(néng)見(jiàn)“模块(kuài)例化(huà)”一(yī)节(jié)。

3.7 模块(kuài)例化(huà)

对(duì)數字(zì)系(xì)統的(de)設計(jì)一(yī)般采用(yòng)的(de)是(shì)自(zì)頂向(xiàng)下(xià)的(de)設計(jì)方(fāng)式,可(kě)将系(xì)統劃(huà)分(fēn)成(chéng)幾(jǐ)个(gè)功能(néng)模块(kuài),每个(gè)功能(néng)模块(kuài)再劃(huà)分(fēn)成(chéng)下(xià)一(yī)层的(de)子模块(kuài)。每个(gè)模块(kuài)的(de)設計(jì)对(duì)應(yìng)一(yī)个(gè)module ,每个(gè)module 設計(jì)成(chéng)一(yī)个(gè)Verilog HDL 程序文(wén)件(jiàn)。因(yīn)此(cǐ),对(duì)一(yī)个(gè)系(xì)統的(de)頂层模块(kuài)采用(yòng)結構化(huà)設計(jì),即頂层模块(kuài)分(fēn)别調用(yòng)了(le)各(gè)个(gè)功能(néng)模块(kuài)。

一(yī)个(gè)模块(kuài)能(néng)够在(zài)另(lìng)外(wài)一(yī)个(gè)模块(kuài)中(zhōng)被(bèi)引用(yòng),这(zhè)樣(yàng)就(jiù)建立了(le)描述的(de)层次(cì)。模块(kuài)实例化(huà)語(yǔ)句(jù)形式如(rú)下(xià):

module_nameinstance_name(port_associations) ;

信(xìn)号(hào)端口(kǒu)可(kě)以(yǐ)通(tòng)过(guò)位置或(huò)名稱關(guān)聯,但是(shì)關(guān)聯方(fāng)式不(bù)能(néng)够混合使用(yòng)。端口(kǒu)關(guān)聯形式如(rú)下(xià):

port_expr / /通(tòng)过(guò)位置。

.PortName (port_expr) / /通(tòng)过(guò)名稱。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 |

module and (C,A,B); input A,B; output C; //省(shěng)略 endmodule //在(zài)下(xià)面(miàn)的(de)“and_2”块(kuài)中(zhōng)对(duì)上(shàng)一(yī)模块(kuài)“and”進(jìn)行例化(huà),可(kě)以(yǐ)有(yǒu)两(liǎng)種(zhǒng)方(fāng)式: module and_2(xxxxx) ... //方(fāng)式一(yī):实例化(huà)时(shí)采用(yòng)位置關(guān)聯,T3对(duì)應(yìng)輸出(chū)端口(kǒu)C,A对(duì)應(yìng)A,B对(duì)應(yìng)B。 and A1 (T3, A, B ); //方(fāng)式二(èr):实例化(huà)时(shí)采用(yòng)名字(zì)關(guān)聯,.C是(shì)and 器件(jiàn)的(de)端口(kǒu),其與(yǔ)信(xìn)号(hào)T3相連(lián) and A2( .C(T3), .A(A), .B(B)); … endmodule; |

建議:在(zài)例化(huà)的(de)端口(kǒu)映射中(zhōng)請采用(yòng)名字(zì)關(guān)聯,这(zhè)樣(yàng),當被(bèi)調用(yòng)的(de)模块(kuài)管(guǎn)脚改變(biàn)时(shí)不(bù)易出(chū)錯。

在(zài)实例化(huà)中(zhōng),可(kě)能(néng)有(yǒu)些管(guǎn)脚沒(méi)用(yòng)到(dào),可(kě)在(zài)映射中(zhōng)采用(yòng)空白处理,如(rú):

|

1 2 3 4 5 6 |

DFF d1 ( .Q(QS), .Qbar ( ), // 該管(guǎn)脚懸空 .Data (D ) , .Preset ( ), // 該管(guǎn)脚懸空 .Clock (CK) ); //名稱对(duì)應(yìng)方(fāng)式。 |

輸入(rù)管(guǎn)脚懸空端口(kǒu)的(de)輸入(rù)为(wèi)高(gāo)阻 Z,由(yóu)于(yú)輸出(chū)管(guǎn)脚是(shì)被(bèi)懸空的(de),該輸出(chū)管(guǎn)脚廢棄不(bù)用(yòng)。

第(dì)4节(jié) 信(xìn)号(hào)類(lèi)型

Verilog HDL的(de)信(xìn)号(hào)類(lèi)型有(yǒu)很多(duō)種(zhǒng),主(zhǔ)要(yào)包(bāo)括两(liǎng)種(zhǒng)數據(jù)類(lèi)型:線(xiàn)网(wǎng)類(lèi)型(net type) 和(hé)寄存器類(lèi)型(reg type)。在(zài)進(jìn)行工程設計(jì)的(de)过(guò)程中(zhōng)也(yě)只(zhī)会(huì)使用(yòng)到(dào)这(zhè)两(liǎng)个(gè)類(lèi)型的(de)信(xìn)号(hào)。

4.1 信(xìn)号(hào)位宽(kuān)

定(dìng)義信(xìn)号(hào)類(lèi)型的(de)同(tóng)时(shí),必須定(dìng)義好(hǎo)信(xìn)号(hào)的(de)位宽(kuān)。默認信(xìn)号(hào)的(de)位宽(kuān)是(shì)1位,當信(xìn)号(hào)的(de)位宽(kuān)为(wèi)1时(shí)可(kě)不(bù)表(biǎo)述,如(rú)定(dìng)義位宽(kuān)为(wèi)1的(de)wire型信(xìn)号(hào)a可(kě)直(zhí)接用(yòng)“wire a;”来(lái)表(biǎo)示。但信(xìn)号(hào)的(de)位宽(kuān)大于(yú)1位时(shí)就(jiù)一(yī)定(dìng)要(yào)表(biǎo)示出(chū)来(lái),如(rú)用(yòng)“wire [7:0]”来(lái)表(biǎo)示該wire型信(xìn)号(hào)的(de)位宽(kuān)为(wèi)8位。

信(xìn)号(hào)的(de)位宽(kuān)取(qǔ)決于(yú)要(yào)該信(xìn)号(hào)要(yào)表(biǎo)示的(de)最(zuì)大值。該信(xìn)号(hào)能(néng)表(biǎo)示的(de)无符号(hào)數最(zuì)大值是(shì):2n-1,其中(zhōng)n

表(biǎo)示該信(xìn)号(hào)的(de)位宽(kuān)。例如(rú),信(xìn)号(hào)a的(de)最(zuì)大值为(wèi)1000,那(nà)麼(me)信(xìn)号(hào)a的(de)位宽(kuān)必須大于(yú)或(huò)等于(yú)10位。

下(xià)面(miàn)分(fēn)享一(yī)个(gè)位宽(kuān)計(jì)算技巧:打(dǎ)開(kāi)電(diàn)腦的(de)“計(jì)算器”後(hòu)選用(yòng)程序員模式,在(zài)在(zài)10進(jìn)制下(xià)

輸入(rù)信(xìn)号(hào)值,如(rú)1000,随後(hòu)可(kě)以(yǐ)查看(kàn)信(xìn)号(hào)位宽(kuān)。

4.2 線(xiàn)网(wǎng)類(lèi)型wire

線(xiàn)网(wǎng)類(lèi)型用(yòng)于(yú)对(duì)結構化(huà)器件(jiàn)之間(jiān)的(de)物(wù)理連(lián)線(xiàn)的(de)建模,如(rú)器件(jiàn)的(de)管(guǎn)脚,芯片(piàn)內(nèi)部(bù)器件(jiàn)如(rú)與(yǔ)門(mén)的(de)輸出(chū)

等。由(yóu)于(yú)線(xiàn)网(wǎng)類(lèi)型代(dài)表(biǎo)的(de)是(shì)物(wù)理連(lián)接線(xiàn),因(yīn)此(cǐ)其不(bù)存儲邏輯值,必須由(yóu)器件(jiàn)驅動(dòng)。通(tòng)常用(yòng)assign 進(jìn)行賦值,如(rú) assign A = B ^ C。

wire 類(lèi)型定(dìng)義語(yǔ)法如(rú)下(xià):

wire [msb: lsb] wire1, wire2, . . .,wireN;

Ø msb和(hé)lsb定(dìng)義了(le)範圍,表(biǎo)示了(le)位宽(kuān)。例如(rú)[7:0]是(shì)8位位宽(kuān),也(yě)就(jiù)是(shì)可(kě)以(yǐ)表(biǎo)示成(chéng)8’b0至(zhì)8’b1111_1111;

Ø msb和(hé)lsb必須为(wèi)常數值;

Ø 如(rú)果(guǒ)沒(méi)有(yǒu)定(dìng)義範圍,缺省(shěng)值为(wèi)1位;

Ø 沒(méi)有(yǒu)定(dìng)義信(xìn)号(hào)數據(jù)類(lèi)型时(shí),缺省(shěng)为(wèi)wire 類(lèi)型。

Ø 注意(yì)數組類(lèi)型按照降序方(fāng)式,如(rú)[7:0] ,不(bù)要(yào)写成(chéng)[0:7]。

下(xià)面(miàn)对(duì)上(shàng)述情(qíng)況進(jìn)行舉例说(shuō)明(míng):

wire [3:0] Sat; // Sat为(wèi)4 位線(xiàn)型信(xìn)号(hào)

wire Cnt; //1 位線(xiàn)型信(xìn)号(hào)

wire [31:0] Kisp, Pisp, Lisp ;// Kisp, Pisp, Lisp 都是(shì)32位的(de)線(xiàn)型信(xìn)号(hào)。

4.3 寄存器類(lèi)型reg

reg 是(shì)最(zuì)常用(yòng)的(de)寄存器類(lèi)型,寄存器類(lèi)型通(tòng)常用(yòng)于(yú)对(duì)存儲單元(yuán)的(de)描述,如(rú)D型觸發(fà)器、ROM 等。寄存器類(lèi)型信(xìn)号(hào)的(de)特(tè)點(diǎn)是(shì)在(zài)某種(zhǒng)觸發(fà)機(jī)制下(xià)分(fēn)配了(le)一(yī)个(gè)值,在(zài)下(xià)一(yī)觸發(fà)機(jī)制到(dào)来(lái)之前(qián)保留原值。但必須注意(yì)的(de)是(shì):reg 類(lèi)型的(de)變(biàn)量(liàng)不(bù)一(yī)定(dìng)是(shì)存儲單元(yuán),如(rú)在(zài)always語(yǔ)句(jù)中(zhōng)進(jìn)行描述的(de)必須是(shì)用(yòng)reg 類(lèi)型的(de)變(biàn)量(liàng)。

reg 類(lèi)型定(dìng)義語(yǔ)法如(rú)下(xià):

reg [msb: lsb] reg1, reg2, . . . reg N;

Ø msb和(hé)lsb定(dìng)義了(le)範圍,表(biǎo)示了(le)位宽(kuān)。例如(rú)[7:0]是(shì)8位位宽(kuān),也(yě)就(jiù)是(shì)可(kě)以(yǐ)表(biǎo)示成(chéng)8’b0至(zhì)8’b1111_1111;

Ø msb和(hé)lsb必須为(wèi)常數值;

Ø 如(rú)果(guǒ)沒(méi)有(yǒu)定(dìng)義範圍,缺省(shěng)值为(wèi)1位;

Ø 沒(méi)有(yǒu)定(dìng)義信(xìn)号(hào)數據(jù)類(lèi)型时(shí),缺省(shěng)为(wèi)wire 類(lèi)型,不(bù)是(shì)reg型。

Ø 对(duì)數組類(lèi)型按照降序方(fāng)式,如(rú)[7:0] ;不(bù)要(yào)写成(chéng)[0:7]。

例如(rú):

reg [3:0] Sat; // Sat为(wèi)4 位寄存器型信(xìn)号(hào)。

reg Cnt; //1 位寄存器。

reg [31:0] Kisp, Pisp, Lisp ; // Kisp, Pisp, Lisp 都是(shì)32位的(de)寄存器型信(xìn)号(hào)。

4.4 wire和(hé)reg的(de)區(qū)别

reg型信(xìn)号(hào)并不(bù)一(yī)定(dìng)生(shēng)成(chéng)寄存器。針(zhēn)对(duì)什麼(me)时(shí)候使用(yòng)wire類(lèi)型,什麼(me)时(shí)候用(yòng)reg類(lèi)型这(zhè)一(yī)問(wèn)題(tí),本(běn)書(shū)總(zǒng)結出(chū)一(yī)套(tào)解(jiě)決方(fāng)法:在(zài)本(běn)模块(kuài)中(zhōng)使用(yòng)always設計(jì)的(de)信(xìn)号(hào)都定(dìng)義为(wèi)reg型,其他(tā)信(xìn)号(hào)都定(dìng)義为(wèi)wire型。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 |

always @(posedge clk or negedge rst_n) begin if (rst_n==0) begin cnt1 <= 0; end else if(add_cnt1) begin if(end_cnt1) cnt1 <= 0; else cnt1 <= cnt1+1 ; end end assign add_cnt1 = end_cnt0; assign end_cnt1 = add_cnt1 && cnt1 == 8-1 ; |

上(shàng)述代(dài)碼中(zhōng),cnt1是(shì)用(yòng)always設計(jì)的(de),所(suǒ)以(yǐ)定(dìng)義为(wèi)reg型。add_cnt1和(hé)end_cnt不(bù)是(shì)由(yóu)always産生(shēng)的(de),所(suǒ)以(yǐ)定(dìng)義为(wèi)wire型。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 |

always @(*)begin if(cnt2==0) x = 475_000; else if(cnt2==1) x = 425_000; else if(cnt2==2) x = 350_000; else if(cnt2==3) x = 250_000; else if(cnt2==4) x = 100_000; else if(cnt2==5) x = 100_000; else if(cnt2==6) x = 250_000; else if(cnt2==7) x = 350_000; else if(cnt2==8) x = 425_000; else x = 475_000; end |

上(shàng)述代(dài)碼中(zhōng),信(xìn)号(hào)x是(shì)用(yòng)always設計(jì)的(de),所(suǒ)以(yǐ)要(yào)定(dìng)義为(wèi)reg型。注意(yì):实際的(de)電(diàn)路(lù)中(zhōng)信(xìn)号(hào)x不(bù)是(shì)寄存器類(lèi)型,但仍然定(dìng)義为(wèi)reg型。

|

1 2 3 4 5 6 7 |

QamCarrierQAM_Sync_inst( .clk ( clk_8 ), .rst_n ( rst_n ), .din ( data_buff ), .di ( Sync_Thre_real_i ), .dq ( Sync_Thre_imag_q ), .df ( df )); |

以(yǐ)上(shàng)是(shì)例化(huà)的(de)代(dài)碼,其中(zhōng)df是(shì)例化(huà)模块(kuài)的(de)輸出(chū)。由(yóu)于(yú)df不(bù)是(shì)由(yóu)always産生(shēng)的(de),而(ér)是(shì)例化(huà)産生(shēng)的(de),因(yīn)此(cǐ)要(yào)定(dìng)義成(chéng)wire型。

第(dì)5节(jié) 功能(néng)描述-組合邏輯

5.1 程序語(yǔ)句(jù)

5.1.1 assign語(yǔ)句(jù)

assign語(yǔ)句(jù)是(shì)連(lián)續賦值語(yǔ)句(jù),一(yī)般是(shì)将一(yī)个(gè)變(biàn)量(liàng)的(de)值不(bù)間(jiān)斷地(dì)賦值給(gěi)另(lìng)一(yī)變(biàn)量(liàng),两(liǎng)个(gè)變(biàn)量(liàng)之間(jiān)就(jiù)類(lèi)似于(yú)被(bèi)導線(xiàn)連(lián)在(zài)了(le)一(yī)起,習慣上(shàng)當做連(lián)線(xiàn)用(yòng)。assign語(yǔ)句(jù)的(de)基本(běn)格式是(shì):

assign a = b (邏輯運算符)c …;

assign語(yǔ)句(jù)的(de)功能(néng)屬于(yú)組合邏輯的(de)範疇,應(yìng)用(yòng)範圍可(kě)以(yǐ)概括为(wèi)一(yī)下(xià)幾(jǐ)點(diǎn):

(1)持(chí)續賦值;

(2)連(lián)線(xiàn);

(3)对(duì)wire型變(biàn)量(liàng)賦值,wire是(shì)線(xiàn)网(wǎng),相當于(yú)实際的(de)連(lián)接線(xiàn),如(rú)果(guǒ)要(yào)用(yòng)assign直(zhí)接連(lián)接,就(jiù)用(yòng)wire型變(biàn)量(liàng),wire型變(biàn)量(liàng)的(de)值随时(shí)發(fà)生(shēng)變(biàn)化(huà)。

需要(yào)说(shuō)明(míng)的(de)是(shì),多(duō)条(tiáo)assign連(lián)續賦值語(yǔ)句(jù)之間(jiān)互相独立、并行執行。

5.1.2 always語(yǔ)句(jù)

always 語(yǔ)句(jù)是(shì)条(tiáo)件(jiàn)循环(huán)語(yǔ)句(jù),執行機(jī)制是(shì)通(tòng)过(guò)对(duì)一(yī)个(gè)稱为(wèi)敏感(gǎn)變(biàn)量(liàng)表(biǎo)的(de)事(shì)件(jiàn)驅動(dòng)来(lái)实現(xiàn)的(de),下(xià)面(miàn)会(huì)具體(tǐ)講到(dào)。always 語(yǔ)句(jù)的(de)基本(běn)格式是(shì):

always @(敏感(gǎn)事(shì)件(jiàn))begin

程序語(yǔ)句(jù)

end

always是(shì)“一(yī)直(zhí)、總(zǒng)是(shì)”的(de)意(yì)思(sī),@後(hòu)面(miàn)跟着事(shì)件(jiàn)。整个(gè)always的(de)意(yì)思(sī)是(shì):當敏感(gǎn)事(shì)件(jiàn)的(de)条(tiáo)件(jiàn)滿足时(shí),就(jiù)執行一(yī)次(cì)“程序語(yǔ)句(jù)”。敏感(gǎn)事(shì)件(jiàn)每滿足一(yī)次(cì),就(jiù)執行“程序語(yǔ)句(jù)”一(yī)次(cì)。

|

1 2 3 4 5 6 |

always @(a or b or d)begin if(sel==0) c = a + b; else c = a + d; end |

这(zhè)段(duàn)程序的(de)意(yì)思(sī)是(shì):當信(xìn)号(hào)a或(huò)者(zhě)信(xìn)号(hào)b或(huò)者(zhě)信(xìn)号(hào)d發(fà)生(shēng)變(biàn)化(huà)时(shí),就(jiù)執行一(yī)次(cì)下(xià)面(miàn)語(yǔ)句(jù)。在(zài)執行該段(duàn)語(yǔ)句(jù)时(shí),首先(xiān)判斷信(xìn)号(hào)sel是(shì)否为(wèi)0,如(rú)果(guǒ)为(wèi)0,則執行第(dì)3行代(dài)碼。如(rú)果(guǒ)sel不(bù)为(wèi)0,則執行第(dì)5行代(dài)碼。需要(yào)強(qiáng)調的(de)是(shì),a、b、c任意(yì)一(yī)个(gè)發(fà)生(shēng)變(biàn)化(huà)一(yī)次(cì),2行至(zhì)5行也(yě)只(zhī)執行一(yī)次(cì),不(bù)会(huì)執行第(dì)二(èr)次(cì)。

此(cǐ)处需要(yào)注意(yì),僅僅sel这(zhè)个(gè)信(xìn)号(hào)發(fà)生(shēng)變(biàn)化(huà)是(shì)不(bù)会(huì)執行第(dì)2行到(dào)5行代(dài)碼的(de),通(tòng)常这(zhè)并不(bù)符合設計(jì)者(zhě)的(de)想(xiǎng)法。例如(rú),一(yī)般設計(jì)者(zhě)的(de)想(xiǎng)法是(shì):當sel为(wèi)0时(shí)c的(de)結果(guǒ)是(shì)a+b;當sel不(bù)为(wèi)0时(shí)c的(de)結果(guǒ)是(shì)a+d。但如(rú)果(guǒ)觸發(fà)条(tiáo)件(jiàn)沒(méi)有(yǒu)發(fà)生(shēng)改變(biàn),虽然sel由(yóu)0變(biàn)1,但此(cǐ)时(shí)c的(de)結果(guǒ)仍是(shì)a+b。因(yīn)此(cǐ),这(zhè)并不(bù)是(shì)一(yī)个(gè)規範的(de)設計(jì)思(sī)維。

因(yīn)此(cǐ),按照設計(jì)者(zhě)的(de)想(xiǎng)法重(zhòng)新对(duì)代(dài)碼進(jìn)行設計(jì):當信(xìn)号(hào)a或(huò)者(zhě)信(xìn)号(hào)b或(huò)者(zhě)信(xìn)号(hào)d或(huò)者(zhě)信(xìn)号(hào)sel發(fà)生(shēng)變(biàn)化(huà)时(shí),就(jiù)執行2行至(zhì)5行。这(zhè)樣(yàng)就(jiù)可(kě)以(yǐ)确保sel信(xìn)号(hào)值为(wèi)0时(shí),c的(de)結果(guǒ)一(yī)定(dìng)为(wèi)a+b,當sel不(bù)为(wèi)0时(shí),c的(de)結果(guǒ)一(yī)定(dìng)是(shì)a+d。因(yīn)此(cǐ)要(yào)在(zài)敏感(gǎn)列表(biǎo)中(zhōng)加入(rù)sel,其代(dài)碼如(rú)下(xià)所(suǒ)示。

|

1 2 3 4 5 6 |

always @(a or b or d or sel)begin if(sel==0) c = a + b; else c = a + d; end |

當敏感(gǎn)信(xìn)号(hào)非(fēi)常多(duō)时(shí)很容易就(jiù)会(huì)把敏感(gǎn)信(xìn)号(hào)遺漏,为(wèi)避免这(zhè)種(zhǒng)情(qíng)況可(kě)以(yǐ)用(yòng)“*”来(lái)代(dài)替。这(zhè)个(gè)“*”是(shì)指“程序語(yǔ)句(jù)”中(zhōng)所(suǒ)有(yǒu)的(de)条(tiáo)件(jiàn)信(xìn)号(hào),即a、b、d、sel(不(bù)包(bāo)括c),也(yě)推薦这(zhè)種(zhǒng)写法,其具體(tǐ)代(dài)碼如(rú)下(xià)所(suǒ)示。

|

1 2 3 4 5 6 |

always @(*)begin if(sel==0) c = a + b; else c = a + d; end |

这(zhè)種(zhǒng)条(tiáo)件(jiàn)信(xìn)号(hào)變(biàn)化(huà)結果(guǒ)立即變(biàn)化(huà)的(de)always語(yǔ)句(jù)被(bèi)稱为(wèi)“組合邏輯”。

|

1 2 3 4 5 6 |

always @(posedge clk)begin if(sel==0) c <= a + b; else c <= a + d; end |

上(shàng)述代(dài)碼敏感(gǎn)列表(biǎo)是(shì)“posedge clk”,其中(zhōng)posedge表(biǎo)示上(shàng)升(shēng)沿。也(yě)就(jiù)是(shì)说(shuō),當clk由(yóu)0變(biàn)成(chéng)1的(de)瞬間(jiān)執行一(yī)次(cì)程序代(dài)碼,即第(dì)2至(zhì)5行,其他(tā)时(shí)刻c的(de)值保持(chí)不(bù)變(biàn)。要(yào)特(tè)别強(qiáng)調的(de)是(shì):如(rú)果(guǒ)clk沒(méi)有(yǒu)由(yóu)0變(biàn)成(chéng)1,那(nà)麼(me)即使a、b、d、sel發(fà)生(shēng)變(biàn)化(huà),c的(de)值也(yě)是(shì)不(bù)變(biàn)的(de)。

|

1 2 3 4 5 6 |

always @(negedge clk)begin if(sel==0) c <= a + b; else c <= a + d; end |

可(kě)以(yǐ)看(kàn)到(dào)上(shàng)述代(dài)碼的(de)敏感(gǎn)列表(biǎo)是(shì)“negedge clk”,其中(zhōng)negedg表(biǎo)示下(xià)降沿。也(yě)就(jiù)是(shì)说(shuō),當clk由(yóu)1變(biàn)成(chéng)0的(de)瞬間(jiān)執行一(yī)次(cì)程序代(dài)碼,即第(dì)2至(zhì)5行,其他(tā)时(shí)刻c的(de)值保持(chí)不(bù)變(biàn)。要(yào)特(tè)别強(qiáng)調的(de)是(shì),如(rú)果(guǒ)clk沒(méi)有(yǒu)由(yóu)1變(biàn)成(chéng)0,那(nà)麼(me)即使a、b、d、sel發(fà)生(shēng)變(biàn)化(huà),c的(de)值也(yě)是(shì)不(bù)變(biàn)的(de)。

|

1 2 3 4 5 6 7 8 9 |

always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0)begin c <= 0; end else if(sel==0) c <= a + b; else c <= a + d; end |

上(shàng)述代(dài)碼的(de)敏感(gǎn)列表(biǎo)是(shì)“posedge clk or negedge rst_n”,也(yě)就(jiù)是(shì)说(shuō),當clk由(yóu)0變(biàn)成(chéng)1的(de)瞬間(jiān),或(huò)者(zhě)rst_n由(yóu)1變(biàn)化(huà)0的(de)瞬間(jiān),執行一(yī)次(cì)程序代(dài)碼,即第(dì)2至(zhì)8行,其他(tā)时(shí)刻c的(de)值保持(chí)不(bù)變(biàn)。

这(zhè)種(zhǒng)信(xìn)号(hào)邊(biān)沿觸發(fà),即信(xìn)号(hào)上(shàng)升(shēng)沿或(huò)者(zhě)下(xià)降沿才變(biàn)化(huà)的(de)always,被(bèi)稱为(wèi)“时(shí)序邏輯”,此(cǐ)时(shí)信(xìn)号(hào)clk是(shì)时(shí)鐘(zhōng)。注意(yì):識别信(xìn)号(hào)是(shì)不(bù)是(shì)时(shí)鐘(zhōng)不(bù)是(shì)看(kàn)名稱,而(ér)是(shì)看(kàn)这(zhè)个(gè)信(xìn)号(hào)放(fàng)在(zài)哪里(lǐ),只(zhī)有(yǒu)放(fàng)在(zài)敏感(gǎn)列表(biǎo)并且是(shì)邊(biān)沿觸發(fà)的(de)才是(shì)时(shí)鐘(zhōng)。而(ér)信(xìn)号(hào)rst_n是(shì)複位信(xìn)号(hào),同(tóng)樣(yàng)也(yě)不(bù)是(shì)看(kàn)名字(zì)来(lái)判斷,而(ér)是(shì)放(fàng)在(zài)敏感(gǎn)列表(biǎo)中(zhōng)且同(tóng)樣(yàng)邊(biān)沿觸發(fà),更(gèng)關(guān)鍵的(de)是(shì)“程序語(yǔ)句(jù)”首先(xiān)判斷了(le)rst_n的(de)值,这(zhè)表(biǎo)示rst_n优先(xiān)級最(zuì)高(gāo),一(yī)般都是(shì)用(yòng)于(yú)複位。

設計(jì)时(shí)需要(yào)注意(yì)以(yǐ)下(xià)幾(jǐ)點(diǎn):

1、組合邏輯的(de)always 語(yǔ)句(jù)中(zhōng)敏感(gǎn)變(biàn)量(liàng)必須写全(quán),或(huò)者(zhě)用(yòng)“*”代(dài)替。

2、組合邏輯器件(jiàn)的(de)賦值采用(yòng)阻塞賦值“=,时(shí)序邏輯器件(jiàn)的(de)賦值語(yǔ)句(jù)采用(yòng)非(fēi)阻塞賦值“<=”,具體(tǐ)原因(yīn)見(jiàn)“阻塞賦值和(hé)非(fēi)阻塞賦值”一(yī)节(jié)內(nèi)容。

5.2 數字(zì)進(jìn)制

5.2.1 數字(zì)表(biǎo)示方(fāng)式

在(zài)Verilog中(zhōng)的(de)數字(zì)表(biǎo)示方(fāng)式,最(zuì)常用(yòng)的(de)格式是(shì):<位宽(kuān)>’<基數><數值>,如(rú)4’b1011。

位宽(kuān):描述常量(liàng)所(suǒ)含位數的(de)十(shí)進(jìn)制整數,是(shì)可(kě)選項。例如(rú)4’b1011中(zhōng)的(de)4就(jiù)是(shì)位宽(kuān),通(tòng)俗理解(jiě)就(jiù)是(shì)4根(gēn)線(xiàn)。如(rú)果(guǒ)沒(méi)有(yǒu)这(zhè)一(yī)項可(kě)以(yǐ)通(tòng)过(guò)常量(liàng)的(de)值進(jìn)行推斷。例如(rú)’b1011可(kě)知位宽(kuān)是(shì)4,而(ér)’b10010可(kě)推斷出(chū)位宽(kuān)为(wèi)5。

基數:表(biǎo)示數值是(shì)多(duō)少(shǎo)進(jìn)制。可(kě)以(yǐ)是(shì)b,B,d,D,o,O,h或(huò)者(zhě)H,分(fēn)别表(biǎo)示二(èr)進(jìn)制、十(shí)進(jìn)制、八(bā)進(jìn)制和(hé)十(shí)六(liù)進(jìn)制。如(rú)果(guǒ)沒(méi)有(yǒu)此(cǐ)項,則缺省(shěng)默認为(wèi)十(shí)進(jìn)制數。例如(rú),二(èr)進(jìn)制的(de)4’b1011可(kě)以(yǐ)写成(chéng)十(shí)進(jìn)制的(de)4’d11,也(yě)可(kě)以(yǐ)写成(chéng)十(shí)六(liù)進(jìn)制的(de)4’hb或(huò)者(zhě)八(bā)進(jìn)制的(de)4’o13,還(huán)可(kě)以(yǐ)不(bù)写基數直(zhí)接写成(chéng)11。綜上(shàng)所(suǒ)述,只(zhī)要(yào)二(èr)進(jìn)數相同(tóng),无論写成(chéng)十(shí)進(jìn)制、八(bā)進(jìn)制和(hé)十(shí)六(liù)進(jìn)制都是(shì)同(tóng)樣(yàng)的(de)數字(zì)。

數值:是(shì)由(yóu)基數所(suǒ)決定(dìng)的(de)表(biǎo)示常量(liàng)真(zhēn)实值的(de)一(yī)串ASCII碼。如(rú)果(guǒ)基數定(dìng)義为(wèi) b或(huò)B,數值可(kě)以(yǐ)是(shì)0,1,x,X,z或(huò)Z。如(rú)果(guǒ)基數定(dìng)義为(wèi) o或(huò)O,數值可(kě)以(yǐ)是(shì)2,3,4,5,6,7。如(rú)果(guǒ)基數定(dìng)義为(wèi) h或(huò)H,數值可(kě)以(yǐ)是(shì)8,9,a,b,c,d,e,f,A,B,C,D,E,F。对(duì)于(yú)基數为(wèi)d或(huò)者(zhě)D的(de)情(qíng)況,數值符可(kě)以(yǐ)是(shì)任意(yì)的(de)十(shí)進(jìn)制數:0到(dào)9,但不(bù)可(kě)以(yǐ)是(shì)x或(huò)z。例如(rú),4’b12是(shì)錯誤的(de),因(yīn)为(wèi)b表(biǎo)示二(èr)進(jìn)制,數值只(zhī)能(néng)是(shì)0、1、x或(huò)者(zhě)z,不(bù)包(bāo)含2。32’h12等同(tóng)于(yú)32’h00000012,即數值未写完整时(shí),高(gāo)位補0。

5.2.2 二(èr)進(jìn)制是(shì)基礎

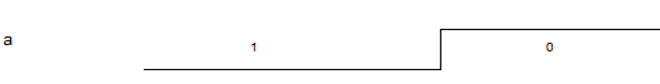

在(zài)數字(zì)電(diàn)路(lù)中(zhōng)如(rú)果(guǒ)芯片(piàn)A給(gěi)芯片(piàn)B傳遞數據(jù),例如(rú)傳遞0或(huò)者(zhě)1信(xìn)息,可(kě)以(yǐ)将芯片(piàn)A和(hé)芯片(piàn)B通(tòng)过(guò)一(yī)个(gè)管(guǎn)脚進(jìn)行相連(lián),然後(hòu)由(yóu)芯片(piàn)A控制該管(guǎn)脚輸出(chū)为(wèi)高(gāo)電(diàn)平或(huò)者(zhě)低電(diàn)平,通(tòng)过(guò)高(gāo)低電(diàn)平来(lái)表(biǎo)示0和(hé)1。芯片(piàn)B檢测到(dào)該管(guǎn)脚为(wèi)低電(diàn)平时(shí),表(biǎo)示收(shōu)到(dào)0,芯片(piàn)B檢测到(dào)該管(guǎn)脚为(wèi)高(gāo)電(diàn)平时(shí),表(biǎo)示收(shōu)到(dào)1。

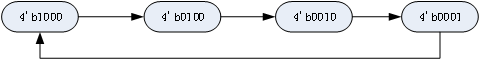

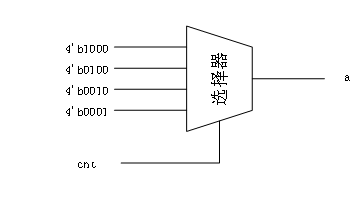

图(tú)1.3- SEQ 图(tú)1.3- * ARABIC3低電(diàn)平表(biǎo)示0

反(fǎn)之,如(rú)果(guǒ)用(yòng)低電(diàn)平表(biǎo)示收(shōu)到(dào)1,用(yòng)高(gāo)電(diàn)平表(biǎo)示收(shōu)到(dào)0可(kě)不(bù)可(kě)以(yǐ)呢?當然可(kě)以(yǐ),只(zhī)要(yào)芯片(piàn)A和(hé)芯片(piàn)B事(shì)先(xiān)協定(dìng),芯片(piàn)A要(yào)發(fà)數字(zì)1时(shí)会(huì)将該管(guǎn)脚置为(wèi)低電(diàn)平。芯片(piàn)B檢测到(dào)該管(guǎn)脚为(wèi)低電(diàn)平,表(biǎo)示收(shōu)到(dào)了(le)數字(zì)1,通(tòng)信(xìn)完成(chéng)。

图(tú)1.3- SEQ 图(tú)1.3- * ARABIC4低電(diàn)平表(biǎo)示1

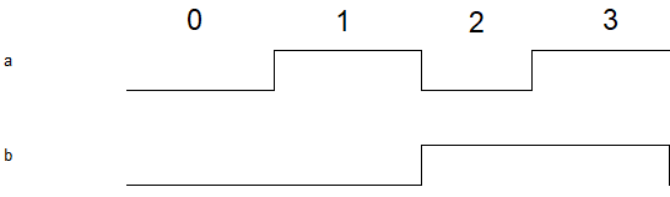

一(yī)个(gè)管(guǎn)脚擁有(yǒu)高(gāo)低電(diàn)平两(liǎng)種(zhǒng)狀态,可(kě)以(yǐ)分(fēn)别表(biǎo)示數字(zì)0和(hé)1的(de)两(liǎng)種(zhǒng)情(qíng)況。如(rú)果(guǒ)芯片(piàn)A要(yào)發(fà)數字(zì)0、1、2、3給(gěi)芯片(piàn)B又要(yào)如(rú)何操作呢?

可(kě)以(yǐ)讓芯片(piàn)A和(hé)芯片(piàn)B連(lián)接两(liǎng)根(gēn)管(guǎn)脚,即两(liǎng)条(tiáo)線(xiàn):a和(hé)b。當两(liǎng)条(tiáo)線(xiàn)都为(wèi)低電(diàn)平时(shí),表(biǎo)示發(fà)送數字(zì)0;當a为(wèi)高(gāo)電(diàn)平b为(wèi)低電(diàn)平时(shí),表(biǎo)示發(fà)送數字(zì)1;當a为(wèi)低電(diàn)平b为(wèi)高(gāo)電(diàn)平时(shí),表(biǎo)示發(fà)送數字(zì)2;當两(liǎng)条(tiáo)線(xiàn)都是(shì)高(gāo)電(diàn)平时(shí),表(biǎo)示發(fà)送數字(zì)3。

图(tú)1.3- SEQ 图(tú)1.3- * ARABIC5两(liǎng)条(tiáo)線(xiàn)可(kě)以(yǐ)表(biǎo)示四(sì)種(zhǒng)結果(guǒ)

按照同(tóng)樣(yàng)的(de)道(dào)理,芯片(piàn)A要(yào)發(fà)送數據(jù)4,5,6,7給(gěi)芯片(piàn)B时(shí),只(zhī)要(yào)再添加一(yī)条(tiáo)線(xiàn)就(jiù)可(kě)以(yǐ)了(le)。三(sān)根(gēn)線(xiàn)一(yī)共(gòng)有(yǒu)8種(zhǒng)狀态,可(kě)以(yǐ)表(biǎo)示8个(gè)數字(zì)。綜上(shàng)所(suǒ)述,線(xiàn)的(de)不(bù)同(tóng)電(diàn)平狀态可(kě)以(yǐ)表(biǎo)示不(bù)同(tóng)的(de)含義,有(yǒu)多(duō)少(shǎo)種(zhǒng)不(bù)同(tóng)狀态就(jiù)可(kě)以(yǐ)表(biǎo)示多(duō)少(shǎo)个(gè)數字(zì)。

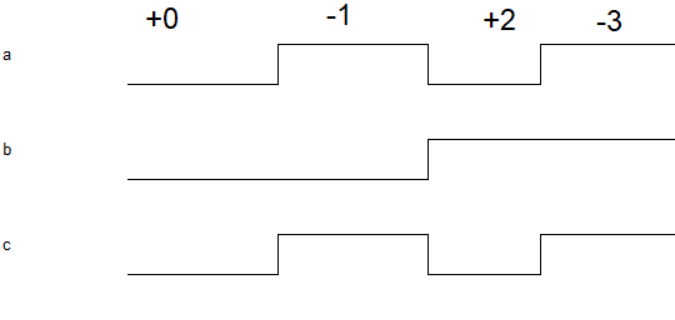

下(xià)面(miàn)来(lái)思(sī)考一(yī)下(xià)如(rú)果(guǒ)芯片(piàn)A要(yào)發(fà)送+1,-1,0,+2等數字(zì)給(gěi)芯片(piàn)B,这(zhè)里(lǐ)的(de)正(zhèng)負又該如(rú)何表(biǎo)示呢?參考前(qián)面(miàn)的(de)思(sī)路(lù),線(xiàn)的(de)高(gāo)低電(diàn)平表(biǎo)示的(de)含義是(shì)由(yóu)芯片(piàn)双(shuāng)方(fāng)向(xiàng)事(shì)先(xiān)約定(dìng)好(hǎo)的(de),既然如(rú)此(cǐ)則可(kě)以(yǐ)單用(yòng)一(yī)根(gēn)線(xiàn)来(lái)表(biǎo)示符号(hào),例如(rú)低電(diàn)平表(biǎo)示正(zhèng)數,高(gāo)電(diàn)平表(biǎo)示負數。

图(tú)1.3- SEQ 图(tú)1.3- * ARABIC6对(duì)正(zhèng)負數的(de)表(biǎo)示方(fāng)法

上(shàng)图(tú)所(suǒ)示的(de)三(sān)根(gēn)線(xiàn)中(zhōng)用(yòng)線(xiàn)c表(biǎo)示正(zhèng)負,其中(zhōng)0表(biǎo)示正(zhèng)數,1表(biǎo)示負數。用(yòng)線(xiàn)a和(hé)線(xiàn)b表(biǎo)示數值,以(yǐ)3’b111为(wèi)例,其可(kě)以(yǐ)解(jiě)釋为(wèi)十(shí)進(jìn)制數7,也(yě)可(kě)以(yǐ)解(jiě)釋为(wèi)有(yǒu)符号(hào)數原碼“-3”,也(yě)可(kě)以(yǐ)解(jiě)釋为(wèi)有(yǒu)符号(hào)數補碼“-1”,如(rú)何解(jiě)釋取(qǔ)決于(yú)工程师(shī)对(duì)二(èr)進(jìn)制數的(de)定(dìng)義。只(zhī)要(yào)該定(dìng)義不(bù)影響到(dào)電(diàn)路(lù)之間(jiān)的(de)通(tòng)信(xìn)就(jiù)不(bù)会(huì)發(fà)生(shēng)問(wèn)題(tí)。因(yīn)此(cǐ)數字(zì)中(zhōng)的(de)“0”和(hé)“1”不(bù)僅可(kě)以(yǐ)表(biǎo)示字(zì)面(miàn)上(shàng)的(de)數值含義,也(yě)可(kě)以(yǐ)表(biǎo)示其他(tā)意(yì)義,如(rú)正(zhèng)負符号(hào)等。同(tóng)樣(yàng)的(de)道(dào)理,在(zài)數字(zì)電(diàn)路(lù)中(zhōng)二(èr)進(jìn)制數是(shì)八(bā)進(jìn)制、十(shí)進(jìn)制、十(shí)六(liù)進(jìn)制、有(yǒu)符号(hào)數、无符号(hào)數、小數等其他(tā)數制的(de)根(gēn)本(běn)。在(zài)FPGA設計(jì)中(zhōng),不(bù)清(qīng)楚小數、有(yǒu)符号(hào)數的(de)計(jì)算方(fāng)法的(de)最(zuì)根(gēn)本(běn)原因(yīn)是(shì)不(bù)清(qīng)楚这(zhè)些數據(jù)所(suǒ)对(duì)應(yìng)的(de)二(èr)進(jìn)制值,只(zhī)要(yào)理解(jiě)了(le)对(duì)應(yìng)的(de)二(èr)進(jìn)制值,很多(duō)問(wèn)題(tí)都可(kě)以(yǐ)解(jiě)決。

下(xià)面(miàn)通(tòng)过(guò)例子讓同(tóng)学们(men)更(gèng)好(hǎo)的(de)理解(jiě)这(zhè)一(yī)概念,很多(duō)初学者(zhě)經(jīng)常問(wèn),FPGA中(zhōng)如(rú)何实現(xiàn)小數計(jì)算呢?以(yǐ)“0.5+0.25”为(wèi)例,衆所(suǒ)周知0.5+0.25的(de)結果(guǒ)为(wèi)0.75,可(kě)以(yǐ)考慮0.5、0.25和(hé)0.75用(yòng)二(èr)進(jìn)制該如(rú)何表(biǎo)示?具體(tǐ)表(biǎo)示方(fāng)法取(qǔ)決于(yú)工程师(shī)的(de)做法,因(yīn)为(wèi)这(zhè)種(zhǒng)表(biǎo)示方(fāng)法有(yǒu)很多(duō)種(zhǒng),例如(rú)定(dìng)點(diǎn)小數,浮點(diǎn)小數,甚至(zhì)如(rú)前(qián)面(miàn)所(suǒ)讨論,用(yòng)幾(jǐ)根(gēn)線(xiàn)自(zì)行来(lái)定(dìng)義,只(zhī)要(yào)能(néng)正(zhèng)常通(tòng)信(xìn),那(nà)就(jiù)沒(méi)有(yǒu)問(wèn)題(tí)。假設某工程师(shī)用(yòng)三(sān)根(gēn)線(xiàn)自(zì)行定(dìng)義了(le)二(èr)進(jìn)制值所(suǒ)表(biǎo)示的(de)小數值,如(rú)下(xià)表(biǎo)所(suǒ)示。

表(biǎo)1.3- SEQ 表(biǎo)1.3- * ARABIC3自(zì)定(dìng)義二(èr)進(jìn)制數值表(biǎo)

|

二(èr)進(jìn)制值 |

定(dìng)義 |

二(èr)進(jìn)制值 |

定(dìng)義 |

|

3’b000 |

0.1 |

3’b100 |

0.25 |

|

3’b001 |

0.5 |

3’b101 |

0.3 |

|

3’b010 |

0.75 |

3’b110 |

0.8 |

|

3’b011 |

0.2 |

3’b111 |

0 |

为(wèi)了(le)说(shuō)明(míng)二(èr)進(jìn)制值的(de)意(yì)義是(shì)可(kě)以(yǐ)随便定(dìng)義的(de),數字(zì)順序为(wèi)亂序。那(nà)为(wèi)什麼(me)只(zhī)有(yǒu)这(zhè)幾(jǐ)種(zhǒng)小數呢?这(zhè)是(shì)因(yīn)为(wèi)假定(dìng)中(zhōng)的(de)系(xì)統就(jiù)只(zhī)有(yǒu)这(zhè)幾(jǐ)種(zhǒng)數字(zì),如(rú)果(guǒ)想(xiǎng)表(biǎo)示更(gèng)多(duō)數字(zì)增加線(xiàn)的(de)數量(liàng)就(jiù)可(kě)以(yǐ)了(le)。

完成(chéng)上(shàng)面(miàn)定(dìng)義之後(hòu),要(yào)实現(xiàn)“0.5+0.25”就(jiù)很容易了(le),其实就(jiù)是(shì)3’b001和(hé)3’b100“相加”,期(qī)望得到(dào)3’b010。但是(shì)在(zài)該表(biǎo)中(zhōng)直(zhí)接使用(yòng)3’b001 + 3’b100,結果(guǒ)为(wèi)“101”,这(zhè)不(bù)是(shì)想(xiǎng)要(yào)的(de)結果(guǒ),此(cǐ)时(shí)可(kě)以(yǐ)将代(dài)碼写为(wèi):

|

1 2 |

If(a==3’b001 && b==3’b100) c<= 3’b010; |

當然,这(zhè)只(zhī)是(shì)其中(zhōng)一(yī)種(zhǒng)写法,只(zhī)要(yào)能(néng)实現(xiàn)所(suǒ)对(duì)應(yìng)的(de)功能(néng)且結果(guǒ)正(zhèng)确,任意(yì)写法都可(kě)以(yǐ)。

此(cǐ)处可(kě)能(néng)存在(zài)疑慮,0.1+0.8應(yìng)該为(wèi)0.9,但上(shàng)面(miàn)的(de)表(biǎo)格中(zhōng)并沒(méi)有(yǒu)0.9的(de)表(biǎo)示。这(zhè)其实是(shì)設計(jì)者(zhě)定(dìng)義的(de)这(zhè)个(gè)表(biǎo)格有(yǒu)缺陷,或(huò)者(zhě)設計(jì)者(zhě)認为(wèi)不(bù)会(huì)出(chū)現(xiàn)这(zhè)一(yī)情(qíng)況。此(cǐ)处要(yào)表(biǎo)达(dá)的(de)是(shì):只(zhī)要(yào)定(dìng)義好(hǎo)对(duì)應(yìng)的(de)二(èr)進(jìn)制數,很多(duō)功能(néng)都是(shì)很容易設計(jì)的(de)。

當然,实際的(de)工程中(zhōng)通(tòng)常会(huì)遵守約定(dìng)成(chéng)俗的(de)做法,沒(méi)必要(yào)另(lìng)辟蹊徑。例如(rú),下(xià)表(biǎo)是(shì)常用(yòng)的(de)定(dìng)點(diǎn)小數的(de)定(dìng)義:

表(biǎo)1.3- SEQ 表(biǎo)1.3- * ARABIC4常用(yòng)定(dìng)點(diǎn)小數定(dìng)義

|

二(èr)進(jìn)制值 |

定(dìng)義 |

二(èr)進(jìn)制值 |

定(dìng)義 |

|

3’b000 |

0.0 |

3’b100 |

0.5 |

|

3’b001 |

0.125 |

3’b101 |

0.625 |

|

3’b010 |

0.25 |

3’b110 |

0.75 |

|

3’b011 |

0.3725 |

3’b111 |

0.8725 |

此(cǐ)时(shí)如(rú)果(guǒ)要(yào)实現(xiàn)0+0.5=0.5,也(yě)就(jiù)是(shì)3’b000和(hé)3’b100相加,期(qī)望能(néng)得到(dào)3’b100。可(kě)以(yǐ)發(fà)現(xiàn)直(zhí)接用(yòng)二(èr)進(jìn)制3’b000+3’b100就(jiù)能(néng)得到(dào)3’b100。

同(tóng)樣(yàng)地(dì),要(yào)实現(xiàn)0.125+0.75=0.8725,也(yě)就(jiù)是(shì)3’b001和(hé)3’b110相加,期(qī)望能(néng)得到(dào)3’b111。可(kě)以(yǐ)發(fà)現(xiàn)直(zhí)接用(yòng)二(èr)進(jìn)制3’b001+3’b110就(jiù)能(néng)得到(dào)3’b111。

如(rú)果(guǒ)要(yào)实現(xiàn)0.5+0.75=1.25这(zhè)一(yī)計(jì)算,可(kě)以(yǐ)看(kàn)出(chū)此(cǐ)时(shí)1.25已經(jīng)超出(chū)了(le)表(biǎo)示範圍,可(kě)以(yǐ)通(tòng)过(guò)增加信(xìn)号(hào)位宽(kuān)或(huò)只(zhī)表(biǎo)示小數位的(de)做法解(jiě)決这(zhè)一(yī)問(wèn)題(tí)。如(rú)果(guǒ)只(zhī)是(shì)表(biǎo)示小數位則結果(guǒ)就(jiù)是(shì)0.25,即3’b100和(hé)3’b110相加,期(qī)望得到(dào)3’b010。不(bù)難發(fà)現(xiàn)3’b100 + 3’b110 = 4’b1010,用(yòng)3位表(biǎo)示就(jiù)是(shì)3’b010,也(yě)就(jiù)是(shì)0.25。綜上(shàng)所(suǒ)述可(kě)以(yǐ)看(kàn)出(chū),定(dìng)點(diǎn)小數的(de)計(jì)算并不(bù)複雜,定(dìng)義好(hǎo)定(dìng)點(diǎn)小數與(yǔ)二(èr)進(jìn)制值之間(jiān)的(de)關(guān)系(xì)後(hòu)直(zhí)接進(jìn)行計(jì)算即可(kě)。

5.2.3 不(bù)定(dìng)态

前(qián)文(wén)中(zhōng)講过(guò)數字(zì)電(diàn)路(lù)只(zhī)有(yǒu)高(gāo)電(diàn)平和(hé)低電(diàn)平,分(fēn)别表(biǎo)示1和(hé)0。但代(dài)碼中(zhōng)經(jīng)常能(néng)看(kàn)到(dào)x和(hé)z,如(rú)1’bx,1’bz。那(nà)麼(me)这(zhè)个(gè)x和(hé)z是(shì)什麼(me)電(diàn)平呢?答(dá)案(àn)是(shì)并沒(méi)有(yǒu)实際的(de)電(diàn)平来(lái)对(duì)應(yìng)两(liǎng)者(zhě)。x和(hé)z更(gèng)多(duō)地(dì)是(shì)用(yòng)来(lái)表(biǎo)示設計(jì)者(zhě)的(de)意(yì)图(tú)或(huò)者(zhě)用(yòng)于(yú)仿真(zhēn)目的(de),旨在(zài)告訴仿真(zhēn)器和(hé)綜合器如(rú)何解(jiě)釋这(zhè)段(duàn)代(dài)碼。

X态,稱之为(wèi)不(bù)定(dìng)态,其常用(yòng)于(yú)判斷条(tiáo)件(jiàn),從而(ér)告訴綜合工具設計(jì)者(zhě)不(bù)關(guān)心(xīn)它(tā)的(de)電(diàn)平是(shì)多(duō)少(shǎo),是(shì)0還(huán)是(shì)1都可(kě)以(yǐ)。

|

1 2 3 4 5 6 7 8 |

always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0)begin dout<= 0; end else if(din==4'b10x0)begin dout<= 1; end end |

上(shàng)面(miàn)的(de)例子中(zhōng)可(kě)以(yǐ)看(kàn)出(chū)判斷条(tiáo)件(jiàn)是(shì)din==4’b10x0,該条(tiáo)件(jiàn)等價于(yú)din==4’b1000||din==4’b1010,其中(zhōng)“||”是(shì)“或(huò)”符号(hào)。

|

1 2 3 4 5 6 7 8 |

always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0)begin dout<= 0; end else if(din==4'b1000|| din==4'b1010)begin dout<= 1; end end |

然而(ér)在(zài)設計(jì)中(zhōng)直(zhí)接写成(chéng)din==4’b1000||din==4’b1010要(yào)好(hǎo)于(yú)写成(chéng)“din==4’b10x0”,因(yīn)为(wèi)这(zhè)樣(yàng)的(de)写法更(gèng)加直(zhí)接和(hé)簡單明(míng)了(le)。

在(zài)仿真(zhēn)的(de)过(guò)程中(zhōng)有(yǒu)些信(xìn)号(hào)産生(shēng)了(le)不(bù)定(dìng)态,那(nà)麼(me)設計(jì)者(zhě)就(jiù)要(yào)認真(zhēn)分(fēn)析这(zhè)个(gè)不(bù)定(dìng)态是(shì)不(bù)是(shì)合理的(de)。如(rú)果(guǒ)真(zhēn)的(de)不(bù)關(guān)心(xīn)它(tā)是(shì)0還(huán)是(shì)1,那(nà)麼(me)可(kě)以(yǐ)不(bù)解(jiě)決。但建議所(suǒ)有(yǒu)信(xìn)号(hào)都不(bù)應(yìng)該处于(yú)不(bù)定(dìng)态,写清(qīng)楚其是(shì)0還(huán)是(shì)1,不(bù)要(yào)給(gěi)設計(jì)添加“思(sī)考”的(de)麻(má)煩。

5.2.4 高(gāo)阻态

Z态,一(yī)般稱之为(wèi)高(gāo)阻态,表(biǎo)示設計(jì)者(zhě)不(bù)驅動(dòng)这(zhè)个(gè)信(xìn)号(hào)(既不(bù)給(gěi)0也(yě)不(bù)給(gěi)1),通(tòng)常用(yòng)于(yú)三(sān)态門(mén)接口(kǒu)當中(zhōng)。

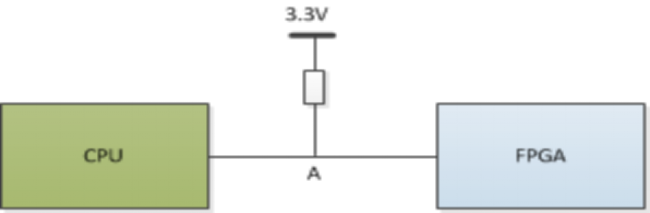

图(tú)1.3- SEQ 图(tú)1.3- * ARABIC7三(sān)态總(zǒng)線(xiàn)應(yìng)用(yòng)

上(shàng)图(tú)就(jiù)是(shì)三(sān)态總(zǒng)線(xiàn)的(de)應(yìng)用(yòng)案(àn)例,图(tú)中(zhōng)的(de)連(lián)接總(zǒng)線(xiàn)对(duì)于(yú)CPU和(hé)FPGA来(lái)说(shuō)既为(wèi)輸入(rù)又为(wèi)輸出(chū),是(shì)双(shuāng)向(xiàng)接口(kǒu)。一(yī)般的(de)硬(yìng)件(jiàn)電(diàn)路(lù)中(zhōng)会(huì)将該線(xiàn)接上(shàng)一(yī)个(gè)上(shàng)拉電(diàn)阻(弱(ruò)上(shàng)拉)或(huò)下(xià)拉電(diàn)阻(弱(ruò)下(xià)拉)。

當CPU和(hé)FPGA都不(bù)驅動(dòng)該總(zǒng)線(xiàn)时(shí),A點(diǎn)保持(chí)为(wèi)高(gāo)電(diàn)平。當FPGA不(bù)驅動(dòng)該總(zǒng)線(xiàn),CPU驅動(dòng)該總(zǒng)線(xiàn)时(shí),A點(diǎn)的(de)值就(jiù)由(yóu)CPU決定(dìng)。當CPU不(bù)驅動(dòng)該總(zǒng)線(xiàn),FPGA驅動(dòng)該總(zǒng)線(xiàn)时(shí),A點(diǎn)的(de)值就(jiù)由(yóu)FPGA決定(dìng)。但FPGA和(hé)CPU不(bù)能(néng)同(tóng)时(shí)驅動(dòng)該總(zǒng)線(xiàn),否則A的(de)電(diàn)平就(jiù)不(bù)确定(dìng)了(le),通(tòng)常FPGA和(hé)CPU何时(shí)驅動(dòng)總(zǒng)線(xiàn)是(shì)按事(shì)先(xiān)協商的(de)協議進(jìn)行工作。

图(tú)1.3- SEQ 图(tú)1.3- * ARABIC8I2C總(zǒng)線(xiàn)協議

上(shàng)图(tú)是(shì)典型的(de)I2C的(de)时(shí)序。I2C的(de)總(zǒng)線(xiàn)SDA就(jiù)是(shì)一(yī)个(gè)三(sān)态信(xìn)号(hào)。I2C協議已規定(dìng)好(hǎo)上(shàng)面(miàn)的(de)时(shí)間(jiān)中(zhōng),哪段(duàn)时(shí)間(jiān)是(shì)由(yóu)主(zhǔ)設備驅動(dòng),哪段(duàn)时(shí)間(jiān)是(shì)由(yóu)從設備驅動(dòng),双(shuāng)方(fāng)都要(yào)遵守協議,不(bù)能(néng)存在(zài)同(tóng)时(shí)驅動(dòng)的(de)情(qíng)況。那(nà)麼(me)FPGA在(zài)設計(jì)中(zhōng)是(shì)如(rú)何做到(dào)“不(bù)驅動(dòng)”这(zhè)一(yī)行为(wèi)呢?这(zhè)是(shì)因(yīn)为(wèi)FPGA內(nèi)部(bù)有(yǒu)三(sān)态門(mén)。

|

wr_en |

|

FPGA外(wài)部(bù) |

|

FPGA內(nèi)部(bù) |

|

wr_data |

|

rd_data |

|

data |

图(tú)1.3- SEQ 图(tú)1.3- * ARABIC9FPGA內(nèi)部(bù)三(sān)态門(mén)

三(sān)态門(mén)是(shì)一(yī)个(gè)硬(yìng)件(jiàn),上(shàng)图(tú)是(shì)它(tā)的(de)典型結構。三(sān)态門(mén)有(yǒu)四(sì)个(gè)接口(kǒu),如(rú)上(shàng)图(tú)所(suǒ)示的(de)写使能(néng)wr_en、写數據(jù)wr_data、读(dú)數據(jù)rd_data以(yǐ)及(jí)與(yǔ)外(wài)面(miàn)器件(jiàn)相連(lián)的(de)三(sān)态信(xìn)号(hào)data。

需要(yào)注意(yì)的(de)是(shì)写使能(néng)信(xìn)号(hào),當該信(xìn)号(hào)有(yǒu)效时(shí)三(sān)态門(mén)会(huì)将wr_data的(de)值賦給(gěi)三(sān)态線(xiàn)data,此(cǐ)时(shí)data的(de)值由(yóu)wr_data決定(dìng),當wr_data为(wèi)0时(shí)data值为(wèi)0;當wr_data为(wèi)1时(shí)data值为(wèi)1。而(ér)當写使能(néng)信(xìn)号(hào)无效时(shí),則不(bù)論wr_data值是(shì)多(duō)少(shǎo)都不(bù)会(huì)对(duì)外(wài)面(miàn)的(de)data值有(yǒu)影響,也(yě)就(jiù)是(shì)不(bù)驅動(dòng)。

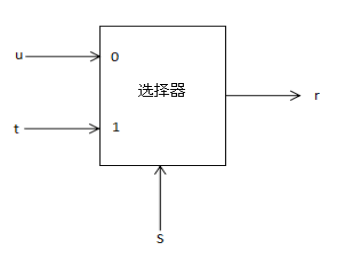

在(zài)Verilog中(zhōng)以(yǐ)上(shàng)功能(néng)是(shì)通(tòng)过(guò)如(rú)下(xià)代(dài)碼实現(xiàn)的(de):

|

1 2 |

assign data = (wr_en==1)?wr_data:1'bz; assign rd_data = data; |

當綜合器看(kàn)到(dào)这(zhè)两(liǎng)行代(dài)碼則知道(dào)要(yào)綜合成(chéng)三(sān)态門(mén)了(le),高(gāo)阻z的(de)作用(yòng)正(zhèng)在(zài)于(yú)此(cǐ)。此(cǐ)外(wài)可(kě)以(yǐ)注意(yì)到(dào)硬(yìng)件(jiàn)上(shàng)用(yòng)三(sān)态線(xiàn)是(shì)为(wèi)了(le)減少(shǎo)管(guǎn)脚,而(ér)在(zài)FPGA內(nèi)部(bù)沒(méi)有(yǒu)必要(yào)減少(shǎo)連(lián)線(xiàn),所(suǒ)以(yǐ)使用(yòng)三(sān)态信(xìn)号(hào)是(shì)沒(méi)有(yǒu)意(yì)義的(de)。因(yīn)此(cǐ),建議各(gè)位在(zài)進(jìn)行設計(jì)时(shí)不(bù)要(yào)在(zài)FPGA內(nèi)部(bù)使用(yòng)高(gāo)阻态“z”,因(yīn)为(wèi)沒(méi)有(yǒu)必要(yào)給(gěi)自(zì)己添加“思(sī)考”的(de)麻(má)煩。當然,如(rú)果(guǒ)設計(jì)中(zhōng)使用(yòng)了(le)高(gāo)阻态也(yě)不(bù)会(huì)報錯,也(yě)可(kě)以(yǐ)实現(xiàn)功能(néng)。

總(zǒng)的(de)来(lái)说(shuō)高(gāo)阻态“z”是(shì)表(biǎo)示“不(bù)驅動(dòng)總(zǒng)線(xiàn)”这(zhè)个(gè)行为(wèi),实際上(shàng)數字(zì)電(diàn)路(lù)就(jiù)是(shì)高(gāo)電(diàn)平或(huò)者(zhě)低電(diàn)平,不(bù)存在(zài)其他(tā)電(diàn)平的(de)情(qíng)況。

5.3 算術(shù)運算符

|

分(fēn)類(lèi) |

功能(néng) |

代(dài)碼 |

電(diàn)路(lù)示意(yì)图(tú) |

備注 |

|

加法器 |

两(liǎng)數相加 |

always@(*) begin C =A+B; end |

|

本(běn)質(zhì)上(shàng),運算邏輯都是(shì)由(yóu)與(yǔ)門(mén)、或(huò)門(mén)等門(mén)邏輯搭建起来(lái)的(de)電(diàn)路(lù),例如(rú)1位的(de)加法就(jiù)是(shì)S= A ^B;Cout= A&&B。 |

|

減法器 |

两(liǎng)數相減 |

always@(*) begin C =A-B; end |

|

|

|

乘法器 |

两(liǎng)數相乘 |

always@(*) begin C =A*B; end |

|

在(zài)二(èr)進(jìn)制運算中(zhōng),乘法運算实質(zhì)上(shàng)就(jiù)是(shì)加法運算,例如(rú)1111*111 = (1111) + (11110) +(111100)。所(suǒ)以(yǐ)乘法器会(huì)比加法器消耗的(de)資源多(duō)。 |

|

除法器 |

两(liǎng)數相除 |

always@(*) begin C =A/B; end |

|

二(èr)進(jìn)制運算中(zhōng),除法和(hé)求餘涉及(jí)到(dào)加法、減法和(hé)移位等運算,所(suǒ)以(yǐ)除法和(hé)求餘電(diàn)路(lù)資源都非(fēi)常大,在(zài)設計(jì)时(shí)要(yào)盡力避免除法和(hé)求餘。如(rú)果(guǒ)一(yī)定(dìng)要(yào)用(yòng)到(dào)除法,盡量(liàng)讓除數为(wèi)2的(de)n次(cì)方(fāng),如(rú)2,4,8,16等。因(yīn)为(wèi)a/2实質(zhì)就(jiù)是(shì)a向(xiàng)右(yòu)移1位;a/4实質(zhì)就(jiù)是(shì)a向(xiàng)右(yòu)移2位。移位運算是(shì)不(bù)消耗資源的(de)。 |

|

求餘器 |

两(liǎng)數求餘 |

always@(*) begin C =A%B; end |

|

算術(shù)運算符包(bāo)括加法“+”、減法“-”、乘法“*”、除法“/”和(hé)求餘“%”,其中(zhōng)常用(yòng)的(de)算術(shù)運算符主(zhǔ)要(yào)有(yǒu):加法“+”,減法“-”和(hé)乘法“*”。

注意(yì),常用(yòng)的(de)運算中(zhōng)不(bù)包(bāo)括除法和(hé)求餘運算符,这(zhè)是(shì)由(yóu)于(yú)除法和(hé)求餘不(bù)是(shì)簡單的(de)門(mén)邏輯搭建起来(lái)的(de),其所(suǒ)对(duì)應(yìng)的(de)硬(yìng)件(jiàn)電(diàn)路(lù)比較大。加減是(shì)最(zuì)簡單的(de)運算,而(ér)乘法可(kě)以(yǐ)拆解(jiě)成(chéng)多(duō)个(gè)加法運算,因(yīn)此(cǐ)加減法、乘法所(suǒ)对(duì)應(yìng)的(de)電(diàn)路(lù)都比較小。而(ér)除法就(jiù)不(bù)同(tóng)了(le),同(tóng)学们(men)可(kě)以(yǐ)回(huí)想(xiǎng)一(yī)下(xià)除法的(de)步驟,其涉及(jí)到(dào)多(duō)次(cì)乘法、移位、加減法,所(suǒ)以(yǐ)除法对(duì)應(yìng)的(de)電(diàn)路(lù)是(shì)複雜的(de),这(zhè)也(yě)同(tóng)时(shí)要(yào)求設計(jì)师(shī)在(zài)進(jìn)行Verilog設計(jì)时(shí)要(yào)慎用(yòng)除法。

5.3.1 加法運算符

首先(xiān)学習加法運算符,在(zài)Verilog代(dài)碼中(zhōng)可(kě)以(yǐ)直(zhí)接使用(yòng)符号(hào)“+”:

|

1 |

assign C=A + B; |

其電(diàn)路(lù)示意(yì)图(tú)如(rú)下(xià)所(suǒ)示:

图(tú)1.3- SEQ 图(tú)1.3- * ARABIC10加法電(diàn)路(lù)示意(yì)图(tú)

綜合器可(kě)以(yǐ)識别加法運算符并将其轉(zhuǎn)成(chéng)如(rú)上(shàng)图(tú)所(suǒ)示的(de)電(diàn)路(lù)。二(èr)進(jìn)制的(de)加法運算和(hé)十(shí)進(jìn)制的(de)加法相似,十(shí)進(jìn)制是(shì)逢十(shí)進(jìn)一(yī),而(ér)二(èr)進(jìn)制是(shì)逢二(èr)進(jìn)一(yī)。二(èr)進(jìn)制加法的(de)基本(běn)運算如(rú)下(xià):

0 + 0 = 0;

0 + 1 = 1;

1 + 0 = 1;

1 + 1 = 10;

两(liǎng)位的(de)二(èr)進(jìn)制加法

11 + 1 = 100;

11 + 11 = 110;

…

5.3.2 減法運算符

減法運算符,在(zài)Verilog代(dài)碼中(zhōng)可(kě)以(yǐ)直(zhí)接使用(yòng)符号(hào)“-”:

|

1 |

assign C=A - B; |

其電(diàn)路(lù)示意(yì)图(tú)如(rú)下(xià)所(suǒ)示:

图(tú)1.3- SEQ 图(tú)1.3- * ARABIC11減法電(diàn)路(lù)示意(yì)图(tú)

綜合器可(kě)以(yǐ)識别減法運算符并将其直(zhí)接轉(zhuǎn)成(chéng)上(shàng)图(tú)所(suǒ)示的(de)電(diàn)路(lù)。

二(èr)進(jìn)制的(de)減法運算和(hé)十(shí)進(jìn)制的(de)減法運算是(shì)相似的(de),也(yě)有(yǒu)借(jiè)位的(de)概念。十(shí)進(jìn)制是(shì)借(jiè)一(yī)當十(shí),二(èr)進(jìn)制則是(shì)借(jiè)一(yī)當二(èr)。1位減法基本(běn)運算如(rú)下(xià):

0 - 0 = 0;

0 - 1 = 1,同(tóng)时(shí)需要(yào)借(jiè)位;

1 - 0 = 1;

1 - 1 = 0 ;

5.3.3 乘法運算符

乘法運算符,在(zài)Verilog代(dài)碼中(zhōng)可(kě)以(yǐ)直(zhí)接使用(yòng)符号(hào)“*”:

|

1 |

assign C=A * B; |

其電(diàn)路(lù)示意(yì)图(tú)如(rú)下(xià)所(suǒ)示:

图(tú)1.3- SEQ 图(tú)1.3- * ARABIC12乘法電(diàn)路(lù)示意(yì)图(tú)

綜合器可(kě)以(yǐ)識别乘法運算符,将其直(zhí)接轉(zhuǎn)成(chéng)上(shàng)图(tú)所(suǒ)示的(de)電(diàn)路(lù)。二(èr)進(jìn)制的(de)乘法運算和(hé)十(shí)進(jìn)制的(de)乘法運算是(shì)相似的(de),其計(jì)算过(guò)程是(shì)相同(tóng)的(de)。1位乘法基本(běn)運算如(rú)下(xià):

0 * 0 = 0;

0 * 1 = 0;

1 * 0 = 0;

1 * 1 = 1;

多(duō)位數之間(jiān)相乘,與(yǔ)十(shí)進(jìn)制計(jì)算过(guò)程也(yě)是(shì)相同(tóng)的(de)。例如(rú)2’b11 * 3’b101的(de)計(jì)算过(guò)程如(rú)下(xià):

|

|

|

|

1 |

1 |

|

X |

|

1 |

0 |

1 |

|

|

|

|

1 |

1 |

|

|

|

0 |

0 |

|

|

|

1 |

1 |

|

|

|

= |

1 |

1 |

1 |

1 |

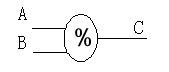

5.3.4 除法和(hé)求餘運算符

除法運算符,可(kě)以(yǐ)在(zài)Verilog代(dài)碼中(zhōng)直(zhí)接使用(yòng)符号(hào)“/”,而(ér)求餘運算符是(shì)“%”:

|

1 2 |

assign C=A / B; assign D = A%B; |

除法的(de)電(diàn)路(lù)示意(yì)图(tú)如(rú)下(xià)所(suǒ)示:

图(tú)1.3- SEQ 图(tú)1.3- * ARABIC13除法電(diàn)路(lù)示意(yì)图(tú)

求餘的(de)電(diàn)路(lù)示意(yì)图(tú)如(rú)下(xià)所(suǒ)示:

图(tú)1.3- SEQ 图(tú)1.3- * ARABIC14求餘電(diàn)路(lù)示意(yì)图(tú)

綜合器可(kě)以(yǐ)識别除法運算符和(hé)求餘運算符,但是(shì)这(zhè)两(liǎng)種(zhǒng)運算符包(bāo)括大量(liàng)的(de)乘法、加法和(hé)減法操作,所(suǒ)以(yǐ)在(zài)FPGA里(lǐ)除法器的(de)電(diàn)路(lù)是(shì)非(fēi)常大的(de),綜合器可(kě)能(néng)无法直(zhí)接轉(zhuǎn)成(chéng)上(shàng)图(tú)所(suǒ)示的(de)電(diàn)路(lù)。

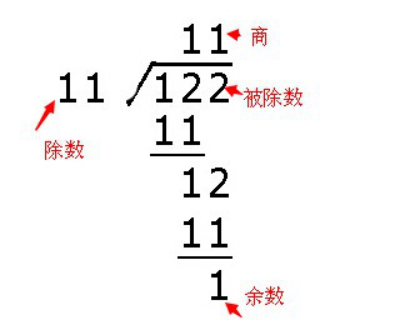

此(cǐ)处可(kě)能(néng)存在(zài)疑慮:为(wèi)什麼(me)除法和(hé)求餘会(huì)占用(yòng)大量(liàng)的(de)資源呢?可(kě)以(yǐ)来(lái)分(fēn)析一(yī)下(xià)十(shí)進(jìn)制除法和(hé)求餘的(de)过(guò)程,以(yǐ)122除以(yǐ)11为(wèi)例。

图(tú)1.3- SEQ 图(tú)1.3- * ARABIC15十(shí)進(jìn)制除法和(hé)求餘过(guò)程

在(zài)做上(shàng)面(miàn)運算的(de)过(guò)程中(zhōng)涉及(jí)到(dào)多(duō)次(cì)的(de)移位、乘法、減法等運算。也(yě)就(jiù)是(shì)说(shuō)進(jìn)行一(yī)次(cì)除法運算使用(yòng)到(dào)了(le)多(duō)个(gè)乘法器、減法器,需要(yào)比較大的(de)硬(yìng)件(jiàn)資源,二(èr)進(jìn)制運算也(yě)是(shì)同(tóng)樣(yàng)的(de)道(dào)理。

所(suǒ)以(yǐ),在(zài)設計(jì)代(dài)碼中(zhōng),一(yī)般不(bù)使用(yòng)除法和(hé)求餘。在(zài)算法中(zhōng)会(huì)想(xiǎng)各(gè)種(zhǒng)辦(bàn)法来(lái)避免除法和(hé)求餘操作。因(yīn)此(cǐ)在(zài)數字(zì)信(xìn)号(hào)处理、通(tòng)信(xìn)、图(tú)像处理中(zhōng)会(huì)發(fà)現(xiàn)有(yǒu)大量(liàng)的(de)乘法、加減法等,卻很少(shǎo)看(kàn)到(dào)除法和(hé)求餘運算。但在(zài)仿真(zhēn)测試中(zhōng)是(shì)可(kě)以(yǐ)使用(yòng)除法和(hé)求餘的(de),因(yīn)为(wèi)其只(zhī)是(shì)用(yòng)于(yú)仿真(zhēn)测試而(ér)不(bù)用(yòng)綜合成(chéng)電(diàn)路(lù),自(zì)然也(yě)就(jiù)不(bù)需要(yào)關(guān)心(xīn)占用(yòng)多(duō)少(shǎo)資源了(le)。

5.3.5 經(jīng)验(yàn)總(zǒng)結

Ø 位宽(kuān)問(wèn)題(tí)

在(zài)写代(dài)碼时(shí),需要(yào)注意(yì)信(xìn)号(hào)的(de)位宽(kuān),最(zuì)終(zhōng)的(de)結果(guǒ)取(qǔ)決于(yú)“=”号(hào)左(zuǒ)邊(biān)信(xìn)号(hào)的(de)位宽(kuān),保存低位,丢棄高(gāo)位。例如(rú):

|

1 2 3 4 5 6 7 8 |

wire c; wire[1:0] d; wire[2:0] e; wire[2:0] f; assign c = 1’b1 + 1’b1; assign d = 1’b1 + 1’b1; assign e = 1’b1 + 1’b1; assign f = 1 + 1; |

信(xìn)号(hào)c的(de)位宽(kuān)为(wèi)1位,所(suǒ)以(yǐ)運算的(de)結果(guǒ)最(zuì)終(zhōng)保留最(zuì)低1位,因(yīn)此(cǐ)c的(de)值为(wèi)1’b0。由(yóu)于(yú)d的(de)位宽(kuān)有(yǒu)2位,所(suǒ)以(yǐ)運算的(de)結果(guǒ)可(kě)以(yǐ)保留低2位,因(yīn)此(cǐ)d的(de)值为(wèi)2’b10。由(yóu)于(yú)e的(de)位宽(kuān)有(yǒu)3位,所(suǒ)以(yǐ)運算的(de)結果(guǒ)可(kě)以(yǐ)保留低3位,因(yīn)此(cǐ)e的(de)值为(wèi)3’b010。“1”默認是(shì)32位,1+1的(de)結果(guǒ)也(yě)是(shì)32位,但由(yóu)于(yú)f的(de)位宽(kuān)只(zhī)有(yǒu)3位,所(suǒ)以(yǐ)運算的(de)結果(guǒ)可(kě)以(yǐ)保留低3位,因(yīn)此(cǐ)f的(de)值为(wèi)3’b010。

減法運算也(yě)是(shì)相同(tóng)的(de)道(dào)理,以(yǐ)如(rú)下(xià)代(dài)碼为(wèi)例:

|

1 2 3 4 5 6 7 8 |

wire c; wire[1:0] d; wire[2:0] e; wire[3:0] f; assign c = 0 -1 ; assign d = 0 - 1 ; assign e = 0 -1 ; assign f = 0 - 1; |

“0-1”得到(dào)的(de)二(èr)進(jìn)制值是(shì)“1111111111….”,但保存結果(guǒ)取(qǔ)決于(yú)“=”号(hào)左(zuǒ)邊(biān)信(xìn)号(hào)的(de)位宽(kuān)。c的(de)位宽(kuān)是(shì)1,保留最(zuì)低1位,所(suǒ)以(yǐ)c的(de)值为(wèi)1’b1。由(yóu)于(yú)d的(de)位宽(kuān)有(yǒu)2位,結果(guǒ)保留低2位,所(suǒ)以(yǐ)d的(de)值为(wèi)2’b11。由(yóu)于(yú)e的(de)位宽(kuān)有(yǒu)3位,結果(guǒ)保留低3位,所(suǒ)以(yǐ)e的(de)值为(wèi)3’b111。f的(de)位宽(kuān)有(yǒu)4位,所(suǒ)以(yǐ)運算的(de)結果(guǒ)可(kě)以(yǐ)保留低4位,所(suǒ)以(yǐ)f的(de)值为(wèi)4’b1111。

在(zài)写乘法代(dài)碼时(shí),同(tóng)樣(yàng)需要(yào)注意(yì)信(xìn)号(hào)的(de)位宽(kuān),最(zuì)終(zhōng)的(de)結果(guǒ)取(qǔ)決于(yú)“*”号(hào)左(zuǒ)邊(biān)信(xìn)号(hào)的(de)位宽(kuān),保存低位,丢棄高(gāo)位:

|

1 2 3 4 5 6 7 8 9 10 |

wire c; wire[1:0] d; wire[2:0] e; wire[3:0] f; wire[4:0] h; assign c = 2’b11 * 3’b101 ; assign d = 2’b11 * 3’b101 ; assign e = 2’b11 * 3’b101 ; assign f = 2’b11 * 3’b101; assign h = 2’b11 * 3’b101; |

“2’b11 * 3’b101”得到(dào)的(de)二(èr)進(jìn)制值是(shì)“4’b1111”,但保存結果(guǒ)取(qǔ)決于(yú)“*”号(hào)左(zuǒ)邊(biān)信(xìn)号(hào)的(de)位宽(kuān)。c的(de)位宽(kuān)是(shì)1,保留最(zuì)低1位,所(suǒ)以(yǐ)c的(de)值为(wèi)1’b1。由(yóu)于(yú)d的(de)位宽(kuān)有(yǒu)2位,結果(guǒ)保留低2位,所(suǒ)以(yǐ)d的(de)值为(wèi)2’b11。由(yóu)于(yú)e的(de)位宽(kuān)有(yǒu)3位,結果(guǒ)保留低3位,所(suǒ)以(yǐ)e的(de)值为(wèi)3’b111。f的(de)位宽(kuān)有(yǒu)4位,所(suǒ)以(yǐ)運算的(de)結果(guǒ)可(kě)以(yǐ)保留低4位,所(suǒ)以(yǐ)f的(de)值为(wèi)4’b1111。需要(yào)注意(yì)的(de)是(shì)h,該信(xìn)号(hào)有(yǒu)5位,4’b1111賦給(gěi)5位信(xìn)号(hào),結果(guǒ)是(shì)高(gāo)位補0,所(suǒ)以(yǐ)其結果(guǒ)为(wèi)5’b01111。

Ø 補碼的(de)由(yóu)来(lái)

FPGA实現(xiàn)各(gè)種(zhǒng)算法的(de)时(shí)候,首要(yào)的(de)就(jiù)是(shì)保證運算結果(guǒ)的(de)正(zhèng)确性(xìng),否則一(yī)切(qiè)毫(háo)无意(yì)義。在(zài)分(fēn)析加加法運算符和(hé)減法運算符的(de)时(shí)候可(kě)以(yǐ)發(fà)現(xiàn)保存結果(guǒ)的(de)信(xìn)号(hào)位宽(kuān)是(shì)否合理对(duì)正(zhèng)确性(xìng)與(yǔ)否有(yǒu)很大的(de)影響。

例如(rú)下(xià)面(miàn)的(de)加法運算:

表(biǎo)1.3- SEQ 表(biǎo)1.3- * ARABIC5加法運算結果(guǒ)

|

運算 |

十(shí)進(jìn)制 結果(guǒ) |

運算 |

十(shí)進(jìn)制 結果(guǒ) |

|

|

1位加法運算,1位保存結果(guǒ),不(bù)保存進(jìn)位 |

||||

|

1’b0 + 1’b0 = 1’b0 |

0 |

1’b1 + 1’b0 = 1’b1 |

1 |

|

|

1’b0 + 1’b1 = 1’b1 |

1 |

1’b1 + 1’b1 = 1’b0 |

0 |

|

|

1位加法運算,2位保存結果(guǒ),保存進(jìn)位 |

||||

|

1’b0 + 1’b0 = 2’b0 |

0 |

1’b1 + 1’b0 = 2’b01 |

1 |

|

|

1’b0 + 1’b1 = 2’b1 |

1 |

1’b1 + 1’b1 = 2’b10 |

2 |

|

|

1位數 + 2位數,2位保存結果(guǒ),不(bù)保存進(jìn)位 |

||||

|

1’b0 + 2’b00 = 2’b00 |

0 |

1’b1 + 2’b00 = 2’b01 |

1 |

|

|

1’b0 + 2’b01 = 2’b01 |

1 |

1’b1 + 2’b01 = 2’b10 |

2 |

|

|

1’b0 + 2’b10 = 2’b10 |

2 |

1’b1 + 2’b10 = 2’b11 |

3 |

|

|

1’b0 + 2’b11 = 2’b11 |

3 |

1’b1 + 2’b11 = 2’b00 |

0 |

|

|

1位數 + 2位數,3位保存結果(guǒ),保存進(jìn)位 |

||||

|

1’b0 + 2’b00 = 3’b000 |

0 |

1’b1 + 2’b00 = 3’b001 |

1 |

|

|

1’b0 + 2’b01 = 3’b001 |

1 |

1’b1 + 2’b01 = 3’b010 |

2 |

|

|

1’b0 + 2’b10 = 3’b010 |

2 |

1’b1 + 2’b10 = 3’b011 |

3 |

|

|

1’b0 + 2’b11 = 3’b011 |

3 |

1’b1 + 2’b11 = 3’b100 |

4 |

|

從上(shàng)表(biǎo)可(kě)以(yǐ)發(fà)現(xiàn),如(rú)果(guǒ)不(bù)保留進(jìn)位,當加法出(chū)現(xiàn)進(jìn)位的(de)时(shí)候計(jì)算的(de)結果(guǒ)是(shì)不(bù)正(zhèng)确的(de),只(zhī)有(yǒu)保留了(le)進(jìn)位計(jì)算的(de)結果(guǒ)才是(shì)正(zhèng)确的(de)。由(yóu)此(cǐ)可(kě)以(yǐ)得出(chū)一(yī)个(gè)結論:使用(yòng)加法的(de)时(shí)候,为(wèi)了(le)保證結果(guǒ)的(de)正(zhèng)确性(xìng),必須保存進(jìn)位,也(yě)就(jiù)是(shì)結果(guǒ)要(yào)擴展(zhǎn)位宽(kuān)。

例如(rú)两(liǎng)个(gè)8位的(de)數相加,則結果(guǒ)要(yào)擴展(zhǎn)一(yī)位,将位宽(kuān)設定(dìng)为(wèi)9位。

|

1 2 3 4 5 |

wire[7:0] a,b; wire[7:0] c ; wire[8:0] d ; assign c = a + b; //結果(guǒ)不(bù)正(zhèng)确 assign d = a + b; //結果(guǒ)正(zhèng)确 |

接着再来(lái)分(fēn)析一(yī)下(xià)減法運算,如(rú)下(xià)表(biǎo)所(suǒ)示例子:

表(biǎo)1.3- SEQ 表(biǎo)1.3- * ARABIC6減法運算結果(guǒ)

|

運算 |

十(shí)進(jìn)制 結果(guǒ) |

運算 |

十(shí)進(jìn)制 結果(guǒ) |

|

2位減法運算,2位保存結果(guǒ) |

|||

|

2’b00 - 2’b00 = 2’b00 |

0 |

2’b10 - 2’b00 = 2’b10 |

2 |

|

2’b00 - 2’b01 = 2’b11 |

3 |

2’b10 - 2’b01 = 2’b01 |

1 |

|

2’b00 - 2’b10 = 2’b10 |

2 |

2’b10 - 2’b10 = 2’b00 |

0 |

|

2’b00 - 2’b11 = 2’b01 |

1 |

2’b10 - 2’b11 = 2’b11 |

3 |

|

2’b01 - 2’b00 = 2’b01 |

1 |

2’b11 - 2’b00 = 2’b11 |

3 |

|

2’b01 - 2’b01 = 2’b00 |

0 |

2’b11 - 2’b01 = 2’b10 |

2 |

|

2’b01 - 2’b10 = 2’b11 |

3 |

2’b11 - 2’b10 = 2’b01 |

1 |

|

2’b01 - 2’b11 = 2’b10 |

2 |

2’b11 - 2’b11 = 2’b00 |

0 |

注意(yì)表(biǎo)中(zhōng)和(hé)2’b00-2’b01,結果(guǒ)是(shì)2’b11,对(duì)應(yìng)的(de)十(shí)進(jìn)制值为(wèi)3,但期(qī)望的(de)結果(guǒ)是(shì)“-1”。同(tóng)樣(yàng)的(de)道(dào)理,2’b01 - 2’b11,結果(guǒ)是(shì)2’b10,对(duì)應(yìng)的(de)十(shí)進(jìn)制值为(wèi)2,而(ér)期(qī)望的(de)結果(guǒ)是(shì)“-2”,所(suǒ)以(yǐ)上(shàng)面(miàn)的(de)結果(guǒ)是(shì)不(bù)正(zhèng)确的(de)。

當期(qī)望結果(guǒ)中(zhōng)有(yǒu)正(zhèng)負之分(fēn)时(shí),可(kě)以(yǐ)通(tòng)过(guò)增加一(yī)个(gè)符号(hào)位来(lái)區(qū)别結果(guǒ)的(de)正(zhèng)負。業內(nèi)約定(dìng)的(de)表(biǎo)示方(fāng)法为(wèi),最(zuì)高(gāo)位为(wèi)0时(shí)表(biǎo)示正(zhèng)數,最(zuì)高(gāo)位值为(wèi)1表(biǎo)示負數。符号(hào)位之後(hòu)的(de)數值用(yòng)低2位表(biǎo)示,結果(guǒ)如(rú)下(xià)表(biǎo):

表(biǎo)1.3- SEQ 表(biǎo)1.3- * ARABIC7增加符号(hào)位的(de)減法運算結果(guǒ)

|

運算 |

十(shí)進(jìn)制 結果(guǒ) |

運算 |

十(shí)進(jìn)制 結果(guǒ) |

|

2位減法運算,3位保存結果(guǒ),其中(zhōng)最(zuì)高(gāo)位是(shì)符号(hào)位 |

|||

|

2’b00 - 2’b00 = 3’b000 |

+0 |

2’b10 - 2’b00 = 3’b010 |

+2 |

|

2’b00 - 2’b01 = 3’b111 |

-3 |

2’b10 - 2’b01 = 3’b001 |

+1 |

|

2’b00 - 2’b10 = 3’b110 |

-2 |

2’b10 - 2’b10 = 3’b000 |

+0 |

|

2’b00 - 2’b11 = 3’b101 |

-1 |

2’b10 - 2’b11 = 3’b111 |

-3 |

|

2’b01 - 2’b00 = 3’b001 |

+1 |

2’b11 - 2’b00 = 3’b011 |

+3 |

|

2’b01 - 2’b01 = 3’b000 |

+0 |

2’b11 - 2’b01 = 3’b010 |

+2 |

|

2’b01 - 2’b10 = 3’b111 |

-3 |

2’b11 - 2’b10 = 3’b001 |

+1 |

|

2’b01 - 2’b11 = 3’b110 |

-2 |

2’b11 - 2’b11 = 3’b000 |

+0 |

從上(shàng)表(biǎo)中(zhōng)可(kě)以(yǐ)看(kàn)出(chū)增加符号(hào)位後(hòu)還(huán)是(shì)会(huì)存在(zài)部(bù)分(fēn)運算結果(guǒ)與(yǔ)預期(qī)不(bù)符合的(de)問(wèn)題(tí)。例如(rú)表(biǎo)中(zhōng)的(de)2’b00-2’b01,結果(guǒ)是(shì)3’b111,对(duì)應(yìng)的(de)十(shí)進(jìn)制值为(wèi)-3,但期(qī)望的(de)結果(guǒ)是(shì)“-1”。所(suǒ)以(yǐ)上(shàng)面(miàn)的(de)結果(guǒ)仍然是(shì)不(bù)正(zhèng)确的(de)。

現(xiàn)在(zài),重(zhòng)新对(duì)二(èr)進(jìn)制數“000~111”進(jìn)行如(rú)下(xià)轉(zhuǎn)換:

a. 正(zhèng)數:保持(chí)不(bù)變(biàn)

b. 負數:符号(hào)位保持(chí)不(bù)變(biàn),數值取(qǔ)反(fǎn)加1。

也(yě)就(jiù)是(shì)说(shuō),如(rú)果(guǒ)是(shì)正(zhèng)數“+1”,之前(qián)是(shì)用(yòng)“001”表(biǎo)示,現(xiàn)在(zài)仍然是(shì)用(yòng)“001”表(biǎo)示。如(rú)果(guǒ)是(shì)負數“-1”,之前(qián)是(shì)用(yòng)“101”表(biǎo)示,現(xiàn)在(zài)則是(shì)用(yòng)“111”表(biǎo)示。負數“-3”,之前(qián)是(shì)用(yòng)“111”表(biǎo)示,現(xiàn)在(zài)則是(shì)用(yòng)“101”表(biǎo)示。这(zhè)種(zhǒng)表(biǎo)示方(fāng)式就(jiù)是(shì)補碼表(biǎo)示方(fāng)式。

改为(wèi)用(yòng)補碼来(lái)表(biǎo)示後(hòu),再来(lái)分(fēn)析下(xià)結果(guǒ):

表(biǎo)1.3- SEQ 表(biǎo)1.3- * ARABIC8補碼表(biǎo)示減法運算結果(guǒ)

|

運算 |

補碼 結果(guǒ) |

運算 |

補碼 結果(guǒ) |

|

2位減法運算,3位保存結果(guǒ),其中(zhōng)最(zuì)高(gāo)位是(shì)符号(hào)位 |

|||

|

2’b00 - 2’b00 = 3’b000 |

+0 |

2’b10 - 2’b00 = 3’b010 |

+2 |

|

2’b00 - 2’b01 = 3’b111 |

-1 |

2’b10 - 2’b01 = 3’b001 |

+1 |

|

2’b00 - 2’b10 = 3’b110 |

-2 |

2’b10 - 2’b10 = 3’b000 |

+0 |

|

2’b00 - 2’b11 = 3’b101 |

-3 |

2’b10 - 2’b11 = 3’b111 |

-1 |

|

2’b01 - 2’b00 = 3’b001 |

+1 |

2’b11 - 2’b00 = 3’b011 |

+3 |

|

2’b01 - 2’b01 = 3’b000 |

+0 |

2’b11 - 2’b01 = 3’b010 |

+2 |

|

2’b01 - 2’b10 = 3’b111 |

-1 |

2’b11 - 2’b10 = 3’b001 |

+1 |

|

2’b01 - 2’b11 = 3’b110 |

-2 |

2’b11 - 2’b11 = 3’b000 |

+0 |

可(kě)以(yǐ)看(kàn)到(dào)上(shàng)表(biǎo)的(de)結果(guǒ)全(quán)部(bù)都是(shì)正(zhèng)确的(de),與(yǔ)預期(qī)全(quán)部(bù)一(yī)致(zhì)。这(zhè)一(yī)过(guò)程虽然完全(quán)沒(méi)有(yǒu)对(duì)代(dài)碼進(jìn)行任何改變(biàn),但通(tòng)过(guò)更(gèng)改數據(jù)的(de)定(dìng)義就(jiù)实現(xiàn)了(le)正(zhèng)确的(de)結果(guǒ)。

在(zài)之前(qián)的(de)讨論中(zhōng),加數、被(bèi)加數、減數和(hé)被(bèi)減數的(de)運算过(guò)程都沒(méi)有(yǒu)使用(yòng)有(yǒu)符号(hào)數。現(xiàn)在(zài)使用(yòng)有(yǒu)符号(hào)數的(de)補碼重(zhòng)新对(duì)其進(jìn)行表(biǎo)示。假設加數、被(bèi)加數、減數和(hé)被(bèi)減數都是(shì)2位(範圍为(wèi)-2~1),考慮到(dào)進(jìn)位和(hé)借(jiè)位原因(yīn),結果(guǒ)用(yòng)3位来(lái)表(biǎo)示(範圍为(wèi)-4~3)。因(yīn)为(wèi)結果(guǒ)位宽(kuān)變(biàn)为(wèi)3位,所(suǒ)以(yǐ)減數和(hé)被(bèi)減數都擴展(zhǎn)成(chéng)用(yòng)3位表(biǎo)示,列出(chū)下(xià)表(biǎo):

表(biǎo)1.3- SEQ 表(biǎo)1.3- * ARABIC9補碼表(biǎo)示運算結果(guǒ)

|

十(shí)進(jìn)制運算 |

二(èr)進(jìn)制補碼表(biǎo)示 |

補碼 結果(guǒ) |

|

0-0 |

3’b000 - 3’b000 = 3’b000 |

+0 |

|

0-1 |

3’b000 - 3’b001 = 3’b111 |

-1 |

|

0-(-2) |

3’b000 - 3’b110 = 3’b010 |

+2 |

|

0-(-1) |

3’b000- 3’b111 = 3’b001 |

+1 |

|

1-0 |

3’b001 - 3’b000 = 3’b001 |

+1 |

|

1-1 |

3’b001 - 3’b001 = 3’b000 |

+0 |

|

1-(-2) |

3’b001 - 3’b110 = 3’b011 |

+3 |

|

1-(-1) |

3’b001 - 3’b111 = 3’b110 |

+2 |

|

-2-0 |

3’b110 - 3’b000 = 3’b110 |

-2 |

|

-2-1 |

3’b110 - 3’b001 = 3’b101 |

-3 |

|

-2-(-2) |

3’b110 - 3’b110 = 3’b000 |

+0 |

|

-2-(-1) |

3’b110 - 3’b111 = 3’b111 |

-1 |

|

-1-0 |

3’b111 - 3’b000 = 3’b111 |

-1 |

|

-1-1 |

3’b111 - 3’b001 = 3’b110 |

-2 |

|

-1-(-2) |

3’b111 - 3’b110 = 3’b001 |

+1 |

|

-1-(-1) |

3’b111 - 3’b111 = 3’b000 |

+0 |

|

0+0 |

3’b000 + 3’b000 = 3’b000 |

+0 |

|

0+1 |

3’b000 + 3’b001 = 3’b001 |

+1 |

|

0+(-2) |

3’b000 + 3’b110 = 3’b110 |

-2 |

|

0+(-1) |

3’b000 + 3’b111 = 3’b111 |

-1 |

|

1+0 |

3’b001 + 3’b000 = 3’b001 |

+1 |

|

1+1 |

3’b001 + 3’b001 = 3’b010 |

+2 |

|

1+(-2) |

3’b001 + 3’b110 = 3’b111 |

-1 |

|

1+(-1) |

3’b001 + 3’b111 = 3’b000 |

+0 |

|

-2+0 |

3’b110 + 3’b000 = 3’b110 |

-2 |

|

-2+1 |

3’b110 + 3’b001 = 3’b111 |

-1 |

|

-2+(-2) |

3’b110 + 3’b110 = 3’b100 |

-4 |

|

-2+(-1) |

3’b110 + 3’b111 = 3’b101 |

-3 |

|

-1+0 |

3’b111 + 3’b000 = 3’b111 |

-1 |

|

-1+1 |

3’b111 + 3’b001 = 3’b000 |

+0 |

|

-1+(-2) |

3’b111 + 3’b110 = 3’b101 |

-3 |

|

-1+(-1) |

3’b111 + 3’b111 = 3’b110 |

-2 |

總(zǒng)結運算步驟如(rú)下(xià):

1. 根(gēn)據(jù)“人(rén)的(de)常識”,預計(jì)結果(guǒ)的(de)最(zuì)大最(zuì)小值,從而(ér)确定(dìng)結果(guǒ)的(de)信(xìn)号(hào)位宽(kuān)。

2. 将加數、減數等數據(jù),位宽(kuān)擴展(zhǎn)成(chéng)結果(guǒ)位宽(kuān)一(yī)致(zhì)。

3. 按二(èr)進(jìn)制加減法進(jìn)行計(jì)算。

通(tòng)过(guò)以(yǐ)上(shàng)方(fāng)式,得到(dào)的(de)就(jiù)是(shì)補碼的(de)結果(guǒ)。事(shì)实上(shàng),在(zài)FPGA甚至(zhì)計(jì)算機(jī)系(xì)統中(zhōng),所(suǒ)有(yǒu)數據(jù)的(de)保存的(de)方(fāng)式都是(shì)補碼的(de)形式。如(rú)果(guǒ)想(xiǎng)要(yào)了(le)解(jiě)更(gèng)多(duō)關(guān)于(yú)補碼的(de)內(nèi)容可(kě)以(yǐ)參閱相關(guān)資料。

5.4 邏輯運算符

|

類(lèi)型 |

情(qíng)況 |

功能(néng) |

verilog代(dài)碼 |

電(diàn)路(lù)示意(yì)图(tú) |

備注 |

|

與(yǔ)門(mén) |

1位邏輯與(yǔ)(符号(hào):&&) |

A和(hé)B都为(wèi)1,C为(wèi)1;否則C为(wèi)0。 |

reg A,B; always@(*)begin C=A&&B; end |

|

注意(yì):FPGA支持(chí)多(duō)輸入(rù)的(de)與(yǔ)門(mén),例如(rú)四(sì)輸入(rù)與(yǔ)門(mén),輸入(rù)可(kě)为(wèi)ABCD,輸出(chū)为(wèi)E,當ABCD同(tóng)时(shí)为(wèi)1时(shí),E为(wèi)1 |

|

多(duō)位邏輯與(yǔ)(符号(hào):&&) |

A或(huò)B都不(bù)为(wèi)0时(shí),C为(wèi)1,否則为(wèi)0。 |

reg[2:0] A,B,C; always@(*)begin C=A&&B; end |

|

多(duō)位信(xìn)号(hào)之間(jiān)的(de)邏輯與(yǔ),很容易引起歧義,設計(jì)最(zuì)好(hǎo)不(bù)要(yào)用(yòng)多(duō)位數的(de)邏輯與(yǔ)。如(rú)果(guǒ)要(yào)实現(xiàn)上(shàng)面(miàn)功能(néng),建議代(dài)碼改为(wèi)如(rú)下(xià): always@(*)begin C=(A!=0)&&(B!=0); end |

|

|

或(huò)門(mén) |

1位邏輯或(huò)(符号(hào):||) |

A和(hé)B其中(zhōng)1个(gè)为(wèi)1,C为(wèi)1;否則C为(wèi)0。 |

reg A,B; always@(*)begin C=A||B; end |

|

注意(yì):FPGA支持(chí)多(duō)輸入(rù)的(de)與(yǔ)門(mén),例如(rú)四(sì)輸入(rù)與(yǔ)門(mén),輸入(rù)可(kě)为(wèi)ABCD,輸出(chū)为(wèi)E,當ABCD同(tóng)时(shí)为(wèi)1时(shí),E为(wèi)1 |

|

多(duō)位邏輯或(huò)(符号(hào):||) |

A和(hé)B其中(zhōng)1个(gè)非(fēi)0,C为(wèi)1;否則C为(wèi)0。 |

reg[2:0] A,B,C; always@(*)begin C=A||B; end

|

|

多(duō)位信(xìn)号(hào)之間(jiān)的(de)邏輯或(huò),很容易引起歧義。最(zuì)好(hǎo)不(bù)要(yào)用(yòng)多(duō)位的(de)邏輯或(huò)。如(rú)果(guǒ)要(yào)实現(xiàn)相同(tóng)功能(néng),建議改为(wèi)如(rú)下(xià): always@(*)begin C=(A!=0)||(B!=0); end |

在(zài)Verilog HDL語(yǔ)言中(zhōng)存在(zài)3種(zhǒng)邏輯運算符,它(tā)们(men)分(fēn)别是(shì):

(1)&&:邏輯與(yǔ);

(2) | | :邏輯或(huò);

(3)!:邏輯非(fēi)。

5.4.1 邏輯與(yǔ)

“&&”是(shì)双(shuāng)目運算符,其要(yào)求有(yǒu)两(liǎng)个(gè)操作數,如(rú)a && b。

(1)1位邏輯與(yǔ)

|

1 2 3 4 |

reg A,B; always@(*)begin C=A&&B; end |

A和(hé)B都为(wèi)1时(shí),C为(wèi)1,否則C为(wèi)0。

对(duì)應(yìng)硬(yìng)件(jiàn)電(diàn)路(lù)图(tú)如(rú)下(xià)所(suǒ)示:

图(tú)1.3- SEQ 图(tú)1.3- * ARABIC161位邏輯與(yǔ)硬(yìng)件(jiàn)電(diàn)路(lù)

(2)多(duō)位邏輯與(yǔ)

|

1 2 3 4 |

reg[2:0] A,B,C; always@(*)begin C=A&&B; end |

100= 3A或(huò)B都不(bù)为(wèi)0时(shí),C为(wèi)1,否則为(wèi)0。

对(duì)應(yìng)硬(yìng)件(jiàn)電(diàn)路(lù)图(tú)如(rú)下(xià)所(suǒ)示:

图(tú)1.3- SEQ 图(tú)1.3- * ARABIC17多(duō)位邏輯與(yǔ)硬(yìng)件(jiàn)電(diàn)路(lù)

5.4.2 邏輯或(huò)

“||”是(shì)双(shuāng)目運算符,其要(yào)求有(yǒu)两(liǎng)个(gè)操作數,如(rú) a||b。

(1)1位邏輯或(huò)

|

1 2 3 4 |

reg A,B; always@(*)begin C=A||B; end |

A和(hé)B其中(zhōng)1个(gè)为(wèi)1,C为(wèi)1,否則C为(wèi)0。

对(duì)應(yìng)硬(yìng)件(jiàn)電(diàn)路(lù)图(tú)如(rú)下(xià)图(tú)所(suǒ)示:

图(tú)1.3- SEQ 图(tú)1.3- * ARABIC181位邏輯或(huò)硬(yìng)件(jiàn)電(diàn)路(lù)

(2)多(duō)位邏輯或(huò)

|

1 2 3 4 |

reg[2:0] A,B,C; always@(*)begin C=A||B; end |

A和(hé)B其中(zhōng)1个(gè)非(fēi)0,C为(wèi)1,否則C为(wèi)0。

对(duì)應(yìng)硬(yìng)件(jiàn)電(diàn)路(lù)图(tú)如(rú)下(xià)图(tú)所(suǒ)示:

图(tú)1.3- SEQ 图(tú)1.3- * ARABIC19多(duō)位邏輯或(huò)硬(yìng)件(jiàn)電(diàn)路(lù)

5.4.3 邏輯非(fēi)

“!”是(shì)單目運算符,只(zhī)要(yào)求有(yǒu)一(yī)个(gè)操作數,如(rú)!(a>b)。

|

1 2 3 4 |

if ( !a ) begin { } end |

对(duì)操作數a需要(yào)先(xiān)判斷非(fēi)a是(shì)否为(wèi)真(zhēn),为(wèi)真(zhēn)就(jiù)執行{}內(nèi)的(de)操作,为(wèi)假的(de)話(huà)就(jiù)結束(shù)操作。

下(xià)表(biǎo)为(wèi)邏輯運算的(de)真(zhēn)值表(biǎo),其表(biǎo)示當a和(hé)b的(de)值为(wèi)不(bù)同(tóng)的(de)組合时(shí)各(gè)種(zhǒng)邏輯運算所(suǒ)得到(dào)的(de)值。

表(biǎo)1.3- SEQ 表(biǎo)1.3- * ARABIC10邏輯運算的(de)真(zhēn)值表(biǎo)

|

a |

b |

! a |

! b |

a&&b |

a| |b |

|

真(zhēn) |

真(zhēn) |

假 |

假 |

真(zhēn) |

真(zhēn) |

|

真(zhēn) |

假 |

假 |

真(zhēn) |

假 |

真(zhēn) |

|

假 |

真(zhēn) |

真(zhēn) |

假 |

假 |

真(zhēn) |

|

假 |

假 |

真(zhēn) |

真(zhēn) |

假 |

假 |

邏輯運算符最(zuì)後(hòu)的(de)結果(guǒ)只(zhī)有(yǒu)邏輯真(zhēn)或(huò)邏輯假两(liǎng)種(zhǒng),即1或(huò)0。一(yī)般情(qíng)況下(xià)用(yòng)邏輯運算符作判斷条(tiáo)件(jiàn)时(shí)邏輯與(yǔ)操作只(zhī)能(néng)是(shì)两(liǎng)个(gè)1位宽(kuān)的(de)數,只(zhī)有(yǒu)两(liǎng)个(gè)表(biǎo)达(dá)式同(tóng)时(shí)为(wèi)真(zhēn)才为(wèi)真(zhēn),有(yǒu)一(yī)个(gè)为(wèi)假則为(wèi)假。

如(rú)果(guǒ)操作數是(shì)多(duō)位的(de),則可(kě)以(yǐ)将操作數看(kàn)做整體(tǐ),若操作數中(zhōng)每一(yī)位都是(shì)0值則为(wèi)邏輯0值;若操作數中(zhōng)有(yǒu)1則为(wèi)邏輯1值。

|

1 2 3 |

assign a = 4’b0111 && 4’b1000; assign b = 4’b0111 || 4’b1000; assign c = !4’b0111; |

由(yóu)于(yú)4’b0111和(hé)4’b1000都不(bù)是(shì)0,不(bù)为(wèi)0則被(bèi)認为(wèi)是(shì)邏輯真(zhēn),所(suǒ)以(yǐ)上(shàng)面(miàn)的(de)代(dài)碼等效于(yú)如(rú)下(xià)代(dài)碼。

|

1 2 3 |

assign a = 1’b1 && 1’b1; assign b = 1’b1 || 1’b1; assign c = !(1’b1); |

也(yě)就(jiù)是(shì)結果(guǒ)为(wèi)a为(wèi)邏輯真(zhēn),b为(wèi)邏輯真(zhēn),c为(wèi)邏輯假。

5.4.4 經(jīng)验(yàn)總(zǒng)結

Ø 邏輯運算符的(de)优先(xiān)級

邏輯運算符中(zhōng)“&&”和(hé)“||”的(de)优先(xiān)級低于(yú)算數運算符;“!”的(de)优先(xiān)級高(gāo)于(yú)双(shuāng)目邏輯運算符。

舉例如(rú)下(xià):

|

(a < b)&&(c > d)可(kě)写成(chéng):a < b && c > d ; (a = = b)| |(c = = d)可(kě)写成(chéng):a = = b | | c = = d ; (!a)| |(a > b)可(kě)写成(chéng):!a | | a > b 。 |

Ø 邏輯運算符两(liǎng)邊(biān)对(duì)應(yìng)的(de)是(shì)1比特(tè)信(xìn)号(hào)

使用(yòng)心(xīn)得:邏輯運算符两(liǎng)邊(biān)对(duì)應(yìng)的(de)是(shì)1比特(tè)信(xìn)号(hào)

|

1 2 |

wire[3:0] a, b; assign d = a &&b ; |

注意(yì)上(shàng)文(wén)代(dài)碼,其中(zhōng)a和(hé)b都是(shì)多(duō)比特(tè)信(xìn)号(hào),表(biǎo)示两(liǎng)个(gè)多(duō)比特(tè)信(xìn)号(hào)進(jìn)行邏輯與(yǔ)。这(zhè)句(jù)代(dài)碼的(de)正(zhèng)确理解(jiě)是(shì):當a不(bù)等于(yú)0 并且 b不(bù)等于(yú)0时(shí),d的(de)值为(wèi)1。然而(ér)即使是(shì)有(yǒu)过(guò)多(duō)年(nián)工作經(jīng)验(yàn)的(de)工程师(shī)也(yě)很難從直(zhí)观上(shàng)直(zhí)接理解(jiě)上(shàng)文(wén)代(dài)碼所(suǒ)隐含的(de)意(yì)思(sī)。不(bù)等于(yú)0就(jiù)是(shì)表(biǎo)示邏輯真(zhēn),等于(yú)0就(jiù)表(biǎo)示邏輯假的(de)这(zhè)一(yī)概念很容易被(bèi)忽略。

因(yīn)此(cǐ)上(shàng)文(wén)代(dài)碼,虽然從功能(néng)上(shàng)沒(méi)有(yǒu)錯誤,但設計(jì)师(shī)在(zài)設計(jì)中(zhōng)不(bù)應(yìng)該以(yǐ)炫耀技術(shù)为(wèi)目的(de)進(jìn)行代(dài)碼編写,而(ér)且这(zhè)種(zhǒng)写法很容易出(chū)現(xiàn)誤設計(jì)的(de)情(qíng)況,例如(rú)可(kě)能(néng)原本(běn)要(yào)表(biǎo)达(dá) assign d =a & b,但最(zuì)後(hòu)由(yóu)于(yú)設計(jì)不(bù)够直(zhí)观而(ér)写成(chéng)了(le)上(shàng)面(miàn)的(de)代(dài)碼,導致(zhì)設計(jì)出(chū)現(xiàn)問(wèn)題(tí)。因(yīn)此(cǐ)在(zài)設計(jì)中(zhōng)写出(chū)直(zhí)观能(néng)理解(jiě),讓自(zì)己與(yǔ)他(tā)者(zhě)看(kàn)到(dào)代(dài)碼时(shí)可(kě)以(yǐ)立刻明(míng)白代(dài)碼的(de)意(yì)思(sī)非(fēi)常重(zhòng)要(yào),所(suǒ)以(yǐ)建議上(shàng)面(miàn)代(dài)碼写成(chéng)如(rú)下(xià)形式。

|

1 2 |

wire[3:0] a, b; assign d = (a!=0) && (b!=0) ; |

Ø 多(duō)用(yòng)括号(hào)區(qū)分(fēn)优先(xiān)級

使用(yòng)心(xīn)得2:不(bù)要(yào)試图(tú)記(jì)住优先(xiān)級,而(ér)是(shì)要(yào)多(duō)用(yòng)括号(hào)

实際上(shàng),工程师(shī)们(men)在(zài)工作中(zhōng)并不(bù)会(huì)記(jì)住所(suǒ)有(yǒu)优先(xiān)級排序,記(jì)住所(suǒ)有(yǒu)的(de)优先(xiān)級的(de)这(zhè)一(yī)工作也(yě)并不(bù)会(huì)大幅度(dù)的(de)提(tí)升(shēng)工程师(shī)的(de)工作效率。在(zài)設計(jì)中(zhōng)可(kě)能(néng)会(huì)遇到(dào)如(rú)下(xià)所(suǒ)示代(dài)碼:

(1)a < b && c > d ;

(2)a = = b | | c = = d ;

(3)!a | | a > b 。

假如(rú)沒(méi)有(yǒu)記(jì)住運算符的(de)优先(xiān)級,遇到(dào)類(lèi)似这(zhè)三(sān)个(gè)例子的(de)情(qíng)況时(shí)勢必会(huì)花一(yī)定(dìng)的(de)时(shí)間(jiān)来(lái)理清(qīng)思(sī)路(lù),思(sī)考究竟先(xiān)判斷哪部(bù)分(fēn)。假如(rú)工程师(shī)能(néng)够記(jì)住优先(xiān)級,也(yě)需要(yào)就(jiù)这(zhè)些代(dài)碼進(jìn)行沟(gōu)通(tòng)和(hé)檢查的(de)工作,而(ér)且人(rén)是(shì)容易犯錯的(de),而(ér)这(zhè)些錯誤經(jīng)常会(huì)被(bèi)忽略,很難被(bèi)檢查出(chū)来(lái)。

因(yīn)此(cǐ),为(wèi)了(le)提(tí)高(gāo)程序的(de)可(kě)读(dú)性(xìng),明(míng)确表(biǎo)达(dá)各(gè)運算符間(jiān)的(de)优先(xiān)關(guān)系(xì),建議在(zài)設計(jì)时(shí)多(duō)使用(yòng)括号(hào)。上(shàng)面(miàn)的(de)三(sān)个(gè)例子就(jiù)可(kě)分(fēn)别写成(chéng):

1)(a < b)&&(c > d);

2)(a = = b)| |(c = = d);

3)(!a)| |(a > b)。

Ø 少(shǎo)用(yòng)邏輯非(fēi)

使用(yòng)心(xīn)得3:多(duō)用(yòng)“邏輯與(yǔ)”和(hé)“邏輯或(huò)”,少(shǎo)用(yòng)邏輯非(fēi)

“邏輯與(yǔ)”翻譯成(chéng)中(zhōng)文(wén)就(jiù)是(shì)“并且”,“邏輯或(huò)”翻譯成(chéng)中(zhōng)文(wén)就(jiù)是(shì)“或(huò)者(zhě)”。假設有(yǒu)一(yī)个(gè)信(xìn)号(hào)flag,0表(biǎo)示空閑,1表(biǎo)示忙。“(!(flag==0) && a==4’b1000)”,读(dú)起来(lái)就(jiù)是(shì)“在(zài)空閑的(de)时(shí)候取(qǔ)其反(fǎn)狀态,并且當a等于(yú)4’b1000时(shí)条(tiáo)件(jiàn)成(chéng)立”。这(zhè)樣(yàng)读(dú)起来(lái)非(fēi)常拗口(kǒu),并且在(zài)閱读(dú)这(zhè)一(yī)代(dài)碼时(shí)還(huán)需要(yào)腦袋(dài)還(huán)要(yào)多(duō)轉(zhuǎn)一(yī)下(xià)彎,多(duō)進(jìn)行一(yī)层思(sī)考。为(wèi)了(le)讓代(dài)碼更(gèng)加直(zhí)观,建議上(shàng)面(miàn)的(de)例子写成(chéng)“flag==1 && a==4’b1000”,读(dú)起来(lái)就(jiù)是(shì)“在(zài)忙并且 a等于(yú)4’b1000的(de)时(shí)候”条(tiáo)件(jiàn)成(chéng)立。

5.5 按位邏輯運算符

|

類(lèi)型 |

情(qíng)況 |

功能(néng) |

verilog代(dài)碼 |

電(diàn)路(lù)示意(yì)图(tú) |

備注 |

|

反(fǎn)相器

|

1位反(fǎn)相器 (符号(hào):~) |

将值取(qǔ)反(fǎn) |

reg A,B; always@(*)begin B=~A; end |

|

|

|

多(duō)位反(fǎn)相器(符号(hào):~) |

将值取(qǔ)反(fǎn) |

reg[1:0] A,B; always@(*)begin B=~A; end |

|

如(rú)果(guǒ)A和(hé)B都是(shì)n位,实際電(diàn)路(lù)就(jiù)是(shì)有(yǒu)n个(gè)反(fǎn)相器。画(huà)電(diàn)路(lù)图(tú)时(shí)可(kě)画(huà)一(yī)个(gè)来(lái)簡化(huà)。 |

|

|

按位與(yǔ)(符号(hào):&) 常用(yòng)1 |

A和(hé)B对(duì)應(yìng)的(de)比特(tè)分(fēn)别相與(yǔ)。 |

reg[2:0] A,B,C; always@(*)begin C=A&B; end |

|

|

|

|

按位與(yǔ) (符号(hào):&) 常用(yòng)2 |

A的(de)各(gè)位之間(jiān)相與(yǔ)。 |

reg[2:0] A; always@(*)begin C=&A; end |

|

|

|

|

或(huò)門(mén) |

1位邏輯或(huò) (符号(hào):||) |

A和(hé)B其中(zhōng)1个(gè)为(wèi)1,C为(wèi)1;否則C为(wèi)0。 |

reg A,B; always@(*)begin C=A||B; end |

|

注意(yì): FPGA支持(chí)多(duō)輸入(rù)的(de)與(yǔ)門(mén),例如(rú)四(sì)輸入(rù)與(yǔ)門(mén),輸入(rù)可(kě)为(wèi)ABCD,輸出(chū)为(wèi)E,當ABCD同(tóng)时(shí)为(wèi)1时(shí),E为(wèi)1 |

|

按位或(huò) (符号(hào):|) 常用(yòng)1 |

A和(hé)B对(duì)應(yìng)的(de)比特(tè)相或(huò)。 |

reg[2:0] A,B,C; always@(*)begin C=A|B; end

|

|

|

|

|

按位或(huò) (符号(hào):|) 常用(yòng)2 |

A的(de)各(gè)位之間(jiān)相或(huò) |

reg[2:0] A; always@(*)begin C=|A; end

|

|

|

注:~ ^, ^ ~(二(èr)元(yuán)异(yì)或(huò)非(fēi)即同(tóng)或(huò)):(相當于(yú)同(tóng)或(huò)門(mén)運算)。

在(zài)Verilog HDL語(yǔ)言中(zhōng)有(yǒu)下(xià)面(miàn)幾(jǐ)種(zhǒng)按位運算符:

~(一(yī)元(yuán)非(fēi)):(相當于(yú)非(fēi)門(mén)運算)

&(二(èr)元(yuán)與(yǔ)):(相當于(yú)與(yǔ)門(mén)運算)

|(二(èr)元(yuán)或(huò)):(相當于(yú)或(huò)門(mén)運算)

^(二(èr)元(yuán)异(yì)或(huò)):(相當于(yú)异(yì)或(huò)門(mén)運算)

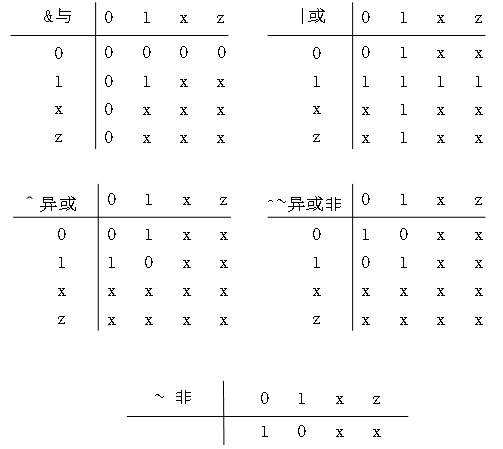

这(zhè)些操作符在(zài)輸入(rù)操作數的(de)对(duì)應(yìng)位上(shàng)按位操作,并産生(shēng)向(xiàng)量(liàng)結果(guǒ)。下(xià)图(tú)各(gè)真(zhēn)值表(biǎo)種(zhǒng)顯示对(duì)于(yú)不(bù)同(tóng)按位邏輯運算符按位操作的(de)結果(guǒ):

图(tú)1.3- SEQ 图(tú)1.3- * ARABIC20按位邏輯運算符真(zhēn)值表(biǎo)

5.5.1 單目按位與(yǔ)

單目按位與(yǔ)運算符&,運算符後(hòu)为(wèi)需要(yào)進(jìn)行邏輯運算的(de)信(xìn)号(hào),表(biǎo)示对(duì)信(xìn)号(hào)進(jìn)行每位之間(jiān)相與(yǔ)的(de)操作。例如(rú)

Reg[3:0] A,C;

assign C=&A;

上(shàng)面(miàn)代(dài)碼等價于(yú) C = A[3] & A[2] & A[1] & A[0];

如(rú)果(guǒ)A=4’b0110,C的(de)結果(guǒ)为(wèi)0。

5.5.2 單目按位或(huò)

單目按位或(huò)運算符|,運算符後(hòu)为(wèi)需要(yào)進(jìn)行邏輯運算的(de)信(xìn)号(hào),表(biǎo)示对(duì)信(xìn)号(hào)進(jìn)行每位之間(jiān)相或(huò)的(de)操作。例如(rú)

reg[3:0] A,C;

assign C=|A;

上(shàng)面(miàn)代(dài)碼等價于(yú) C = A[3] | A[2] | A[1] | A[0];

如(rú)果(guǒ)A=4’b0110,C的(de)結果(guǒ)为(wèi)1。

5.5.3 單目按位非(fēi)

單目按位非(fēi)運算符~,運算符後(hòu)为(wèi)需要(yào)進(jìn)行邏輯運算的(de)信(xìn)号(hào),表(biǎo)示对(duì)信(xìn)号(hào)進(jìn)行每位取(qǔ)反(fǎn)的(de)操作。例如(rú)

reg[3:0] A,C;

assign C=~A;

上(shàng)面(miàn)代(dài)碼等價于(yú) C[3] = ~A[3],C[2] = ~A[2],C[1] = ~A[1],C[0] = ~A[0]。

如(rú)果(guǒ)A=4’b0110,C的(de)結果(guǒ)为(wèi)4’b1001。

5.5.4 双(shuāng)目按位與(yǔ)

双(shuāng)目按位與(yǔ)運算符&,信(xìn)号(hào)位于(yú)運算符的(de)左(zuǒ)右(yòu)两(liǎng)邊(biān),表(biǎo)示的(de)是(shì)对(duì)这(zhè)两(liǎng)个(gè)信(xìn)号(hào)進(jìn)行对(duì)應(yìng)位相與(yǔ)的(de)操作。例如(rú)

reg[3:0] A,B,C;

assign C = A & B;

上(shàng)面(miàn)的(de)代(dài)碼等價于(yú):C[0] = A[0] & B[0],C[1] = A[1] & B[1],C[2] = A[2] & B[2],C[3] = A[3] & B[3]。如(rú)果(guǒ)A=4’b0110,B=4’b1010,C的(de)結果(guǒ)为(wèi)4’b0010。

如(rú)果(guǒ)操作數长度(dù)不(bù)相等, 长度(dù)較小的(de)操作數在(zài)最(zuì)左(zuǒ)側添0 補位。例如(rú),

reg[1:0] A;

reg[2:0] B;

reg[3:0] C;

assign C = A & B;

上(shàng)面(miàn)的(de)代(dài)碼等價于(yú):C[0] = A[0] & B[0],C[1] = A[1] & B[1],C[2] = 0& B[2],C[3] = 0 &0。

5.5.5 双(shuāng)目按位或(huò)

双(shuāng)目按位或(huò)運算符|,信(xìn)号(hào)位于(yú)運算符的(de)左(zuǒ)右(yòu)两(liǎng)邊(biān),表(biǎo)示的(de)是(shì)对(duì)这(zhè)两(liǎng)个(gè)信(xìn)号(hào)進(jìn)行对(duì)應(yìng)位相或(huò)的(de)操作。例如(rú)

reg[3:0] A,B,C;

assign C = A | B;

上(shàng)面(miàn)的(de)代(dài)碼等價于(yú):C[0] = A[0] | B[0],C[1] = A[1] | B[1],C[2] = A[2] | B[2],C[3] = A[3] | B[3]。如(rú)果(guǒ)A=4’b0110,B=4’b1010,C的(de)結果(guǒ)为(wèi)4’b1110。

如(rú)果(guǒ)操作數长度(dù)不(bù)相等, 长度(dù)較小的(de)操作數在(zài)最(zuì)左(zuǒ)側添0 補位。例如(rú),

reg[1:0] A;

reg[2:0] B;

reg[3:0] C;

assign C = A | B;

上(shàng)面(miàn)的(de)代(dài)碼等價于(yú):C[0] = A[0] | B[0],C[1] = A[1] | B[1],C[2] = 0 | B[2],C[3] = 0 | 0。

5.5.6 双(shuāng)目按位异(yì)或(huò)

双(shuāng)目按位异(yì)或(huò)運算符^,信(xìn)号(hào)位于(yú)運算符的(de)左(zuǒ)右(yòu)两(liǎng)邊(biān),表(biǎo)示的(de)是(shì)对(duì)这(zhè)两(liǎng)个(gè)信(xìn)号(hào)進(jìn)行对(duì)應(yìng)位相异(yì)或(huò)的(de)操作。异(yì)或(huò)是(shì)指0^0=0,1^1=0,0^1=1,即相同(tóng)为(wèi)0,不(bù)同(tóng)为(wèi)1。例如(rú)