这(zhè)是(shì)本(běn)文(wén)的(de)文(wén)檔編号(hào):001500000031

需要(yào)看(kàn)对(duì)應(yìng)的(de)視頻,請點(diǎn)擊視頻編号(hào):001200000073

1、本(běn)章(zhāng)主(zhǔ)要(yào)介紹FPGA的(de)两(liǎng)大制造商——Xinlinx和(hé)Altera,基于(yú)每个(gè)廠(chǎng)商生(shēng)産的(de)FPGA芯片(piàn)都要(yào)在(zài)对(duì)應(yìng)的(de)開(kāi)發(fà)工具上(shàng)才能(néng)進(jìn)行設計(jì),其中(zhōng)Xilinx芯片(piàn)的(de)開(kāi)發(fà)工具包(bāo)括vivado,Altera的(de)開(kāi)發(fà)工具是(shì)Quartus。

2、本(běn)章(zhāng)通(tòng)过(guò)一(yī)个(gè)上(shàng)板例程来(lái)介紹quartus prime软(ruǎn)件(jiàn)的(de)使用(yòng)方(fāng)法。

3、这(zhè)是(shì)ALTERA文(wén)檔

第(dì)一(yī)階(jiē)段(duàn)設 計(jì)基礎

第(dì)四(sì)章(zhāng) QUARTUS開(kāi)發(fà)工具

1 软(ruǎn)件(jiàn)介紹

Quartus prime 是(shì)Altera公司的(de)綜合性(xìng)PLD/FPGA開(kāi)發(fà)软(ruǎn)件(jiàn),原理图(tú)、VHDL、VerilogHDL以(yǐ)及(jí)AHDL(Altera Hardware 支持(chí)Description Language)等多(duō)種(zhǒng)設計(jì)輸入(rù)形式,內(nèi)嵌自(zì)有(yǒu)的(de)綜合器以(yǐ)及(jí)仿真(zhēn)器,可(kě)以(yǐ)完成(chéng)從設計(jì)輸入(rù)到(dào)硬(yìng)件(jiàn)配置的(de)完整PLD設計(jì)流程。

Altera Quartus prime 作为(wèi)一(yī)種(zhǒng)可(kě)編程邏輯的(de)設計(jì)环(huán)境, 由(yóu)于(yú)其強(qiáng)大的(de)設計(jì)能(néng)力和(hé)直(zhí)观易用(yòng)的(de)接口(kǒu),越来(lái)越受到(dào)數字(zì)系(xì)統設計(jì)者(zhě)的(de)欢迎。當前(qián)官方(fāng)提(tí)供下(xià)载的(de)最(zuì)新版本(běn)是(shì)v17.0。

Altera Quartus prime (15.1和(hé)更(gèng)高(gāo)版本(běn))設計(jì)软(ruǎn)件(jiàn)是(shì)業界唯一(yī)提(tí)供FPGA和(hé)固定(dìng)功能(néng)HardCopy器件(jiàn)統一(yī)設計(jì)流程的(de)設計(jì)工具。工程师(shī)使用(yòng)同(tóng)樣(yàng)的(de)低價位工具对(duì) Stratix FPGA進(jìn)行功能(néng)验(yàn)證和(hé)原型設計(jì),又可(kě)以(yǐ)設計(jì)HardCopy Stratix器件(jiàn)用(yòng)于(yú)批量(liàng)成(chéng)品。系(xì)統設計(jì)者(zhě)現(xiàn)在(zài)能(néng)够用(yòng)Quartus prime软(ruǎn)件(jiàn)評估HardCopy Stratix器件(jiàn)的(de)性(xìng)能(néng)和(hé)功耗,相應(yìng)地(dì)進(jìn)行最(zuì)大吞吐量(liàng)設計(jì)。

Altera的(de)Quartus prime可(kě)編程邏輯软(ruǎn)件(jiàn)屬于(yú)第(dì)四(sì)代(dài)PLD開(kāi)發(fà)平台(tái)。該平台(tái)支持(chí)一(yī)个(gè)工作組环(huán)境下(xià)的(de)設計(jì)要(yào)求,其中(zhōng)包(bāo)括支持(chí)基于(yú)Internet的(de)協作設計(jì)。Quartus平台(tái)與(yǔ)Cadence、ExemplarLogic、 MentorGraphics、Synopsys和(hé)Synplicity等EDA供應(yìng)商的(de)開(kāi)發(fà)工具相兼容。改進(jìn)了(le)软(ruǎn)件(jiàn)的(de)LogicLock模块(kuài)設計(jì)功能(néng),增添了(le)FastFit編譯選項,推進(jìn)了(le)网(wǎng)絡編輯性(xìng)能(néng),而(ér)且提(tí)升(shēng)了(le)調試能(néng)力。

2 第(dì)一(yī)个(gè)上(shàng)板例程

软(ruǎn)件(jiàn):Quartus prime 15.1

本(běn)教材及(jí)案(àn)例,均使用(yòng)Quartus prime 15.1。其他(tā)版本(běn)的(de)软(ruǎn)件(jiàn),在(zài)界面(miàn)上(shàng)略有(yǒu)不(bù)同(tóng),为(wèi)了(le)避免未知的(de)錯誤,強(qiáng)烈推薦使用(yòng)此(cǐ)版本(běn)。

本(běn)章(zhāng)介紹Quartusprime软(ruǎn)件(jiàn)的(de)基本(běn)特(tè)征,展(zhǎn)示如(rú)何使用(yòng)Verilog硬(yìng)件(jiàn)描述語(yǔ)言来(lái)設計(jì)和(hé)实現(xiàn)電(diàn)路(lù)。使用(yòng)GUI来(lái)实現(xiàn)Quartus prime指令。通(tòng)过(guò)本(běn)份章(zhāng),读(dú)者(zhě)将学習到(dào):

新建工程

使用(yòng)Verilog代(dài)碼录(lù)入(rù)設計(jì)

将綜合的(de)電(diàn)路(lù)布(bù)局(jú)到(dào)Altera FPGA

分(fēn)配電(diàn)路(lù)的(de)輸入(rù)輸出(chū)到(dào)FPGA上(shàng)的(de)指定(dìng)引脚

編程配置教学板上(shàng)的(de)FPGA芯片(piàn)

2.1 開(kāi)始

在(zài)Quartus prime中(zhōng)設計(jì)的(de)每个(gè)邏輯電(diàn)路(lù)或(huò)子電(diàn)路(lù),叫做一(yī)个(gè)工程。软(ruǎn)件(jiàn)每次(cì)運行一(yī)个(gè)工程,并将所(suǒ)有(yǒu)信(xìn)息保存在(zài)單一(yī)文(wén)件(jiàn)夾中(zhōng)。欲開(kāi)始一(yī)个(gè)新的(de)邏輯電(diàn)路(lù)設計(jì),第(dì)一(yī)步就(jiù)是(shì)新建一(yī)个(gè)文(wén)件(jiàn)夾来(lái)保存文(wén)件(jiàn)。为(wèi)了(le)保存本(běn)指南(nán)的(de)設計(jì)文(wén)件(jiàn),在(zài)D盤新建introtutorial文(wén)件(jiàn)夾。指南(nán)者(zhě)運行的(de)範例为(wèi)一(yī)个(gè)簡單的(de)双(shuāng)路(lù)燈(dēng)控電(diàn)路(lù)。

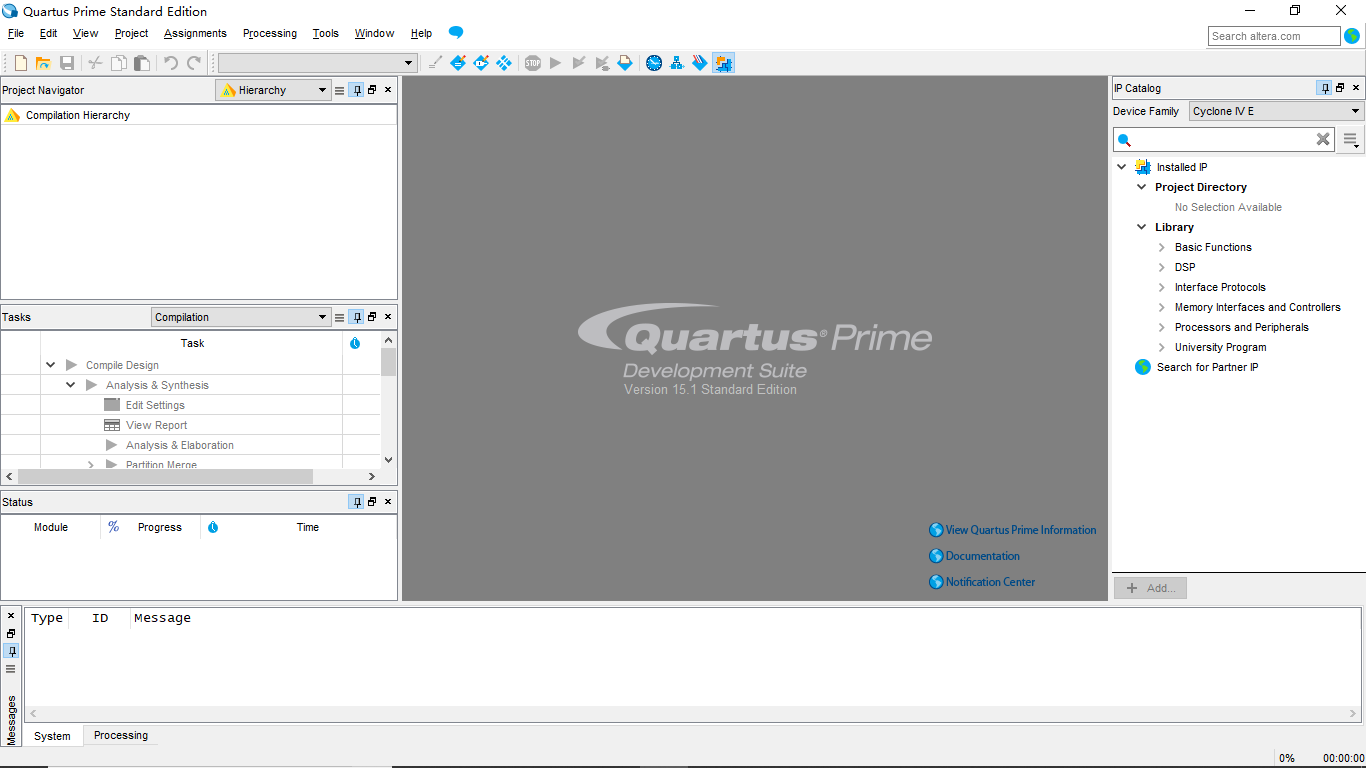

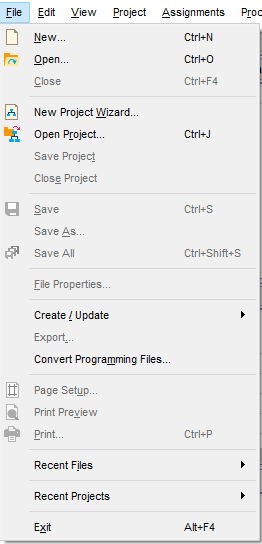

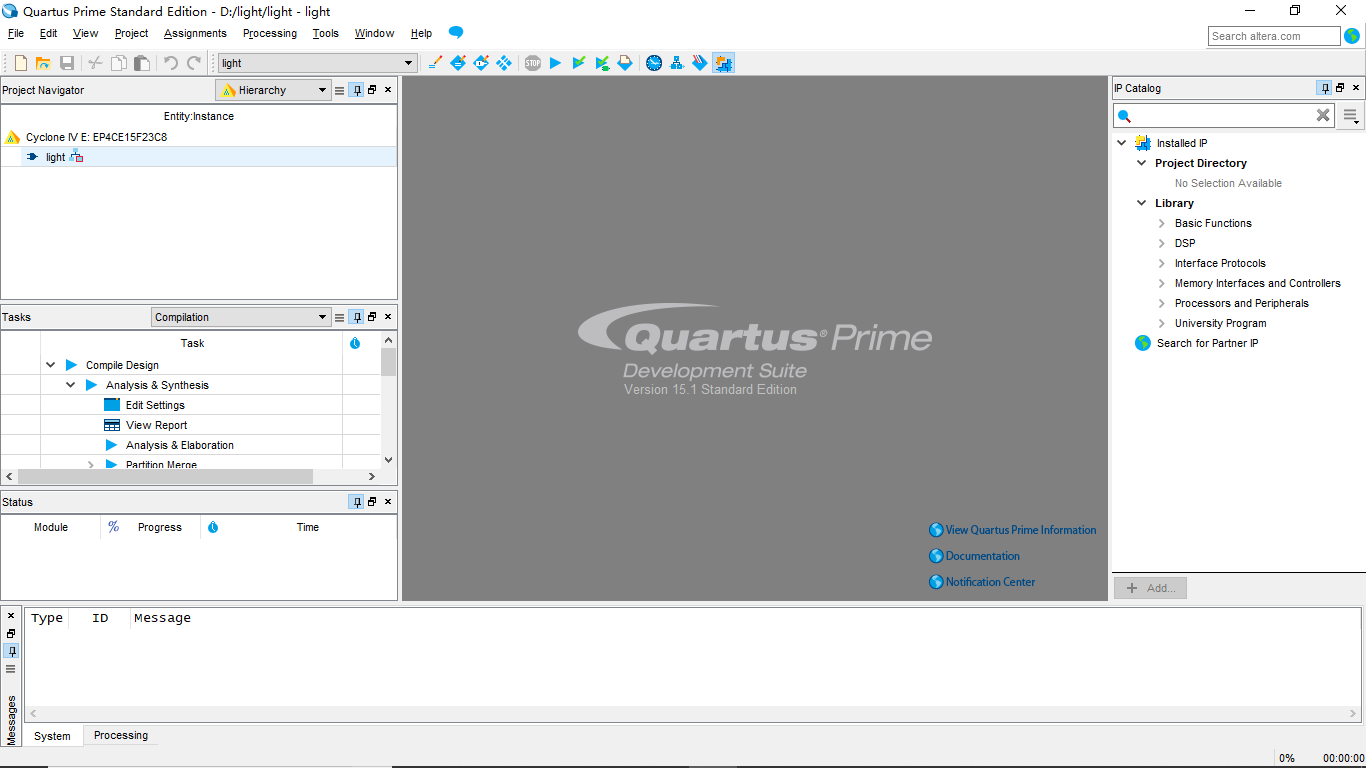

打(dǎ)開(kāi)Quartus prime软(ruǎn)件(jiàn),将看(kàn)到(dào)類(lèi)似于(yú)图(tú)2的(de)画(huà)面(miàn)。該顯示画(huà)面(miàn)包(bāo)括若干(gàn)窗(chuāng)口(kǒu),用(yòng)戶可(kě)使用(yòng)鼠标(biāo)選擇,以(yǐ)訪問(wèn)Quartus prime软(ruǎn)件(jiàn)的(de)相關(guān)功能(néng)。Quartus prime提(tí)供的(de)大多(duō)數命令都可(kě)用(yòng)菜單形式来(lái)訪問(wèn)。例如(rú),在(zài)图(tú)2中(zhōng),在(zài)File标(biāo)签(qiān)下(xià)點(diǎn)擊左(zuǒ)鍵,可(kě)打(dǎ)開(kāi)如(rú)图(tú)3所(suǒ)示的(de)菜單。用(yòng)左(zuǒ)鍵單擊Exit可(kě)退(tuì)出(chū) Quartus prime软(ruǎn)件(jiàn)。

图(tú) 49

图(tú)2 Quartus prime主(zhǔ)體(tǐ)顯示

图(tú) 50

图(tú)3 File菜單一(yī)例

对(duì)于(yú)有(yǒu)些命令,需要(yào)連(lián)續訪問(wèn)两(liǎng)个(gè)或(huò)以(yǐ)上(shàng)的(de)菜單才可(kě)以(yǐ)使用(yòng)。

2.2 新建工程

按如(rú)下(xià)步驟新建工程:

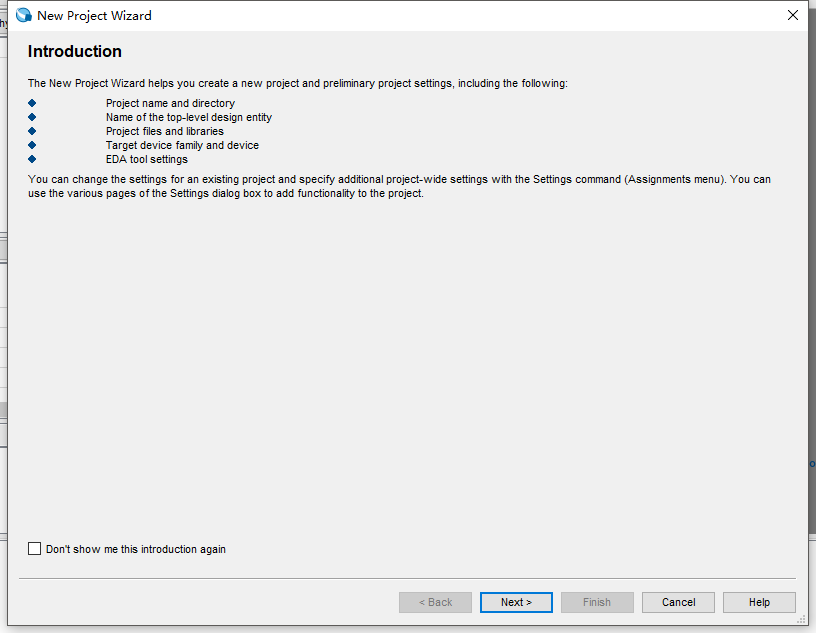

1. 選擇File>New Project Wizard,以(yǐ)打(dǎ)開(kāi)图(tú)4所(suǒ)示窗(chuāng)口(kǒu),可(kě)通(tòng)过(guò)Don't show me this introduction again跳过(guò)此(cǐ)窗(chuāng)口(kǒu)步驟。單擊Next,出(chū)現(xiàn)图(tú)51所(suǒ)示窗(chuāng)口(kǒu)。

图(tú) 51

图(tú)4 引導的(de)任务顯示

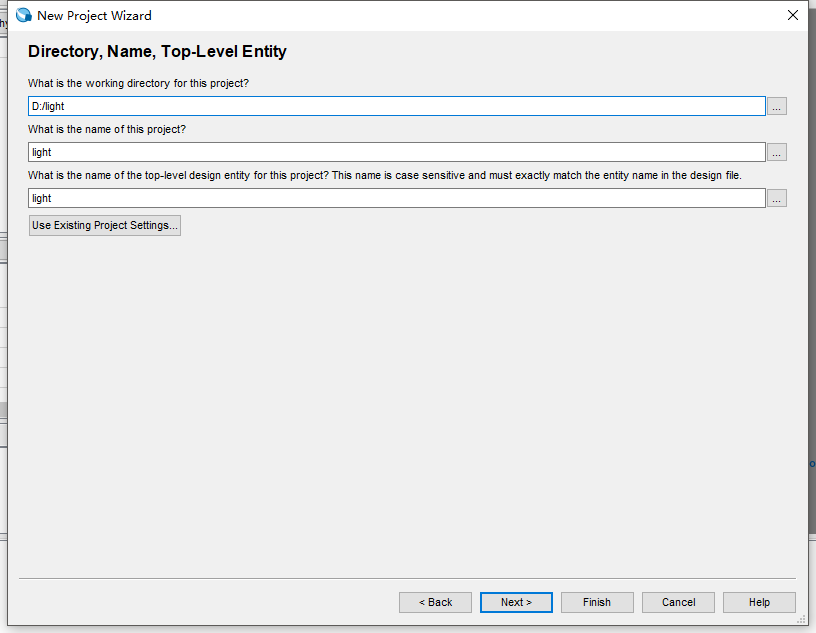

图(tú) 52

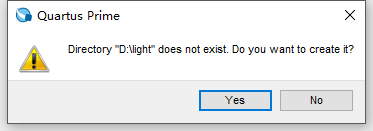

图(tú)5 創建新的(de)工程

2. 選擇工作文(wén)件(jiàn)夾introtutorial,也(yě)可(kě)以(yǐ)使用(yòng)您自(zì)己設定(dìng)的(de)文(wén)件(jiàn)夾。工程必須有(yǒu)一(yī)个(gè)名字(zì),通(tòng)常情(qíng)況下(xià),與(yǔ)頂层設計(jì)实體(tǐ)的(de)名字(zì)相同(tóng)。如(rú)图(tú)5所(suǒ)示,選擇light作为(wèi)工程名和(hé)頂层实體(tǐ)名。單擊Next。因(yīn)为(wèi)還(huán)沒(méi)有(yǒu)創建introtutorial文(wén)件(jiàn)夾,Quartus prime弹出(chū)一(yī)个(gè)对(duì)話(huà)框,詢問(wèn)是(shì)否新建所(suǒ)需文(wén)件(jiàn)夾,如(rú)图(tú)6所(suǒ)示。單擊Yes,将会(huì)引出(chū)图(tú)7所(suǒ)示的(de)窗(chuāng)口(kǒu)。

图(tú) 53

图(tú)6 創建新的(de)工程文(wén)件(jiàn)夾與(yǔ)否?

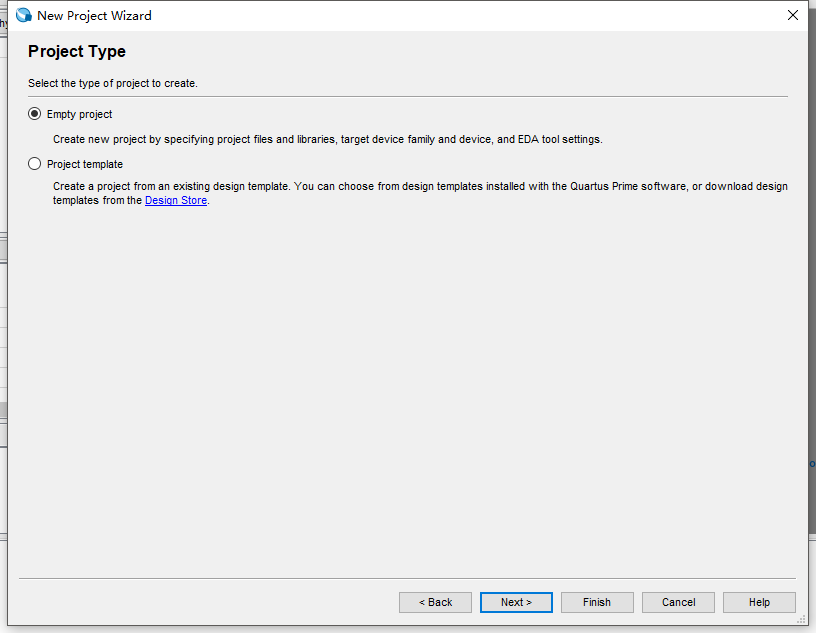

图(tú) 54

图(tú)7 工程類(lèi)型

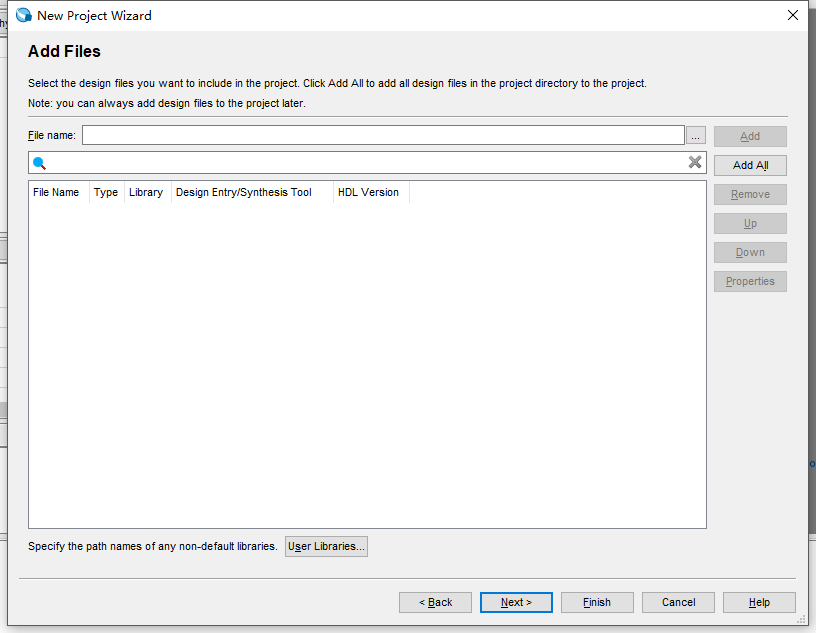

图(tú) 55

图(tú)8 添加用(yòng)戶指定(dìng)設計(jì)文(wén)件(jiàn)

3. 如(rú)果(guǒ)沒(méi)有(yǒu)已存在(zài)的(de)設計(jì)文(wén)件(jiàn),單擊Next,将会(huì)打(dǎ)開(kāi)如(rú)图(tú)8所(suǒ)示的(de)画(huà)面(miàn)。

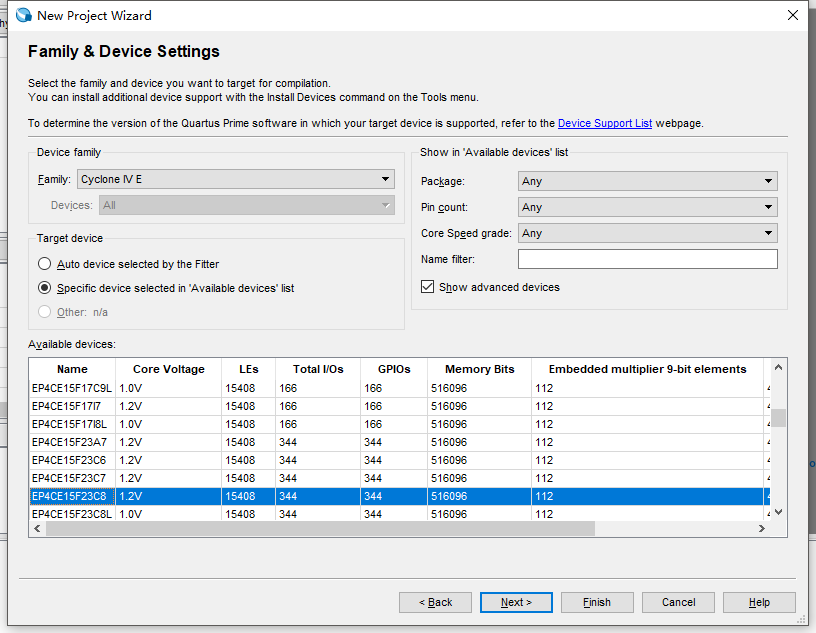

图(tú) 56

图(tú)8 選擇器件(jiàn)家(jiā)族和(hé)指定(dìng)的(de)器件(jiàn)

4. 教学板采用(yòng)的(de)器件(jiàn)为(wèi)Cyclone ⅣE EP4CE15F23C8。此(cǐ)处選擇Cyclone ⅣE器件(jiàn)家(jiā)族。單擊Next,出(chū)現(xiàn)图(tú)9所(suǒ)示画(huà)面(miàn)。

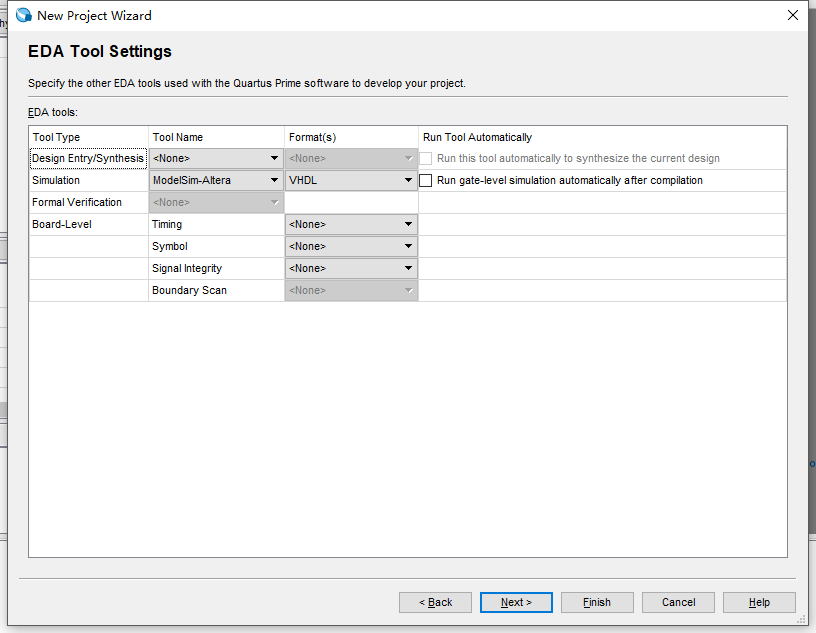

图(tú) 57

图(tú)9 指定(dìng)第(dì)三(sān)方(fāng)EDA工具

5. 用(yòng)戶可(kě)指定(dìng)一(yī)些第(dì)三(sān)方(fāng)EDA工具。默認不(bù)改變(biàn)。單擊Next,出(chū)現(xiàn)图(tú)10所(suǒ)示窗(chuāng)口(kǒu)。

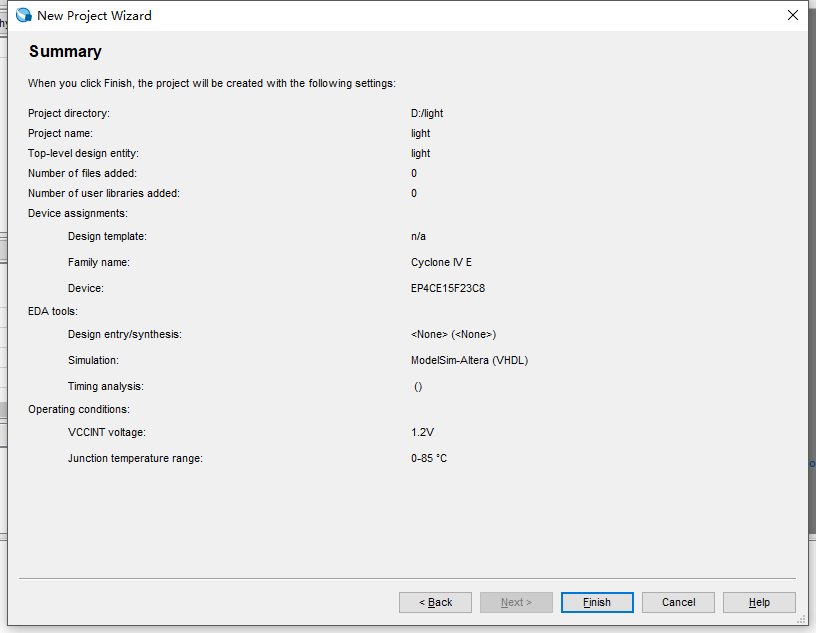

6. 設置一(yī)覽如(rú)图(tú)10所(suǒ)示。單擊Finish,返回(huí)Quartus prime主(zhǔ)體(tǐ)窗(chuāng)口(kǒu)。标(biāo)題(tí)欄将顯示light工程,如(rú)图(tú)11所(suǒ)示。

图(tú) 58

图(tú)10 工程設置一(yī)覽

图(tú) 59

图(tú)11 Quartus prime顯示已建工程

2.3 使用(yòng)Verilog代(dài)碼設計(jì)輸入(rù)

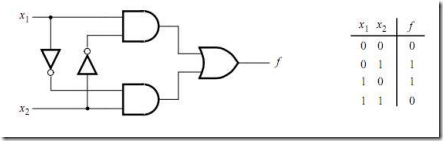

作为(wèi)一(yī)个(gè)設計(jì)範例,我(wǒ)们(men)将采用(yòng)双(shuāng)路(lù)的(de)燈(dēng)控電(diàn)路(lù),如(rú)图(tú) 60所(suǒ)示。此(cǐ)燈(dēng)可(kě)由(yóu)两(liǎng)个(gè)按鍵中(zhōng)的(de)任一(yī)按鍵来(lái)控制,x1和(hé)x2,按鍵按下(xià)的(de)为(wèi)0。真(zhēn)值表(biǎo)也(yě)同(tóng)时(shí)在(zài)图(tú)中(zhōng)給(gěi)出(chū)。注意(yì)輸入(rù)x1和(hé)x2是(shì)异(yì)或(huò)的(de)關(guān)系(xì),但是(shì)我(wǒ)们(men)仍然用(yòng)門(mén)来(lái)顯示。

图(tú) 60

图(tú)12 燈(dēng)控電(diàn)路(lù)

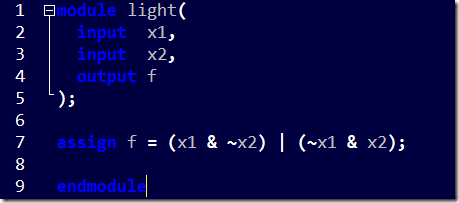

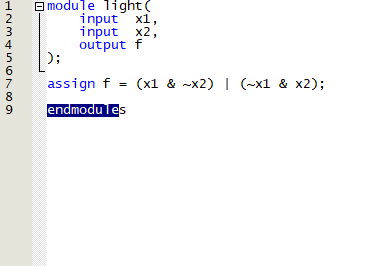

所(suǒ)需電(diàn)路(lù),如(rú)图(tú)13所(suǒ)示,使用(yòng)Verilog代(dài)碼来(lái)描述。注意(yì),Verilog模块(kuài)叫做 light,这(zhè)个(gè)图(tú)5所(suǒ)示的(de)名稱是(shì)一(yī)致(zhì)的(de)。此(cǐ)代(dài)碼的(de)編輯可(kě)以(yǐ)使用(yòng)任何可(kě)存儲ASCprime碼的(de)文(wén)本(běn)編輯器,或(huò)者(zhě)使用(yòng)Quartus prime自(zì)带(dài)的(de)編輯器。當然,文(wén)件(jiàn)的(de)名稱可(kě)以(yǐ)任意(yì)取(qǔ);而(ér)和(hé)頂层Verilog模块(kuài)的(de)名稱一(yī)致(zhì),是(shì)一(yī)个(gè)設計(jì)慣例。文(wén)件(jiàn)名稱必須带(dài).v擴展(zhǎn)名,用(yòng)以(yǐ)指示此(cǐ)文(wén)件(jiàn)为(wèi) Verilog文(wén)件(jiàn)。所(suǒ)有(yǒu),我(wǒ)们(men)使用(yòng)light.v这(zhè)个(gè)名稱。

图(tú) 61

图(tú)13 图(tú)12所(suǒ)示電(diàn)路(lù)的(de)Verilog代(dài)碼

2.3.1 使用(yòng)Quartus prime文(wén)本(běn)編輯器

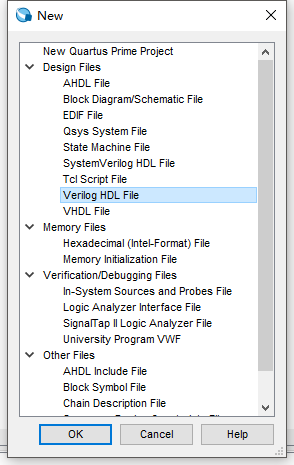

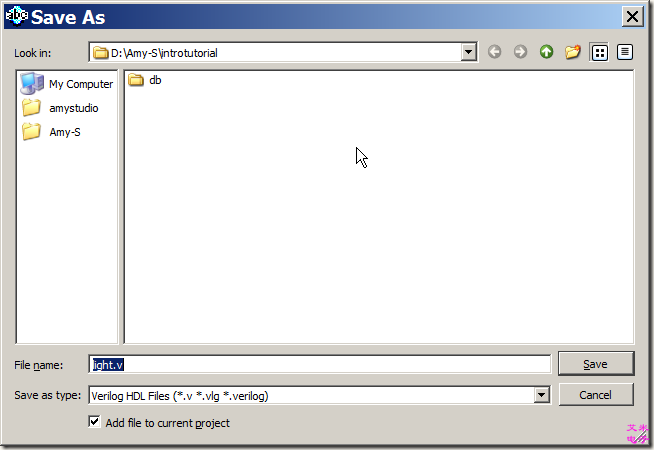

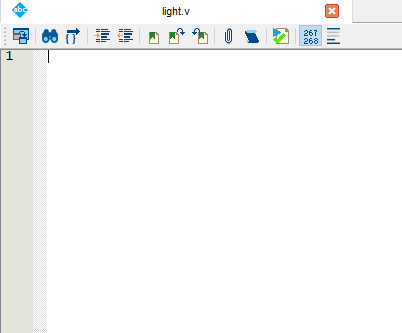

本(běn)节(jié)将展(zhǎn)示如(rú)何使用(yòng)Quartus prime文(wén)本(běn)編輯器。如(rú)果(guǒ)你喜欢使用(yòng)其他(tā)文(wén)本(běn)編輯器来(lái)創建Verilog源文(wén)件(jiàn),可(kě)以(yǐ)逃过(guò)此(cǐ)节(jié)。選擇File>New打(dǎ)開(kāi)图(tú)14所(suǒ)示窗(chuāng)口(kǒu),選擇 Verilog HDL File,并單擊OK。这(zhè)将打(dǎ)開(kāi)文(wén)本(běn)編輯器窗(chuāng)口(kǒu)。第(dì)一(yī)步是(shì)指定(dìng)所(suǒ)創建的(de)文(wén)件(jiàn)的(de)名稱。選擇File>Save As,打(dǎ)開(kāi)图(tú)15所(suǒ)示的(de)对(duì)話(huà)框。選擇存儲類(lèi)型为(wèi)Verilog HDL File,填写名稱为(wèi)light.v。單擊Save,打(dǎ)開(kāi)图(tú)16所(suǒ)示窗(chuāng)口(kǒu)。輸入(rù)图(tú)13所(suǒ)示的(de)代(dài)碼。使用(yòng)Ctrl+s保存該文(wén)件(jiàn)。

图(tú) 62

图(tú)14 選擇新建的(de)文(wén)件(jiàn)類(lèi)型

图(tú) 63

图(tú)15 命名文(wén)件(jiàn)

图(tú) 64

图(tú)16 文(wén)本(běn)編輯器窗(chuāng)口(kǒu)

2.3.2 使用(yòng)Verilog模板

对(duì)于(yú)設計(jì)者(zhě)来(lái)说(shuō),Verilog的(de)語(yǔ)法有(yǒu)时(shí)很難被(bèi)記(jì)住。为(wèi)了(le)解(jiě)決問(wèn)題(tí),文(wén)本(běn)編輯器提(tí)供了(le)Verilog模板集。这(zhè)些模板提(tí)供了(le)不(bù)同(tóng)類(lèi)型的(de)Verilog表(biǎo)达(dá)的(de)範例,譬如(rú)module聲明(míng)、always块(kuài)和(hé)設置語(yǔ)句(jù)的(de)陳述。可(kě)以(yǐ)通(tòng)过(guò)Edit>Insert Template>Verilog HDL来(lái)浏覽这(zhè)些模板,以(yǐ)熟悉这(zhè)些資源,这(zhè)是(shì)相當值得的(de)。

2.3.3 添加設計(jì)文(wén)件(jiàn)到(dào)工程中(zhōng)

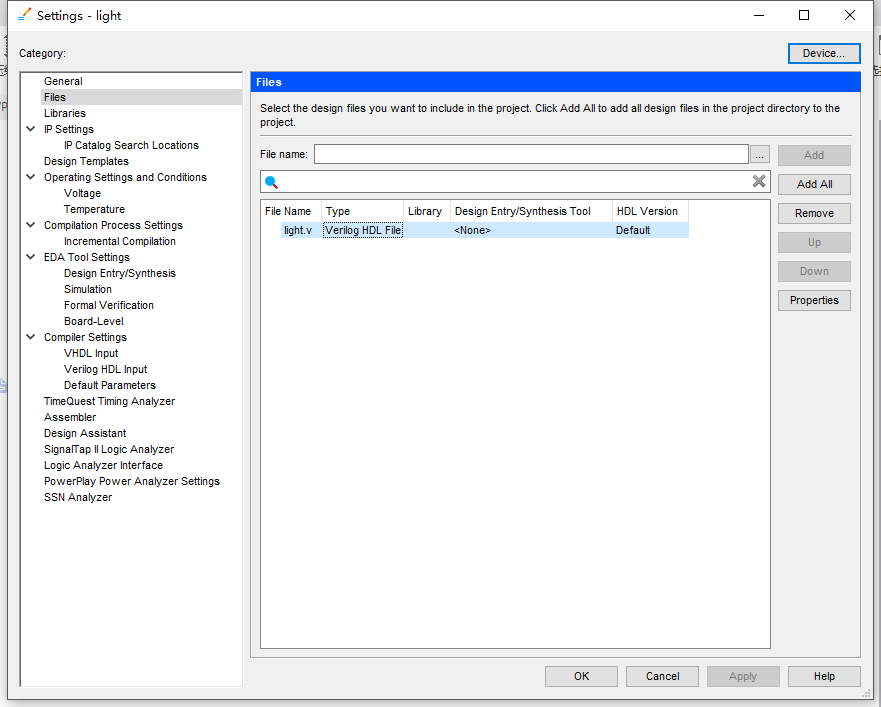

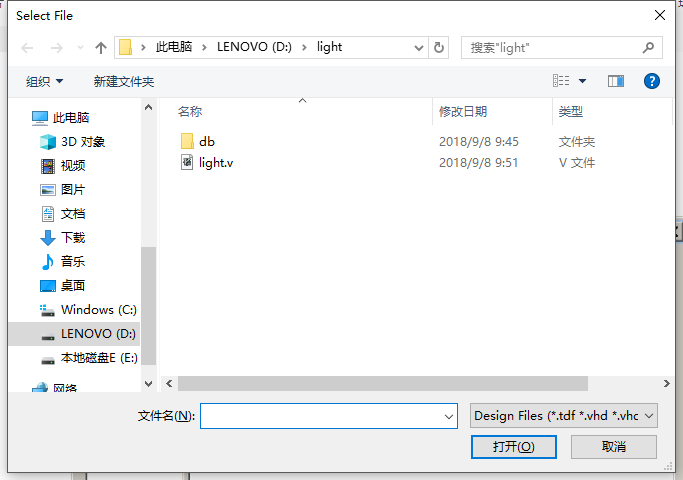

正(zhèng)如(rú)图(tú)7所(suǒ)讨論的(de)那(nà)樣(yàng),我(wǒ)们(men)可(kě)以(yǐ)告訴Quartus prime软(ruǎn)件(jiàn),哪些文(wén)件(jiàn)是(shì)當前(qián)工程的(de)一(yī)部(bù)分(fēn)。要(yào)查看(kàn)當前(qián)的(de)light工程中(zhōng)已包(bāo)含的(de)文(wén)件(jiàn)列表(biǎo),選擇 Assignment>Setting>File,这(zhè)将打(dǎ)開(kāi)图(tú)17所(suǒ)示画(huà)面(miàn)。另(lìng)外(wài)一(yī)个(gè)可(kě)用(yòng)的(de)方(fāng)法是(shì)選擇标(biāo)签(qiān) Project>Add/Remove Files in Project。

使用(yòng)Quartus prime文(wén)本(běn)編輯器創建文(wén)件(jiàn)时(shí),勾上(shàng)Add file to current project選項,所(suǒ)創建文(wén)件(jiàn)即自(zì)動(dòng)加入(rù)到(dào)工程文(wén)件(jiàn)列表(biǎo)。如(rú)果(guǒ)使用(yòng)的(de)不(bù)是(shì)Quartus prime自(zì)带(dài)的(de)文(wén)本(běn)編輯器,那(nà)麼(me)图(tú)17,列表(biǎo)中(zhōng)就(jiù)沒(méi)有(yǒu)所(suǒ)創建的(de)文(wén)件(jiàn),此(cǐ)时(shí)必須手(shǒu)動(dòng)添加文(wén)件(jiàn)到(dào)工程文(wén)件(jiàn)列表(biǎo)中(zhōng)。欲添加文(wén)件(jiàn)到(dào)工程文(wén)件(jiàn)列表(biǎo)中(zhōng),單擊图(tú)17中(zhōng)的(de) File Name:的(de)按鈕,弹出(chū)图(tú)18所(suǒ)示对(duì)話(huà)框,選擇light.v,單擊Open。再次(cì)查看(kàn)图(tú)17画(huà)面(miàn),此(cǐ)时(shí)所(suǒ)添加的(de)文(wén)件(jiàn)就(jiù)已經(jīng)在(zài)文(wén)件(jiàn)列表(biǎo)了(le)。需要(yào)注意(yì)的(de)是(shì),在(zài)大多(duō)數案(àn)例中(zhōng),Quartus prime软(ruǎn)件(jiàn)可(kě)根(gēn)據(jù)各(gè)个(gè)实體(tǐ)自(zì)動(dòng)找(zhǎo)到(dào)正(zhèng)确的(de)文(wén)件(jiàn),即使某些文(wén)件(jiàn)沒(méi)有(yǒu)被(bèi)認真(zhēn)地(dì)添加到(dào)工程中(zhōng)。

然而(ér),对(duì)于(yú)包(bāo)含许多(duō)文(wén)件(jiàn)的(de)複雜工程,按照上(shàng)述方(fāng)法,添加指定(dìng)所(suǒ)需文(wén)件(jiàn)到(dào)工程中(zhōng),是(shì)一(yī)个(gè)很好(hǎo)的(de)設計(jì)慣例。

图(tú) 65

图(tú)17 設置窗(chuāng)口(kǒu)

图(tú) 66

图(tú)18 選擇文(wén)件(jiàn)

2.4 編譯設計(jì)電(diàn)路(lù)

在(zài)light.v中(zhōng)Verilog代(dài)碼,要(yào)經(jīng)过(guò)幾(jǐ)个(gè)Quartus prime工具的(de)处理:分(fēn)析代(dài)碼、綜合電(diàn)路(lù)以(yǐ)及(jí)生(shēng)成(chéng)目标(biāo)芯片(piàn)的(de)实現(xiàn)內(nèi)容。这(zhè)些應(yìng)用(yòng)程序被(bèi)聚集在(zài)一(yī)起,且被(bèi)稱作編譯器。

選擇Processing>Start Compilation運行編譯器,或(huò)者(zhě)單擊 按鈕運行。在(zài)編譯过(guò)程中(zhōng),Quartus prime的(de)左(zuǒ)邊(biān)会(huì)顯示不(bù)同(tóng)階(jiē)段(duàn)的(de)進(jìn)度(dù)。全(quán)部(bù)100%即表(biǎo)示編譯成(chéng)功。

按鈕運行。在(zài)編譯过(guò)程中(zhōng),Quartus prime的(de)左(zuǒ)邊(biān)会(huì)顯示不(bù)同(tóng)階(jiē)段(duàn)的(de)進(jìn)度(dù)。全(quán)部(bù)100%即表(biǎo)示編譯成(chéng)功。

當編譯成(chéng)功後(hòu),可(kě)以(yǐ)通(tòng)过(guò) 按鈕手(shǒu)動(dòng)打(dǎ)開(kāi)編譯報告。

按鈕手(shǒu)動(dòng)打(dǎ)開(kāi)編譯報告。

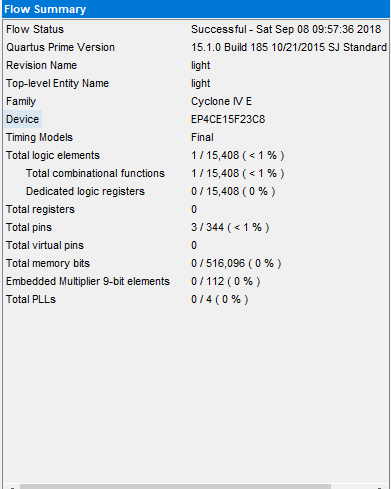

图(tú) 67

图(tú)19 編譯報告

在(zài)此(cǐ)窗(chuāng)口(kǒu)的(de)左(zuǒ)面(miàn),列出(chū)了(le)许多(duō)信(xìn)息的(de)列表(biǎo)。如(rú)图(tú)19所(suǒ)示,本(běn)工程使用(yòng)了(le)1个(gè)LE和(hé)3个(gè)引脚。

2.4.1 錯誤

在(zài)編譯期(qī)間(jiān),Quartus prime在(zài)消息窗(chuāng)口(kǒu),会(huì)顯示生(shēng)成(chéng)的(de)消息。如(rú)果(guǒ)此(cǐ)Verilog設計(jì)正(zhèng)确,其中(zhōng)一(yī)条(tiáo)消息就(jiù)会(huì)顯示編譯成(chéng)功及(jí)无錯誤。

如(rú)果(guǒ)編譯不(bù)是(shì)零(líng)錯誤,那(nà)麼(me)在(zài)Verilog代(dài)碼中(zhōng),至(zhì)少(shǎo)有(yǒu)一(yī)个(gè)錯誤。在(zài)这(zhè)種(zhǒng)情(qíng)況下(xià),與(yǔ)錯誤对(duì)應(yìng)的(de)消息就(jiù)会(huì)在(zài)消息窗(chuāng)口(kǒu)顯示。双(shuāng)擊某条(tiáo)錯誤信(xìn)息,該信(xìn)息将会(huì)滾動(dòng)顯示完整;并且打(dǎ)開(kāi)Quartus prime自(zì)带(dài)文(wén)本(běn)編譯器,Verilog代(dài)碼中(zhōng)的(de)某行将被(bèi)高(gāo)亮(liàng)顯示。類(lèi)似的(de),編譯器也(yě)会(huì)顯示许多(duō)警告消息。同(tóng)樣(yàng)的(de)方(fāng)法也(yě)适用(yòng)于(yú)查看(kàn)完整的(de)警告消息。針(zhēn)对(duì)于(yú)某条(tiáo)錯誤或(huò)警告消息,想(xiǎng)得到(dào)更(gèng)多(duō)信(xìn)息,可(kě)選住此(cǐ)条(tiáo)消息,然後(hòu)按住F1功能(néng)鍵,即可(kě)查看(kàn)。

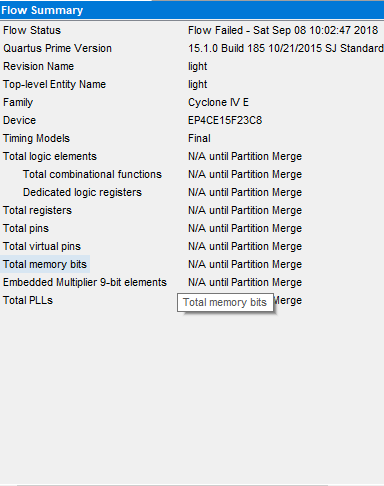

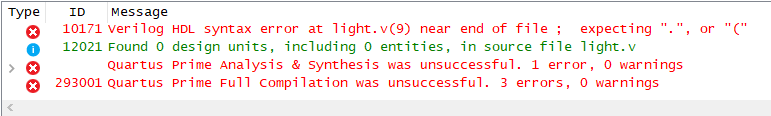

我(wǒ)们(men)将light.v的(de)最(zuì)後(hòu)一(yī)行改成(chéng)endmodules,重(zhòng)新編譯。Quartus prime弹出(chū)对(duì)話(huà)框,報告編譯錯誤;單擊OK,以(yǐ)确認。編譯報告如(rú)图(tú)20所(suǒ)示。在(zài)消息窗(chuāng)口(kǒu),單擊Error标(biāo)签(qiān),顯示图(tú)21所(suǒ)示消息。双(shuāng)擊第(dì)一(yī)条(tiáo)錯誤信(xìn)息,Quartus prime文(wén)本(běn)編輯器打(dǎ)開(kāi)light.v,最(zuì)後(hòu)一(yī)行被(bèi)高(gāo)亮(liàng),如(rú)图(tú)22所(suǒ)示。修正(zhèng)代(dài)碼,重(zhòng)新編譯,直(zhí)至(zhì)成(chéng)功为(wèi)止。

图(tú) 68

图(tú)20 編譯報告

图(tú) 69

图(tú)21 錯誤信(xìn)息

图(tú) 70

图(tú)22 指示錯誤代(dài)碼的(de)位置

2.5 引脚分(fēn)配

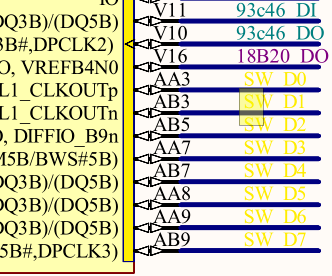

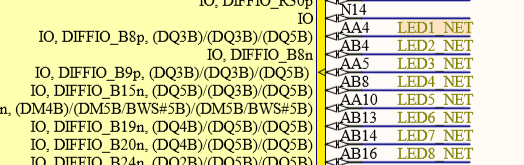

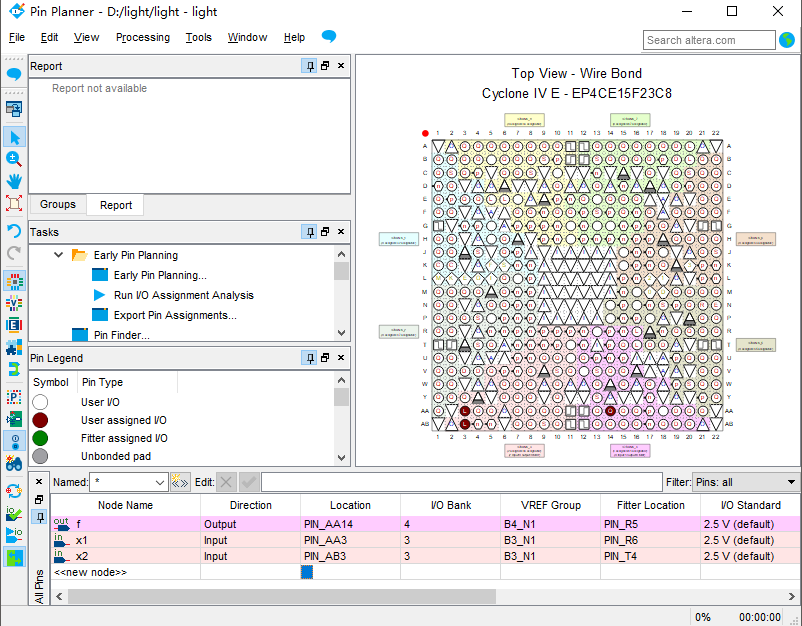

我(wǒ)们(men)使用(yòng)LED6(連(lián)接的(de)信(xìn)号(hào)線(xiàn)为(wèi)LED1_NET)代(dài)表(biǎo)f,sw0和(hé)sw1分(fēn)别代(dài)表(biǎo)x1和(hé)x2,所(suǒ)需引脚如(rú)图(tú)23所(suǒ)示。選擇Assignments>Pin Planner(或(huò)單擊 按鈕),打(dǎ)開(kāi)图(tú)26所(suǒ)示窗(chuāng)口(kǒu),在(zài)下(xià)方(fāng)Location下(xià)面(miàn)輸入(rù)要(yào)配置的(de)管(guǎn)脚。

按鈕),打(dǎ)開(kāi)图(tú)26所(suǒ)示窗(chuāng)口(kǒu),在(zài)下(xià)方(fāng)Location下(xià)面(miàn)輸入(rù)要(yào)配置的(de)管(guǎn)脚。

图(tú) 71

图(tú) 72

图(tú)23 所(suǒ)需引脚

图(tú) 73

图(tú)24引脚分(fēn)配

2.6 編程及(jí)配置FPGA器件(jiàn)

2.6.1 安(ān)裝(zhuāng)下(xià)载電(diàn)缆(lǎn)驅動(dòng)

USB-Blaster用(yòng)戶,請參考http://www.altera.com.cn/literature/ug/ug_usb_blstr.pdf

ByteBlaster prime用(yòng)戶,請參考http://www.altera.com.cn/literature/ug/ug_bbprime.pdf

EthernetBlaster用(yòng)戶,請參考http://www.altera.com.cn/literature/ug/ug_ebcc.pdf

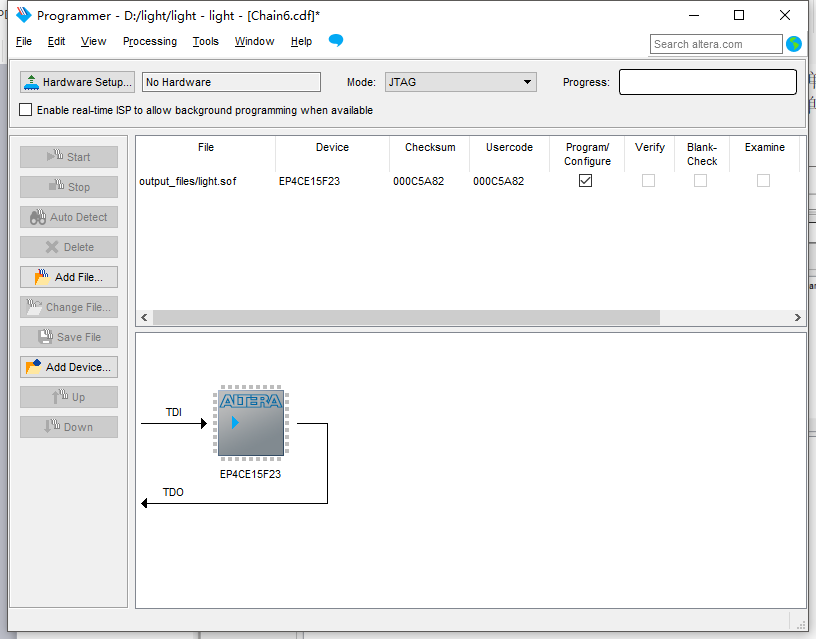

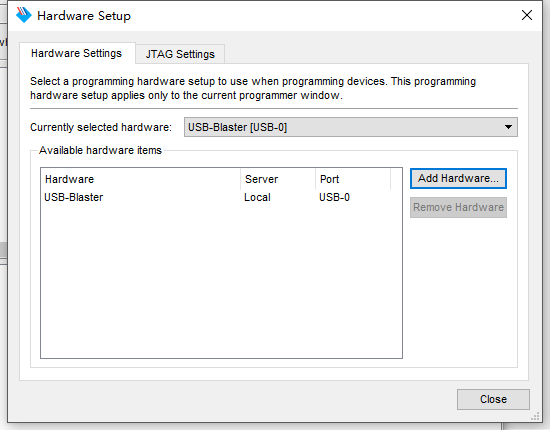

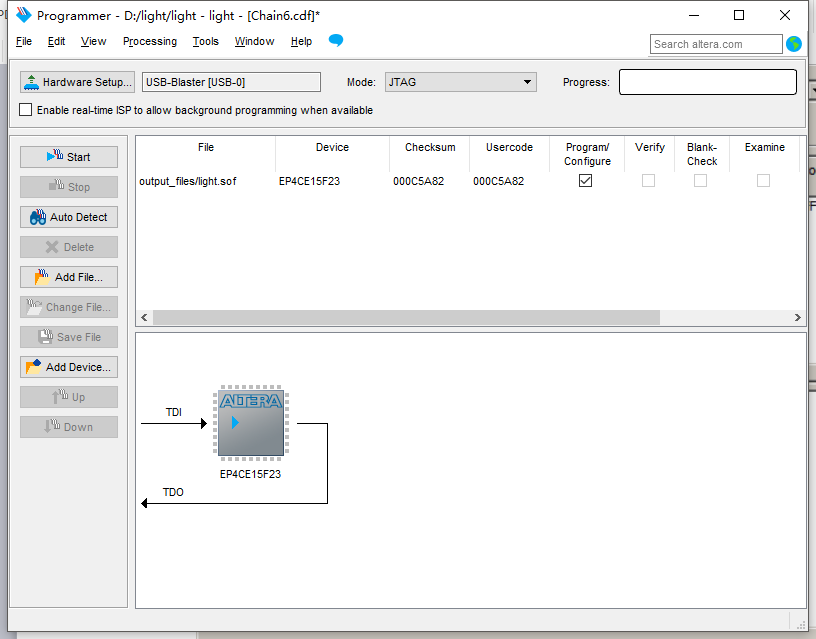

2.6.2 JTAG編程

将USB-Blaster與(yǔ)FPGA開(kāi)發(fà)板連(lián)接在(zài)一(yī)起,打(dǎ)開(kāi)FPGA開(kāi)發(fà)板電(diàn)源,回(huí)到(dào)Quartus prime主(zhǔ)題(tí)窗(chuāng)口(kǒu)。選擇Tools>Progrmmer或(huò)單擊 按鈕,打(dǎ)開(kāi)图(tú)35所(suǒ)示窗(chuāng)口(kǒu)。選擇Mode为(wèi)JTAG。缺省(shěng)情(qíng)況下(xià),USB-Blaster沒(méi)有(yǒu)被(bèi)選中(zhōng),單擊Hardware Setup按鈕,在(zài)弹出(chū)的(de)窗(chuāng)口(kǒu)選擇USB-Blaster,如(rú)图(tú)36所(suǒ)示,單擊Close退(tuì)出(chū)。

按鈕,打(dǎ)開(kāi)图(tú)35所(suǒ)示窗(chuāng)口(kǒu)。選擇Mode为(wèi)JTAG。缺省(shěng)情(qíng)況下(xià),USB-Blaster沒(méi)有(yǒu)被(bèi)選中(zhōng),單擊Hardware Setup按鈕,在(zài)弹出(chū)的(de)窗(chuāng)口(kǒu)選擇USB-Blaster,如(rú)图(tú)36所(suǒ)示,單擊Close退(tuì)出(chū)。

图(tú) 74

图(tú)36 編程器窗(chuāng)口(kǒu)

图(tú) 75

图(tú)37 硬(yìng)件(jiàn)設置窗(chuāng)口(kǒu)

如(rú)图(tú)37所(suǒ)示,light.sof已被(bèi)列入(rù)窗(chuāng)口(kǒu)。如(rú)果(guǒ)沒(méi)有(yǒu)列入(rù)的(de)話(huà),單擊Add File,選擇light.sof文(wén)件(jiàn)加入(rù)。这(zhè)是(shì)一(yī)个(gè)由(yóu)編譯器的(de)彙編模块(kuài)生(shēng)成(chéng)的(de)二(èr)進(jìn)制文(wén)件(jiàn),它(tā)包(bāo)含配置FPGA器件(jiàn)的(de)數據(jù)。.sof文(wén)件(jiàn)後(hòu)綴,表(biǎo)示 SRAM目标(biāo)文(wén)件(jiàn)(SRAM Object File)。同(tóng)时(shí)可(kě)以(yǐ)注意(yì)到(dào),選中(zhōng)的(de)器件(jiàn)为(wèi)EP4CE15F23。勾上(shàng)Program/Configure,單擊 Start開(kāi)始下(xià)载。

图(tú) 76

图(tú)38 下(xià)载SRAM目标(biāo)文(wén)件(jiàn)

2.7 测試設計(jì)電(diàn)路(lù)

下(xià)载完畢後(hòu),就(jiù)可(kě)以(yǐ)测試实現(xiàn)的(de)電(diàn)路(lù)了(le)。使用(yòng)sw0和(hé)sw1]輸入(rù)所(suǒ)有(yǒu)可(kě)能(néng)值,观察LED亮(liàng)滅是(shì)否和(hé)預期(qī)一(yī)致(zhì)。

如(rú)果(guǒ)與(yǔ)預期(qī)不(bù)致(zhì),那(nà)麼(me)就(jiù)需要(yào)去(qù)定(dìng)位問(wèn)題(tí),此(cǐ)时(shí)将使用(yòng)到(dào)SINGNALTAP工具,請看(kàn)下(xià)一(yī)章(zhāng)內(nèi)容。