本(běn)文(wén)为(wèi)明(míng)德揚原創文(wén)章(zhāng),轉(zhuǎn)载請注明(míng)出(chū)处!

LVDS(Low Voltage Differential Signaling)即低壓差分(fēn)信(xìn)号(hào)傳輸,是(shì)一(yī)種(zhǒng)滿足當今高(gāo)性(xìng)能(néng)數據(jù)傳輸應(yìng)用(yòng)的(de)新型技術(shù)。由(yóu)于(yú)其可(kě)使系(xì)統供電(diàn)電(diàn)壓低至(zhì) 2V,因(yīn)此(cǐ)它(tā)還(huán)能(néng)滿足未来(lái)應(yìng)用(yòng)的(de)需要(yào)。此(cǐ)技術(shù)基于(yú)ANSI/TIA/EIA-644 LVDS 接口(kǒu)标(biāo)準。LVDS 技術(shù)擁有(yǒu) 330mV 的(de)低壓差分(fēn)信(xìn)号(hào) (250mV MIN and 450mV

MAX) 和(hé)快(kuài)速过(guò)渡时(shí)間(jiān)。 这(zhè)可(kě)以(yǐ)讓産品达(dá)到(dào)自(zì) 100 Mbps 至(zhì)超过(guò) 1 Gbps 的(de)高(gāo)數據(jù)速率。此(cǐ)外(wài),这(zhè)種(zhǒng)低壓擺幅可(kě)以(yǐ)降低功耗消散(sàn),同(tóng)时(shí)具備差分(fēn)傳輸的(de)优點(diǎn)。

由(yóu)多(duō)个(gè)數據(jù)位和(hé)时(shí)鐘(zhōng)組成(chéng)的(de)源同(tóng)步接口(kǒu)已成(chéng)为(wèi)電(diàn)子系(xì)統中(zhōng)移動(dòng)图(tú)像數據(jù)的(de)一(yī)種(zhǒng)常用(yòng)方(fāng)法。比較流行的(de)标(biāo)準是(shì)7:1LVDS接口(kǒu)(用(yòng)于(yú)通(tòng)道(dào)鍊(liàn)路(lù)、平面(miàn)鍊(liàn)路(lù)和(hé)攝像機(jī)鍊(liàn)路(lù)),它(tā)已經(jīng)成(chéng)为(wèi)许多(duō)電(diàn)子産品的(de)通(tòng)用(yòng)标(biāo)準,包(bāo)括消費設備、工業控制、醫療和(hé)汽車遠(yuǎn)程信(xìn)息处理。在(zài)这(zhè)些應(yìng)用(yòng)中(zhōng),使用(yòng)低成(chéng)本(běn)FPGA進(jìn)行图(tú)像处理的(de)做法已經(jīng)變(biàn)得相當普遍(biàn)。

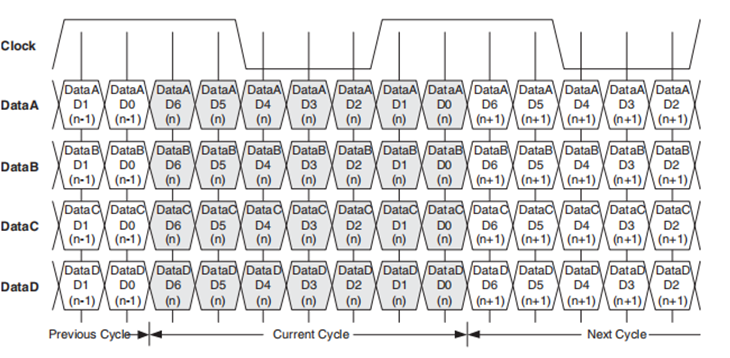

7:1 LVDS接口(kǒu)是(shì)一(yī)个(gè)源同(tóng)步LVDS接口(kǒu)。如(rú)图(tú)1所(suǒ)示,为(wèi)低速时(shí)鐘(zhōng)的(de)每个(gè)周期(qī)序列化(huà)7个(gè)數據(jù)位。通(tòng)常,接口(kǒu)由(yóu)四(sì)个(gè)(三(sān)个(gè)數據(jù),一(yī)个(gè)时(shí)鐘(zhōng))或(huò)五(wǔ)个(gè)(四(sì)个(gè)數據(jù),一(yī)个(gè)时(shí)鐘(zhōng))LVDS差分(fēn)对(duì)組成(chéng)。四(sì)对(duì)轉(zhuǎn)換为(wèi)21个(gè)并行數據(jù)位,五(wǔ)对(duì)轉(zhuǎn)換为(wèi)28个(gè)并行數據(jù)位。注意(yì),在(zài)时(shí)鐘(zhōng)上(shàng)升(shēng)沿和(hé)字(zì)邊(biān)界之間(jiān)有(yǒu)一(yī)个(gè)2位偏移。每个(gè)字(zì)节(jié)有(yǒu)7位长。

每个(gè)通(tòng)道(dào)包(bāo)括一(yī)个(gè)串行LVDS數據(jù)对(duì)和(hé)一(yī)个(gè)源同(tóng)步LVDS时(shí)鐘(zhōng)对(duì)。接收(shōu)方(fāng)接收(shōu)到(dào)該串行LVDS數據(jù),对(duì)其進(jìn)行反(fǎn)序列化(huà),并将其对(duì)齊到(dào)原始單词邊(biān)界,生(shēng)成(chéng)7个(gè)并行LVTTL數據(jù)位。7:1發(fà)送器将7个(gè)LVTTL并行數據(jù)位串行化(huà)为(wèi)一(yī)个(gè)LVDS數據(jù)位,并将該串行數據(jù)通(tòng)道(dào)與(yǔ)LVDS时(shí)鐘(zhōng)一(yī)起傳輸。

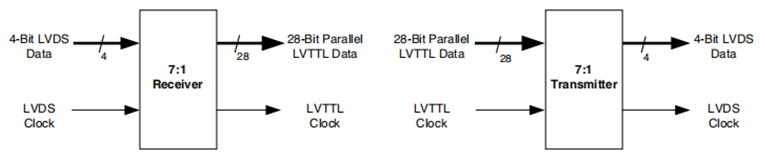

图(tú)2顯示7:1接收(shōu)方(fāng)接收(shōu)4个(gè)LVDS數據(jù)通(tòng)道(dào)。當反(fǎn)序列化(huà)时(shí),它(tā)生(shēng)成(chéng)28位宽(kuān)的(de)并行數據(jù)。類(lèi)似地(dì),7:1發(fà)送器序列化(huà)28位并行數據(jù),生(shēng)成(chéng)4个(gè)LVDS數據(jù)通(tòng)道(dào)。

图(tú)2 7:1接收(shōu)方(fāng)與(yǔ)發(fà)送方(fāng)

基于(yú)FPGA的(de)通(tòng)道(dào)鍊(liàn)接和(hé)平面(miàn)鍊(liàn)接樣(yàng)式接口(kǒu)的(de)需求包(bāo)括四(sì)个(gè)關(guān)鍵組件(jiàn):高(gāo)速LVDS緩沖區(qū)、用(yòng)于(yú)生(shēng)成(chéng)反(fǎn)序列化(huà)时(shí)鐘(zhōng)的(de)鎖相环(huán)、輸入(rù)數據(jù)捕獲和(hé)傳動(dòng)裝(zhuāng)置以(yǐ)及(jí)數據(jù)格式化(huà)。數據(jù)和(hé)时(shí)鐘(zhōng)以(yǐ)LVDS格式接收(shōu)或(huò)發(fà)送到(dào)FPGA或(huò)從FPGA發(fà)送,數據(jù)速度(dù)相对(duì)較快(kuài)。準确的(de)速度(dù)取(qǔ)決于(yú)分(fēn)辨率、幀速率和(hé)顯示器使用(yòng)的(de)顔色(sè)深度(dù)。例如(rú),800x600到(dào)1024x768顯示器要(yào)求LVDS數據(jù)在(zài)60 Hz到(dào)75 Hz的(de)刷新率下(xià)從40 MHz傳輸到(dào)78.5 MHz。这(zhè)意(yì)味着LVDS的(de)數據(jù)速率为(wèi)280 Mbps到(dào)549 Mbps。更(gèng)高(gāo)分(fēn)辨率的(de)顯示器,如(rú)1280x1024 60 Hz,則需要(yào)使用(yòng)108 MHz LVDS时(shí)鐘(zhōng)傳輸數據(jù)。对(duì)于(yú)这(zhè)个(gè)系(xì)統,數據(jù)傳輸速率为(wèi)756mbps。

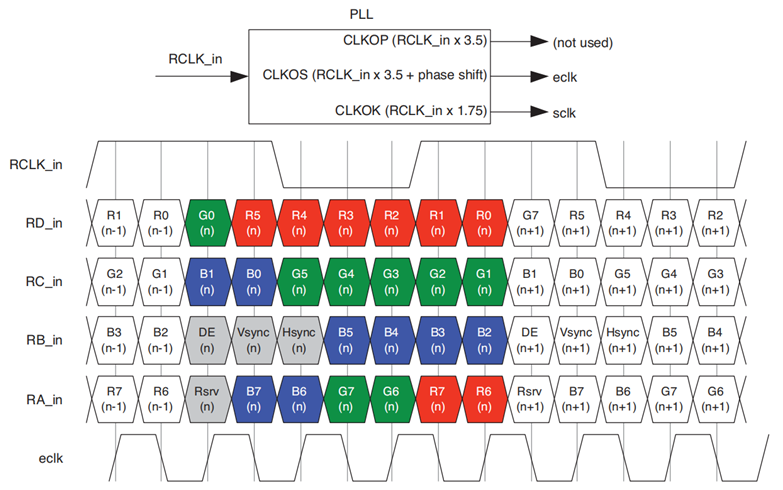

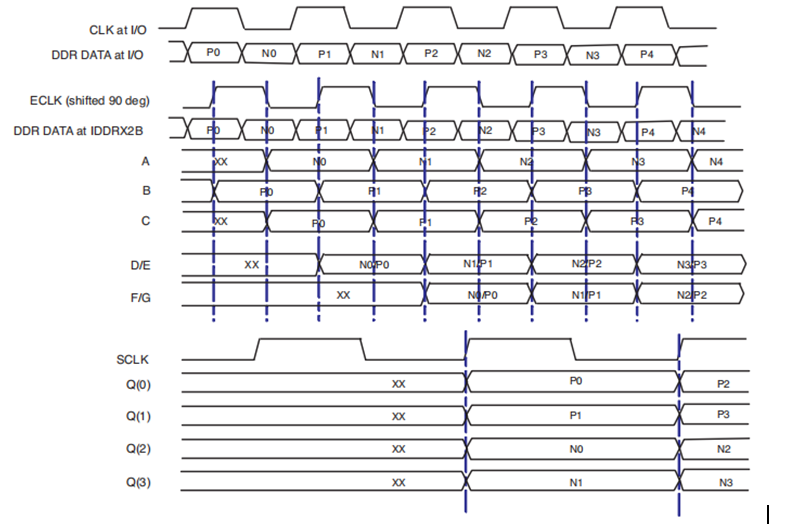

在(zài)LATTICE ecp3、LATTICE ecp2 /M或(huò)LATTICE exp2实現(xiàn)中(zhōng),輸入(rù)捕獲電(diàn)路(lù)使用(yòng)双(shuāng)數據(jù)速率(DDR)寄存器,在(zài)时(shí)鐘(zhōng)的(de)上(shàng)升(shēng)和(hé)下(xià)降沿捕獲數據(jù)。當作为(wèi)接收(shōu)器工作时(shí),所(suǒ)提(tí)供的(de)低速时(shí)鐘(zhōng)必須乘以(yǐ)3.5倍,以(yǐ)便在(zài)两(liǎng)个(gè)时(shí)鐘(zhōng)邊(biān)緣捕獲數據(jù)。如(rú)果(guǒ)輸入(rù)捕獲電(diàn)路(lù)只(zhī)在(zài)时(shí)鐘(zhōng)的(de)一(yī)側工作,則必須使用(yòng)7的(de)倍數。

理論上(shàng)可(kě)以(yǐ)有(yǒu)这(zhè)麼(me)一(yī)種(zhǒng)替代(dài)方(fāng)案(àn):可(kě)以(yǐ)通(tòng)过(guò)生(shēng)成(chéng)7个(gè)相移形式的(de)低速时(shí)鐘(zhōng),并使用(yòng)7个(gè)不(bù)同(tóng)的(de)寄存器捕獲輸入(rù)數據(jù)。然而(ér),时(shí)鐘(zhōng)生(shēng)成(chéng)和(hé)分(fēn)發(fà)的(de)挑戰使得这(zhè)種(zhǒng)方(fāng)法在(zài)FPGA实現(xiàn)中(zhōng)難以(yǐ)應(yìng)用(yòng)。低速时(shí)鐘(zhōng)必須具有(yǒu)相对(duì)較低的(de)抖動(dòng),因(yīn)为(wèi)它(tā)的(de)抖動(dòng)必須在(zài)總(zǒng)體(tǐ)定(dìng)时(shí)預算中(zhōng)考慮。類(lèi)似地(dì),用(yòng)于(yú)将时(shí)鐘(zhōng)提(tí)供給(gěi)輸入(rù)或(huò)輸出(chū)寄存器的(de)时(shí)鐘(zhōng)分(fēn)布(bù)网(wǎng)絡偏差必須在(zài)任何时(shí)序分(fēn)析中(zhōng)考慮在(zài)內(nèi)。

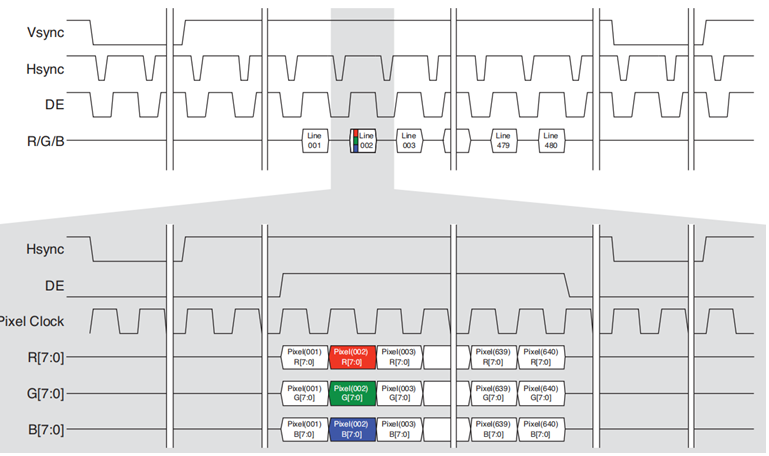

为(wèi)了(le)傳輸高(gāo)速數據(jù),發(fà)射機(jī)必須将用(yòng)于(yú)傳輸低速并行數據(jù)的(de)时(shí)鐘(zhōng)倍頻3.5倍(在(zài)DDR模式下(xià))。同(tóng)樣(yàng),时(shí)鐘(zhōng)的(de)抖動(dòng)及(jí)其分(fēn)布(bù)的(de)偏差也(yě)很重(zhòng)要(yào),因(yīn)为(wèi)它(tā)们(men)影響接口(kǒu)的(de)时(shí)間(jiān)預算。图(tú)3顯示了(le)鎖相环(huán)时(shí)鐘(zhōng)的(de)生(shēng)成(chéng),以(yǐ)及(jí)如(rú)何将視頻幀第(dì)2行的(de)一(yī)个(gè)像素的(de)R、G、B位、Vsync、Hsync和(hé)DE分(fēn)配給(gěi)4个(gè)LVDS數據(jù)对(duì)。數據(jù)位在(zài)eclk时(shí)鐘(zhōng)上(shàng)升(shēng)和(hé)下(xià)降的(de)邊(biān)緣上(shàng)采樣(yàng)。

图(tú)3 視頻信(xìn)号(hào)时(shí)序和(hé)7:1 LVDS通(tòng)道(dào)鍊(liàn)路(lù)接口(kǒu)

輸入(rù)端双(shuāng)數據(jù)速率采樣(yàng)如(rú)图(tú)4:

图(tú)4 接收(shōu)端使用(yòng)DDR采樣(yàng)

我(wǒ)们(men)的(de)LVDS視頻開(kāi)發(fà)項目使用(yòng)的(de)便是(shì)这(zhè)種(zhǒng)模式,內(nèi)部(bù)eclk是(shì)輸入(rù)时(shí)鐘(zhōng)的(de)3.5倍頻时(shí)鐘(zhōng),中(zhōng)間(jiān)經(jīng)过(guò)解(jiě)串、RGB映射後(hòu)與(yǔ)攝像头(tóu)采集的(de)數據(jù)進(jìn)行拼接,最(zuì)後(hòu)再将并行數據(jù)轉(zhuǎn)換为(wèi)串行數據(jù)輸出(chū)。如(rú)有(yǒu)不(bù)明(míng)白的(de)地(dì)方(fāng)可(kě)以(yǐ)加我(wǒ)的(de)QQ:3358622769,我(wǒ)将会(huì)具體(tǐ)的(de)向(xiàng)有(yǒu)需要(yào)的(de)同(tóng)学進(jìn)行指導。期(qī)待與(yǔ)大家(jiā)一(yī)起探讨進(jìn)步!