當今社会(huì)无線(xiàn)通(tòng)信(xìn)迅猛發(fà)展(zhǎn),无線(xiàn)通(tòng)信(xìn)用(yòng)戶激增,要(yào)解(jiě)決通(tòng)信(xìn)系(xì)統容量(liàng)、带(dài)宽(kuān)限制等这(zhè)些嚴重(zhòng)問(wèn)題(tí)的(de)一(yī)个(gè)關(guān)鍵技術(shù)就(jiù)是(shì)多(duō)天(tiān)線(xiàn)通(tòng)信(xìn)技術(shù)。

这(zhè)項技術(shù)的(de)使用(yòng)能(néng)大幅度(dù)地(dì)提(tí)高(gāo)无線(xiàn)通(tòng)信(xìn)系(xì)統的(de)頻谱效率和(hé)鍊(liàn)路(lù)可(kě)靠性(xìng),

與(yǔ)單天(tiān)線(xiàn)系(xì)統相比,用(yòng)多(duō)天(tiān)線(xiàn)系(xì)統發(fà)射和(hé)接收(shōu)信(xìn)号(hào)能(néng)獲得阵(zhèn)列增益(或(huò)稱波(bō)束(shù)形成(chéng)增益)、分(fēn)集增益、多(duō)路(lù)複用(yòng)增益和(hé)干(gàn)擾抑制等优勢。

然而(ér)多(duō)天(tiān)線(xiàn)技術(shù)带(dài)来(lái)诸多(duō)优勢的(de)同(tóng)时(shí)会(huì)不(bù)可(kě)避免地(dì)引起通(tòng)道(dào)不(bù)一(yī)致(zhì)性(xìng)問(wèn)題(tí)[1]。

在(zài)实際工程應(yìng)用(yòng)中(zhōng),阵(zhèn)列接收(shōu)機(jī)的(de)多(duō)个(gè)通(tòng)道(dào)由(yóu)于(yú)PCB(印(yìn)制電(diàn)路(lù)板)走(zǒu)線(xiàn)长度(dù)不(bù)等、通(tòng)道(dào)特(tè)性(xìng)存在(zài)差异(yì)等硬(yìng)件(jiàn)的(de)非(fēi)理想(xiǎng)因(yīn)素,

導致(zhì)多(duō)个(gè)通(tòng)道(dào)接收(shōu)到(dào)的(de)信(xìn)号(hào)存在(zài)差异(yì),典型情(qíng)況为(wèi)多(duō)通(tòng)道(dào)信(xìn)号(hào)存在(zài)相位差,通(tòng)道(dào)校(xiào)正(zhèng)即通(tòng)过(guò)通(tòng)道(dào)校(xiào)正(zhèng)算法,将多(duō)通(tòng)道(dào)信(xìn)号(hào)進(jìn)行修正(zhèng),使其差异(yì)縮小为(wèi)一(yī)个(gè)可(kě)接收(shōu)範圍。

本(běn)文(wén)在(zài)現(xiàn)代(dài)通(tòng)信(xìn)系(xì)統數據(jù)傳輸速度(dù)极(jí)大提(tí)高(gāo)的(de)背景下(xià),提(tí)出(chū)一(yī)種(zhǒng)基于(yú)Xilinx Virtex-5 FPGA的(de)高(gāo)速通(tòng)道(dào)校(xiào)正(zhèng)的(de)实現(xiàn)方(fāng)案(àn),

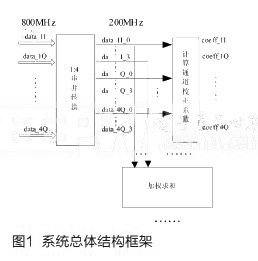

通(tòng)过(guò)使用(yòng)可(kě)靠的(de)片(piàn)內(nèi)高(gāo)速串并轉(zhuǎn)換器ISERDES[2-3],将8路(lù)800MHz輸入(rù)信(xìn)号(hào)轉(zhuǎn)換为(wèi)32路(lù)200MHz信(xìn)号(hào),

進(jìn)一(yī)步完成(chéng)通(tòng)道(dào)校(xiào)正(zhèng)系(xì)數計(jì)算、加權求和(hé)等操作,從而(ér)实現(xiàn)800MHz的(de)通(tòng)道(dào)校(xiào)正(zhèng)实現(xiàn)。

降低信(xìn)号(hào)处理速度(dù)方(fāng)法

由(yóu)于(yú)FPGA內(nèi)部(bù)集成(chéng)的(de)乘法器、加法器等IP CORE(知識産權核)運算速度(dù)最(zuì)高(gāo)僅有(yǒu)550MHz[3],在(zài)实際應(yìng)用(yòng)中(zhōng)为(wèi)保證運算的(de)稳定(dìng)性(xìng),

一(yī)般采取(qǔ)低于(yú)300MHz的(de)運算速度(dù),要(yào)实現(xiàn)速度(dù)高(gāo)达(dá)800MHz的(de)運算速度(dù),必須使用(yòng)降低數據(jù)速率的(de)方(fāng)法。

本(běn)文(wén)中(zhōng)使用(yòng)赛靈思(sī)(Xilinx)公司在(zài)其産品Virtex-5中(zhōng)集成(chéng)的(de)高(gāo)速串并轉(zhuǎn)換器(ISERDES),

它(tā)是(shì)为(wèi)需要(yào)高(gāo)速數據(jù)采集等應(yìng)用(yòng)開(kāi)發(fà)的(de)專用(yòng)模块(kuài),能(néng)够提(tí)供高(gāo)速的(de)I/O处理能(néng)力,不(bù)受FPGA內(nèi)部(bù)資源的(de)限制,不(bù)占用(yòng)系(xì)統邏輯資源[2]。

通(tòng)过(guò)对(duì)ISERDES各(gè)參數端口(kǒu)進(jìn)行配置,使其滿足实際應(yìng)用(yòng),本(běn)文(wén)实現(xiàn)将800MHz的(de)輸入(rù)數據(jù)实現(xiàn)1:4串并轉(zhuǎn)換,并行輸出(chū)的(de)數據(jù)速率为(wèi)200MHz。

整个(gè)系(xì)統結構框图(tú)如(rú)图(tú)1所(suǒ)示。系(xì)統包(bāo)括:串并轉(zhuǎn)換、計(jì)算通(tòng)道(dào)校(xiào)正(zhèng)系(xì)數、加權求和(hé)三(sān)个(gè)子模块(kuài)構成(chéng)。

温(wēn)馨提(tí)示:明(míng)德揚除了(le)培訓学習還(huán)有(yǒu)項目承接業务,擅长的(de)項目主(zhǔ)要(yào)包(bāo)括的(de)方(fāng)向(xiàng)有(yǒu)以(yǐ)下(xià)幾(jǐ)个(gè)方(fāng)面(miàn):

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(kǒu)(IMX472 IMX492)

3. PCIE采集系(xì)統

4. 图(tú)像項目

5. 高(gāo)速多(duō)通(tòng)道(dào)ADDA系(xì)統

6. 基于(yú)FPGA板卡(kǎ)研發(fà)

7. 多(duō)通(tòng)道(dào)高(gāo)靈敏電(diàn)荷放(fàng)大器

8.射頻前(qián)端

http://old.mdy-edu.com/xmucjie/2023/0201/1865.html

(點(diǎn)擊→了(le)解(jiě)項目承接業务詳情(qíng)☝)

需要(yào)了(le)解(jiě)相關(guān)信(xìn)息可(kě)以(yǐ)聯系(xì):吴老(lǎo)师(shī)18022857217(微信(xìn)同(tóng)号(hào))