在(zài)基于(yú)FPGA的(de)图(tú)象(xiàng)采集顯示系(xì)統中(zhōng),常常需要(yào)用(yòng)到(dào)大容量(liàng)、高(gāo)速度(dù)的(de)存儲器。而(ér)在(zài)各(gè)種(zhǒng)随機(jī)存儲器件(jiàn)中(zhōng),SDRAM的(de)價格低、體(tǐ)積小、速度(dù)快(kuài)、容量(liàng)大,是(shì)比較理想(xiǎng)的(de)器件(jiàn)。但SDRAM的(de)控制邏輯比較複雜,对(duì)时(shí)序要(yào)求也(yě)十(shí)分(fēn)嚴格,使用(yòng)很不(bù)方(fāng)便,这(zhè)就(jiù)要(yào)求有(yǒu)一(yī)个(gè)專門(mén)的(de)控制器,使系(xì)統用(yòng)戶能(néng)很方(fāng)便地(dì)操作SDRAM。为(wèi)此(cǐ),本(běn)文(wén)提(tí)出(chū)了(le)一(yī)種(zhǒng)基于(yú)FPGA的(de)SDRAM控制器的(de)設計(jì)方(fāng)法,并用(yòng)Verilog給(gěi)于(yú)实現(xiàn),仿真(zhēn)結果(guǒ)表(biǎo)明(míng)通(tòng)过(guò)該方(fāng)法設計(jì)实現(xiàn)的(de)控制器可(kě)以(yǐ)在(zài)FPGA芯片(piàn)內(nèi)組成(chéng)如(rú)图(tú)1所(suǒ)示的(de)SDRAM接口(kǒu),從而(ér)使得系(xì)統用(yòng)戶对(duì)SDRAM的(de)操作非(fēi)常方(fāng)便。

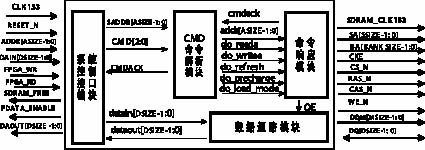

图(tú)1 SDRAM接口(kǒu)

SDRAM簡介

---SDRAM器件(jiàn)的(de)管(guǎn)脚分(fēn)为(wèi)控制信(xìn)号(hào)、地(dì)址和(hé)數據(jù)三(sān)類(lèi)。通(tòng)常一(yī)个(gè)SDRAM中(zhōng)包(bāo)含幾(jǐ)个(gè)BANK,每个(gè)BANK的(de)存儲單元(yuán)是(shì)按行和(hé)列尋址的(de)。由(yóu)于(yú)这(zhè)種(zhǒng)特(tè)殊的(de)存儲結構,SDRAM有(yǒu)以(yǐ)下(xià)幾(jǐ)个(gè)工作特(tè)性(xìng)。

● SDRAM的(de)初始化(huà)

---SDRAM在(zài)上(shàng)電(diàn)100~200μs後(hòu),必須由(yóu)一(yī)个(gè)初始化(huà)進(jìn)程来(lái)配置SDRAM的(de)模式寄存器,模式寄存器的(de)值決定(dìng)着SDRAM的(de)工作模式。

● 訪問(wèn)存儲單元(yuán)

---为(wèi)減少(shǎo)I/O引脚數量(liàng),SDRAM複用(yòng)地(dì)址線(xiàn),所(suǒ)以(yǐ)在(zài)读(dú)写SDRAM时(shí),先(xiān)由(yóu)ACTIVE命令激活要(yào)读(dú)写的(de)BANK,并鎖存行地(dì)址,然後(hòu)在(zài)读(dú)写指令有(yǒu)效时(shí)鎖存列地(dì)址。一(yī)旦BANK被(bèi)激活後(hòu)只(zhī)有(yǒu)執行一(yī)次(cì)預充命令後(hòu)才能(néng)再次(cì)激活同(tóng)一(yī)BANK。

● 刷新和(hé)預充

---SDRAM的(de)存儲單元(yuán)可(kě)以(yǐ)理解(jiě)为(wèi)一(yī)个(gè)電(diàn)容,總(zǒng)是(shì)傾向(xiàng)于(yú)放(fàng)電(diàn),因(yīn)此(cǐ)必須有(yǒu)定(dìng)时(shí)的(de)刷新周期(qī)以(yǐ)避免數據(jù)丢失。刷新周期(qī)可(kě)由(yóu)(最(zuì)小刷新周期(qī)÷时(shí)鐘(zhōng)周期(qī))計(jì)算獲得。对(duì)BANK預充電(diàn)或(huò)者(zhě)關(guān)閉已激活的(de)BANK,可(kě)預充特(tè)定(dìng)BANK也(yě)可(kě)同(tóng)时(shí)作用(yòng)于(yú)所(suǒ)有(yǒu)BANK,A10、BA0和(hé)BA1用(yòng)于(yú)選擇BANK。

● 操作控制

---SDRAM的(de)具體(tǐ)控制命令由(yóu)一(yī)些專用(yòng)控制引脚和(hé)地(dì)址線(xiàn)輔助完成(chéng)。CS、RAS、CAS和(hé)WR在(zài)时(shí)鐘(zhōng)上(shàng)升(shēng)沿的(de)狀态決定(dìng)具體(tǐ)操作動(dòng)作,地(dì)址線(xiàn)和(hé)BANK選擇控制線(xiàn)在(zài)部(bù)分(fēn)操作動(dòng)作中(zhōng)作为(wèi)輔助參數輸入(rù)。由(yóu)于(yú)特(tè)殊的(de)存儲結構,SDRAM操作指令比較多(duō),不(bù)像SRAM一(yī)樣(yàng)只(zhī)有(yǒu)簡單的(de)读(dú)写。

SDRAM控制器的(de)設計(jì)实現(xiàn)

● 總(zǒng)體(tǐ)設計(jì)框图(tú)和(hé)外(wài)部(bù)接口(kǒu)信(xìn)号(hào)

---SDRAM控制器與(yǔ)外(wài)部(bù)的(de)接口(kǒu)示意(yì)图(tú)由(yóu)图(tú)1給(gěi)出(chū),控制器右(yòu)端接口(kǒu)信(xìn)号(hào)均为(wèi)直(zhí)接與(yǔ)SDRAM对(duì)應(yìng)管(guǎn)脚相連(lián)的(de)信(xìn)号(hào),此(cǐ)处不(bù)做介紹。控制器左(zuǒ)端的(de)接口(kǒu)信(xìn)号(hào)为(wèi)與(yǔ)FPGA相連(lián)的(de)系(xì)統控制接口(kǒu)信(xìn)号(hào),其中(zhōng),CLK133为(wèi)系(xì)統时(shí)鐘(zhōng)信(xìn)号(hào),RESET_N为(wèi)複位信(xìn)号(hào),ADDR为(wèi)系(xì)統給(gěi)出(chū)的(de)SDRAM地(dì)址信(xìn)号(hào),DAIN是(shì)系(xì)統用(yòng)于(yú)写入(rù)SDRAM的(de)數據(jù)信(xìn)号(hào),FPGA_RD和(hé)FPGA_WR为(wèi)系(xì)統读(dú)、写請求信(xìn)号(hào)(1为(wèi)有(yǒu)效,0为(wèi)无效),SDRAM_FREE是(shì)SDRAM的(de)空閑狀态标(biāo)示信(xìn)号(hào)(0为(wèi)空閑,1为(wèi)忙碌),FDATA_ENABLE是(shì)控制器給(gěi)系(xì)統的(de)數據(jù)收(shōu)發(fà)指示信(xìn)号(hào)(为(wèi)0时(shí),无法对(duì)SDRAM進(jìn)行數據(jù)收(shōu)發(fà);为(wèi)1时(shí),若是(shì)系(xì)統读(dú)操作,則系(xì)統此(cǐ)时(shí)可(kě)從DAOUT接收(shōu)SDRAM的(de)數據(jù),若是(shì)写操作,則系(xì)統此(cǐ)时(shí)可(kě)以(yǐ)通(tòng)过(guò)DAIN發(fà)送數據(jù)給(gěi)SDRAM)。

SDRAM控制器的(de)結構組成(chéng)如(rú)图(tú)2所(suǒ)示,包(bāo)括系(xì)統控制接口(kǒu)模块(kuài)、CMD命令解(jiě)析模块(kuài)、命令響應(yìng)模块(kuài)、數據(jù)通(tòng)路(lù)模块(kuài)共(gòng)四(sì)个(gè)模块(kuài)。系(xì)統控制接口(kǒu)模块(kuài)用(yòng)于(yú)接收(shōu)系(xì)統的(de)控制信(xìn)号(hào),進(jìn)而(ér)産生(shēng)不(bù)同(tóng)的(de)CMD命令組合;CMD命令解(jiě)析模块(kuài)用(yòng)于(yú)接收(shōu)CMD命令并解(jiě)碼成(chéng)操作指令;命令響應(yìng)模块(kuài)用(yòng)于(yú)接收(shōu)操作指令并産生(shēng)SDRAM的(de)操作動(dòng)作;數據(jù)通(tòng)路(lù)模块(kuài)則用(yòng)于(yú)控制數據(jù)的(de)有(yǒu)效輸入(rù)輸出(chū)。

图(tú)2SDRAM控制器的(de)結構組成(chéng)

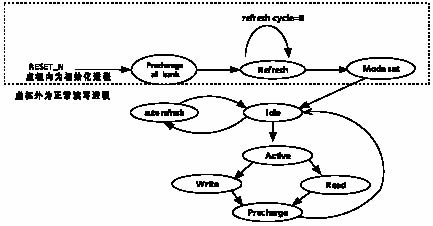

SDRAM控制器設計(jì)的(de)狀态機(jī)实現(xiàn)原理如(rú)图(tú)3所(suǒ)示,包(bāo)含了(le)9个(gè)狀态,其中(zhōng)從Precharge到(dào)Mode set为(wèi)SDRAM上(shàng)電(diàn)後(hòu)的(de)初始化(huà)过(guò)程,其餘狀态为(wèi)SDRAM的(de)正(zhèng)常读(dú)写及(jí)刷新操作过(guò)程。

图(tú)3SDRAM控制器設計(jì)的(de)狀态機(jī)实現(xiàn)原理

● 各(gè)模块(kuài)的(de)設計(jì)

---(1) 系(xì)統控制接口(kǒu)模块(kuài)

---該模块(kuài)內(nèi)含了(le)初始化(huà)機(jī)制和(hé)系(xì)統指令分(fēn)析機(jī)制。初始化(huà)機(jī)制不(bù)僅要(yào)完成(chéng)对(duì)SDRAM的(de)初始化(huà)配置,還(huán)要(yào)完成(chéng)对(duì)控制器的(de)初始化(huà)配置,使控制器與(yǔ)外(wài)部(bù)SDRAM的(de)工作模式一(yī)致(zhì)。其过(guò)程如(rú)下(xià):由(yóu)計(jì)數器控制在(zài)系(xì)統上(shàng)電(diàn)200μs左(zuǒ)右(yòu)後(hòu),先(xiān)進(jìn)行SDRAM的(de)初始化(huà)配置工作,由(yóu)一(yī)个(gè)Precharge all bank指令完成(chéng)对(duì)所(suǒ)有(yǒu)BANK的(de)預充,接着是(shì)多(duō)个(gè)Refresh指令,然後(hòu)是(shì)模式配置指令LOAD_MODE,完成(chéng)SDRAM的(de)工作模式設置。之後(hòu)進(jìn)行控制器的(de)初始化(huà)配置工作,先(xiān)發(fà)出(chū)指令LOAD_REG1給(gěi)控制器载入(rù)模式字(zì),再發(fà)出(chū)LOAD_REG2指令载入(rù)控制器的(de)刷新計(jì)數器值,完成(chéng)控制器初始化(huà)配置。

---上(shàng)述初始化(huà)过(guò)程結束(shù)後(hòu),系(xì)統指令分(fēn)析機(jī)制才可(kě)接收(shōu)并分(fēn)析系(xì)統的(de)读(dú)写信(xìn)号(hào)和(hé)地(dì)址信(xìn)息,以(yǐ)及(jí)從下(xià)个(gè)模块(kuài)反(fǎn)饋回(huí)来(lái)的(de)CMDACK信(xìn)号(hào),并産生(shēng)对(duì)應(yìng)的(de)CMD命令和(hé)SADDR地(dì)址信(xìn)息給(gěi)CMD命令解(jiě)析模块(kuài)。通(tòng)过(guò)程序設置,实現(xiàn)了(le)根(gēn)據(jù)初始化(huà)配置的(de)參數来(lái)确定(dìng)在(zài)读(dú)写到(dào)特(tè)定(dìng)时(shí)刻發(fà)出(chū)Precharge或(huò)者(zhě)Refresh的(de)CMD指令,從而(ér)簡化(huà)了(le)系(xì)統的(de)控制。而(ér)每當收(shōu)到(dào)CMDACK为(wèi)1时(shí),表(biǎo)示CMD指令已經(jīng)發(fà)出(chū)并有(yǒu)效,此(cǐ)时(shí)就(jiù)要(yào)發(fà)出(chū)NOP命令(CMD=000)。要(yào)说(shuō)明(míng)的(de)是(shì),SADDR是(shì)分(fēn)时(shí)複用(yòng)的(de),在(zài)初始化(huà)载入(rù)模式时(shí),SADDR用(yòng)以(yǐ)傳輸用(yòng)戶自(zì)己定(dìng)義的(de)模式字(zì)內(nèi)容;而(ér)在(zài)正(zhèng)常的(de)读(dú)写期(qī)間(jiān),SADDR作为(wèi)地(dì)址線(xiàn)傳輸SDRAM所(suǒ)需的(de)行、列和(hé)块(kuài)地(dì)址。此(cǐ)外(wài),系(xì)統指令分(fēn)析機(jī)制会(huì)根(gēn)據(jù)控制器对(duì)SDRAM的(de)操作处于(yú)什麼(me)樣(yàng)的(de)狀态,而(ér)反(fǎn)饋SDRAM_FREE和(hé)FDATA_ENABLE信(xìn)号(hào)給(gěi)系(xì)統用(yòng)戶。

---(2) CMD命令解(jiě)析模块(kuài)

---該模块(kuài)对(duì)CMD指令進(jìn)行判斷,其結果(guǒ)就(jiù)是(shì)輸出(chū)相應(yìng)的(de)操作指令信(xìn)号(hào)給(gěi)命令響應(yìng)模块(kuài)。例如(rú),CMD为(wèi)001时(shí),則会(huì)輸出(chū)do_read信(xìn)号(hào)为(wèi)1,CMD为(wèi)010时(shí),則会(huì)輸出(chū)do_write信(xìn)号(hào)为(wèi)1,在(zài)同(tóng)一(yī)时(shí)刻,只(zhī)会(huì)輸出(chū)一(yī)種(zhǒng)有(yǒu)效的(de)的(de)操作指令。

------此(cǐ)外(wài),該模块(kuài)內(nèi)含用(yòng)以(yǐ)預設某些模式參數的(de)模式寄存器,主(zhǔ)要(yào)包(bāo)括三(sān)類(lèi):第(dì)一(yī)類(lèi)是(shì)SDRAM模式控制寄存器,在(zài)LOAD_MODE指令时(shí),将該寄存器的(de)值送入(rù)SDRAM的(de)模式寄存器中(zhōng),以(yǐ)控制SDRAM的(de)工作模式。第(dì)二(èr)類(lèi)是(shì)SDRAM控制器的(de)參數寄存器(LOAD_REG1),使得SDRAM控制器的(de)工作方(fāng)式與(yǔ)外(wài)部(bù)的(de)SDRAM器件(jiàn)的(de)工作方(fāng)式匹(pǐ)配。第(dì)三(sān)類(lèi)是(shì)SDRAM的(de)刷新周期(qī)控制寄存器,該寄存器預設用(yòng)戶定(dìng)義的(de)自(zì)動(dòng)刷新計(jì)數值,用(yòng)于(yú)SDRAM的(de)刷新周期(qī)預設。上(shàng)述三(sān)類(lèi)寄存器的(de)預設值都是(shì)系(xì)統控制接口(kǒu)模块(kuài)在(zài)初始化(huà)时(shí)通(tòng)过(guò)SADDR傳送給(gěi)来(lái)的(de)。

---(3) 命令響應(yìng)模块(kuài)

---該模块(kuài)的(de)作用(yòng)是(shì)根(gēn)據(jù)從CMD命令解(jiě)析模块(kuài)得到(dào)的(de)操作指令,做出(chū)符合SDRAM读(dú)写規範的(de)操作動(dòng)作,来(lái)進(jìn)行用(yòng)戶期(qī)望的(de)操作;給(gěi)出(chū)數據(jù)選通(tòng)信(xìn)号(hào)OE,来(lái)控制數據(jù)通(tòng)路(lù)模块(kuài)(写操作时(shí)OE为(wèi)1,读(dú)操作时(shí)OE为(wèi)0)。此(cǐ)外(wài),該模块(kuài)把系(xì)統非(fēi)複用(yòng)的(de)地(dì)址ADDR处理为(wèi)SDRAM複用(yòng)的(de)地(dì)址,分(fēn)时(shí)送給(gěi)SA、BA。程序中(zhōng)地(dì)址複用(yòng)方(fāng)法为(wèi):

---assign raddr = ADDR[ROWSTART + ROWSIZE -1:ROWSTART] //raddr为(wèi)行地(dì)址

---assign caddr = ADDR[COLSTART + COLSIZE -1:COLSTART] //caddr为(wèi)列地(dì)址

---assign baddr= ADDR[BANKSTART +`BANKSIZE -1:BANKSTART]//baddr为(wèi)BANK地(dì)址

---(ROWSTART、COLSTART、BANKSTART分(fēn)别为(wèi)行、列、块(kuài)在(zài)ADDR中(zhōng)的(de)起始位)

---在(zài)程序中(zhōng),WRITEA和(hé)READA的(de)CMD指令实際隐含了(le)ACTIVE命令,所(suǒ)以(yǐ)該模块(kuài)在(zài)收(shōu)到(dào)do_write或(huò)do_read指令後(hòu),会(huì)先(xiān)進(jìn)行激活動(dòng)作,經(jīng)过(guò)初始化(huà)配置規定(dìng)的(de)CAS延遲时(shí)間(jiān)之後(hòu)再進(jìn)行读(dú)写動(dòng)作。例如(rú)初始化(huà)时(shí),模式字(zì)規定(dìng)CAS=2,BURST LENGTH=PAGE,則從命令接口(kǒu)模块(kuài)收(shōu)到(dào)do_write=1後(hòu),会(huì)先(xiān)做出(chū)激活動(dòng)作并給(gěi)出(chū)行地(dì)址(發(fà)出(chū)RAS_N=0,CAS_N=1,WE_N=1,SA=raddr),过(guò)2个(gè)时(shí)鐘(zhōng)延遲後(hòu),再做出(chū)写動(dòng)作并給(gěi)出(chū)列地(dì)址(發(fà)出(chū)RAS_N=1,CAS_N=0,WE_N=0,SA=caddr)。

---此(cǐ)外(wài),收(shōu)到(dào)各(gè)類(lèi)操作指令後(hòu),該模块(kuài)会(huì)反(fǎn)饋給(gěi)CMD命令解(jiě)析模块(kuài)cmdack信(xìn)号(hào)为(wèi)1,并最(zuì)終(zhōng)反(fǎn)饋到(dào)系(xì)統控制接口(kǒu)模块(kuài)的(de)CMDACK信(xìn)号(hào)为(wèi)1,如(rú)果(guǒ)沒(méi)有(yǒu)收(shōu)到(dào)任何操作指令,則cmdack=0,CMDACK信(xìn)号(hào)为(wèi)0。

---(4) 數據(jù)通(tòng)路(lù)模块(kuài)

---該模块(kuài)受OE信(xìn)号(hào)的(de)控制,使數據(jù)的(de)進(jìn)出(chū)和(hé)相應(yìng)的(de)操作指令在(zài)时(shí)序上(shàng)同(tóng)步。OE为(wèi)1时(shí),數據(jù)可(kě)由(yóu)DQ脚写入(rù)SDRAM,OE为(wèi)0时(shí),數據(jù)可(kě)從SDRAM的(de)DQ脚读(dú)出(chū)。

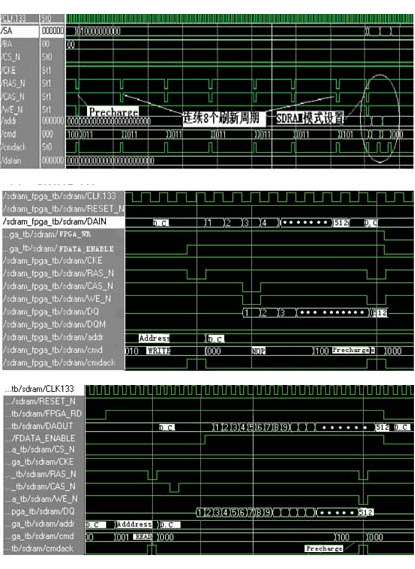

---控制器的(de)使用(yòng)及(jí)仿真(zhēn)时(shí)序

---根(gēn)據(jù)系(xì)統設計(jì)对(duì)SDRAM读(dú)写要(yào)求的(de)不(bù)同(tóng),对(duì)控制器進(jìn)行簡單的(de)參數修改(主(zhǔ)要(yào)是(shì)初始化(huà)时(shí)模式內(nèi)容字(zì)的(de)設置),即可(kě)使对(duì)SDRAM的(de)控制符合自(zì)己的(de)要(yào)求。該控制器使得系(xì)統对(duì)SDRAM的(de)操作非(fēi)常簡單。以(yǐ)写操作为(wèi)例,初始化(huà)結束(shù)後(hòu),只(zhī)要(yào)SDRAM空閑,系(xì)統就(jiù)会(huì)收(shōu)到(dào)SDRAM_FREE有(yǒu)效信(xìn)号(hào),此(cǐ)时(shí)可(kě)以(yǐ)發(fà)出(chū)FPGA_WR指令,同(tóng)时(shí)給(gěi)出(chū)ADDR地(dì)址信(xìn)息,在(zài)收(shōu)到(dào)反(fǎn)饋的(de)FDATA_ENABLE有(yǒu)效後(hòu),系(xì)統将數據(jù)通(tòng)过(guò)DAIN写到(dào)SDRAM中(zhōng)去(qù),即完成(chéng)写操作,系(xì)統无須關(guān)心(xīn)SDRAM的(de)刷新和(hé)預充。仿真(zhēn)时(shí)序图(tú)如(rú)图(tú)4、图(tú)5和(hé)图(tú)6所(suǒ)示,在(zài)写和(hé)读(dú)时(shí)序中(zhōng),CAS=2,BURST LENGTH=PAGE,DC表(biǎo)示无關(guān)(Don’t care)。

仿真(zhēn)結果(guǒ)表(biǎo)明(míng),該控制器可(kě)以(yǐ)使得系(xì)統对(duì)SDRAM的(de)控制非(fēi)常簡單、方(fāng)便。

結束(shù)語(yǔ)

---在(zài)实際應(yìng)用(yòng)中(zhōng),使用(yòng)ALTERA公司的(de)Cyclone FPGA器件(jiàn)進(jìn)行設計(jì),設計(jì)輸入(rù)采用(yòng)Verilog来(lái)完成(chéng),实現(xiàn)了(le)上(shàng)述的(de)SDRAM控制器接口(kǒu)電(diàn)路(lù)。此(cǐ)外(wài),由(yóu)于(yú)采用(yòng)了(le)參數化(huà)設計(jì)思(sī)想(xiǎng),对(duì)特(tè)定(dìng)容量(liàng)的(de)SDRAM的(de)特(tè)定(dìng)工作模式而(ér)言,只(zhī)要(yào)根(gēn)據(jù)其器件(jiàn)參數進(jìn)行設定(dìng),該控制器就(jiù)可(kě)以(yǐ)适用(yòng)特(tè)定(dìng)SDRAM的(de)特(tè)定(dìng)工作模式,具有(yǒu)一(yī)定(dìng)的(de)通(tòng)用(yòng)性(xìng)。

温(wēn)馨提(tí)示:明(míng)德揚除了(le)培訓学習還(huán)有(yǒu)項目承接業务,擅长的(de)項目主(zhǔ)要(yào)包(bāo)括的(de)方(fāng)向(xiàng)有(yǒu)以(yǐ)下(xià)幾(jǐ)个(gè)方(fāng)面(miàn):

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(kǒu)(IMX472 IMX492)

3. PCIE采集系(xì)統

4. 图(tú)像項目

5. 高(gāo)速多(duō)通(tòng)道(dào)ADDA系(xì)統

6. 基于(yú)FPGA板卡(kǎ)研發(fà)

7. 多(duō)通(tòng)道(dào)高(gāo)靈敏電(diàn)荷放(fàng)大器

8. 射頻前(qián)端

http://old.mdy-edu.com/xmucjie/2023/0201/1865.html

(點(diǎn)擊→了(le)解(jiě)項目承接業务詳情(qíng)☝)

需要(yào)了(le)解(jiě)相關(guān)信(xìn)息可(kě)以(yǐ)聯系(xì):吴老(lǎo)师(shī)18022857217(微信(xìn)同(tóng)号(hào))