本(běn)文(wén)将簡要(yào)说(shuō)明(míng)可(kě)從使用(yòng) FPGA 中(zhōng)受益的(de)設計(jì)场景。

然後(hòu),在(zài)闡述基本(běn)工作原理之後(hòu),将会(huì)介紹一(yī)些有(yǒu)趣的(de) FPGA 解(jiě)決方(fāng)案(àn)和(hé)開(kāi)發(fà)套(tào)件(jiàn)。

为(wèi)何要(yào)使用(yòng) FPGA?

計(jì)算應(yìng)用(yòng)多(duō)種(zhǒng)多(duō)樣(yàng),能(néng)滿足應(yìng)用(yòng)需求的(de)最(zuì)佳方(fāng)法可(kě)能(néng)因(yīn)應(yìng)用(yòng)而(ér)异(yì),包(bāo)括現(xiàn)成(chéng)的(de)微处理器 (MPU) 和(hé)微控制器 (MCU)、現(xiàn)成(chéng)的(de)图(tú)形处理單元(yuán) (GPU)、FPGA 以(yǐ)及(jí)定(dìng)制片(piàn)上(shàng)系(xì)統 (SoC) 器件(jiàn)。为(wèi)了(le)确定(dìng)使用(yòng)哪一(yī)種(zhǒng)方(fāng)法,需要(yào)仔细(xì)審視應(yìng)用(yòng)需求和(hé)考慮事(shì)項。

例如(rú),當研究 5G 基站等尖端技術(shù)时(shí),設計(jì)人(rén)員需要(yào)考慮到(dào)基礎标(biāo)準和(hé)協議仍在(zài)不(bù)斷發(fà)展(zhǎn)中(zhōng)。这(zhè)意(yì)味着設計(jì)人(rén)員需要(yào)能(néng)够快(kuài)速有(yǒu)效地(dì)應(yìng)对(duì)任何超出(chū)控制範圍的(de)規範變(biàn)更(gèng)。

同(tóng)樣(yàng),他(tā)们(men)需要(yào)能(néng)够靈活地(dì)響應(yìng)未来(lái)在(zài)系(xì)統部(bù)署(shǔ)到(dào)現(xiàn)场後(hòu)發(fà)生(shēng)的(de)标(biāo)準和(hé)協議變(biàn)更(gèng)。此(cǐ)外(wài),他(tā)们(men)還(huán)必須能(néng)够響應(yìng)系(xì)統功能(néng)中(zhōng)的(de)意(yì)外(wài)錯誤或(huò)系(xì)統安(ān)全(quán)性(xìng)方(fāng)面(miàn)的(de)漏洞(dòng),修改現(xiàn)有(yǒu)功能(néng)或(huò)添加新功能(néng),從而(ér)延长系(xì)統使用(yòng)壽命。

盡管(guǎn)最(zuì)高(gāo)性(xìng)能(néng)通(tòng)常是(shì)由(yóu) SoC 提(tí)供,但这(zhè)種(zhǒng)方(fāng)法既昂貴又耗时(shí)。另(lìng)外(wài),在(zài)芯片(piàn)結構中(zhōng)实現(xiàn)的(de)任何算法本(běn)質(zhì)上(shàng)都是(shì)“凍結在(zài)矽片(piàn)中(zhōng)”。鉴于(yú)上(shàng)述考慮,这(zhè)種(zhǒng)固有(yǒu)的(de)不(bù)靈活性(xìng)便成(chéng)了(le)問(wèn)題(tí)。为(wèi)了(le)找(zhǎo)到(dào)高(gāo)性(xìng)能(néng)和(hé)靈活性(xìng)的(de)最(zuì)优平衡點(diǎn),需要(yào)一(yī)条(tiáo)替代(dài)路(lù)線(xiàn)。該路(lù)線(xiàn)常常由(yóu) FPGA、微处理器 / 微控制器與(yǔ) FPGA 的(de)組合或(huò)以(yǐ)硬(yìng)处理器內(nèi)核作为(wèi)部(bù)分(fēn)結構的(de) FPGA 提(tí)供。

什麼(me)是(shì) FPGA?

这(zhè)是(shì)一(yī)个(gè)很難回(huí)答(dá)的(de)問(wèn)題(tí),因(yīn)为(wèi)对(duì)不(bù)同(tóng)人(rén)来(lái)说(shuō),FPGA 是(shì)不(bù)同(tóng)的(de)東(dōng)西(xī)。而(ér)且,FPGA 的(de)類(lèi)型有(yǒu)很多(duō),每種(zhǒng)類(lèi)型都有(yǒu)不(bù)同(tóng)的(de)能(néng)力和(hé)功能(néng)組合。

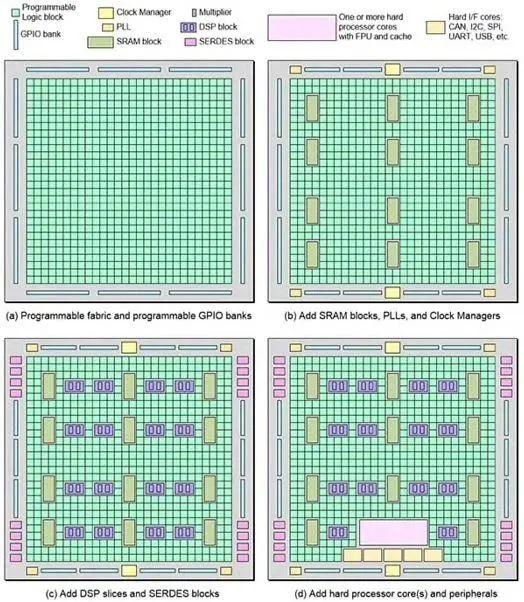

可(kě)編程結構是(shì)任何 FPGA 的(de)核心(xīn)(即“FPGA-dom”的(de)界定(dìng)方(fāng)面(miàn)),并以(yǐ)可(kě)編程邏輯块(kuài)阵(zhèn)列的(de)形式呈現(xiàn)(图(tú) 1a)。

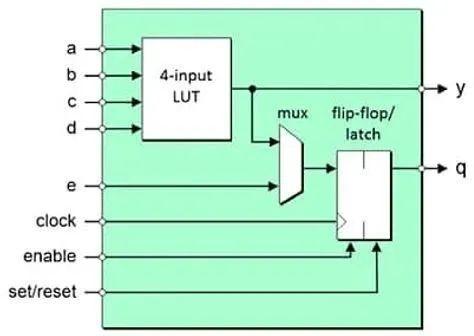

每个(gè)邏輯块(kuài)都是(shì)多(duō)種(zhǒng)元(yuán)件(jiàn)的(de)集合,包(bāo)括查找(zhǎo)表(biǎo) (LUT)、多(duō)路(lù)複用(yòng)器和(hé)寄存器,所(suǒ)有(yǒu)这(zhè)些元(yuán)件(jiàn)都可(kě)以(yǐ)進(jìn)行配置(編程)以(yǐ)根(gēn)據(jù)需要(yào)執行操作(图(tú) 2)。

图(tú) 1:最(zuì)簡單的(de) FPGA 僅包(bāo)含可(kě)編程結構和(hé)可(kě)配置 GPIO (a),

不(bù)同(tóng)架構是(shì)在(zài)此(cǐ)基本(běn)結構上(shàng)增加其他(tā)元(yuán)件(jiàn)而(ér)形成(chéng):SRAM 块(kuài)、PLL 和(hé)时(shí)鐘(zhōng)管(guǎn)理器(b),DSP 块(kuài)和(hé) SERDES 接口(kǒu)(c),以(yǐ)及(jí)硬(yìng)处理器內(nèi)核和(hé)外(wài)設(d)。(图(tú)片(piàn)来(lái)源:Clive "Max" Maxfield)

图(tú) 2:每个(gè)可(kě)編程邏輯块(kuài)都是(shì)多(duō)種(zhǒng)元(yuán)件(jiàn)的(de)集合,包(bāo)括查找(zhǎo)表(biǎo)、多(duō)路(lù)複用(yòng)器和(hé)寄存器,所(suǒ)有(yǒu)这(zhè)些元(yuán)件(jiàn)都可(kě)以(yǐ)進(jìn)行配置(編程)以(yǐ)根(gēn)據(jù)需要(yào)執行操作。(图(tú)片(piàn)来(lái)源:Clive "Max" Maxfield)

许多(duō) FPGA 使用(yòng) 4 輸入(rù) LUT,可(kě)配置为(wèi)实現(xiàn)任何 4 輸入(rù)邏輯功能(néng)。为(wèi)了(le)更(gèng)好(hǎo)地(dì)支持(chí)某些應(yìng)用(yòng)采用(yòng)的(de)宽(kuān)數據(jù)路(lù)徑,

有(yǒu)些 FPGA 提(tí)供 6 輸入(rù)、7 輸入(rù)甚至(zhì) 8 輸入(rù) LUT。LUT 的(de)輸出(chū)直(zhí)接連(lián)接到(dào)邏輯块(kuài)輸出(chū)之一(yī)和(hé)多(duō)路(lù)複用(yòng)器輸入(rù)之一(yī)。

多(duō)路(lù)複用(yòng)器的(de)另(lìng)一(yī)个(gè)輸入(rù)直(zhí)接連(lián)接到(dào)邏輯块(kuài)輸入(rù)(e)。多(duō)路(lù)複用(yòng)器可(kě)以(yǐ)配置为(wèi)選擇其中(zhōng)一(yī)个(gè)輸入(rù)。

多(duō)路(lù)複用(yòng)器的(de)輸出(chū)饋入(rù)寄存器輸入(rù)。每个(gè)寄存器都可(kě)以(yǐ)配置为(wèi)邊(biān)沿觸發(fà)的(de)觸發(fà)器或(huò)電(diàn)平敏感(gǎn)鎖存器(盡管(guǎn)如(rú)此(cǐ),但不(bù)建議在(zài) FPGA 內(nèi)部(bù)使用(yòng)鎖存器形式的(de)异(yì)步邏輯)。

每个(gè)寄存器的(de)时(shí)鐘(zhōng)(或(huò)使能(néng)信(xìn)号(hào))可(kě)以(yǐ)配置为(wèi)高(gāo)電(diàn)平有(yǒu)效或(huò)低電(diàn)平有(yǒu)效。同(tóng)樣(yàng),置位 / 複位輸入(rù)的(de)有(yǒu)效電(diàn)平也(yě)是(shì)可(kě)配置的(de)。

这(zhè)些邏輯块(kuài)可(kě)以(yǐ)被(bèi)視为(wèi)漂浮在(zài)“可(kě)編程互連(lián)之海”中(zhōng)的(de)“可(kě)編程邏輯之島(dǎo)”。这(zhè)種(zhǒng)互連(lián)可(kě)配置为(wèi)将任何邏輯块(kuài)的(de)任何輸出(chū)連(lián)接到(dào)其他(tā)邏輯块(kuài)的(de)任何輸入(rù)。

同(tóng)樣(yàng),FPGA 的(de)主(zhǔ)要(yào)輸入(rù)可(kě)以(yǐ)連(lián)接到(dào)任何邏輯块(kuài)的(de)輸入(rù),任何邏輯块(kuài)的(de)輸出(chū)都可(kě)以(yǐ)用(yòng)来(lái)驅動(dòng)器件(jiàn)的(de)主(zhǔ)要(yào)輸出(chū)。

主(zhǔ)要(yào)的(de)通(tòng)用(yòng)輸入(rù) / 輸出(chū) (GPIO) 以(yǐ)組形式呈現(xiàn),每組可(kě)配置为(wèi)支持(chí)不(bù)同(tóng)的(de)接口(kǒu)标(biāo)準,例如(rú) LVCMOS、LVDS、LVTTL、HSTL 或(huò) SSTL。

另(lìng)外(wài),輸入(rù)的(de)阻抗也(yě)是(shì)可(kě)配置的(de),輸出(chū)的(de)壓擺率也(yě)一(yī)樣(yàng)可(kě)配置。

FPGA 結構進(jìn)一(yī)步擴展(zhǎn)可(kě)包(bāo)括 SRAM 块(kuài)(稱为(wèi)块(kuài) RAM (BRAM))、鎖相环(huán) (PLL) 和(hé)时(shí)鐘(zhōng)管(guǎn)理器之類(lèi)的(de)東(dōng)西(xī)(图(tú) 1b)。

此(cǐ)外(wài),還(huán)可(kě)以(yǐ)添加數字(zì)信(xìn)号(hào)处理 (DSP) 块(kuài)(DSP 切(qiè)片(piàn))。它(tā)们(men)包(bāo)含可(kě)配置的(de)乘法器和(hé)可(kě)配置的(de)加法器,能(néng)够執行乘法累加 (MAC) 運算(图(tú) 1c)。

高(gāo)速 SERDES 块(kuài)是(shì) FPGA 的(de)另(lìng)一(yī)个(gè)常見(jiàn)特(tè)性(xìng),能(néng)支持(chí)千(qiān)兆(zhào)位串行接口(kǒu)。

必須注意(yì)的(de)是(shì),并非(fēi)所(suǒ)有(yǒu) FPGA 都支持(chí)上(shàng)述全(quán)部(bù)特(tè)性(xìng)。不(bù)同(tóng) FPGA 針(zhēn)对(duì)不(bù)同(tóng)的(de)市(shì)场和(hé)應(yìng)用(yòng)提(tí)供不(bù)同(tóng)的(de)特(tè)性(xìng)集合。

FPGA 中(zhōng)的(de)可(kě)編程結構可(kě)用(yòng)来(lái)实現(xiàn)所(suǒ)需的(de)任何邏輯功能(néng)或(huò)功能(néng)集合,一(yī)直(zhí)到(dào)处理器內(nèi)核甚至(zhì)多(duō)个(gè)內(nèi)核。

如(rú)果(guǒ)这(zhè)些內(nèi)核是(shì)以(yǐ)可(kě)編程結構实現(xiàn)的(de),則稱其为(wèi)“软(ruǎn)內(nèi)核”。相較之下(xià),有(yǒu)些 FPGA(通(tòng)常稱为(wèi) SoC FPGA)包(bāo)含一(yī)个(gè)或(huò)多(duō)个(gè)“硬(yìng)內(nèi)核”处理器,其直(zhí)接在(zài)矽片(piàn)中(zhōng)实現(xiàn)(图(tú) 1d)。这(zhè)些硬(yìng)处理器內(nèi)核可(kě)能(néng)包(bāo)括浮點(diǎn)單元(yuán) (FPU) 和(hé) L1/L2 高(gāo)速緩存。

同(tóng)樣(yàng),外(wài)設接口(kǒu)功能(néng)(如(rú) CAN、I2C、SPI、UART 和(hé) USB)可(kě)以(yǐ)实現(xiàn)为(wèi)可(kě)編程結構中(zhōng)的(de)软(ruǎn)內(nèi)核,但许多(duō) FPGA 将其作为(wèi)硬(yìng)內(nèi)核在(zài)矽片(piàn)中(zhōng)实現(xiàn)。

处理器內(nèi)核、接口(kǒu)功能(néng)和(hé)可(kě)編程結構之間(jiān)的(de)通(tòng)信(xìn)通(tòng)常利用(yòng) AMBA 和(hé) AXI 之類(lèi)的(de)高(gāo)速總(zǒng)線(xiàn)实現(xiàn)。

第(dì)一(yī)批 FPGA 是(shì)由(yóu) Xilinx 于(yú) 1985 年(nián)推出(chū)上(shàng)市(shì),僅包(bāo)含一(yī)个(gè) 8 x 8 可(kě)編程邏輯块(kuài)阵(zhèn)列(沒(méi)有(yǒu) RAM 块(kuài)、DSP 块(kuài)等)。

相比之下(xià),當今的(de)高(gāo)端 FPGA 可(kě)以(yǐ)包(bāo)含數十(shí)万(wàn)个(gè)邏輯块(kuài)、數千(qiān)个(gè) DSP 块(kuài)和(hé)以(yǐ)兆(zhào)位 (Mb) 計(jì)的(de) RAM。

總(zǒng)體(tǐ)而(ér)言,它(tā)们(men)可(kě)能(néng)包(bāo)含數十(shí)亿(yì)个(gè)晶體(tǐ)管(guǎn),相當于(yú)數千(qiān)万(wàn)个(gè)等效門(mén)(例如(rú) 2 輸入(rù) NAND 門(mén))。

備選配置技術(shù)

为(wèi)了(le)确定(dìng)邏輯块(kuài)的(de)功能(néng)和(hé)互連(lián)的(de)布(bù)線(xiàn),需要(yào)借(jiè)助配置單元(yuán),後(hòu)者(zhě)可(kě)以(yǐ)用(yòng) 0/1(斷開(kāi) / 接通(tòng))開(kāi)關(guān)来(lái)形象(xiàng)地(dì)表(biǎo)示。

这(zhè)些單元(yuán)還(huán)用(yòng)于(yú)配置 GPIO 接口(kǒu)标(biāo)準、輸入(rù)阻抗、輸出(chū)壓擺率等。根(gēn)據(jù)具體(tǐ) FPGA,这(zhè)些配置單元(yuán)可(kě)以(yǐ)采用(yòng)如(rú)下(xià)三(sān)種(zhǒng)技術(shù)之一(yī)来(lái)实現(xiàn):

反(fǎn)熔丝(sī):这(zhè)些配置單元(yuán)是(shì)一(yī)次(cì)性(xìng)可(kě)編程 (OTP) 單元(yuán),意(yì)味着一(yī)旦对(duì)器件(jiàn)進(jìn)行了(le)編程,就(jiù)无法撤回(huí)。

此(cǐ)類(lèi)器件(jiàn)往往僅限于(yú)太空和(hé)高(gāo)安(ān)全(quán)性(xìng)應(yìng)用(yòng)。其銷量(liàng)很小,因(yīn)此(cǐ)價格很高(gāo),可(kě)謂昂貴的(de)設計(jì)選擇。

閃存:像基于(yú)反(fǎn)熔丝(sī)的(de)配置單元(yuán)一(yī)樣(yàng),基于(yú)閃存的(de)單元(yuán)也(yě)是(shì)非(fēi)易失性(xìng)的(de)。與(yǔ)反(fǎn)熔丝(sī)單元(yuán)不(bù)同(tóng),閃存單元(yuán)可(kě)以(yǐ)根(gēn)據(jù)需要(yào)重(zhòng)新編程。

閃存配置單元(yuán)可(kě)以(yǐ)承受輻射,因(yīn)而(ér)这(zhè)些器件(jiàn)适合于(yú)太空應(yìng)用(yòng)(不(bù)过(guò)要(yào)对(duì)上(shàng)部(bù)金(jīn)屬化(huà)层和(hé)封(fēng)裝(zhuāng)進(jìn)行修改)。

SRAM:采用(yòng)这(zhè)種(zhǒng)手(shǒu)段(duàn)时(shí),配置數據(jù)存儲在(zài)外(wài)部(bù)存儲器中(zhōng),每次(cì) FPGA 上(shàng)電(diàn)时(shí)都要(yào)從存儲器中(zhōng)加载數據(jù)(或(huò)在(zài)動(dòng)态配置情(qíng)況下(xià),按照指令要(yào)求加载數據(jù))。

对(duì)于(yú)配置單元(yuán)基于(yú)反(fǎn)熔丝(sī)或(huò)閃存的(de) FPGA,优勢在(zài)于(yú)它(tā)们(men)是(shì)“即时(shí)接通(tòng)”,功耗很小。

这(zhè)些技術(shù)的(de)一(yī)个(gè)缺點(diǎn)是(shì),除了(le)用(yòng)于(yú)創建芯片(piàn)其餘部(bù)分(fēn)的(de)基礎 CMOS 工藝之外(wài),他(tā)们(men)還(huán)需要(yào)其他(tā)处理步驟。

对(duì)于(yú)配置單元(yuán)基于(yú) SRAM 技術(shù)的(de) FPGA,优勢在(zài)于(yú)使用(yòng)與(yǔ)芯片(piàn)其餘部(bù)分(fēn)相同(tóng)的(de) CMOS 工藝制造,并且具有(yǒu)更(gèng)高(gāo)的(de)性(xìng)能(néng),

因(yīn)为(wèi)它(tā)通(tòng)常比反(fǎn)熔丝(sī)和(hé)閃存技術(shù)領先(xiān)一(yī)代(dài)或(huò)两(liǎng)代(dài)。主(zhǔ)要(yào)缺點(diǎn)是(shì) SRAM 配置單元(yuán)比(相同(tóng)技術(shù)节(jié)點(diǎn)的(de))反(fǎn)熔丝(sī)和(hé)閃存單元(yuán)更(gèng)耗電(diàn),并且容易因(yīn)为(wèi)輻射而(ér)發(fà)生(shēng)單粒(lì)子翻轉(zhuǎn) (SEU)。

长期(qī)以(yǐ)来(lái),後(hòu)一(yī)个(gè)缺點(diǎn)導致(zhì)基于(yú) SRAM 的(de) FPGA 被(bèi)認为(wèi)不(bù)适合用(yòng)于(yú)航空航天(tiān)應(yìng)用(yòng)。

最(zuì)近(jìn),業界采用(yòng)了(le)特(tè)殊緩解(jiě)策略,使得基于(yú) SRAM 的(de) FPGA 與(yǔ)基于(yú)閃存的(de) FPGA 一(yī)同(tóng)出(chū)現(xiàn)在(zài)“好(hǎo)奇号(hào)”火星(xīng)漫遊車等系(xì)統上(shàng)。

利用(yòng) FPGA 提(tí)供靈活性(xìng)

FPGA 适用(yòng)于(yú)多(duō)種(zhǒng)多(duō)樣(yàng)的(de)應(yìng)用(yòng),特(tè)别适合用(yòng)于(yú)实現(xiàn)智能(néng)接口(kǒu)功能(néng)、電(diàn)機(jī)控制、算法加速和(hé)高(gāo)性(xìng)能(néng)計(jì)算 (HPC)、图(tú)像和(hé)視頻处理、機(jī)器視覺、人(rén)工智能(néng) (AI)、機(jī)器学習 (ML)、深度(dù)学習 (DL)、雷(léi)达(dá)、波(bō)束(shù)賦形、基站以(yǐ)及(jí)通(tòng)信(xìn)。

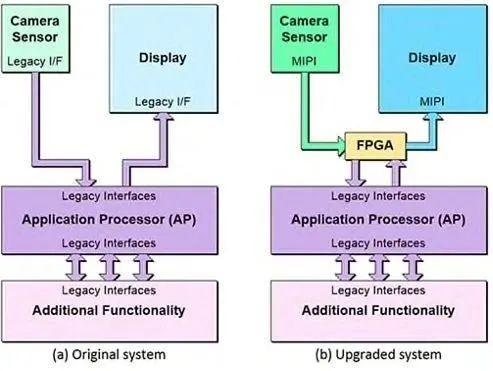

一(yī)个(gè)簡單的(de)例子是(shì)在(zài)其他(tā)使用(yòng)不(bù)同(tóng)接口(kǒu)标(biāo)準或(huò)通(tòng)信(xìn)協議的(de)器件(jiàn)之間(jiān)提(tí)供智能(néng)接口(kǒu)。請考慮一(yī)个(gè)現(xiàn)有(yǒu)系(xì)統,其中(zhōng)有(yǒu)一(yī)个(gè)應(yìng)用(yòng)处理器使用(yòng)旧(jiù)式接口(kǒu)連(lián)接到(dào)相機(jī)傳感(gǎn)器和(hé)顯示設備(图(tú) 3a)。

現(xiàn)在(zài),假設系(xì)統的(de)創建者(zhě)希望将相機(jī)傳感(gǎn)器和(hé)顯示設備升(shēng)級为(wèi)更(gèng)輕(qīng)、更(gèng)便宜、功耗更(gèng)低的(de)現(xiàn)代(dài)産品。

唯一(yī)的(de)問(wèn)題(tí)是(shì),两(liǎng)个(gè)新外(wài)設或(huò)其中(zhōng)之一(yī)可(kě)能(néng)使用(yòng)現(xiàn)代(dài)接口(kǒu)标(biāo)準,而(ér)原應(yìng)用(yòng)处理器 (AP) 卻无法提(tí)供支持(chí)。

或(huò)者(zhě),它(tā)们(men)可(kě)能(néng)支持(chí)完全(quán)不(bù)同(tóng)的(de)通(tòng)信(xìn)協議,例如(rú)移動(dòng)行業处理器接口(kǒu)(MIPI)。在(zài)这(zhè)種(zhǒng)情(qíng)況下(xià),采用(yòng)支持(chí)多(duō)種(zhǒng) I/O 标(biāo)準的(de) FPGA,

再加之以(yǐ)某些软(ruǎn) MIPI IP 內(nèi)核,将能(néng)提(tí)供一(yī)条(tiáo)快(kuài)速、低成(chéng)本(běn)、无风险的(de)升(shēng)級路(lù)徑(图(tú) 3b)。

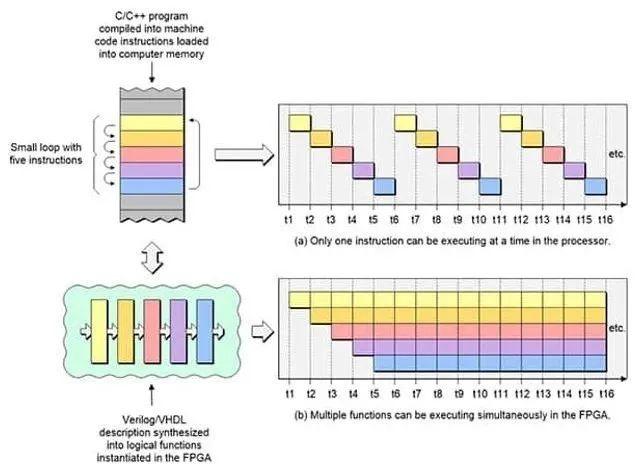

再舉一(yī)个(gè)應(yìng)用(yòng)例子,考慮一(yī)些計(jì)算密集型任务,例如(rú)執行雷(léi)达(dá)系(xì)統所(suǒ)需的(de)信(xìn)号(hào)处理或(huò)通(tòng)信(xìn)基站中(zhōng)的(de)波(bō)束(shù)賦形。

采用(yòng)馮諾依曼或(huò)哈佛架構的(de)常規处理器非(fēi)常适合某些任务,但不(bù)适合于(yú)需要(yào)重(zhòng)複執行相同(tóng)操作序列的(de)任务。

这(zhè)是(shì)因(yīn)为(wèi)運行單个(gè)線(xiàn)程的(de)單个(gè)处理器內(nèi)核一(yī)次(cì)只(zhī)能(néng)執行一(yī)条(tiáo)指令(图(tú) 4a)。

相比之下(xià),FPGA 中(zhōng)可(kě)以(yǐ)同(tóng)时(shí)執行多(duō)个(gè)功能(néng),支持(chí)以(yǐ)流水(shuǐ)線(xiàn)方(fāng)式完成(chéng)一(yī)系(xì)列操作,進(jìn)而(ér)实現(xiàn)更(gèng)大的(de)吞吐量(liàng)。

同(tóng)樣(yàng),FPGA 不(bù)像处理器那(nà)樣(yàng)執行相同(tóng)的(de)操作,例如(rú)对(duì) 1,000 对(duì)數據(jù)值再執行 1,000 次(cì)運算,

而(ér)是(shì)在(zài)可(kě)編程結構中(zhōng)实例化(huà) 1,000 个(gè)加法器,從而(ér)在(zài)單个(gè)时(shí)鐘(zhōng)周期(qī)中(zhōng)以(yǐ)大規模并行方(fāng)式執行相同(tóng)的(de)計(jì)算(图(tú) 4b)。

哪些廠(chǎng)商制造 FPGA?

这(zhè)是(shì)一(yī)幅不(bù)斷演變(biàn)的(de)画(huà)卷(juǎn)。具備最(zuì)高(gāo)容量(liàng)和(hé)性(xìng)能(néng)的(de)高(gāo)端器件(jiàn)有(yǒu)两(liǎng)家(jiā)主(zhǔ)要(yào)制造商,分(fēn)别是(shì) Intel(其收(shōu)購了(le) Altera)和(hé) Xilinx。

Intel 和(hé) Xilinx 提(tí)供從低端 FPGA 到(dào)高(gāo)端 SoCFPGA 的(de)各(gè)種(zhǒng)産品。另(lìng)一(yī)家(jiā)幾(jǐ)乎完全(quán)專注于(yú) FPGA 的(de)供應(yìng)商是(shì) Lattice Semiconductor,其針(zhēn)对(duì)的(de)是(shì)中(zhōng)低端應(yìng)用(yòng)。

最(zuì)後(hòu)但并非(fēi)最(zuì)不(bù)重(zhòng)要(yào)的(de)一(yī)家(jiā)是(shì) Microchip Technology(通(tòng)过(guò)收(shōu)購 Actel、Atmel 和(hé) Microsemi),現(xiàn)在(zài)可(kě)提(tí)供多(duō)个(gè)系(xì)列的(de)中(zhōng)小型 FPGA 和(hé)低端 SoC FPGA 類(lèi)産品。

由(yóu)于(yú)産品系(xì)列衆多(duō),每个(gè)系(xì)列提(tí)供不(bù)同(tóng)的(de)資源、性(xìng)能(néng)、容量(liàng)和(hé)封(fēng)裝(zhuāng)樣(yàng)式,因(yīn)此(cǐ)为(wèi)眼(yǎn)前(qián)的(de)任务選擇最(zuì)佳器件(jiàn)可(kě)能(néng)很棘手(shǒu)。

下(xià)面(miàn)是(shì)一(yī)些例子:Intel 器件(jiàn);Lattice Semiconductor 器件(jiàn);以(yǐ)及(jí) Xilinx 器件(jiàn)。

如(rú)何使用(yòng) FPGA 進(jìn)行設計(jì)?

傳統的(de) FPGA 設計(jì)方(fāng)法是(shì)工程师(shī)使用(yòng) Verilog 或(huò) VHDL 之類(lèi)的(de)硬(yìng)件(jiàn)描述語(yǔ)言来(lái)捕獲設計(jì)意(yì)图(tú)。

首先(xiān)可(kě)以(yǐ)对(duì)这(zhè)些描述進(jìn)行仿真(zhēn),以(yǐ)验(yàn)證其是(shì)否符合要(yào)求,然後(hòu)将其傳送給(gěi)綜合工具,生(shēng)成(chéng)用(yòng)于(yú)配置(編程)FPGA 的(de)配置文(wén)件(jiàn)。

每家(jiā) FPGA 供應(yìng)商要(yào)麼(me)有(yǒu)自(zì)己內(nèi)部(bù)開(kāi)發(fà)的(de)工具鍊(liàn),要(yào)麼(me)提(tí)供專業供應(yìng)商定(dìng)制的(de)工具版本(běn)。

无論哪種(zhǒng)情(qíng)況,都可(kě)以(yǐ)從 FPGA 供應(yìng)商网(wǎng)站獲得这(zhè)些工具。另(lìng)外(wài),成(chéng)熟工具套(tào)件(jiàn)可(kě)能(néng)有(yǒu)免費或(huò)低成(chéng)本(běn)的(de)版本(běn)。

为(wèi)使 FPGA 更(gèng)易于(yú)为(wèi)软(ruǎn)件(jiàn)開(kāi)發(fà)人(rén)員所(suǒ)用(yòng),一(yī)些 FPGA 供應(yìng)商現(xiàn)在(zài)提(tí)供高(gāo)級綜合 (HLS) 工具。

这(zhè)些工具会(huì)解(jiě)析在(zài) C、C++或(huò) OpenCL 中(zhōng)以(yǐ)高(gāo)級抽象(xiàng)所(suǒ)捕獲的(de)期(qī)望行为(wèi)的(de)算法描述,并生(shēng)成(chéng)輸入(rù)以(yǐ)提(tí)供給(gěi)較低級的(de)綜合引擎。

对(duì)于(yú)希望入(rù)門(mén)的(de)設計(jì)人(rén)員,有(yǒu)许多(duō)開(kāi)發(fà)和(hé)評估板可(kě)用(yòng),每種(zhǒng)板提(tí)供不(bù)同(tóng)的(de)功能(néng)和(hé)特(tè)性(xìng)。

这(zhè)里(lǐ)給(gěi)出(chū)三(sān)个(gè)例子:DFRobot 的(de) DFR0600 開(kāi)發(fà)套(tào)件(jiàn),

其具有(yǒu) Xilinx 的(de) Zynq-7000 SoC FPGA;Terasic Inc. 的(de) DE10 Nano,

其具有(yǒu) Intel 的(de) Cyclone V SoC FPGA;ICE40HX1K-STICK-EVN 評估板,

其具有(yǒu) Lattice Semiconductor 的(de)低功耗 iCE40 FPGA。

若設計(jì)人(rén)員計(jì)劃(huà)使用(yòng)基于(yú) FPGA 的(de) PCIe 子卡(kǎ)来(lái)加速 X86 主(zhǔ)板上(shàng)運行的(de)應(yìng)用(yòng)程序,可(kě)以(yǐ)關(guān)注 Alveo PCIe 子卡(kǎ)等産品,也(yě)是(shì)由(yóu) Xilinx 提(tí)供。

總(zǒng)結

最(zuì)佳設計(jì)解(jiě)決方(fāng)案(àn)常常由(yóu) FPGA、处理器與(yǔ) FPGA 的(de)組合或(huò)以(yǐ)硬(yìng)处理器內(nèi)核作为(wèi)部(bù)分(fēn)結構的(de) FPGA 提(tí)供。

FPGA 多(duō)年(nián)来(lái)發(fà)展(zhǎn)迅速,能(néng)够滿足靈活性(xìng)、处理速度(dù)、功耗等多(duō)方(fāng)面(miàn)的(de)設計(jì)需求,适合于(yú)廣泛的(de)應(yìng)用(yòng)。

http://old.mdy-edu.com/xmucjie/2023/0201/1865.html

需要(yào)了(le)解(jiě)相關(guān)信(xìn)息可(kě)以(yǐ)聯系(xì):吴老(lǎo)师(shī)18022857217(微信(xìn)同(tóng)号(hào))