最(zuì)近(jìn)有(yǒu)很多(duō)人(rén)在(zài)問(wèn),学習 FPGA 到(dào)底是(shì)選擇 Intel altera 的(de)還(huán)是(shì) xilinx 的(de)呢?

于(yú)是(shì)我(wǒ)就(jiù)苦(kǔ)口(kǒu)婆心(xīn)的(de)说(shuō)了(le)一(yī)大堆(duī),中(zhōng)心(xīn)思(sī)想(xiǎng)大概就(jiù)是(shì),学習 FPGA 一(yī)定(dìng)要(yào)学習 FPGA 的(de)設計(jì)思(sī)想(xiǎng)以(yǐ)及(jí)設計(jì)原理,

不(bù)要(yào)糾結于(yú)單一(yī)的(de)实验(yàn)平台(tái)或(huò)者(zhě)操作软(ruǎn)件(jiàn),因(yīn)为(wèi)你想(xiǎng)在(zài)这(zhè)个(gè)行業越走(zǒu)越高(gāo)的(de)話(huà),廣度(dù)和(hé)深度(dù)都是(shì)要(yào)有(yǒu)所(suǒ)了(le)解(jiě)的(de)。

初期(qī)学習的(de)时(shí)候尤其注重(zhòng)動(dòng)手(shǒu),選擇一(yī)款操作平台(tái)以(yǐ)及(jí)操作软(ruǎn)件(jiàn)是(shì)为(wèi)了(le)讓你更(gèng)好(hǎo)的(de)去(qù)動(dòng)手(shǒu)做,

而(ér)不(bù)是(shì)讓你在(zài)这(zhè)款软(ruǎn)件(jiàn)或(huò)者(zhě)实验(yàn)平台(tái)去(qù)做文(wén)章(zhāng),因(yīn)为(wèi)不(bù)懂原理的(de)話(huà),換个(gè)环(huán)境你同(tóng)樣(yàng)是(shì)什麼(me)都不(bù)明(míng)白。

尤其是(shì)現(xiàn)在(zài)的(de)科技公司産品更(gèng)新升(shēng)級換代(dài)還(huán)比較快(kuài),要(yào)学会(huì)去(qù)掌握最(zuì)核心(xīn)的(de)知識點(diǎn)才是(shì)王道(dào)。

下(xià)面(miàn),咱们(men)就(jiù)来(lái)簡單聊聊 Intel altera 和(hé) Xilinx 的(de) FPGA 區(qū)别,

欢迎大家(jiā)一(yī)起交流,三(sān)人(rén)行,必有(yǒu)我(wǒ)师(shī),共(gòng)同(tóng)学習,共(gòng)同(tóng)進(jìn)步。

对(duì)于(yú) Intel altera 和(hé) Xilinx 的(de) FPGA,本(běn)人(rén)認为(wèi)可(kě)以(yǐ)分(fēn)为(wèi)两(liǎng)个(gè)方(fāng)面(miàn)去(qù)比較一(yī)下(xià),基本(běn)邏輯資源和(hé)內(nèi)部(bù)基本(běn)架構。

從目前(qián)企業中(zhōng)做開(kāi)發(fà)使用(yòng)的(de)廣泛性(xìng)来(lái)说(shuō),Xilinx 占得比重(zhòng)确实是(shì)大一(yī)些,但是(shì)從其他(tā)方(fāng)面(miàn)来(lái)说(shuō),比如(rú)價格,相对(duì)而(ér)言 Intel altera 的(de)便宜些。

对(duì)于(yú)两(liǎng)者(zhě)的(de)特(tè)點(diǎn),Xilinx 的(de)短(duǎn)線(xiàn)資源非(fēi)常豐富,这(zhè)樣(yàng)在(zài)实現(xiàn)的(de)时(shí)候,布(bù)線(xiàn)的(de)成(chéng)功率很高(gāo),尤其是(shì)邏輯做得比較滿的(de)时(shí)候。

而(ér) Intel altera 的(de) FPGA 的(de)短(duǎn)線(xiàn)資源經(jīng)常不(bù)够用(yòng),經(jīng)常要(yào)占用(yòng) LE 来(lái)充當布(bù)線(xiàn)資源,这(zhè)也(yě)是(shì)为(wèi)什麼(me) Intel altera 的(de) FPGA 可(kě)以(yǐ)便宜的(de)原因(yīn),

資源少(shǎo)些當然便宜,但是(shì)如(rú)果(guǒ)你是(shì)高(gāo)手(shǒu),也(yě)能(néng)把他(tā)的(de)性(xìng)能(néng)發(fà)揮得很好(hǎo)。

另(lìng)外(wài)就(jiù)是(shì)關(guān)于(yú)块(kuài) RAM,Xilinx 的(de)双(shuāng)口(kǒu) RAM 是(shì)真(zhēn)的(de),Intel altera 的(de)沒(méi)有(yǒu)双(shuāng)口(kǒu) RAM,

如(rú)果(guǒ)你要(yào)实現(xiàn)真(zhēn)正(zhèng)的(de)双(shuāng)口(kǒu) RAM,只(zhī)能(néng)用(yòng)两(liǎng)块(kuài) RAM 来(lái)背靠背地(dì)实現(xiàn),这(zhè)樣(yàng)你的(de) RAM 資源就(jiù)少(shǎo)了(le)一(yī)半,如(rú)果(guǒ)你的(de)應(yìng)用(yòng)对(duì)片(piàn)內(nèi)双(shuāng)口(kǒu) RAM 的(de)需求很重(zhòng)要(yào),用(yòng) Intel altera 的(de)就(jiù)劃(huà)不(bù)来(lái)。

下(xià)面(miàn)咱们(men)就(jiù)從我(wǒ)刚才说(shuō)的(de)基本(běn)邏輯資源和(hé)內(nèi)部(bù)基本(běn)架構这(zhè)两(liǎng)个(gè)方(fāng)面(miàn)来(lái)聊聊。

1、基本(běn)邏輯資源

基本(běn)的(de)邏輯資源我(wǒ)建議大家(jiā)可(kě)以(yǐ)去(qù)看(kàn)看(kàn)两(liǎng)家(jiā)的(de)芯片(piàn)做个(gè)比較,今天(tiān)时(shí)間(jiān)有(yǒu)限就(jiù)不(bù)給(gěi)各(gè)位詳談了(le),通(tòng)过(guò)比較你会(huì)發(fà)現(xiàn)我(wǒ)上(shàng)面(miàn)说(shuō)的(de)還(huán)是(shì)有(yǒu)點(diǎn)道(dào)理的(de)。

2、內(nèi)部(bù)基本(běn)架構

從 1985 年(nián) Xilinx 公司推出(chū)第(dì)一(yī)片(piàn) FPGA 到(dào)現(xiàn)在(zài),FPGA 的(de)使用(yòng)已經(jīng)有(yǒu) 30 多(duō)年(nián)的(de)曆史了(le)。

目前(qián)主(zhǔ)流市(shì)场的(de) FPGA 主(zhǔ)要(yào)還(huán)是(shì) Xilinx 和(hé) Intel altera 两(liǎng)大系(xì)列,下(xià)面(miàn)分(fēn)别来(lái)介紹下(xià)它(tā)们(men)各(gè)自(zì)的(de)基本(běn)結構組成(chéng)。

Xilinx 的(de) FPGA 主(zhǔ)要(yào)由(yóu)以(yǐ)下(xià)單元(yuán)結構組成(chéng):可(kě)配置邏輯块(kuài)(CLB)、时(shí)鐘(zhōng)管(guǎn)理模块(kuài)(CMT)、存儲器(RAM/FIFO)、數字(zì)信(xìn)号(hào)处理模块(kuài)(DSP)和(hé)一(yī)些專用(yòng)模块(kuài)。

以(yǐ) Virtex-5 为(wèi)例,簡單介紹下(xià)各(gè)模块(kuài)的(de)功能(néng)。

1、可(kě)配置邏輯块(kuài)(CLB)

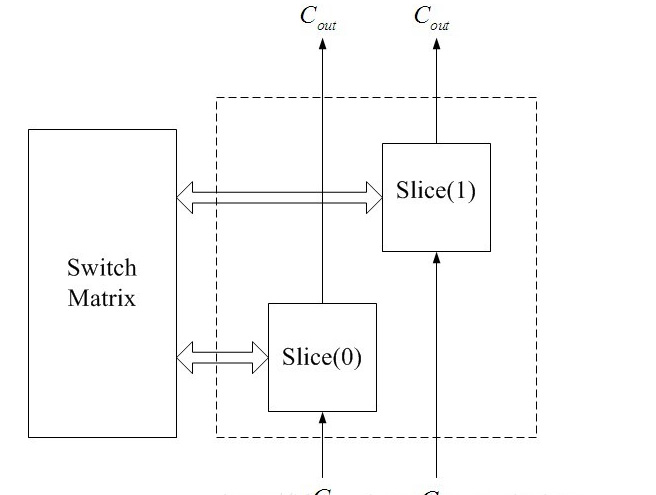

CLB 是(shì) FPGA 中(zhōng)組成(chéng)設計(jì)邏輯的(de)主(zhǔ)要(yào)資源,也(yě)是(shì)電(diàn)路(lù)設計(jì)中(zhōng)工作的(de)主(zhǔ)要(yào)对(duì)象(xiàng),

下(xià)面(miàn)对(duì) CLB 的(de)內(nèi)外(wài)結構做一(yī)个(gè)簡單介紹。FPGA 的(de)邏輯就(jiù)是(shì)由(yóu)阵(zhèn)列排布(bù)的(de) CLB 实現(xiàn)的(de),每个(gè) CLB 單元(yuán)都和(hé)一(yī)个(gè)開(kāi)關(guān)阵(zhèn)列相連(lián),并受其控制以(yǐ)实現(xiàn)邏輯,如(rú)下(xià)图(tú)所(suǒ)示:

每一(yī)个(gè) CLB 中(zhōng)包(bāo)含有(yǒu)两(liǎng)个(gè)基本(běn)結構(Slice),每个(gè)基本(běn)結構中(zhōng)包(bāo)含 4 个(gè)查找(zhǎo)表(biǎo)(LUT)、4 个(gè)存儲單元(yuán)、廣函(hán)數多(duō)路(lù)器(Wide_function Multiplexer)和(hé)進(jìn)位邏輯,

这(zhè)種(zhǒng)基本(běn)結構(Slice)稱为(wèi) SLICEL。另(lìng)外(wài),有(yǒu)些基本(běn)結構(Slice)中(zhōng)還(huán)包(bāo)含使用(yòng) RAM 存儲數據(jù)的(de)功能(néng)和(hé)使用(yòng) 32 位寄存器移位的(de)功能(néng),支持(chí)这(zhè)些功能(néng)的(de)基本(běn)結構稱为(wèi) SLICEM。

2、时(shí)鐘(zhōng)管(guǎn)理模块(kuài)(CMT)

时(shí)鐘(zhōng)管(guǎn)理模块(kuài)(CMT)用(yòng)于(yú)産生(shēng)高(gāo)質(zhì)量(liàng)的(de)时(shí)鐘(zhōng),以(yǐ) Virtex-5 系(xì)列器件(jiàn)为(wèi)例,CMT 包(bāo)括两(liǎng)个(gè) 數字(zì)时(shí)鐘(zhōng)管(guǎn)理單元(yuán)(DCM)和(hé)一(yī)个(gè)鎖相环(huán)電(diàn)路(lù)(PLL)。

3、存儲器(RAM/FIFO)

現(xiàn)代(dài) Xilinx 的(de) FPGA 都有(yǒu)內(nèi)部(bù)的(de)存儲器块(kuài),以(yǐ) Virtex-5 为(wèi)例,內(nèi)部(bù)包(bāo)含若干(gàn)块(kuài) RAM,每一(yī)块(kuài) 36KB,并且 RAM 的(de)大小可(kě)以(yǐ)靈活配置。

Virtex-5 內(nèi)的(de) RAM 是(shì)同(tóng)步的(de)双(shuāng)口(kǒu) RAM,并且可(kě)以(yǐ)配置为(wèi)多(duō)速率的(de) FIFO 存儲器,极(jí)大地(dì)提(tí)高(gāo)了(le)設計(jì)的(de)靈活性(xìng)。

4、數字(zì)信(xìn)号(hào)处理模块(kuài)(DSP)

大多(duō)數的(de) FPGA 産品都提(tí)供了(le) DSP。

5、其他(tā)專用(yòng)模块(kuài)

除了(le)上(shàng)述模块(kuài)外(wài),在(zài)現(xiàn)代(dài)的(de) Xilinx 的(de) FPGA 産品中(zhōng)還(huán)有(yǒu)一(yī)些其他(tā)專用(yòng)模块(kuài),

例如(rú):Rocket IO 千(qiān)兆(zhào)位級收(shōu)發(fà)器、PCI Express 端點(diǎn)模块(kuài)和(hé)三(sān)态以(yǐ)太网(wǎng) MAC 模块(kuài)等。

Intel altera 的(de)産品一(yī)般包(bāo)括如(rú)下(xià)單元(yuán)結構:邏輯阵(zhèn)列模块(kuài)(LAB)、TriMatrix 存儲器模块(kuài)(RAM)、數字(zì)信(xìn)号(hào)处理模块(kuài)(DSP)和(hé)鎖相环(huán)模块(kuài)(PLL)。

下(xià)面(miàn)以(yǐ) Startix II 器件(jiàn)为(wèi)例说(shuō)明(míng) Intel altera 公司産品的(de)結構。

1、邏輯阵(zhèn)列模块(kuài)(LAB)

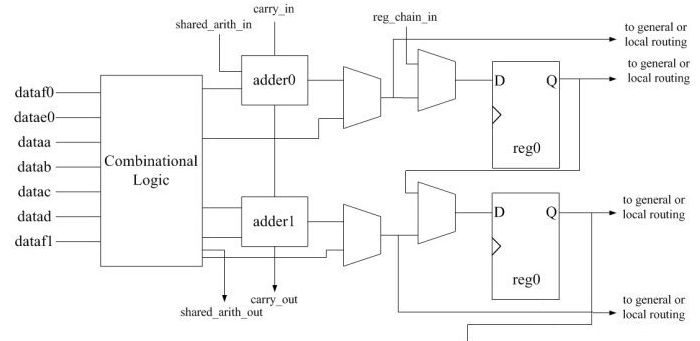

邏輯阵(zhèn)列模块(kuài)(LAB)的(de)主(zhǔ)要(yào)結構是(shì) 8 个(gè)适應(yìng)邏輯模块(kuài)(ALM),還(huán)包(bāo)括一(yī)些進(jìn)位鍊(liàn)和(hé)控制邏輯等結構。适應(yìng)邏輯模块(kuài)(ALM)是(shì) Stratix II 器件(jiàn)的(de)基本(běn)模块(kuài),其結構如(rú)下(xià)图(tú)。

每个(gè) ALM 中(zhōng)都包(bāo)含了(le)两(liǎng)个(gè)可(kě)編程的(de)寄存器、两(liǎng)个(gè)專用(yòng)全(quán)加器、一(yī)个(gè)進(jìn)位鍊(liàn)、一(yī)个(gè)共(gòng)享算術(shù)鍊(liàn)和(hé)一(yī)个(gè)寄存器鍊(liàn)。

需要(yào)注意(yì)的(de)是(shì),在(zài)上(shàng)图(tú)所(suǒ)示的(de)組合邏輯块(kuài)(Combinational Logic)中(zhōng)包(bāo)含了(le)两(liǎng)个(gè) 4 輸入(rù) 4 查找(zhǎo)表(biǎo)(LUT)和(hé) 4 个(gè)三(sān)輸入(rù)的(de)查找(zhǎo)表(biǎo)。

2、 存儲器模块(kuài)(RAM)

Stratix II 器件(jiàn)具有(yǒu) TriMatrix 存儲結構,它(tā)包(bāo)括 3 種(zhǒng)大小的(de)嵌入(rù)式 RAM 块(kuài)。

TriMatrix 存儲器包(bāo)括 512 位的(de) M512 块(kuài)、4Kb 的(de) M4K 块(kuài)和(hé) 512Kb 的(de) M-RAM 块(kuài),每个(gè)都可(kě)以(yǐ)配置支持(chí)各(gè)種(zhǒng)特(tè)性(xìng)。

3、 數字(zì)信(xìn)号(hào)处理模块(kuài)(DSP)

DSP 块(kuài)結構是(shì)为(wèi)实現(xiàn)多(duō)種(zhǒng) 最(zuì)大性(xìng)能(néng)和(hé)最(zuì)小邏輯資源利用(yòng)率的(de) DSP 功能(néng)而(ér)优化(huà)的(de)。

4、 鎖相环(huán)(PLL)

Stratix II 器件(jiàn)具有(yǒu)多(duō)达(dá) 12 个(gè)鎖相环(huán)(PLL)和(hé) 48 个(gè)独立系(xì)統时(shí)鐘(zhōng),可(kě)以(yǐ)作为(wèi)中(zhōng)央时(shí)鐘(zhōng)管(guǎn)理器滿足系(xì)統时(shí)序需求。

以(yǐ)上(shàng)可(kě)以(yǐ)看(kàn)出(chū),Xilinx 與(yǔ) Intel altera 的(de) FPGA 的(de)結構最(zuì)大不(bù)同(tóng)還(huán)是(shì)其邏輯單元(yuán)部(bù)分(fēn):Xilinx 的(de)邏輯單元(yuán)基本(běn)組成(chéng)为(wèi)可(kě)配置邏輯模块(kuài)(CLB),而(ér) Intel altera 的(de)为(wèi) LAB,

但更(gèng)深一(yī)层講,CLB 和(hé) LAB 里(lǐ)面(miàn)也(yě)都是(shì)由(yóu) LUT、觸發(fà)器等構成(chéng)的(de)。两(liǎng)个(gè)公司的(de) FPGA 組成(chéng)各(gè)有(yǒu)特(tè)點(diǎn),这(zhè)也(yě)決定(dìng)了(le)它(tā)们(men)的(de) FPGA 産品在(zài)功能(néng)上(shàng)各(gè)有(yǒu)特(tè)點(diǎn)。

總(zǒng)的(de)来(lái)说(shuō),Xilinx 家(jiā)独有(yǒu) 可(kě)配置邏輯块(kuài)(CLB)/Slice,Intel altera 家(jiā)独有(yǒu)邏輯阵(zhèn)列模块(kuài)(LAB),可(kě)以(yǐ)这(zhè)麼(me)理解(jiě)。簡單聊聊,希望对(duì)各(gè)位大俠学習理解(jiě)有(yǒu)所(suǒ)幫助。

http://old.mdy-edu.com/xmucjie/2023/0201/1865.html