在(zài)掌握FPGA基本(běn)知識以(yǐ)及(jí)數字(zì)图(tú)像处理基礎之後(hòu),

還(huán)需要(yào)準備的(de)硬(yìng)件(jiàn)有(yǒu)——

1块(kuài)FPGA開(kāi)發(fà)板MP801(含有(yǒu)顯示接口(kǒu),攝像头(tóu)接口(kǒu)),

1个(gè)入(rù)門(mén)級的(de)攝像头(tóu)(0v7670),

在(zài)正(zhèng)式開(kāi)啟FPGA图(tú)像处理開(kāi)發(fà)之旅之前(qián),务必要(yào)使用(yòng)FPGA驅動(dòng)攝像头(tóu)視頻顯示,同(tóng)时(shí)要(yào)掌握攝像头(tóu)驅動(dòng)和(hé)液晶屏驅動(dòng)接口(kǒu)和(hé)时(shí)序,最(zuì)重(zhòng)要(yào)就(jiù)是(shì)要(yào)能(néng)够進(jìn)行視頻流Modesim仿真(zhēn)。

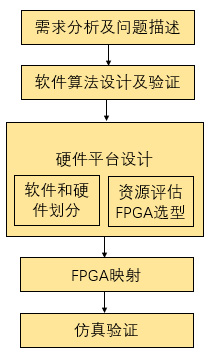

一(yī)个(gè)常規的(de)FPGA图(tú)像处理開(kāi)發(fà)流程是(shì)由(yóu)需求分(fēn)析及(jí)問(wèn)題(tí)描述、软(ruǎn)件(jiàn)算法設計(jì)及(jí)验(yàn)證、硬(yìng)件(jiàn)平台(tái)設計(jì)、FPGA映射以(yǐ)及(jí)仿真(zhēn)验(yàn)證幾(jǐ)部(bù)分(fēn)組成(chéng)。如(rú)下(xià)图(tú)所(suǒ)示

一(yī)、需求分(fēn)析及(jí)問(wèn)題(tí)描述

1.1 系(xì)統的(de)功能(néng)。也(yě)就(jiù)是(shì)你要(yào)做什麼(me),需要(yào)一(yī)个(gè)詳细(xì)的(de)图(tú)像处理後(hòu)的(de)預期(qī)結果(guǒ)说(shuō)明(míng)。

1.2 系(xì)統的(de)性(xìng)能(néng)。完成(chéng)这(zhè)个(gè)系(xì)統的(de)指标(biāo)是(shì)什麼(me),对(duì)于(yú)实时(shí)的(de)图(tú)像处理来(lái)说(shuō)。系(xì)統所(suǒ)允许的(de)最(zuì)大延时(shí)以(yǐ)及(jí)需要(yào)每秒(miǎo)所(suǒ)处理的(de)幀數是(shì)比較關(guān)鍵的(de)两(liǎng)个(gè)指标(biāo)。同(tóng)时(shí)比如(rú)采用(yòng)的(de)攝像头(tóu)的(de)分(fēn)辨率、焦距等指标(biāo),還(huán)有(yǒu)車牌(pái)識别的(de)識别率要(yào)求等。

1.3系(xì)統的(de)工作环(huán)境。图(tú)像处理受光(guāng)照的(de)影響因(yīn)素很大,因(yīn)此(cǐ)考慮系(xì)統的(de)工作环(huán)境对(duì)後(hòu)期(qī)算法的(de)選擇极(jí)其重(zhòng)要(yào)。還(huán)需要(yào)考慮要(yào)契合所(suǒ)工作的(de)機(jī)械位置,对(duì)板子形狀體(tǐ)積等影響。

二(èr)、软(ruǎn)件(jiàn)算法設計(jì)及(jí)其验(yàn)證

在(zài)進(jìn)行FPGA图(tú)像開(kāi)發(fà)之前(qián),首要(yào)做的(de)就(jiù)是(shì)软(ruǎn)件(jiàn)算法設計(jì)及(jí)其验(yàn)證,其中(zhōng)软(ruǎn)件(jiàn)算法複雜性(xìng)会(huì)对(duì),硬(yìng)件(jiàn)的(de)架構,硬(yìng)件(jiàn)的(de)選型以(yǐ)及(jí)資源的(de)消耗。因(yīn)此(cǐ)做FPGA图(tú)像開(kāi)發(fà)不(bù)直(zhí)接在(zài)FPGA上(shàng)做,因(yīn)为(wèi)後(hòu)期(qī)的(de)編譯,調試将会(huì)花費很长时(shí)間(jiān)。

在(zài)拿到(dào)需求之後(hòu),我(wǒ)们(men)一(yī)般首先(xiān)要(yào)做的(de)就(jiù)是(shì)使用(yòng)Matlab/opncnv软(ruǎn)件(jiàn)算法验(yàn)證,不(bù)斷的(de)調試仿真(zhēn),選取(qǔ)一(yī)个(gè)最(zuì)优的(de)方(fāng)案(àn);然後(hòu)嘗試将串行的(de)软(ruǎn)件(jiàn)算法以(yǐ)及(jí)软(ruǎn)件(jiàn)封(fēng)裝(zhuāng)的(de)函(hán)數,

改写成(chéng)适合FPGA处理的(de)形式,在(zài)進(jìn)行進(jìn)一(yī)步仿真(zhēn)验(yàn)證。其中(zhōng)最(zuì)重(zhòng)要(yào)的(de)一(yī)點(diǎn)就(jiù)是(shì)精度(dù)問(wèn)題(tí),因(yīn)为(wèi)FPGA不(bù)善于(yú)处理浮點(diǎn)運算,因(yīn)此(cǐ)要(yào)考慮浮點(diǎn)到(dào)定(dìng)點(diǎn)的(de)轉(zhuǎn)化(huà),

这(zhè)樣(yàng)做,當然会(huì)带(dài)来(lái)精度(dù)的(de)丢失,因(yīn)此(cǐ)需要(yào)評估精度(dù)对(duì)系(xì)統的(de)影響,在(zài)滿足要(yào)求範圍內(nèi),進(jìn)而(ér)来(lái)确定(dìng)FPGA中(zhōng)定(dìng)點(diǎn)轉(zhuǎn)換的(de)位數。舉一(yī)个(gè)例子:

計(jì)算3.145/2(1.573);系(xì)統要(yào)求的(de)精度(dù)在(zài)0.01之內(nèi),在(zài)FPGA計(jì)算中(zhōng)可(kě)以(yǐ)首先(xiān)将3.145擴大256倍取(qǔ)整後(hòu)为(wèi)805進(jìn)行計(jì)算;得到(dào)[805/2]=402,然後(hòu)在(zài)縮小256倍(右(yòu)移8bit)等于(yú)1.570;可(kě)以(yǐ)看(kàn)到(dào)滿足系(xì)統精度(dù)要(yào)求。

三(sān)、硬(yìng)件(jiàn)平台(tái)設計(jì)

3.1软(ruǎn)件(jiàn)和(hé)硬(yìng)件(jiàn)劃(huà)分(fēn)

这(zhè)里(lǐ)所(suǒ)说(shuō)的(de)硬(yìng)件(jiàn)指的(de)是(shì)由(yóu)FPGA邏輯实現(xiàn),软(ruǎn)件(jiàn)是(shì)由(yóu)DSP、ARM、單片(piàn)機(jī)編程实現(xiàn),像計(jì)算量(liàng)較大的(de)預处理算法(形态学濾波(bō)、sobel算子和(hé)均值濾波(bō)等)可(kě)以(yǐ)交由(yóu)FPGA加入(rù)处理,像一(yī)些涉及(jí)到(dào)複雜浮點(diǎn)運算或(huò)者(zhě)FPGA不(bù)易实現(xiàn)的(de)可(kě)以(yǐ)交由(yóu)软(ruǎn)件(jiàn)編程实現(xiàn),达(dá)到(dào)软(ruǎn)硬(yìng)協同(tóng)工作。

3.1資源評估和(hé)FPGA選型

在(zài)硬(yìng)件(jiàn)方(fāng)案(àn)确定(dìng)後(hòu),在(zài)系(xì)統選型之前(qián),很有(yǒu)必要(yào)对(duì)系(xì)統資源的(de)預估,对(duì)图(tú)像处理系(xì)統来(lái)講,肯定(dìng)会(huì)涉及(jí)到(dào)诸如(rú)行緩存,幀緩存,以(yǐ)及(jí)顯存,不(bù)可(kě)避免的(de)会(huì)使用(yòng)到(dào)片(piàn)上(shàng)資源(寄存器,SRAM資源),

同(tóng)时(shí)也(yě)会(huì)預留一(yī)些調試的(de)片(piàn)上(shàng)資源(SigaltapII),一(yī)般片(piàn)內(nèi)資源較多(duō)的(de)FPGA比較貴,像大的(de)幀緩存可(kě)以(yǐ)考慮存儲在(zài)片(piàn)外(wài)資源上(shàng)。

四(sì)、FPGA映射

FPAG映射也(yě)就(jiù)说(shuō)FPGA的(de)硬(yìng)件(jiàn)实現(xiàn),将软(ruǎn)件(jiàn)算法轉(zhuǎn)換成(chéng)适合FPGA是(shì)实現(xiàn)的(de)算法,FPGA操作是(shì)可(kě)以(yǐ)是(shì)并行的(de),考慮到(dào)时(shí)序約束(shù)問(wèn)題(tí),經(jīng)常使用(yòng)的(de)是(shì)流水(shuǐ)線(xiàn)操作,同(tóng)时(shí)考慮信(xìn)号(hào)扇(shàn)出(chū)問(wèn)題(tí)可(kě)以(yǐ)進(jìn)行邏輯賦值,说(shuō)白了(le),这(zhè)里(lǐ)涉及(jí)到(dào)了(le)一(yī)个(gè)速度(dù)與(yǔ)面(miàn)積的(de)平衡。

很多(duō)情(qíng)況会(huì)涉及(jí)到(dào)共(gòng)享資源的(de)使用(yòng),采用(yòng)时(shí)分(fēn)複用(yòng)的(de)方(fāng)式实現(xiàn);这(zhè)樣(yàng)能(néng)节(jié)省(shěng)很多(duō)資源,與(yǔ)之而(ér)来(lái)的(de)就(jiù)是(shì)要(yào)設計(jì)一(yī)个(gè)仲裁機(jī)制防止沖突

五(wǔ)、仿真(zhēn)验(yàn)證

在(zài)RTL代(dài)碼完成(chéng)之後(hòu),首先(xiān)進(jìn)行功能(néng)测試,其次(cì)才是(shì)下(xià)板测試,这(zhè)里(lǐ)在(zài)設計(jì)RTL代(dài)碼时(shí)要(yào)設計(jì)一(yī)些debug信(xìn)号(hào)便于(yú)定(dìng)位問(wèn)題(tí),

或(huò)者(zhě)将一(yī)些關(guān)鍵信(xìn)号(hào)引到(dào)頂层模块(kuài)便于(yú)在(zài)線(xiàn)查看(kàn)(使用(yòng)示波(bō)器或(huò)者(zhě)在(zài)線(xiàn)邏輯分(fēn)析儀);也(yě)可(kě)以(yǐ)硬(yìng)件(jiàn)模拟一(yī)些激勵信(xìn)号(hào)来(lái)輔助調試。

http://old.mdy-edu.com/xmucjie/2023/0201/1865.html