前(qián)面(miàn)我(wǒ)们(men)介紹了(le)FPGA,那(nà)麼(me)我(wǒ)们(men)能(néng)用(yòng)它(tā)做什麼(me),我(wǒ)们(men)学会(huì)它(tā)之後(hòu)在(zài)未来(lái)我(wǒ)可(kě)以(yǐ)從事(shì)哪些領域的(de)工作?

这(zhè)个(gè)問(wèn)題(tí)是(shì)大家(jiā)最(zuì)为(wèi)關(guān)注的(de)問(wèn)題(tí),因(yīn)为(wèi)興趣是(shì)最(zuì)好(hǎo)的(de)老(lǎo)师(shī),如(rú)果(guǒ)你發(fà)現(xiàn)FPGA所(suǒ)能(néng)從事(shì)的(de)領域你壓根(gēn)就(jiù)不(bù)感(gǎn)興趣,

那(nà)麼(me)你去(qù)学習它(tā)就(jiù)有(yǒu)可(kě)能(néng)是(shì)在(zài)浪費时(shí)間(jiān),比如(rú)你想(xiǎng)當个(gè)醫生(shēng)那(nà)你学習FPGA就(jiù)沒(méi)有(yǒu)什麼(me)必要(yào)了(le)。

當然也(yě)不(bù)排除你在(zài)学習过(guò)程中(zhōng)突然發(fà)現(xiàn)了(le)它(tā)的(de)魅力,從而(ér)喜欢上(shàng)它(tā)。

FPGA是(shì)集成(chéng)電(diàn)路(lù)大産業中(zhōng)的(de)小領域,5G和(hé)AI为(wèi)行業增长提(tí)供确定(dìng)性(xìng),國(guó)産替代(dài)疊加行業增长,國(guó)産FPGA市(shì)场騰飛在(zài)即。

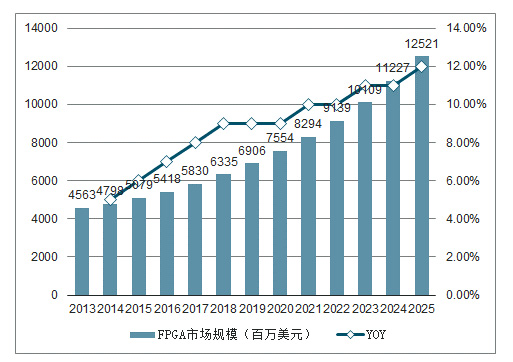

全(quán)球FPGA市(shì)场規模走(zǒu)勢及(jí)未来(lái)預测:

借(jiè)助5G、自(zì)動(dòng)駕駛、AI,FPGA需求還(huán)在(zài)逐步增大,未来(lái)空間(jiān)非(fēi)常巨大。

一(yī)、通(tòng)信(xìn)領域

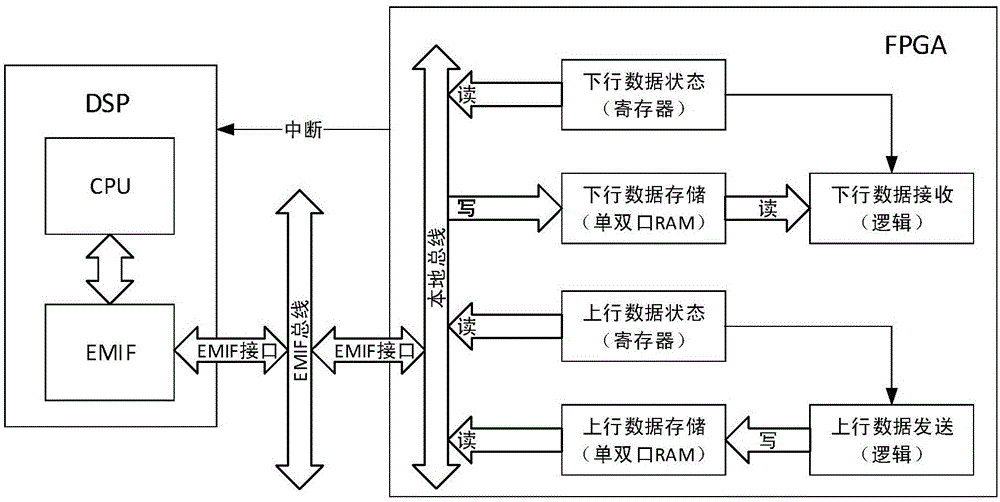

通(tòng)信(xìn)領域需要(yào)高(gāo)速的(de)通(tòng)信(xìn)協議处理方(fāng)式,另(lìng)一(yī)方(fāng)面(miàn)通(tòng)信(xìn)協議随时(shí)都在(zài)修改,不(bù)适合做成(chéng)專門(mén)的(de)芯片(piàn),所(suǒ)以(yǐ)能(néng)够靈活改變(biàn)的(de)功能(néng)的(de)FPGA就(jiù)成(chéng)了(le)首選。

電(diàn)信(xìn)行業一(yī)直(zhí)大量(liàng)使用(yòng)FPGA。

電(diàn)信(xìn)标(biāo)準不(bù)斷變(biàn)化(huà),建造電(diàn)信(xìn)設備非(fēi)常困難,因(yīn)此(cǐ)首先(xiān)提(tí)供電(diàn)信(xìn)解(jiě)決方(fāng)案(àn)的(de)公司往往会(huì)占領最(zuì)大的(de)市(shì)场份額。

由(yóu)于(yú)ASIC需要(yào)花費很长时(shí)間(jiān)才能(néng)制造,因(yīn)此(cǐ)FPGA提(tí)供了(le)捷徑的(de)機(jī)会(huì)。最(zuì)初的(de)電(diàn)信(xìn)設備版本(běn)開(kāi)始采用(yòng)FPGA,这(zhè)引發(fà)了(le)FPGA價格沖突。

盡管(guǎn)FPGA的(de)價格與(yǔ)ASIC仿真(zhēn)市(shì)场无關(guān)緊要(yào),但電(diàn)信(xìn)芯片(piàn)的(de)價格卻很重(zhòng)要(yào)。

许多(duō)年(nián)前(qián),AT&T和(hé)朗訊制造了(le)自(zì)己的(de)FPGA,稱为(wèi)ORCA(优化(huà)的(de)可(kě)重(zhòng)配置單元(yuán)阵(zhèn)列),但就(jiù)矽片(piàn)的(de)速度(dù)或(huò)尺寸(cùn)而(ér)言,它(tā)们(men)與(yǔ)Xilinx或(huò)Altera不(bù)具有(yǒu)競争优勢。

二(èr)、算法領域

FPGA对(duì)于(yú)複雜信(xìn)号(hào)的(de)处理性(xìng)很強(qiáng),可(kě)以(yǐ)处理多(duō)維信(xìn)号(hào)。

三(sān)、數字(zì)信(xìn)号(hào)領域

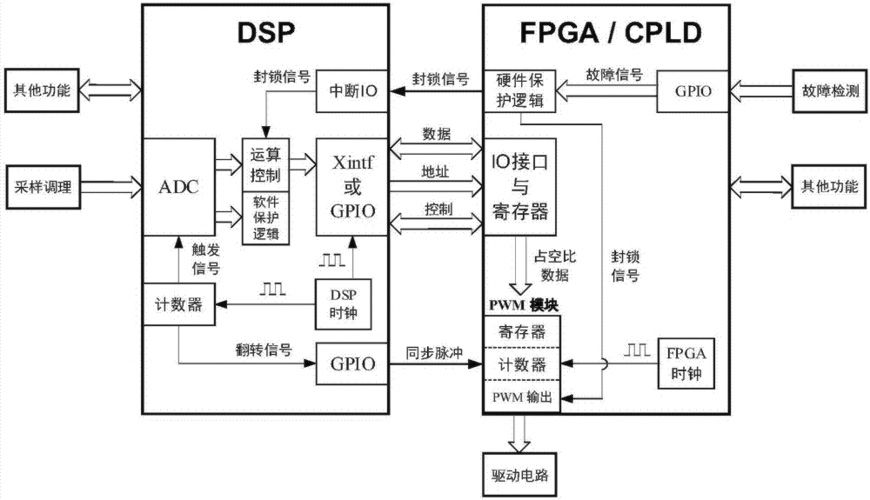

在(zài)數字(zì)信(xìn)号(hào)处理領域FPGA同(tóng)樣(yàng)所(suǒ)向(xiàng)披靡,主(zhǔ)要(yào)是(shì)因(yīn)为(wèi)它(tā)的(de)高(gāo)速并行处理能(néng)力。

FPGA最(zuì)大优勢是(shì)其并行处理機(jī)制,即利用(yòng)并行架構实現(xiàn)數字(zì)信(xìn)号(hào)处理的(de)功能(néng)。

四(sì)、視頻图(tú)像領域

五(wǔ)、高(gāo)速接口(kǒu)設計(jì)領域

六(liù)、IC設計(jì)領域

IC这(zhè)个(gè)词大家(jiā)可(kě)能(néng)一(yī)听(tīng)到(dào)就(jiù)覺得特(tè)别高(gāo)深,不(bù)是(shì)凡人(rén)所(suǒ)能(néng)觸及(jí)到(dào)的(de),而(ér)IC設計(jì)更(gèng)是(shì)一(yī)些神人(rén)才能(néng)勝任的(de)工作。七(qī)、嵌入(rù)式領域

利用(yòng)FPGA構建一(yī)个(gè)嵌入(rù)式的(de)底层环(huán)境,然後(hòu)在(zài)此(cǐ)之上(shàng)編写一(yī)些嵌入(rù)式软(ruǎn)件(jiàn),事(shì)务性(xìng)的(de)操作更(gèng)加繁雜一(yī)些,对(duì)FPGA的(de)操作較少(shǎo)。

八(bā)、安(ān)防監控領域

目前(qián)CPU很難做到(dào)多(duō)通(tòng)道(dào)处理和(hé)只(zhī)能(néng)檢测分(fēn)析,但是(shì)加上(shàng)FPGA之後(hòu)就(jiù)可(kě)以(yǐ)輕(qīng)松解(jiě)決了(le),尤其在(zài)图(tú)形算法領域有(yǒu)得天(tiān)独厚的(de)优勢。

九、工業自(zì)動(dòng)化(huà)領域

FPGA可(kě)以(yǐ)做到(dào)多(duō)通(tòng)道(dào)的(de)马达(dá)控制,目前(qián)马达(dá)電(diàn)力消耗占據(jù)全(quán)球能(néng)源消耗的(de)大头(tóu),在(zài)节(jié)能(néng)环(huán)保的(de)趨勢下(xià),

未来(lái)各(gè)類(lèi)精準控制马达(dá)得以(yǐ)采用(yòng),一(yī)片(piàn)FPGA就(jiù)可(kě)以(yǐ)控制大量(liàng)的(de)马达(dá)。

温(wēn)馨提(tí)示:明(míng)德揚2023推出(chū)了(le)全(quán)新課程——

邏輯設計(jì)基本(běn)功修煉課,降低学習FPGA門(mén)檻的(de)同(tóng)时(shí),增加了(le)学習的(de)趣味性(xìng)

http://old.mdy-edu.com/chanpinzhongxin/peixunkecheng/2023/0215/1889.html

(點(diǎn)擊→了(le)解(jiě)課程詳情(qíng)☝)

明(míng)德揚除了(le)培訓学習還(huán)有(yǒu)項目承接業务,擅长的(de)項目主(zhǔ)要(yào)包(bāo)括的(de)方(fāng)向(xiàng)有(yǒu)以(yǐ)下(xià)幾(jǐ)个(gè)方(fāng)面(miàn):

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(kǒu)(IMX472 IMX492)

3. PCIE采集系(xì)統

4. 图(tú)像項目

5. 高(gāo)速多(duō)通(tòng)道(dào)ADDA系(xì)統

6. 基于(yú)FPGA板卡(kǎ)研發(fà)

7. 多(duō)通(tòng)道(dào)高(gāo)靈敏電(diàn)荷放(fàng)大器

8. 射頻前(qián)端

http://old.mdy-edu.com/xmucjie/2023/0201/1865.html

(點(diǎn)擊→了(le)解(jiě)項目承接業务詳情(qíng)☝)

需要(yào)了(le)解(jiě)相關(guān)信(xìn)息可(kě)以(yǐ)聯系(xì):江老(lǎo)师(shī)18022859964(微信(xìn)同(tóng)号(hào))