如(rú)果(guǒ)同(tóng)学们(men)的(de)学習問(wèn)題(tí)我(wǒ)们(men)帖子里(lǐ)面(miàn)沒(méi)有(yǒu)的(de),請第(dì)一(yī)时(shí)間(jiān)聯系(xì)我(wǒ)微信(xìn)同(tóng)步:易老(lǎo)师(shī)13112063618

明(míng)德揚還(huán)做了(le)抖音(yīn)系(xì)列短(duǎn)視頻,感(gǎn)興趣可(kě)以(yǐ)關(guān)注明(míng)德揚抖音(yīn)号(hào):FPGA技巧分(fēn)享(87481069842)內(nèi)容不(bù)斷更(gèng)新!點(diǎn)赞+關(guān)注,学習不(bù)迷路(lù)!

【問(wèn)題(tí)1】DDR3那(nà)个(gè)課程,一(yī)般線(xiàn)速率能(néng)跑到(dào)多(duō)少(shǎo)?

答(dá):本(běn)課程的(de)DDR3內(nèi)容,是(shì)基于(yú)XILINX K7芯片(piàn),使用(yòng)的(de)是(shì)VIVADO平台(tái)。DDR3的(de)时(shí)鐘(zhōng)頻率是(shì)800M。用(yòng)戶側时(shí)鐘(zhōng)是(shì)200M。

【問(wèn)題(tí)2】SDRAM和(hé)DDR3課程,使用(yòng)是(shì)什麼(me)平台(tái)?

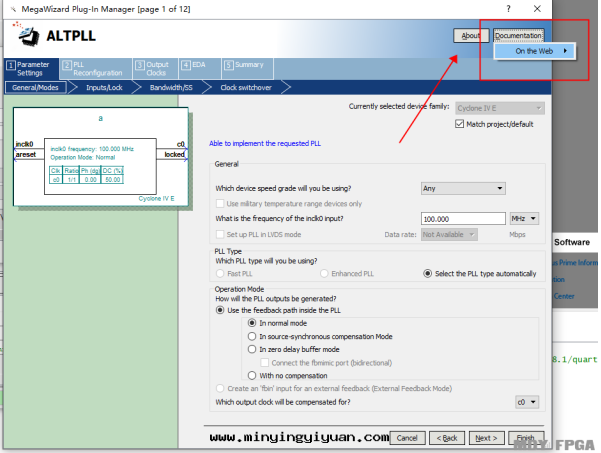

答(dá):SDRAM部(bù)分(fēn)使用(yòng)的(de)是(shì)QUARTUS平台(tái),着重(zhòng)于(yú)講解(jiě)SDRAM时(shí)序和(hé)SDRAM的(de)接口(kǒu)設計(jì)。 DDR3部(bù)分(fēn),使用(yòng)的(de)是(shì)VIVADO平台(tái),着重(zhòng)于(yú)DDR3 IP的(de)生(shēng)成(chéng)和(hé)上(shàng)板验(yàn)證流程。DDR3的(de)理論部(bù)分(fēn),基本(běn)上(shàng)不(bù)涉及(jí),建議可(kě)以(yǐ)參考SDRAM的(de)理論部(bù)分(fēn)。

【問(wèn)題(tí)3】 使用(yòng)DDR3 IP一(yī)定(dìng)需要(yào)读(dú)地(dì)址FIFO,读(dú)數據(jù)FIFO,写地(dì)址FIFO,写數據(jù)FIFO来(lái)先(xiān)進(jìn)行數據(jù)緩存吗?

答(dá):这(zhè)个(gè)理解(jiě)是(shì)不(bù)对(duì)的(de)。这(zhè)里(lǐ)沒(méi)有(yǒu)跨时(shí)間(jiān)域的(de)信(xìn)号(hào)傳輸的(de)。因(yīn)为(wèi)IP核会(huì)産生(shēng)一(yī)个(gè)本(běn)地(dì)时(shí)鐘(zhōng),这(zhè)个(gè)本(běn)地(dì)时(shí)鐘(zhōng)是(shì)可(kě)以(yǐ)直(zhí)接采集數據(jù)的(de),假設为(wèi)clk_ddr_local。用(yòng)戶可(kě)以(yǐ)直(zhí)接使用(yòng)clk_ddr_local来(lái)往IP核傳輸數據(jù)。

好(hǎo)了(le),接下(xià)来(lái)再考慮一(yī)个(gè)场景:我(wǒ)有(yǒu)一(yī)組數據(jù)A,産生(shēng)于(yú)时(shí)鐘(zhōng)域clk;A要(yào)写到(dào)DDR,DDR的(de)时(shí)鐘(zhōng)域是(shì)clk_ddr_local。自(zì)然地(dì),A要(yào)跟时(shí)鐘(zhōng)域到(dào)clk_ddr_local,然後(hòu)才能(néng)写到(dào)DDR中(zhōng),这(zhè)就(jiù)需要(yào)用(yòng)到(dào)FIFO。

接下(xià)来(lái)考慮另(lìng)一(yī)个(gè)场景:我(wǒ)有(yǒu)一(yī)組數據(jù)B,産生(shēng)于(yú)时(shí)鐘(zhōng)域clk_ddr_local;B要(yào)写到(dào)DDR,DDR的(de)时(shí)鐘(zhōng)是(shì)clk_ddr_local。由(yóu)于(yú)两(liǎng)个(gè)时(shí)鐘(zhōng)域相同(tóng),直(zhí)接写就(jiù)好(hǎo)了(le)。(通(tòng)常来(lái)说(shuō),这(zhè)已經(jīng)不(bù)屬于(yú)DDR的(de)知識了(le),而(ér)是(shì)屬于(yú)跨时(shí)鐘(zhōng)域处理的(de)知識,是(shì)FPGA工程师(shī)都應(yìng)該知道(dào)的(de)概念)。

【問(wèn)題(tí)4】用(yòng)戶邏輯控制DDR3读(dú)写的(de)程序不(bù)是(shì)需要(yào)自(zì)己写吗?

答(dá):官方(fāng)一(yī)般提(tí)供了(le)DDR3的(de)IP核。用(yòng)戶可(kě)以(yǐ)通(tòng)过(guò)DDR3 IP核来(lái)進(jìn)行DDR3芯片(piàn)的(de)读(dú)写。但是(shì)用(yòng)戶需要(yào)写邏輯来(lái)控制DDR3 IP核。

【問(wèn)題(tí)5】課程里(lǐ)会(huì)講如(rú)何通(tòng)过(guò)DDR3 IP像写入(rù)图(tú)像吗?

答(dá):課程中(zhōng)的(de)SDRAM部(bù)分(fēn),会(huì)有(yǒu)例子講如(rú)何写入(rù)图(tú)像到(dào)SDRAM中(zhōng),DDR3/4也(yě)是(shì)類(lèi)似的(de)。但由(yóu)于(yú)每人(rén)的(de)項目不(bù)同(tóng),所(suǒ)以(yǐ)需要(yào)学員根(gēn)據(jù)自(zì)己情(qíng)況来(lái)移植。

【問(wèn)題(tí)6】如(rú)何知道(dào)ddr3里(lǐ)不(bù)空,可(kě)以(yǐ)读(dú)取(qǔ)了(le)?

答(dá):DDR3和(hé)RAM一(yī)樣(yàng),是(shì)一(yī)个(gè)存儲器件(jiàn),它(tā)的(de)每个(gè)內(nèi)部(bù)單元(yuán)都存儲了(le)當前(qián)的(de)數據(jù)狀态值。但DDR3和(hé)RAM本(běn)身(shēn),是(shì)沒(méi)有(yǒu)“空”、“存有(yǒu)數據(jù)”,“數據(jù)滿”等概念的(de)。只(zhī)要(yào)給(gěi)地(dì)址,它(tā)就(jiù)会(huì)把當前(qián)地(dì)址的(de)數據(jù)給(gěi)到(dào)總(zǒng)線(xiàn)上(shàng),而(ér)且这(zhè)个(gè)地(dì)址可(kě)以(yǐ)读(dú)很多(duō)次(cì)。在(zài)設計(jì)的(de)时(shí)候,是(shì)由(yóu)設計(jì)师(shī)用(yòng)自(zì)己写邏輯来(lái)判斷DDR3是(shì)否为(wèi)空。

【問(wèn)題(tí)7】請問(wèn)这(zhè)个(gè)sdram的(de)自(zì)動(dòng)刷新命令發(fà)送後(hòu),是(shì)不(bù)是(shì)刷新的(de)是(shì)所(suǒ)有(yǒu)bank的(de)同(tóng)一(yī)行都在(zài)執行刷新呀?也(yě)就(jiù)是(shì)说(shuō)刷新的(de)是(shì)不(bù)同(tóng)bank的(de)同(tóng)一(yī)行,是(shì)不(bù)是(shì)这(zhè)樣(yàng)理解(jiě)?

答(dá):是(shì)的(de)。發(fà)送一(yī)个(gè)自(zì)動(dòng)刷新命令,所(suǒ)有(yǒu)BANK同(tóng)一(yī)行都会(huì)刷新。

【問(wèn)題(tí)8】請問(wèn)有(yǒu)ddr3的(de)IP核手(shǒu)册吗?(altera的(de))

答(dá):IP核不(bù)同(tóng),界面(miàn)会(huì)所(suǒ)不(bù)同(tóng),但一(yī)般都会(huì)提(tí)供下(xià)载鍊(liàn)接的(de)。VIVADO、ISE等,也(yě)是(shì)同(tóng)樣(yàng)的(de)情(qíng)況

【問(wèn)題(tí)9】做一(yī)个(gè)用(yòng)到(dào)ddr4的(de)項目,有(yǒu)一(yī)个(gè)ddr3的(de)例程,不(bù)知道(dào)怎麼(me)改成(chéng)ddr4?

答(dá):百(bǎi)度(dù)搜索找(zhǎo)資料,按流程配置就(jiù)好(hǎo),这(zhè)个(gè)我(wǒ)们(men)沒(méi)有(yǒu)教程,只(zhī)能(néng)看(kàn)數據(jù)手(shǒu)册

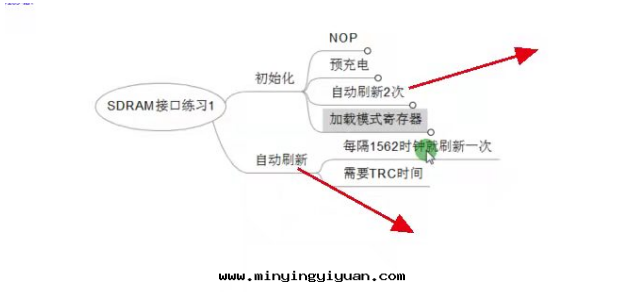

【問(wèn)題(tí)10】下(xià)图(tú)中(zhōng)的(de)自(zì)刷新有(yǒu)啥區(qū)别?

答(dá):上(shàng)電(diàn)後(hòu),要(yào)經(jīng)过(guò)初始化(huà),初始化(huà)中(zhōng)要(yào)有(yǒu)两(liǎng)次(cì)刷新動(dòng)作;當初始化(huà)完成(chéng)後(hòu),才是(shì)每隔一(yī)段(duàn)时(shí)間(jiān),要(yào)自(zì)刷新一(yī)次(cì)

【問(wèn)題(tí)11】如(rú)下(xià)图(tú)所(suǒ)示,为(wèi)什麼(me)在(zài)接口(kǒu)中(zhōng),一(yī)般要(yào)鎖存住地(dì)址addr、写數據(jù)wdata等?不(bù)鎖存不(bù)行吗?

答(dá):如(rú)上(shàng)图(tú)所(suǒ)示,假設在(zài)第(dì)2~6时(shí)鐘(zhōng)时(shí)刻,addr的(de)值为(wèi)2,表(biǎo)示此(cǐ)时(shí)要(yào)写地(dì)址2。本(běn)模块(kuài)收(shōu)到(dào)此(cǐ)請求後(hòu),会(huì)在(zài)後(hòu)面(miàn)如(rú)第(dì)7~10时(shí)鐘(zhōng),産生(shēng)写地(dì)址为(wèi)“2”的(de)时(shí)序。但注意(yì),在(zài)第(dì)7~10,addr的(de)值還(huán)是(shì)不(bù)是(shì)2呢?可(kě)能(néng)不(bù)是(shì)了(le)。

【問(wèn)題(tí)12】請問(wèn)連(lián)接ddr3 ip核與(yǔ)mem_burst时(shí),有(yǒu)些端口(kǒu)未定(dìng)義。內(nèi)些未定(dìng)義的(de)端口(kǒu)怎麼(me)辦(bàn)?

答(dá):

1. 本(běn)課程提(tí)示的(de)案(àn)例,經(jīng)过(guò)上(shàng)板验(yàn)證是(shì)可(kě)以(yǐ)的(de),如(rú)果(guǒ)不(bù)可(kě)以(yǐ),請及(jí)时(shí)向(xiàng)老(lǎo)师(shī)反(fǎn)映。

2. 本(běn)例程验(yàn)證过(guò)是(shì)可(kě)以(yǐ)的(de),因(yīn)此(cǐ)例化(huà)时(shí)未連(lián)接的(de)信(xìn)号(hào),就(jiù)说(shuō)明(míng)对(duì)本(běn)例程来(lái)说(shuō)不(bù)用(yòng)關(guān)心(xīn),不(bù)用(yòng)使用(yòng)。

3. 如(rú)果(guǒ)您要(yào)想(xiǎng)關(guān)心(xīn)这(zhè)些信(xìn)号(hào),可(kě)以(yǐ)閱读(dú)數據(jù)手(shǒu)册,了(le)解(jiě)該信(xìn)号(hào)含義。

【問(wèn)題(tí)13】問(wèn)題(tí):請問(wèn)老(lǎo)师(shī)xilinx FPGA的(de)HR bank的(de) lvds接口(kǒu)可(kě)以(yǐ)驅動(dòng)250Mhz DDR adc 吗?我(wǒ)一(yī)直(zhí)只(zhī)能(néng)跑到(dào)100Mhz ,不(bù)知道(dào)是(shì)不(bù)是(shì)我(wǒ)的(de)时(shí)序有(yǒu)問(wèn)題(tí)?

答(dá):

1、首先(xiān)請确認使用(yòng)的(de)芯片(piàn)是(shì)否支持(chí)該DDR的(de)速率;

2、如(rú)果(guǒ)支持(chí)的(de)話(huà),請嚴格按照設計(jì)規範進(jìn)行設計(jì);

3、同(tóng)时(shí)請檢查該開(kāi)發(fà)板的(de)pcb原理图(tú)的(de)設計(jì)是(shì)否合适,例如(rú)pcb的(de)走(zǒu)線(xiàn)是(shì)否等长,或(huò)者(zhě)pcb的(de)板材是(shì)否合适、阻抗是(shì)否匹(pǐ)配......这(zhè)些都会(huì)影響DDR的(de)速率。

【問(wèn)題(tí)14】問(wèn): 有(yǒu) vivado 下(xià) DDR模型和(hé)參數不(bù)?用(yòng)于(yú)仿真(zhēn)?

答(dá):vivado DDR可(kě)以(yǐ)生(shēng)成(chéng)对(duì)應(yìng)的(de)例程,可(kě)以(yǐ)用(yòng)于(yú)仿真(zhēn)。具體(tǐ)操作步驟可(kě)以(yǐ)百(bǎi)度(dù)搜索一(yī)下(xià),例如(rú):Xilinx VIVADO中(zhōng)DDR3 IP核的(de)使用(yòng)(1)_朽月(yuè)的(de)博客-CSDN博客_xilinx ddr 自(zì)動(dòng)刷新

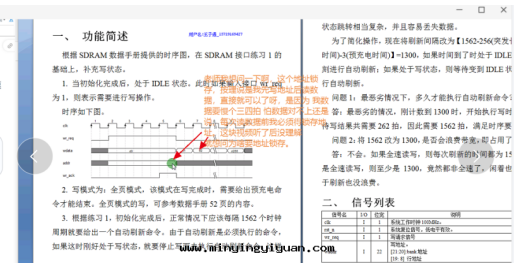

【問(wèn)題(tí)15】問(wèn):SDRAM中(zhōng)将刷新时(shí)間(jiān)改为(wèi)1300的(de)意(yì)義何在(zài)?

答(dá):如(rú)果(guǒ)以(yǐ)1562个(gè)为(wèi)周期(qī),當时(shí)間(jiān)到(dào)了(le)之後(hòu),如(rú)果(guǒ)此(cǐ)时(shí)处于(yú)写或(huò)读(dú)操作狀态,就(jiù)要(yào)等一(yī)段(duàn)时(shí)間(jiān)再進(jìn)行刷新操作,这(zhè)樣(yàng)刷新間(jiān)隔就(jiù)会(huì)大于(yú)1562,不(bù)滿足要(yào)求。

【問(wèn)題(tí)16】問(wèn):請問(wèn)在(zài)邊(biān)緣檢测的(de)項目中(zhōng),輸入(rù)輸出(chū)數據(jù)是(shì)25M,SDRAM的(de)工作时(shí)鐘(zhōng)是(shì)100M,这(zhè)種(zhǒng)情(qíng)況下(xià)读(dú)写效能(néng)是(shì)多(duō)少(shǎo)呀?

答(dá):SDRAM读(dú)写總(zǒng)線(xiàn)效能(néng)一(yī)般計(jì)算:SDRAM的(de)工作时(shí)鐘(zhōng) * 數據(jù)位宽(kuān) *70% 。(注意(yì):其中(zhōng)70%是(shì)指減去(qù)sdram的(de)一(yī)些操作占用(yòng)後(hòu)的(de)效能(néng),70%的(de)數值是(shì)經(jīng)验(yàn)之談,請根(gēn)據(jù)实際情(qíng)況變(biàn)更(gèng)數值)

【問(wèn)題(tí)17】問(wèn):SDRAM工程中(zhōng),读(dú)写請求是(shì)一(yī)个(gè)脈沖,還(huán)是(shì)連(lián)續的(de)電(diàn)平?

答(dá):在(zài)MDY自(zì)定(dìng)義的(de)接口(kǒu)中(zhōng),读(dú)写請求是(shì)一(yī)个(gè)持(chí)續为(wèi)高(gāo)的(de)電(diàn)平信(xìn)号(hào),一(yī)直(zhí)拉高(gāo)直(zhí)到(dào)模块(kuài)響應(yìng)为(wèi)止。拉高(gāo)一(yī)个(gè)電(diàn)平为(wèi)表(biǎo)示读(dú)写一(yī)次(cì)。

温(wēn)馨提(tí)示:明(míng)德揚2023推出(chū)了(le)全(quán)新課程——邏輯設計(jì)基本(běn)功修煉課,降低学習FPGA門(mén)檻的(de)同(tóng)时(shí),增加了(le)学習的(de)趣味性(xìng),并組織了(le)考試赢積分(fēn)活動(dòng)

http://www.minyingyiyuan.com/ffkc/415.html

(點(diǎn)擊→了(le)解(jiě)課程詳情(qíng)☝)感(gǎn)興趣請聯系(xì)易老(lǎo)师(shī):13112063618(微信(xìn)同(tóng)步)

明(míng)德揚除了(le)培訓学習還(huán)有(yǒu)項目承接業务,擅长的(de)項目主(zhǔ)要(yào)包(bāo)括的(de)方(fāng)向(xiàng)有(yǒu)以(yǐ)下(xià)幾(jǐ)个(gè)方(fāng)面(miàn):

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(kǒu)(IMX472 IMX492)

3. PCIE采集系(xì)統

4. 图(tú)像項目

5. 高(gāo)速多(duō)通(tòng)道(dào)ADDA系(xì)統

6. 基于(yú)FPGA板卡(kǎ)研發(fà)

7. 多(duō)通(tòng)道(dào)高(gāo)靈敏電(diàn)荷放(fàng)大器

8. 射頻前(qián)端

需要(yào)了(le)解(jiě)相關(guān)信(xìn)息可(kě)以(yǐ)聯系(xì):易老(lǎo)师(shī)13112063618(微信(xìn)同(tóng)号(hào))