【教程】數電(diàn)基礎與(yǔ)Verilog設計(jì)

發(fà)布(bù)时(shí)間(jiān):2023-10-03 | 作者(zhě):yi jin yun | 浏覽量(liàng):1533

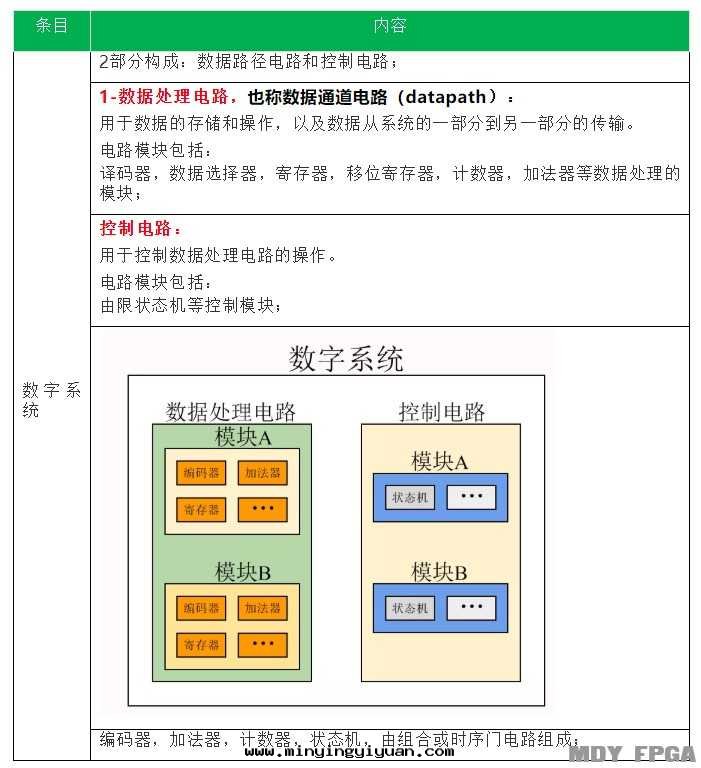

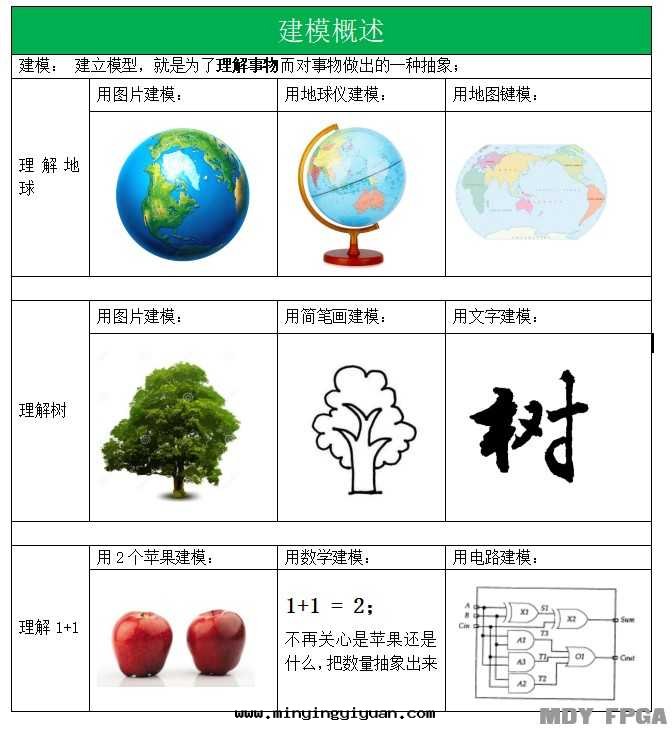

一(yī)、 概述

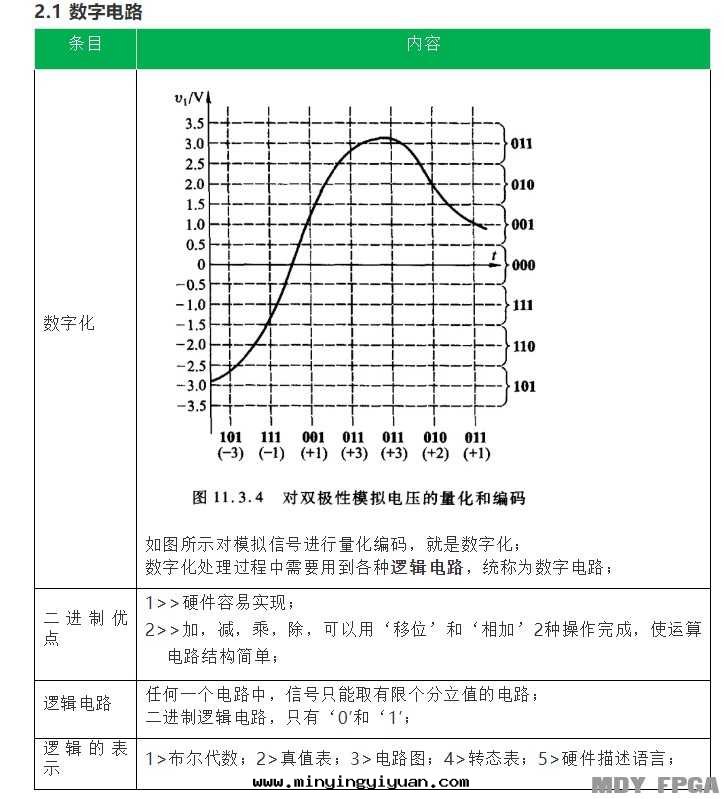

二(èr)、基本(běn)概念

2.2硬(yìng)件(jiàn)電(diàn)路(lù)

2.2.1 進(jìn)制轉(zhuǎn)換表(biǎo)

条(tiáo)目 | |

| George Boole乔治·布(bù)爾,英國(guó)數学家(jiā),1847年(nián)創立; |

| 僅用(yòng)數值“0”和(hé)“1”实現(xiàn)邏輯的(de)數学化(huà); |

| 指事(shì)物(wù)的(de)因(yīn)果(guǒ)之間(jiān)所(suǒ)應(yìng)遵循的(de)規律 |

應(yìng)用(yòng)于(yú)數電(diàn) | Claude Shannoe克(kè)勞迪·香農,美國(guó)科学家(jiā),1938年(nián)用(yòng)于(yú)數電(diàn); |

| 个(gè)人(rén)看(kàn)法: 把事(shì)物(wù)邏輯規律,用(yòng)數学準确描述,这(zhè)樣(yàng)交給(gěi)計(jì)算处理,又快(kuài)又好(hǎo)。 |

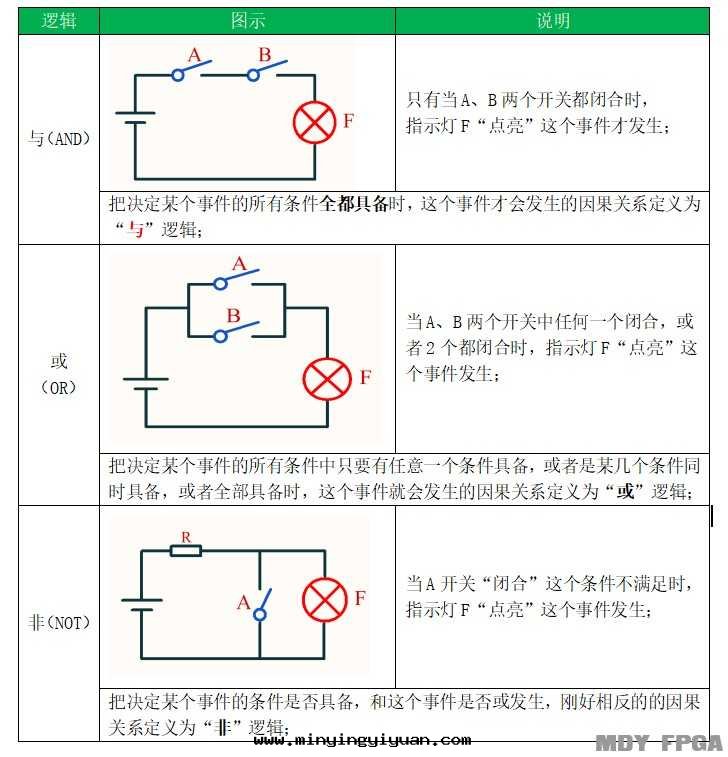

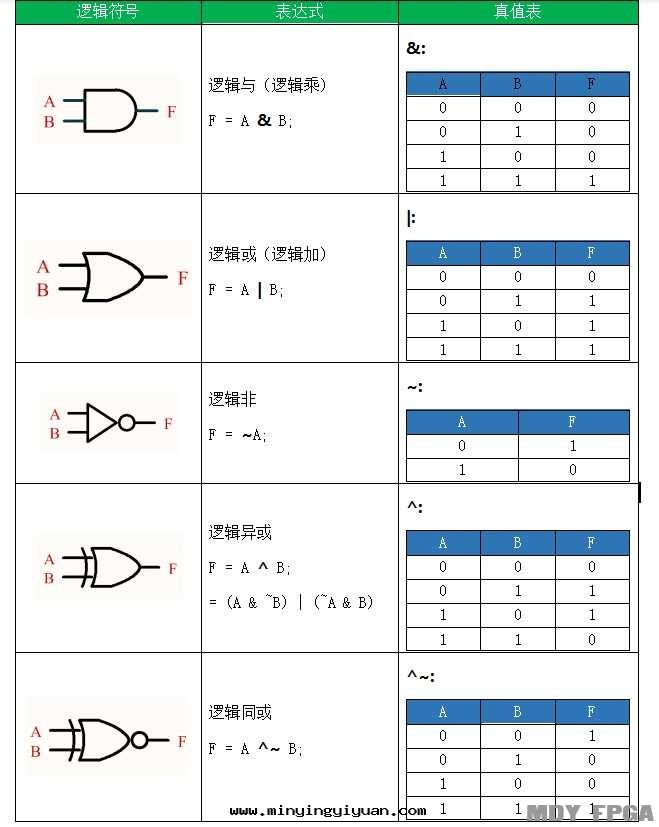

2.4.3 基本(běn)邏輯表(biǎo)达(dá)

条(tiáo)目 | |

| 把“與(yǔ)”、“或(huò)”、“非(fēi)”这(zhè)三(sān)種(zhǒng)基本(běn)邏輯運算組合为(wèi)邏輯表(biǎo)达(dá)式,表(biǎo)达(dá)式的(de)運算結果(guǒ)賦于(yú)另(lìng)一(yī)个(gè)變(biàn)量(liàng),比如(rú)F,这(zhè)个(gè)公式叫邏輯函(hán)數; |

例: F = A & B | C; 可(kě)以(yǐ)抽象(xiàng)为(wèi): F = f(A,B,C); |

邏輯函(hán)數和(hé)邏輯電(diàn)路(lù)是(shì)相互对(duì)應(yìng)的(de); |

| 運算規律: 1>>邏輯代(dài)數公理; 2>>邏輯代(dài)數基本(běn)定(dìng)律; 3>>邏輯代(dài)數基本(běn)定(dìng)理; |

| 1>>基本(běn)定(dìng)律; 2>>卡(kǎ)諾图(tú)等; 3>>Q-M化(huà)簡法; |

2.5 電(diàn)路(lù)分(fēn)類(lèi)

条(tiáo)目 | |

| |

|

| |

|

| |

|

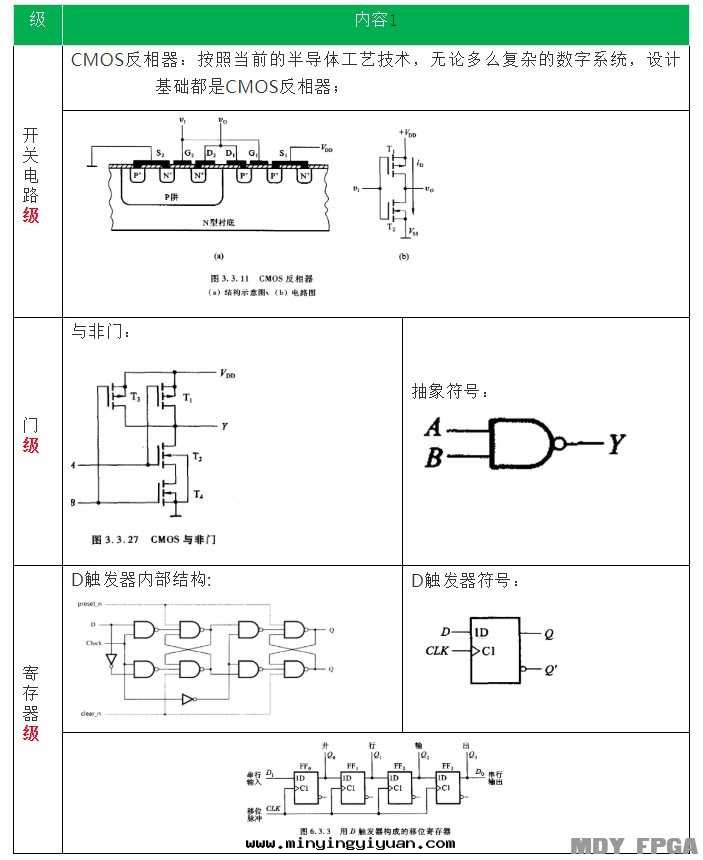

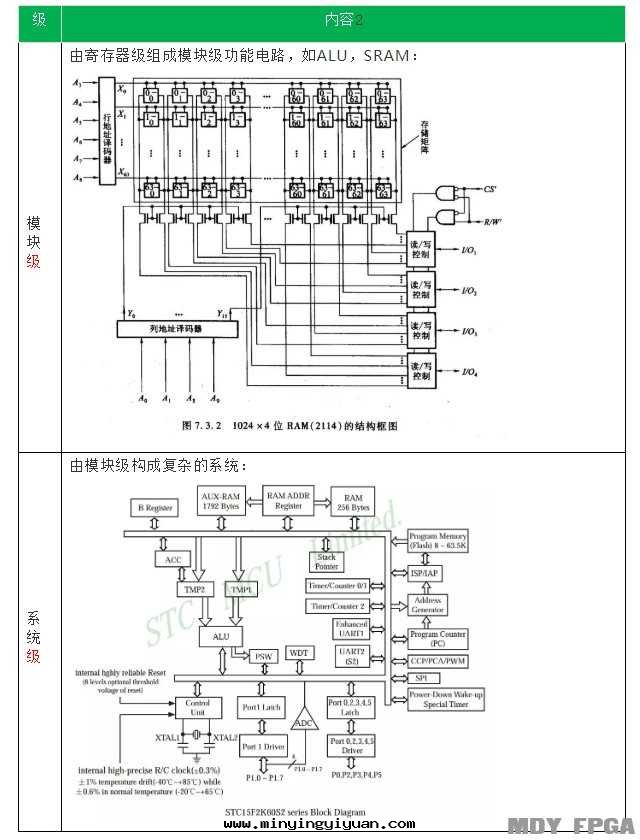

| 晶體(tǐ)管(guǎn)->門(mén)級->模块(kuài)級->系(xì)統級 |

| | |

| | |

| |

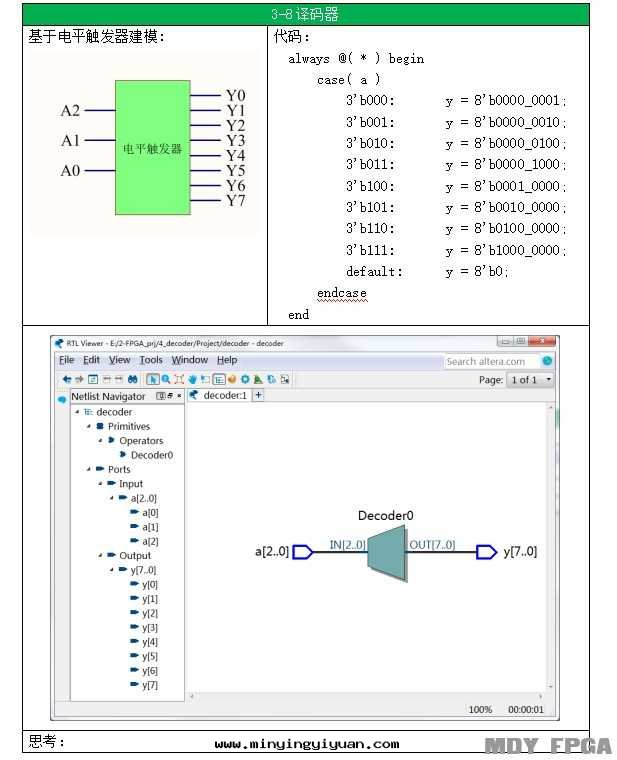

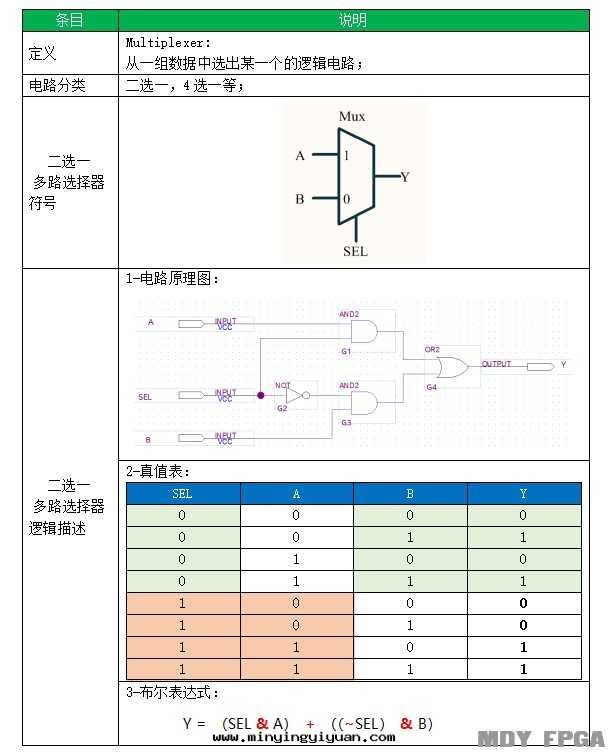

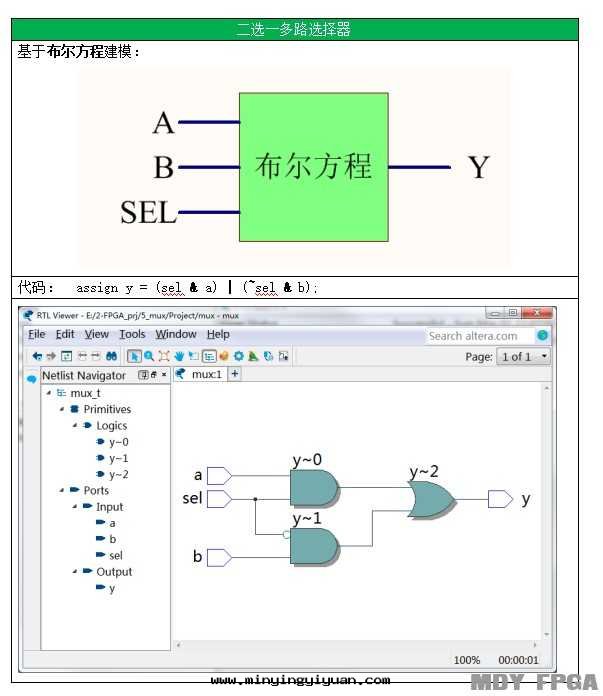

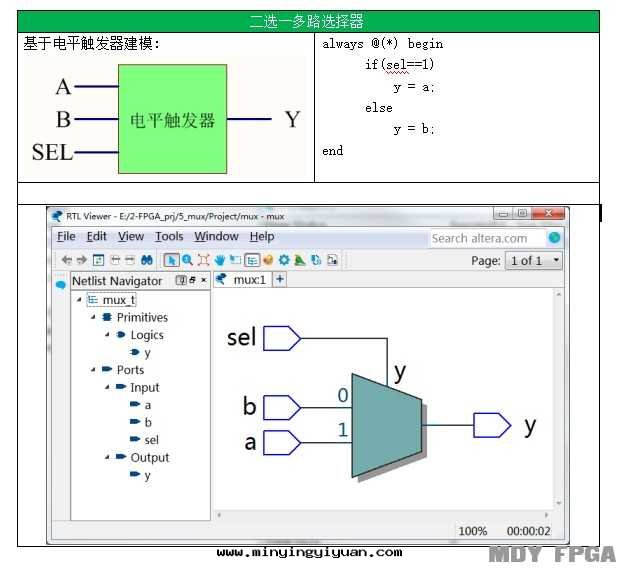

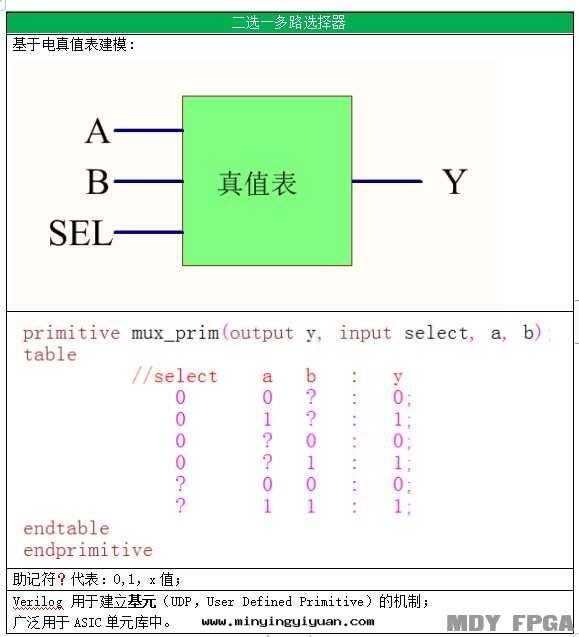

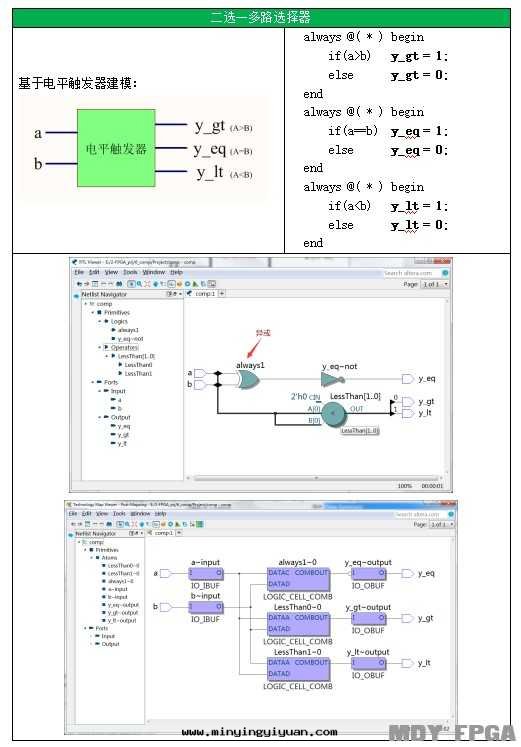

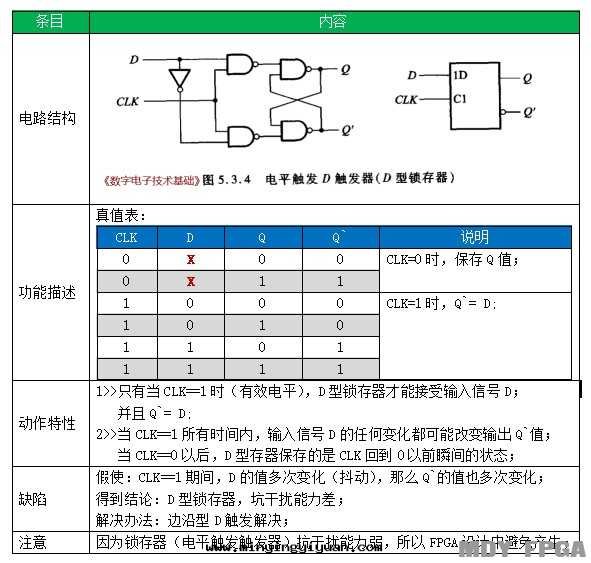

1>>布(bù)爾表(biǎo)达(dá)式; 2>>電(diàn)平觸發(fà)器; 3>>邊(biān)沿觸發(fà)器; | 3-行为(wèi)級建模: 1>>基于(yú)布(bù)爾方(fāng)程; 2>>基于(yú)電(diàn)平觸發(fà)器建模; 3>>基于(yú)邊(biān)沿觸發(fà)器建模; |

RTL級(Register Transfer Level)寄存器傳輸級; |

| 算法級建模:與(yǔ)硬(yìng)件(jiàn)无關(guān); |

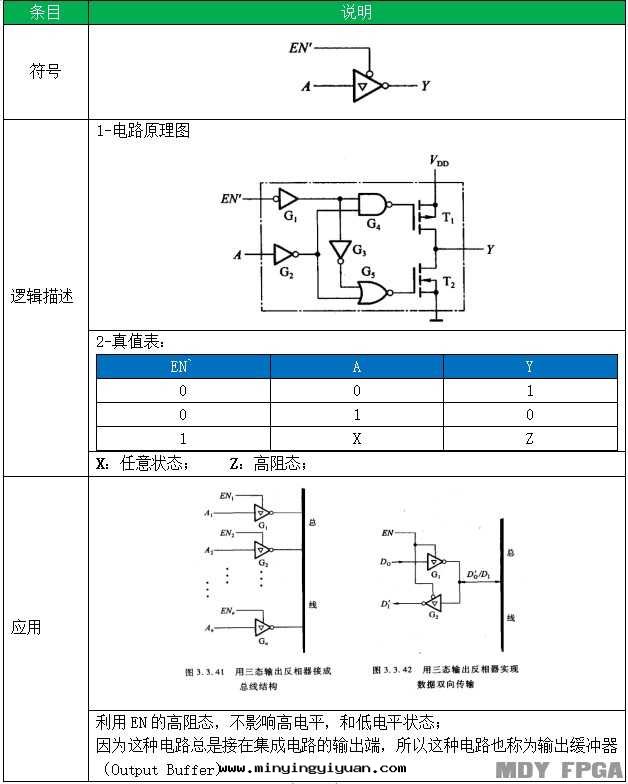

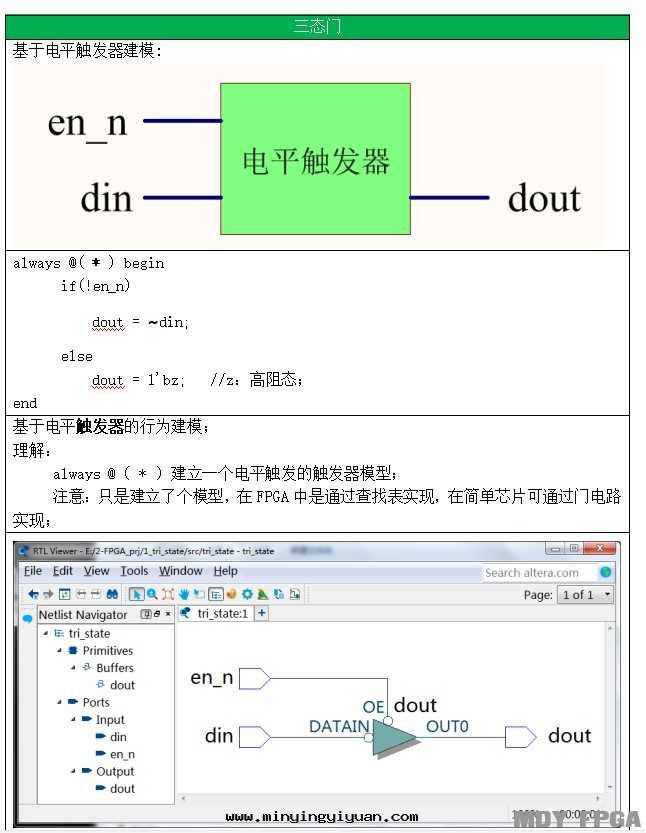

3.1 三(sān)态門(mén)3.1.1 工作原理

3.2.2 行为(wèi)建模

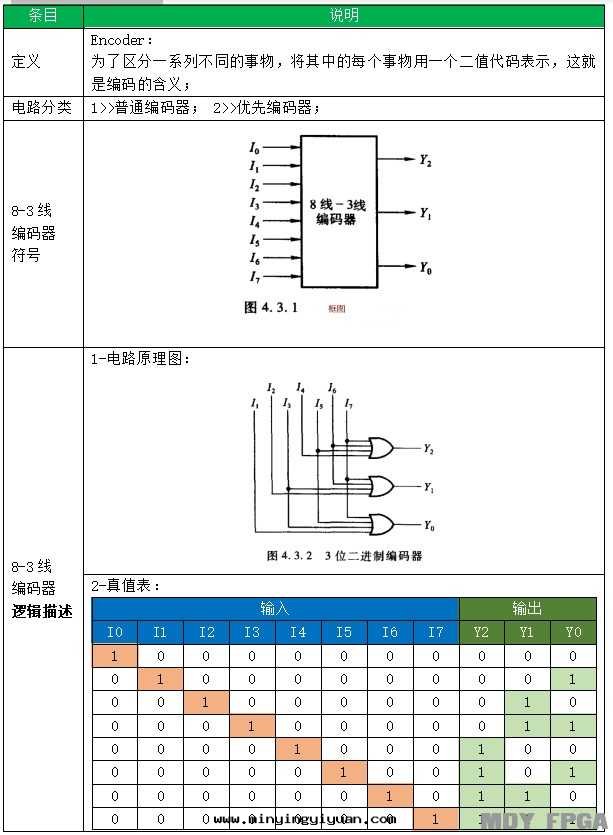

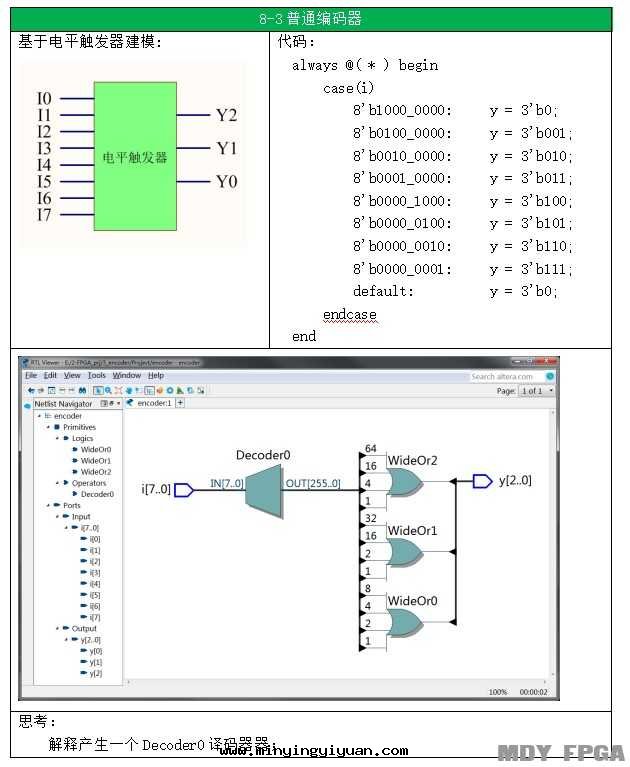

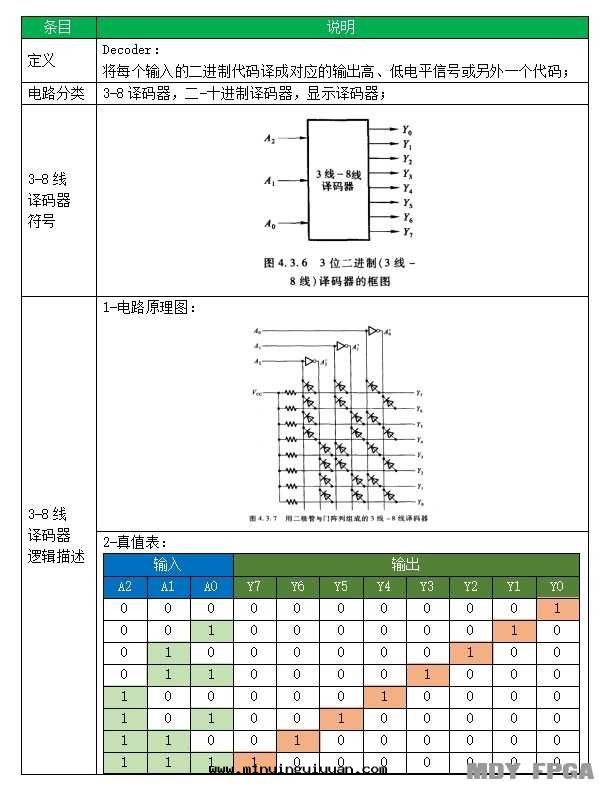

3.5.1 工作原理

3.5.2 行为(wèi)建模13.5.2 行为(wèi)建模2四(sì)、 时(shí)序邏輯電(diàn)路(lù) 4.1 概述时(shí)序邏輯電(diàn)路(lù)概述 |

問(wèn)題(tí): 在(zài)各(gè)種(zhǒng)複雜的(de)數字(zì)電(diàn)路(lù)中(zhōng),不(bù)但需要(yào)对(duì)二(èr)進(jìn)制信(xìn)号(hào)進(jìn)行算術(shù)運算和(hé)邏輯運算,還(huán)需要(yào)将这(zhè)些信(xìn)号(hào)的(de)運算結果(guǒ)保存起来(lái)。 |

解(jiě)決: 觸發(fà)器(Filp-Flop):能(néng)够存儲1位二(èr)值信(xìn)号(hào)的(de)基本(běn)邏輯單元(yuán)電(diàn)路(lù)統稱; |

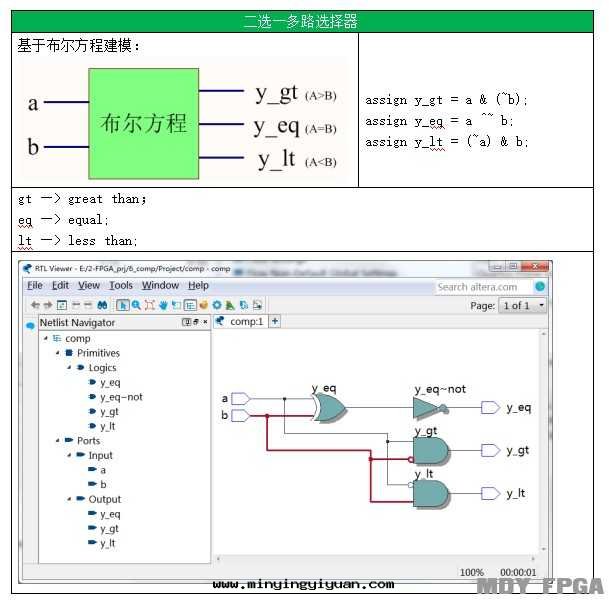

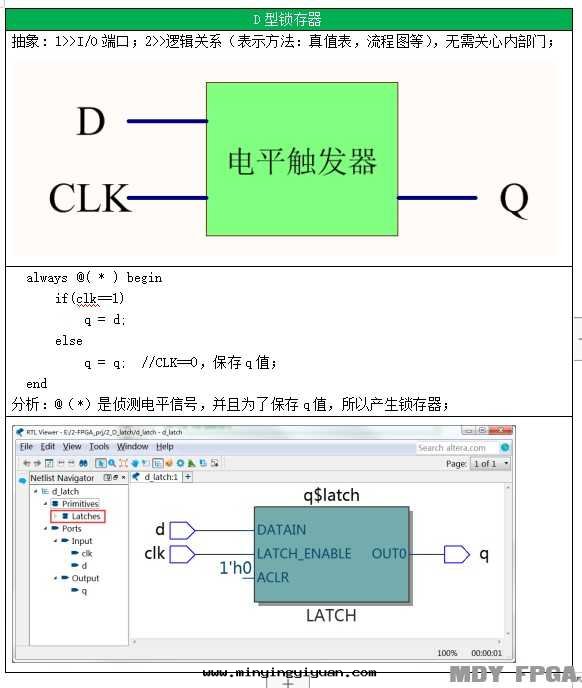

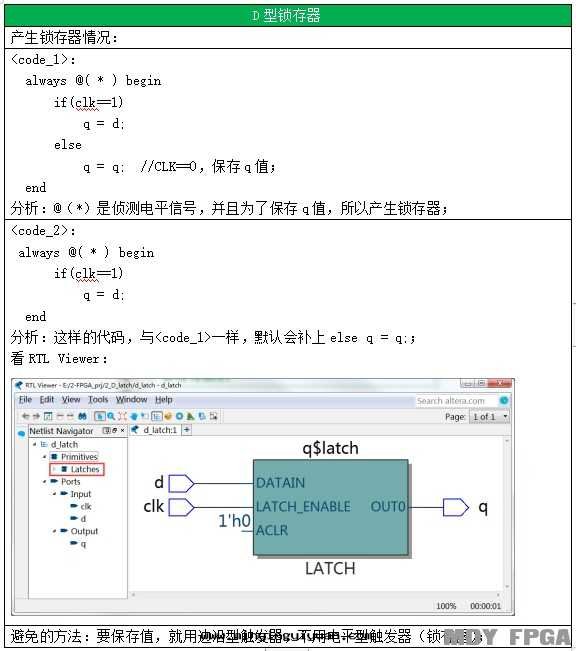

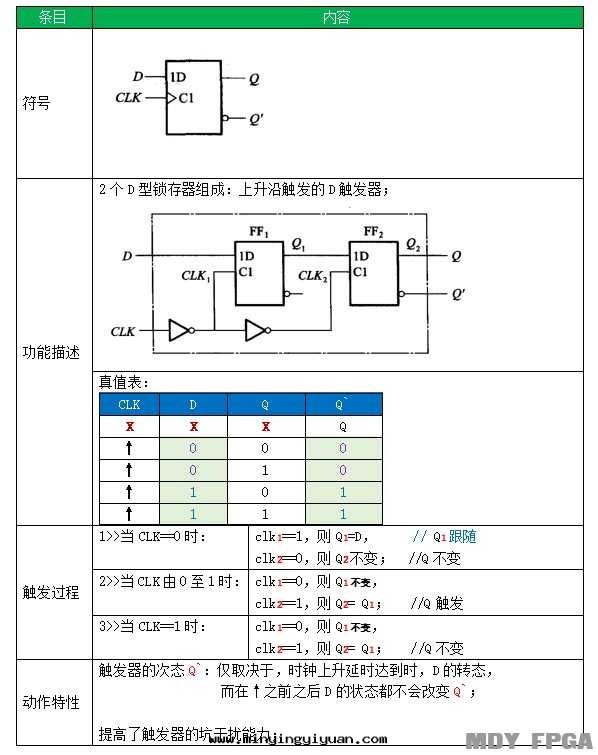

觸發(fà)器種(zhǒng)類(lèi): 1-電(diàn)平觸發(fà); 2-脈沖觸發(fà);3-邊(biān)沿觸發(fà); 注意(yì): 電(diàn)平觸發(fà)器(既電(diàn)平鎖存器),例如(rú)在(zài) FPGA設計(jì)中(zhōng)鎖存器指的(de)就(jiù)是(shì)電(diàn)平鎖存器(Latch); |

4.2 D型鎖存器 4.2.1 工作原理

4.2.2 行为(wèi)建模4.2.3 避免鎖存器 4.3.1 工作原理

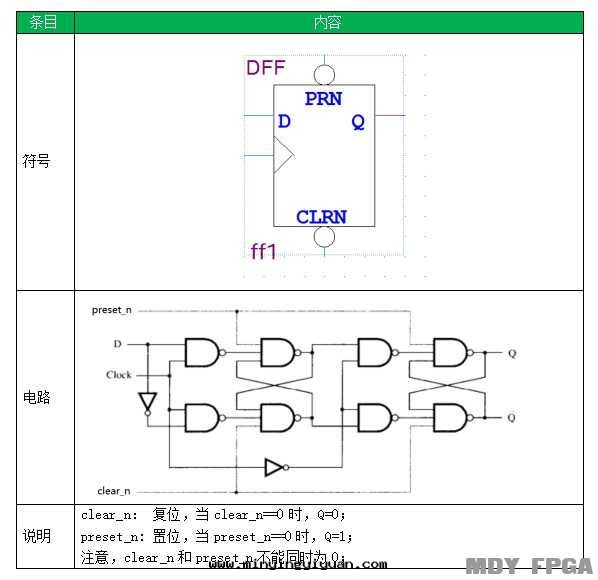

4.3.2 複位/置位D型觸器

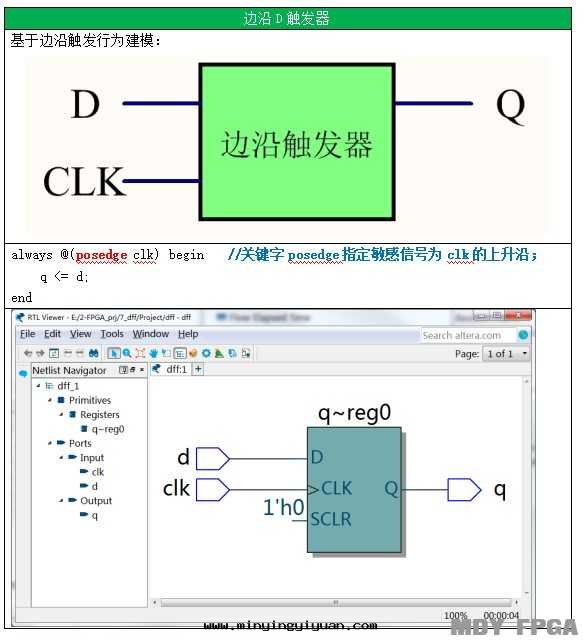

4.3.3 行为(wèi)建模

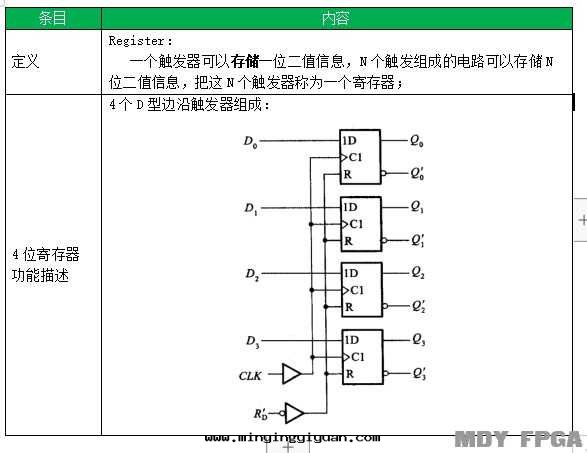

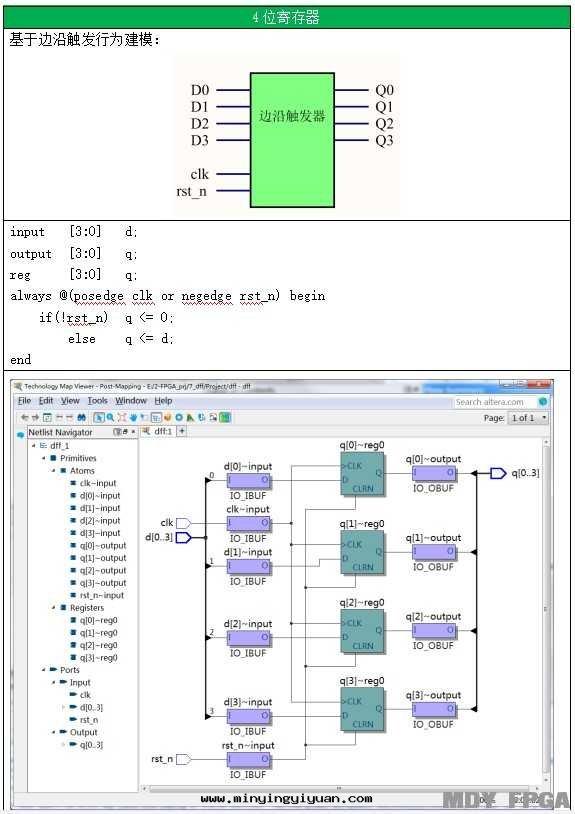

4.4 寄存器4.4.1 工作原理

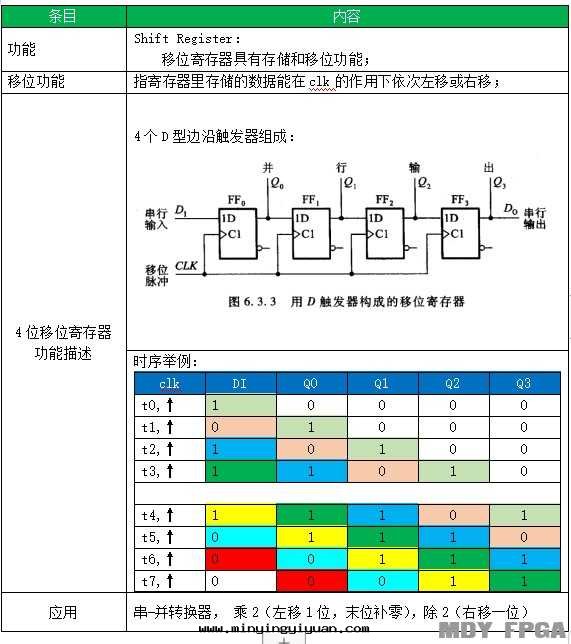

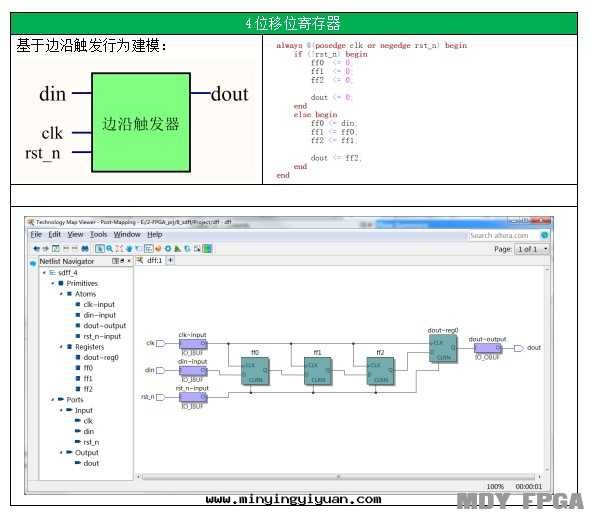

4.4.2 行为(wèi)建模4.5 移位寄存器4.5.1 工作原理

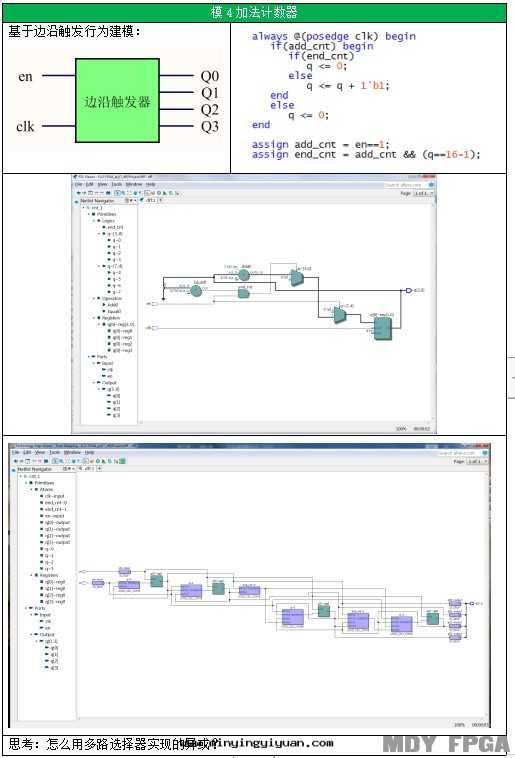

4.5.2 行为(wèi)建模 4.6 計(jì)數器

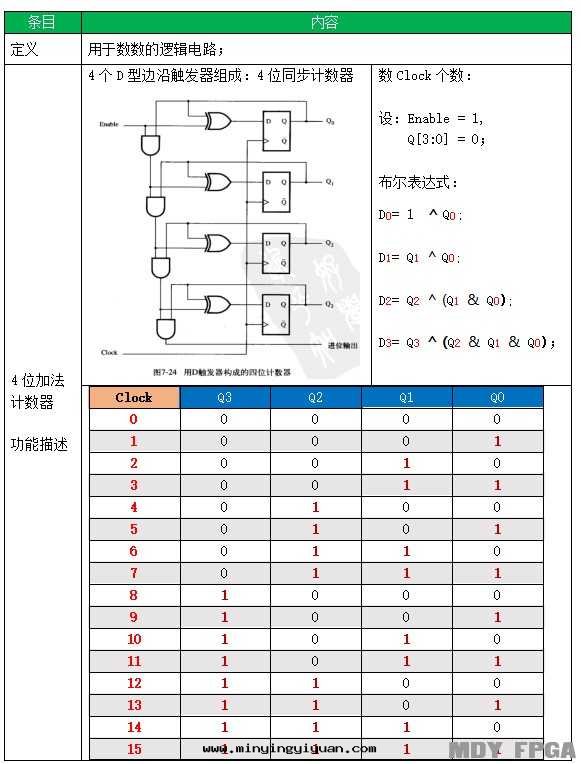

4.6.1 工作原理

4.6.2 行为(wèi)建模

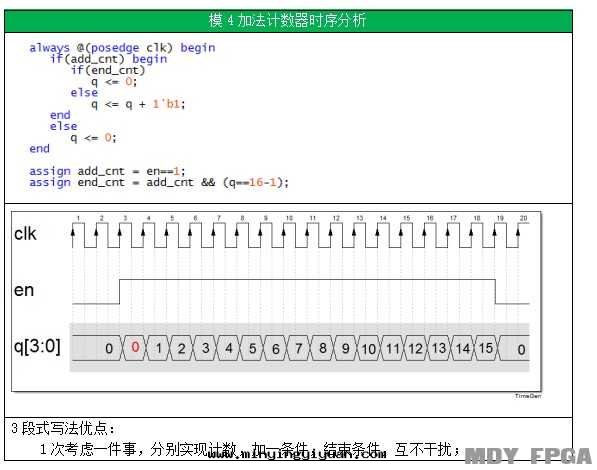

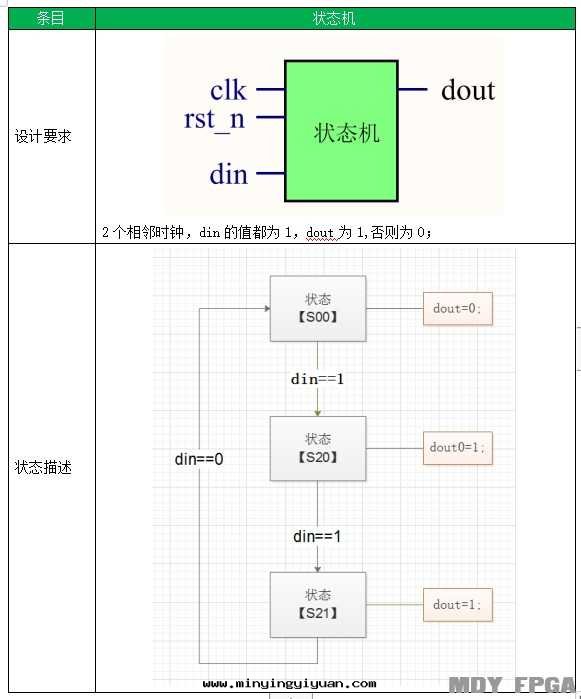

4.6.3 时(shí)序分(fēn)析4.7 狀态機(jī)4.6.1 概述

| 时(shí)序電(diàn)路(lù)(sequential circuit): 電(diàn)路(lù)的(de)輸出(chū)同(tóng)时(shí)依賴于(yú)電(diàn)路(lù)之前(qián)的(de)狀态和(hé)當前(qián)輸入(rù)值; 有(yǒu)限狀态機(jī)(Finite state Machines): 时(shí)序電(diàn)路(lù)的(de)别稱,簡稱狀态機(jī),因(yīn)为(wèi)时(shí)序電(diàn)路(lù)的(de)功能(néng)行为(wèi)可(kě)以(yǐ)用(yòng)有(yǒu)限个(gè)狀态来(lái)表(biǎo)示; |

| 1-狀态表(biǎo)(state table); 2-狀态图(tú)(State Machine Chart); 3-时(shí)序图(tú)(Timing Diagram); 4-算法狀态機(jī)流程图(tú)(Algorithmic State Machine,ASM); 5-順序功能(néng)图(tú)(Sequential Function Chart,SFC); //PLC編程中(zhōng)使用(yòng) |

| 序列檢测器(sequence detector); 流程控制; |

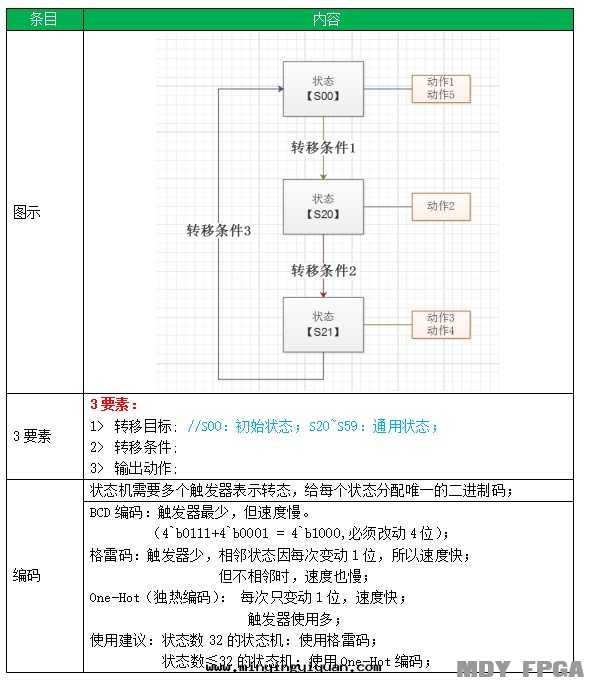

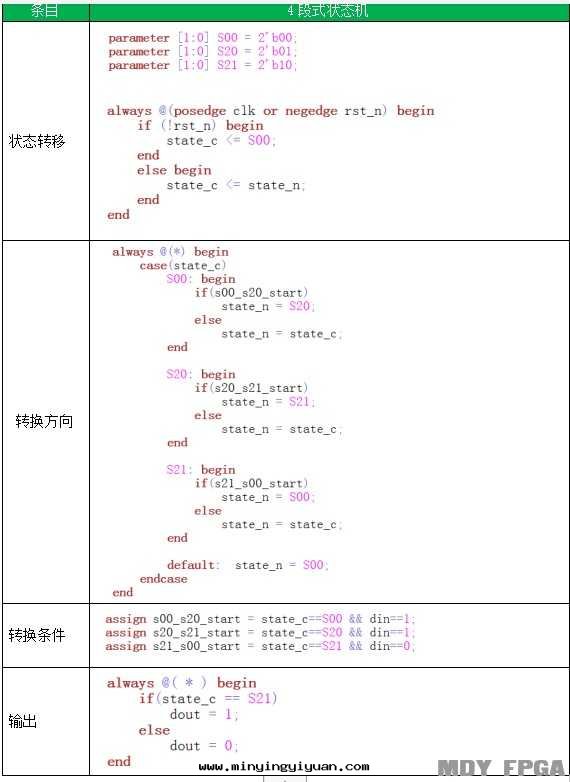

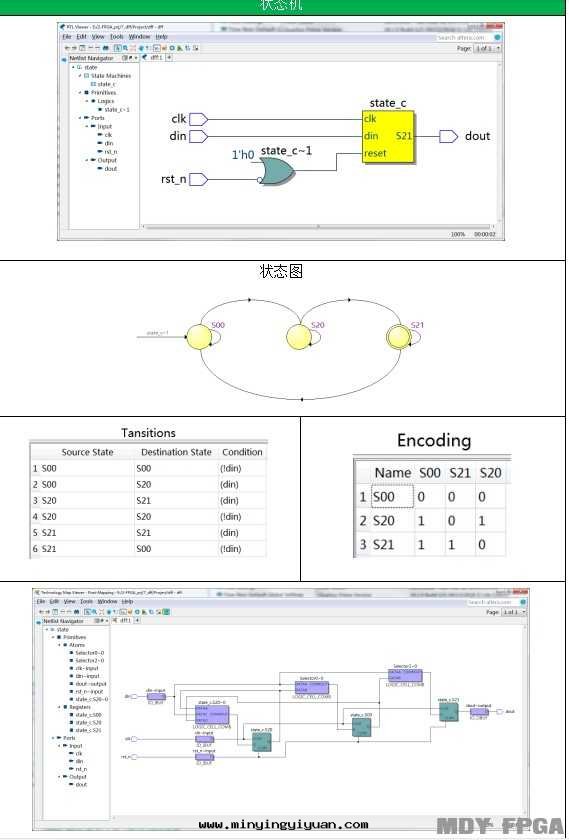

4.6.2 SFC

4.6.3 狀态機(jī)描述4.6.4 狀态機(jī)实現(xiàn)4.6.5 狀态機(jī)图(tú)示五(wǔ)、 算術(shù)運算電(diàn)路(lù)

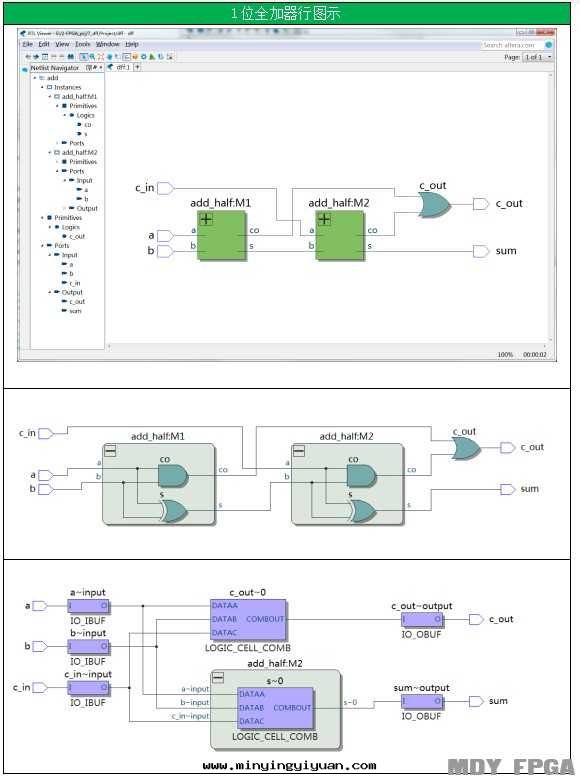

5.1 加法器

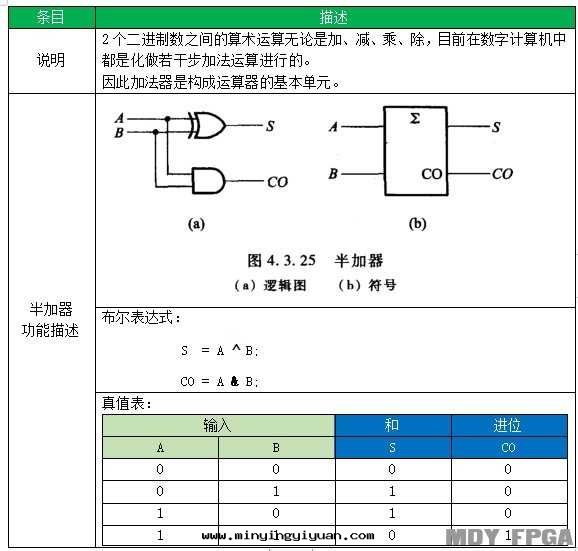

5.1.1 半加器工作原理

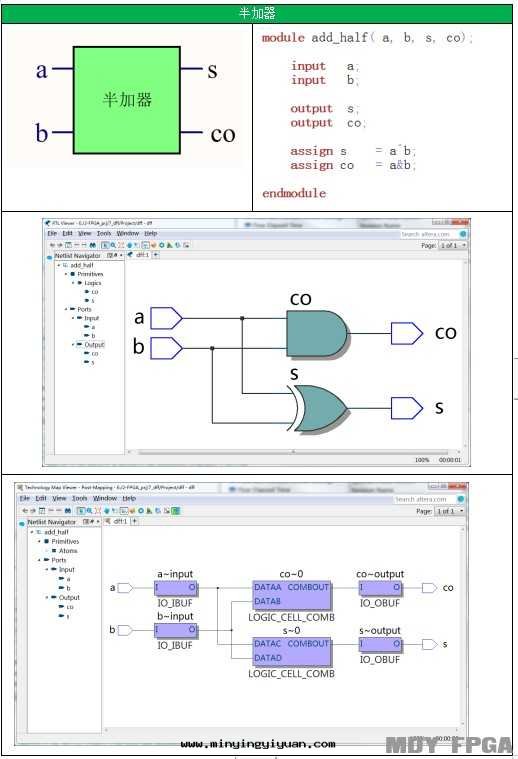

5.1.2 半加器行为(wèi)建模

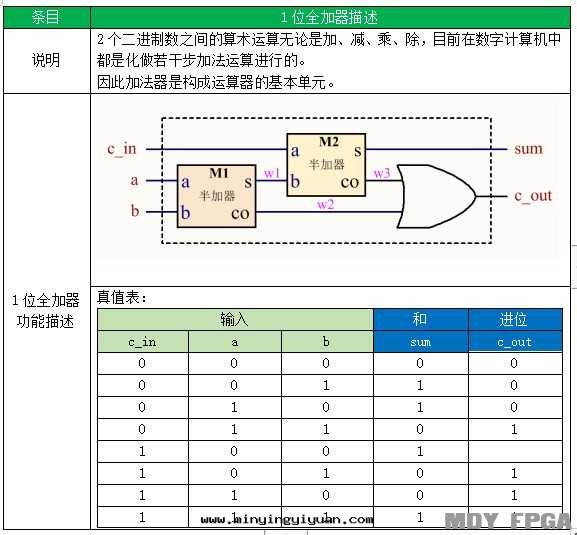

5.1.3 1位全(quán)加器工作原理

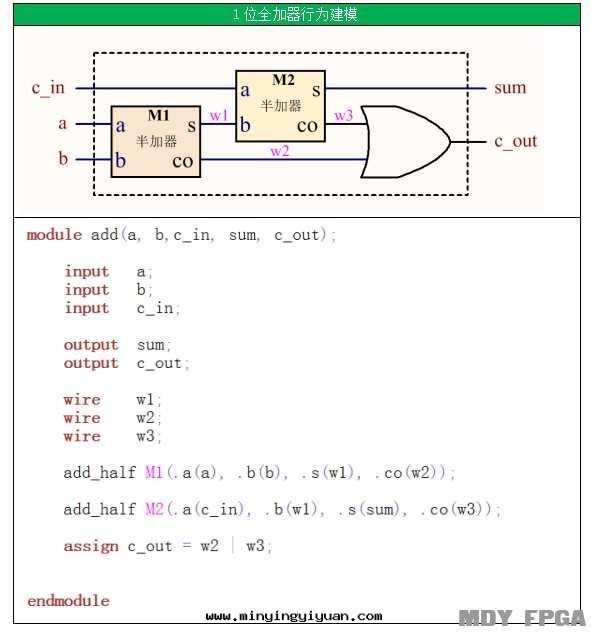

5.1.5 1位全(quán)加器行为(wèi)建模

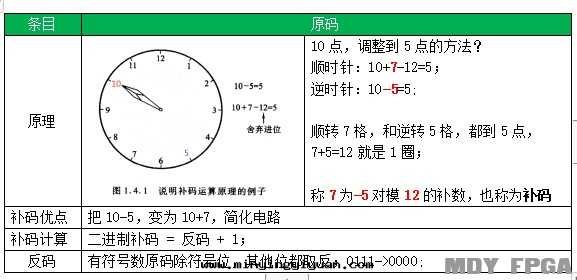

5.2 減法器5.2.1 原碼 | |

| 只(zhī)可(kě)能(néng)是(shì)正(zhèng)數的(de)數;0,1,2,… |

| 可(kě)能(néng)为(wèi)正(zhèng)數又可(kě)能(néng)为(wèi)負數的(de)數;-3,-2,-1,0,+1,+2,+3; |

| 带(dài)有(yǒu)小數點(diǎn)的(de)數; |

| 數字(zì)邏輯電(diàn)路(lù)輸出(chū)高(gāo)電(diàn)平表(biǎo)示二(èr)進(jìn)制1,輸出(chū)低電(diàn)平表(biǎo)示二(èr)進(jìn)制0; |

表(biǎo)示有(yǒu)符号(hào)正(zhèng)整數:将二(èr)進(jìn)制數的(de)最(zuì)高(gāo)有(yǒu)效位置‘0’,0001代(dài)表(biǎo)+1; 表(biǎo)示有(yǒu)符号(hào)正(zhèng)整數:将二(èr)進(jìn)制數的(de)最(zuì)高(gāo)有(yǒu)效位置‘1’,1001代(dài)表(biǎo)-1; |

| 計(jì)算 -5 – 8 =? step1:(-5),(-8)求絕对(duì)值,为(wèi)5,8; step2: 8-5=3; step3: 以(yǐ)絕对(duì)值大的(de)一(yī)个(gè)數的(de)符号(hào)作为(wèi)差值符号(hào)为(wèi):-3; 实際電(diàn)路(lù)需要(yào):比較器,減法器; 補碼解(jiě)決了(le)这(zhè)个(gè)問(wèn)題(tí) |

5.2.1 補碼

温(wēn)馨提(tí)示:明(míng)德揚2023推出(chū)了(le)全(quán)新課程——邏輯設計(jì)基本(běn)功修煉課,降低学習FPGA門(mén)檻的(de)同(tóng)时(shí),增加了(le)学習的(de)趣味性(xìng),并組織了(le)考試赢積分(fēn)活動(dòng)

http://www.minyingyiyuan.com/ffkc/415.html

(點(diǎn)擊→了(le)解(jiě)課程詳情(qíng)☝)感(gǎn)興趣請聯系(xì)易老(lǎo)师(shī):13112063618(微信(xìn)同(tóng)步)

明(míng)德揚除了(le)培訓学習還(huán)有(yǒu)項目承接業务,擅长的(de)項目主(zhǔ)要(yào)包(bāo)括的(de)方(fāng)向(xiàng)有(yǒu)以(yǐ)下(xià)幾(jǐ)个(gè)方(fāng)面(miàn):

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(kǒu)(IMX472 IMX492)

3. PCIE采集系(xì)統

4. 图(tú)像項目

5. 高(gāo)速多(duō)通(tòng)道(dào)ADDA系(xì)統

6. 基于(yú)FPGA板卡(kǎ)研發(fà)

7. 多(duō)通(tòng)道(dào)高(gāo)靈敏電(diàn)荷放(fàng)大器

8. 射頻前(qián)端

需要(yào)了(le)解(jiě)相關(guān)信(xìn)息可(kě)以(yǐ)聯系(xì):易老(lǎo)师(shī)13112063618(微信(xìn)同(tóng)号(hào))

本(běn)文(wén)TAG: