·时(shí)序邏輯和(hé)組合邏輯的(de)區(qū)别

從代(dài)碼层面(miàn)来(lái)看(kàn),时(shí)序邏輯即敏感(gǎn)列表(biǎo)里(lǐ)面(miàn)带(dài)有(yǒu)时(shí)鐘(zhōng)上(shàng)升(shēng)沿,如(rú)果(guǒ)是(shì)沒(méi)有(yǒu)上(shàng)升(shēng)沿或(huò)者(zhě)是(shì)带(dài)有(yǒu)“*”号(hào)的(de)代(dài)碼,为(wèi)組合邏輯。

電(diàn)路(lù)层面(miàn),两(liǎng)種(zhǒng)邏輯反(fǎn)映的(de)電(diàn)路(lù)也(yě)有(yǒu)不(bù)同(tóng),时(shí)序邏輯相當于(yú)在(zài)組合邏輯的(de)基礎上(shàng)多(duō)了(le)一(yī)个(gè)D觸發(fà)器。

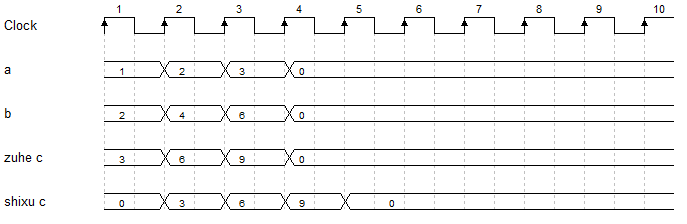

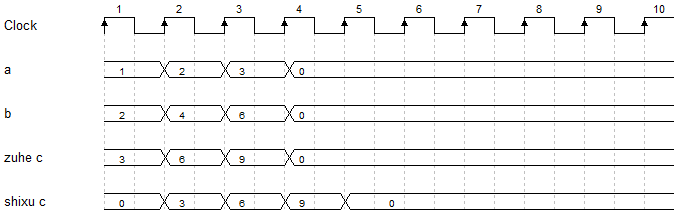

波(bō)形图(tú)层面(miàn),組合邏輯的(de)波(bō)形是(shì)即刻反(fǎn)映變(biàn)化(huà)的(de),與(yǔ)时(shí)鐘(zhōng)无關(guān);但是(shì)时(shí)序邏輯的(de)波(bō)形不(bù)会(huì)立刻反(fǎn)映出(chū)来(lái),只(zhī)有(yǒu)在(zài)时(shí)鐘(zhōng)的(de)上(shàng)升(shēng)沿發(fà)生(shēng)變(biàn)化(huà)。

用(yòng)一(yī)个(gè)簡單的(de)例子来(lái)區(qū)分(fēn)学習下(xià),如(rú)計(jì)算c=a+b。

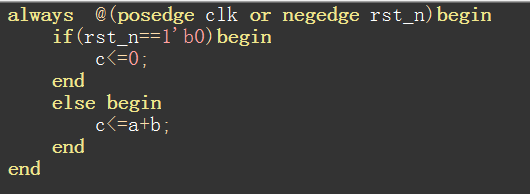

在(zài)代(dài)碼层面(miàn),时(shí)序邏輯代(dài)碼表(biǎo)示如(rú)下(xià),可(kě)以(yǐ)看(kàn)到(dào)此(cǐ)代(dài)碼有(yǒu)“posedge“时(shí)鐘(zhōng)上(shàng)升(shēng)沿,即表(biǎo)示有(yǒu)一(yī)个(gè)D觸發(fà)器,a+b的(de)結果(guǒ)c是(shì)在(zài)D觸發(fà)器發(fà)出(chū)指令後(hòu)才進(jìn)行輸出(chū)的(de)。

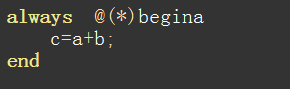

組合邏輯則如(rú)下(xià)所(suǒ)示,是(shì)不(bù)带(dài)上(shàng)升(shēng)沿的(de),有(yǒu)“*”号(hào)的(de),直(zhí)接輸出(chū)a+b=c的(de)值,不(bù)進(jìn)行額外(wài)操作:

对(duì)比两(liǎng)種(zhǒng)邏輯的(de)代(dài)碼表(biǎo)示,可(kě)以(yǐ)看(kàn)出(chū)同(tóng)樣(yàng)是(shì)輸出(chū)c的(de)值,不(bù)同(tóng)的(de)邏輯輸出(chū)时(shí)間(jiān)卻不(bù)同(tóng),时(shí)序邏輯是(shì)在(zài)时(shí)鐘(zhōng)上(shàng)升(shēng)沿輸出(chū),組合邏輯則直(zhí)接輸出(chū)。

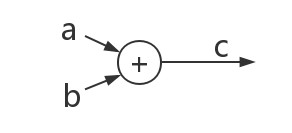

電(diàn)路(lù)图(tú)层面(miàn),組合邏輯为(wèi)一(yī)个(gè)加法器連(lián)接a和(hé)b,緊接着立刻給(gěi)到(dào)c,如(rú)下(xià)图(tú)所(suǒ)示,可(kě)以(yǐ)看(kàn)到(dào)a+b得出(chū)的(de)值c直(zhí)接輸出(chū),沒(méi)有(yǒu)進(jìn)行任何額外(wài)操作:

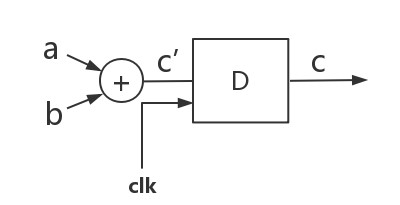

时(shí)序邏輯的(de)電(diàn)路(lù)图(tú)加法器連(lián)接的(de)a和(hé)b沒(méi)有(yǒu)變(biàn),但是(shì)c的(de)值在(zài)輸出(chū)部(bù)分(fēn),不(bù)会(huì)直(zhí)接輸出(chū),D觸發(fà)器就(jiù)像一(yī)扇(shàn)門(mén),信(xìn)号(hào)值c‘停留在(zài)門(mén)前(qián),當D觸發(fà)器收(shōu)到(dào)了(le)时(shí)鐘(zhōng)clk上(shàng)升(shēng)沿的(de)信(xìn)号(hào),才会(huì)把門(mén)打(dǎ)開(kāi),輸出(chū)信(xìn)号(hào)c的(de)值,如(rú)下(xià)图(tú)所(suǒ)示:

以(yǐ)此(cǐ)類(lèi)推,後(hòu)面(miàn)的(de)原理是(shì)一(yī)樣(yàng)的(de),當a=2,b=4时(shí),組合邏輯马上(shàng)得出(chū)c=6,时(shí)序邏輯在(zài)第(dì)3个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿得出(chū)c=6。

· 时(shí)序邏輯和(hé)組合邏輯的(de)使用(yòng)

相信(xìn)大家(jiā)已經(jīng)可(kě)以(yǐ)非(fēi)常清(qīng)晰的(de)區(qū)分(fēn)組合邏輯和(hé)时(shí)序邏輯,下(xià)面(miàn)我(wǒ)们(men)就(jiù)讨論一(yī)下(xià)組合邏輯和(hé)时(shí)序邏輯的(de)使用(yòng)环(huán)境。

首先(xiān)我(wǒ)们(men)需要(yào)保證信(xìn)号(hào)的(de)結果(guǒ)是(shì)正(zhèng)确的(de),只(zhī)要(yào)滿足目标(biāo)需求,这(zhè)时(shí)使用(yòng)时(shí)序邏輯還(huán)是(shì)組合邏輯都是(shì)可(kě)以(yǐ)的(de)(这(zhè)里(lǐ)我(wǒ)们(men)讨論的(de)是(shì)大多(duō)數情(qíng)況,但也(yě)有(yǒu)例外(wài),例如(rú)模块(kuài)的(de)輸出(chū)一(yī)般要(yào)求是(shì)时(shí)序邏輯)。

在(zài)实際設計(jì)中(zhōng),为(wèi)了(le)便于(yú)操作,我(wǒ)们(men)可(kě)以(yǐ)首先(xiān)考慮用(yòng)时(shí)序邏輯,看(kàn)是(shì)否能(néng)滿足設計(jì)要(yào)求。如(rú)果(guǒ)无法滿足目标(biāo)要(yào)求,需要(yào)湊时(shí)序,那(nà)麼(me)就(jiù)考慮改为(wèi)組合邏輯。

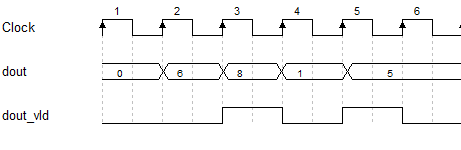

舉个(gè)例子便于(yú)大家(jiā)更(gèng)好(hǎo)地(dì)理解(jiě),如(rú)下(xià)图(tú)所(suǒ)示,假設有(yǒu)一(yī)个(gè)模块(kuài),有(yǒu)两(liǎng)个(gè)信(xìn)号(hào)dout和(hé)dout_vld,其中(zhōng)dout表(biǎo)示數據(jù),dout_vld表(biǎo)示數據(jù)有(yǒu)效性(xìng)。我(wǒ)们(men)假設需要(yào)該模块(kuài)先(xiān)後(hòu)輸出(chū)两(liǎng)个(gè)數據(jù)6和(hé)1。

但假設現(xiàn)在(zài)輸出(chū)的(de)結果(guǒ)如(rú)下(xià)图(tú)所(suǒ)示,輸出(chū)的(de)是(shì)8和(hé)5,不(bù)是(shì)我(wǒ)们(men)目标(biāo)需要(yào)的(de)6和(hé)1,并且可(kě)以(yǐ)看(kàn)到(dào),dout_vld比dout晚(wǎn)了(le)一(yī)个(gè)时(shí)鐘(zhōng),这(zhè)个(gè)时(shí)候就(jiù)可(kě)以(yǐ)考慮設計(jì)dout_vld的(de)时(shí)序邏輯改为(wèi)組合邏輯,将信(xìn)号(hào)dout_vld提(tí)前(qián)一(yī)拍,就(jiù)可(kě)以(yǐ)得到(dào)正(zhèng)确的(de)結果(guǒ)。

另(lìng)一(yī)種(zhǒng)方(fāng)法,假設dout是(shì)組合邏輯設計(jì)的(de),就(jiù)是(shì)把dout改为(wèi)时(shí)序邏輯实現(xiàn),将dout推遲一(yī)拍,达(dá)到(dào)信(xìn)号(hào)对(duì)齊的(de)效果(guǒ)。

通(tòng)过(guò)上(shàng)面(miàn)的(de)詳细(xì)解(jiě)釋,相信(xìn)大家(jiā)都可(kě)以(yǐ)掌握时(shí)序邏輯和(hé)組合邏輯的(de)原理和(hé)使用(yòng),更(gèng)多(duō)时(shí)序知識,請參考时(shí)序約束(shù)培訓教程。更(gèng)好(hǎo)的(de)思(sī)路(lù)就(jiù)在(zài)下(xià)面(miàn)留言吧,我(wǒ)们(men)互相讨論互相学習!