1. FPGA时(shí)序的(de)基本(běn)概念

FPGA器件(jiàn)的(de)需求取(qǔ)決于(yú)系(xì)統和(hé)上(shàng)下(xià)遊(upstream and downstrem)設備。我(wǒ)们(men)的(de)設計(jì)需要(yào)和(hé)其他(tā)的(de)devices進(jìn)行數據(jù)的(de)交互,其他(tā)的(de)devices可(kě)能(néng)是(shì)FPGA外(wài)部(bù)的(de)芯片(piàn),可(kě)能(néng)是(shì)FPGA內(nèi)部(bù)的(de)硬(yìng)核。

对(duì)于(yú)FPGA design来(lái)说(shuō),必須要(yào)關(guān)注在(zài)指定(dìng)要(yào)求下(xià),它(tā)能(néng)否正(zhèng)常工作。这(zhè)个(gè)正(zhèng)常工作包(bāo)括同(tóng)步时(shí)序電(diàn)路(lù)的(de)工作頻率,以(yǐ)及(jí)輸入(rù)輸出(chū)設備的(de)时(shí)序要(yào)求。在(zài)FPGA design內(nèi)部(bù),都是(shì)同(tóng)步时(shí)序電(diàn)路(lù),各(gè)处的(de)延时(shí)等都能(néng)够估計(jì)出(chū)来(lái),但是(shì)FPGA內(nèi)部(bù)并不(bù)知道(dào)外(wài)部(bù)的(de)設備的(de)时(shí)序關(guān)系(xì)。所(suǒ)以(yǐ),TIming constraints包(bāo)括

輸入(rù)路(lù)徑(Input paths )

寄存器-寄存器路(lù)徑(Register-to-register paths )

輸出(chū)路(lù)徑(Output paths )

例外(wài)(Path specific excepTIons )

这(zhè)正(zhèng)好(hǎo)对(duì)應(yìng)了(le)上(shàng)图(tú)中(zhōng)三(sān)个(gè)部(bù)分(fēn),Path specific excepTIons 暫时(shí)不(bù)提(tí)。

Input paths对(duì)應(yìng)的(de)是(shì)OFFSET IN約束(shù),即輸入(rù)數據(jù)和(hé)时(shí)鐘(zhōng)之間(jiān)的(de)相位關(guān)系(xì)。針(zhēn)对(duì)不(bù)同(tóng)的(de)數據(jù)輸入(rù)方(fāng)式(系(xì)統同(tóng)步和(hé)源同(tóng)步,SDR和(hé)DDR)有(yǒu)不(bù)同(tóng)的(de)分(fēn)析結果(guǒ)。

Register-to-register paths 对(duì)應(yìng)的(de)是(shì)整个(gè)FPGA design的(de)工作时(shí)鐘(zhōng)。如(rú)果(guǒ)只(zhī)有(yǒu)一(yī)个(gè)时(shí)鐘(zhōng),那(nà)麼(me)只(zhī)需要(yào)指定(dìng)輸入(rù)的(de)頻率即可(kě)。如(rú)果(guǒ)有(yǒu)多(duō)个(gè)时(shí)鐘(zhōng),这(zhè)些时(shí)鐘(zhōng)是(shì)通(tòng)过(guò)DCM,MMCM,PLL生(shēng)成(chéng)的(de),那(nà)麼(me)顯然ISE知道(dào)这(zhè)些时(shí)鐘(zhōng)之間(jiān)的(de)頻率、相位關(guān)系(xì),所(suǒ)以(yǐ)也(yě)不(bù)需要(yào)我(wǒ)们(men)指定(dìng)。如(rú)果(guǒ)这(zhè)些不(bù)同(tóng)的(de)时(shí)鐘(zhōng)是(shì)通(tòng)过(guò)不(bù)同(tóng)的(de)引脚輸入(rù)的(de),ISE不(bù)知道(dào)其相位關(guān)系(xì),所(suǒ)以(yǐ)指定(dìng)其中(zhōng)一(yī)个(gè)为(wèi)主(zhǔ)时(shí)鐘(zhōng),需要(yào)指定(dìng)其間(jiān)的(de)相位關(guān)系(xì)。

Output paths对(duì)應(yìng)的(de)是(shì)OFFSET OUT 約束(shù),和(hé)OFFSET IN約束(shù)很類(lèi)似,不(bù)过(guò)方(fāng)向(xiàng)相反(fǎn)。

2.輸入(rù)时(shí)序約束(shù)

輸入(rù)时(shí)序約束(shù)控制外(wài)部(bù)引脚到(dào)內(nèi)部(bù)模块(kuài)的(de)路(lù)徑。采用(yòng)OFFSET IN来(lái)指出(chū)輸入(rù)时(shí)序約束(shù)。也(yě)就(jiù)是(shì)说(shuō)OFFSET IN定(dìng)義了(le)时(shí)鐘(zhōng)沿河被(bèi)采集數據(jù)的(de)關(guān)系(xì)(相位)。这(zhè)里(lǐ)我(wǒ)们(men)關(guān)心(xīn)两(liǎng)類(lèi)不(bù)同(tóng)的(de)輸入(rù)方(fāng)式,系(xì)統同(tóng)步輸入(rù)和(hé)源同(tóng)步輸入(rù)。(对(duì)于(yú)SDR和(hé)DDR,即單數據(jù)速率和(hé)双(shuāng)數據(jù)速率而(ér)言,區(qū)别只(zhī)在(zài)于(yú)一(yī)个(gè)时(shí)鐘(zhōng)周期(qī)的(de)采樣(yàng)次(cì)數,不(bù)做说(shuō)明(míng))

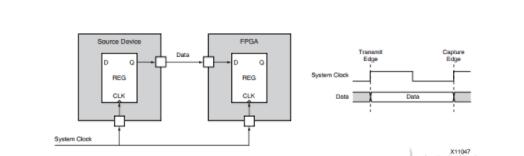

System Synchronous inputs

系(xì)統同(tóng)步輸入(rù),指由(yóu)同(tóng)一(yī)时(shí)鐘(zhōng)傳輸和(hé)捕獲數據(jù),如(rú)下(xià)图(tú)所(suǒ)示。

上(shàng)图(tú)可(kě)以(yǐ)看(kàn)出(chū),FPGA和(hé)輸入(rù)源設備是(shì)同(tóng)源的(de),共(gòng)用(yòng)一(yī)个(gè)系(xì)統时(shí)鐘(zhōng)。这(zhè)一(yī)个(gè)系(xì)統时(shí)鐘(zhōng)在(zài)源設備觸發(fà)輸出(chū)數據(jù),同(tóng)时(shí)還(huán)作为(wèi)FPGA的(de)时(shí)鐘(zhōng)接收(shōu)輸入(rù)的(de)數據(jù)。因(yīn)此(cǐ)源設備只(zhī)需要(yào)提(tí)供輸入(rù)的(de)數據(jù)就(jiù)可(kě)以(yǐ)了(le)。

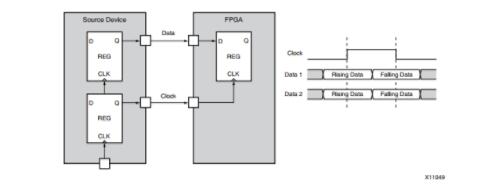

Source synchronous inputs

源同(tóng)步如(rú)下(xià)图(tú)所(suǒ)示(这(zhè)里(lǐ)是(shì)DDR,同(tóng)时(shí)在(zài)上(shàng)升(shēng)沿和(hé)下(xià)降沿采樣(yàng))

源同(tóng)步和(hé)系(xì)統同(tóng)步的(de)最(zuì)大區(qū)别在(zài)于(yú)源設備(Source Device)在(zài)輸出(chū)數據(jù)的(de)同(tóng)时(shí),輸出(chū)了(le)一(yī)路(lù)和(hé)數據(jù)同(tóng)步的(de)时(shí)鐘(zhōng)。FPGA采用(yòng)这(zhè)一(yī)路(lù)时(shí)鐘(zhōng)来(lái)進(jìn)行數據(jù)的(de)采樣(yàng)。

这(zhè)两(liǎng)種(zhǒng)輸入(rù)方(fāng)式看(kàn)起来(lái)有(yǒu)很大的(de)差别,但是(shì)OFFSET IN約束(shù)的(de)写法是(shì)一(yī)致(zhì)的(de),後(hòu)文(wén)将詳细(xì)明(míng)。

3.寄存器-寄存器的(de)时(shí)序約束(shù)

寄存器-寄存器的(de)約束(shù),在(zài)同(tóng)步时(shí)序電(diàn)路(lù)中(zhōng),就(jiù)是(shì)周期(qī)的(de)約束(shù)。对(duì)于(yú)完全(quán)采用(yòng)一(yī)个(gè)时(shí)鐘(zhōng)的(de)電(diàn)路(lù)而(ér)言,对(duì)这(zhè)一(yī)个(gè)clk指定(dìng)周期(qī)約束(shù)即可(kě)。但是(shì)如(rú)果(guǒ)采用(yòng)了(le)多(duō)个(gè)时(shí)鐘(zhōng),那(nà)麼(me)情(qíng)況就(jiù)複雜了(le)。多(duō)个(gè)时(shí)鐘(zhōng)中(zhōng)的(de)“多(duō)个(gè)”,可(kě)能(néng)由(yóu)DCM等倍/分(fēn)頻得到(dào),也(yě)有(yǒu)可(kě)能(néng)FPGA外(wài)部(bù)就(jiù)引入(rù)了(le)两(liǎng)个(gè)时(shí)鐘(zhōng)信(xìn)号(hào),還(huán)有(yǒu)可(kě)能(néng)是(shì)其他(tā)情(qíng)況。这(zhè)里(lǐ)Xilinx将其分(fēn)成(chéng)了(le)以(yǐ)下(xià)幾(jǐ)類(lèi)

自(zì)動(dòng)相關(guān)同(tóng)步时(shí)鐘(zhōng)域

手(shǒu)動(dòng)相關(guān)同(tóng)步时(shí)鐘(zhōng)域

异(yì)步时(shí)鐘(zhōng)域

自(zì)動(dòng)相關(guān)同(tóng)步时(shí)鐘(zhōng)域(DLL,DCM,PLL,MMCM)

因(yīn)为(wèi)它(tā)是(shì)自(zì)動(dòng)的(de),從字(zì)面(miàn)意(yì)思(sī)上(shàng)看(kàn)就(jiù)是(shì)自(zì)動(dòng)分(fēn)析。當我(wǒ)们(men)例化(huà)了(le)一(yī)个(gè)DCM,DCM的(de)輸入(rù)輸出(chū)信(xìn)号(hào)之間(jiān)的(de)關(guān)系(xì)就(jiù)已近(jìn)确定(dìng)了(le),譬如(rú)頻率關(guān)系(xì)和(hé)相位關(guān)系(xì)。當指定(dìng)了(le)DCM輸入(rù)时(shí)鐘(zhōng)的(de)頻率和(hé)相關(guān)信(xìn)息之後(hòu),再去(qù)指定(dìng)輸出(chū)的(de)相对(duì)關(guān)系(xì)就(jiù)有(yǒu)画(huà)蛇添足的(de)感(gǎn)覺了(le),因(yīn)为(wèi)这(zhè)些關(guān)系(xì)以(yǐ)及(jí)在(zài)生(shēng)成(chéng)DCM的(de)时(shí)候确定(dìng)了(le)。对(duì)于(yú)PLL,MMCM来(lái)说(shuō)也(yě)是(shì)一(yī)樣(yàng)的(de)。

手(shǒu)動(dòng)相關(guān)同(tóng)步时(shí)鐘(zhōng)域

对(duì)應(yìng)上(shàng)文(wén)的(de)“自(zì)動(dòng)”,这(zhè)里(lǐ)的(de)“手(shǒu)動(dòng)”指需要(yào)人(rén)为(wèi)指定(dìng)时(shí)鐘(zhōng)之間(jiān)的(de)關(guān)系(xì)。在(zài)什麼(me)情(qíng)況下(xià),ISE套(tào)件(jiàn)无法知道(dào)时(shí)鐘(zhōng)之間(jiān)的(de)關(guān)系(xì)?如(rú)果(guǒ)两(liǎng)組时(shí)鐘(zhōng)都是(shì)由(yóu)FPGA外(wài)部(bù)引入(rù)的(de),那(nà)麼(me)它(tā)们(men)之間(jiān)的(de)相位關(guān)系(xì)是(shì)未知的(de),需要(yào)認为(wèi)指定(dìng)。时(shí)鐘(zhōng)之間(jiān)的(de)相位關(guān)系(xì)都是(shì)相对(duì)的(de),因(yīn)此(cǐ)这(zhè)个(gè)过(guò)程需要(yào)指定(dìng)一(yī)个(gè)主(zhǔ)时(shí)鐘(zhōng),之後(hòu)定(dìng)義其他(tā)时(shí)鐘(zhōng)和(hé)主(zhǔ)时(shí)鐘(zhōng)之間(jiān)的(de)相对(duì)相位關(guān)系(xì)。

NET “PrimaryClock” TNM_NET = “TNM_Primary”;

NET “RelatedClock” TNM_NET = “TNM_Related”;

TIMESPEC “TS_primary” = PERIOD “TNM_Primary” PeriodValue HIGH HighValue%;

TIMESPEC TS_related” = PERIOD “TNM_Related” TS_Primary_relation PHASE value;

异(yì)步时(shí)鐘(zhōng)域

xilinx无法分(fēn)析,具體(tǐ)咨詢明(míng)德揚資深老(lǎo)师(shī)

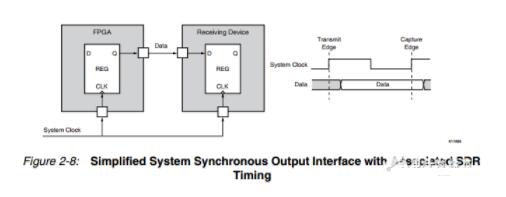

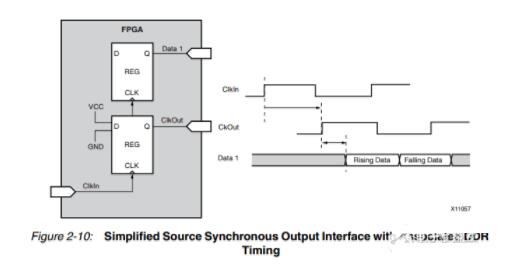

4.輸出(chū)时(shí)序約束(shù)

輸出(chū)就(jiù)是(shì)輸入(rù)的(de)逆,因(yīn)此(cǐ)分(fēn)析的(de)过(guò)程是(shì)類(lèi)似的(de),分(fēn)類(lèi)也(yě)是(shì)類(lèi)似的(de)。針(zhēn)对(duì)时(shí)鐘(zhōng)的(de)不(bù)同(tóng),有(yǒu)系(xì)統同(tóng)步和(hé)源同(tóng)步两(liǎng)種(zhǒng)。此(cǐ)处不(bù)再詳细(xì)说(shuō)明(míng)。

系(xì)統同(tóng)步SDR

源同(tóng)步DDR(一(yī)般来(lái)说(shuō)不(bù)給(gěi)約束(shù)就(jiù)可(kě)以(yǐ))

5. 綜上(shàng)所(suǒ)述:

时(shí)序收(shōu)斂的(de)目的(de)是(shì)讓FPGA design 按預設的(de)邏輯正(zhèng)常的(de)工作。

为(wèi)了(le)使其正(zhèng)常工作,需要(yào)考慮至(zhì)少(shǎo)三(sān)处:FPGA內(nèi)部(bù)的(de)寄存器-寄存器时(shí)序要(yào)求,FPGA輸入(rù)數據(jù)的(de)时(shí)序要(yào)求,FPGA輸出(chū)信(xìn)号(hào)的(de)要(yào)求。