導读(dú)——不(bù)是(shì)每个(gè)人(rén)都能(néng)成(chéng)为(wèi)一(yī)代(dài)宗师(shī),因(yīn)为(wèi)在(zài)一(yī)个(gè)时(shí)代(dài)宗师(shī)只(zhī)有(yǒu)少(shǎo)數人(rén),成(chéng)不(bù)了(le)宗师(shī),可(kě)以(yǐ)選擇成(chéng)为(wèi)門(mén)派高(gāo)手(shǒu),立足武林(lín)的(de)六(liù)合一(yī)之路(lù)无外(wài)乎秘密武器、江湖(hú)規矩、內(nèi)功心(xīn)法、武術(shù)動(dòng)作、內(nèi)功修煉及(jí)实戰經(jīng)验(yàn)。修煉六(liù)脈神劍,成(chéng)为(wèi)高(gāo)手(shǒu),行走(zǒu)江湖(hú),行俠仗義,斬奸除惡,開(kāi)啟江湖(hú)人(rén)生(shēng)!

0.引言——高(gāo)手(shǒu)沒(méi)有(yǒu)天(tiān)賦,只(zhī)有(yǒu)初心(xīn)、選擇、努力和(hé)毅力

图(tú)1 工業視覺处理(图(tú)片(piàn)来(lái)源:自(zì)電(diàn)子元(yuán)件(jiàn)技術(shù))

图(tú)像处理是(shì)通(tòng)过(guò)对(duì)图(tú)像進(jìn)行增強(qiáng)、複原、重(zhòng)建、分(fēn)析及(jí)特(tè)征識别等处理以(yǐ)得到(dào)目标(biāo)結果(guǒ),在(zài)工業、消費電(diàn)子、安(ān)防等領域具有(yǒu)廣泛的(de)應(yìng)用(yòng)。FPAG支持(chí)实时(shí)流水(shuǐ)線(xiàn)運算(跟工廠(chǎng)流水(shuǐ)線(xiàn)作業一(yī)樣(yàng)、不(bù)同(tóng)的(de)工序可(kě)以(yǐ)同(tóng)时(shí)開(kāi)展(zhǎn)),具有(yǒu)高(gāo)实时(shí)性(xìng)特(tè)點(diǎn)(通(tòng)过(guò)并行作業、可(kě)以(yǐ)在(zài)极(jí)短(duǎn)的(de)时(shí)間(jiān)內(nèi)完成(chéng)任务),是(shì)图(tú)像处理應(yìng)用(yòng)的(de)主(zhǔ)要(yào)平台(tái),在(zài)一(yī)些高(gāo)并發(fà)性(xìng)、实时(shí)性(xìng)要(yào)求較高(gāo)的(de)應(yìng)用(yòng)領域,只(zhī)能(néng)通(tòng)过(guò)FPGA实現(xiàn)。

FPGA图(tú)像工程师(shī)的(de)薪資水(shuǐ)平普遍(biàn)較高(gāo),但綜合能(néng)力要(yào)求极(jí)高(gāo),又是(shì)算法、又是(shì)編程,又是(shì)硬(yìng)件(jiàn),不(bù)是(shì)迫不(bù)得已或(huò)者(zhě)興趣,很多(duō)人(rén)一(yī)開(kāi)始就(jiù)選擇放(fàng)棄,实際入(rù)門(mén)真(zhēn)的(de)是(shì)这(zhè)樣(yàng)子吗?跟很多(duō)技術(shù)一(yī)樣(yàng),難不(bù)在(zài)技術(shù)本(běn)身(shēn),在(zài)学習的(de)初心(xīn)、态度(dù)、流程及(jí)方(fāng)法,下(xià)面(miàn)是(shì)本(běn)人(rén)基于(yú)多(duō)年(nián)的(de)經(jīng)验(yàn)整理FPGA图(tú)像工程师(shī)晉級之路(lù)。

1.選武器——倚天(tiān)QUARTUS、屠龙VIVADO,掌控优先(xiān)

FPGA開(kāi)發(fà)的(de)工具平台(tái)包(bāo)括綜合編譯工具、仿真(zhēn)工具、代(dài)碼編写工具及(jí)入(rù)門(mén)開(kāi)發(fà)板,選好(hǎo)用(yòng)好(hǎo)工具平台(tái)不(bù)僅可(kě)以(yǐ)降低入(rù)門(mén)難度(dù),還(huán)利于(yú)快(kuài)速提(tí)升(shēng)設計(jì)開(kāi)發(fà)能(néng)力。工具平台(tái)選擇以(yǐ)易于(yú)入(rù)門(mén),便于(yú)熟練掌控,利于(yú)升(shēng)級为(wèi)基本(běn)原則,下(xià)面(miàn)是(shì)有(yǒu)關(guān)工具平台(tái)選擇、使用(yòng)方(fāng)法及(jí)相關(guān)資料的(de)分(fēn)享:

(1)選開(kāi)發(fà)工具

①綜合編譯工具——优選QUARTUS,升(shēng)級VIVADO

主(zhǔ)流的(de)FPGA廠(chǎng)商主(zhǔ)要(yào)有(yǒu):國(guó)際Intel、Xinlinx、Lattice等,國(guó)內(nèi)的(de)紫光(guāng)同(tóng)創、京(jīng)微齊力、高(gāo)雲(yún)半導體(tǐ)等,每家(jiā)廠(chǎng)商都有(yǒu)自(zì)己的(de)開(kāi)發(fà)工具,解(jiě)決新建工程、仿真(zhēn)綜合,配置管(guǎn)脚、下(xià)载和(hé)在(zài)線(xiàn)調試等問(wèn)題(tí),功能(néng)大同(tóng)小异(yì),差异(yì)主(zhǔ)要(yào)存在(zài)于(yú)操作習慣、性(xìng)能(néng)及(jí)操作方(fāng)法等方(fāng)面(miàn)。主(zhǔ)流的(de)開(kāi)發(fà)工具主(zhǔ)要(yào)有(yǒu)来(lái)自(zì)Intel的(de)QUARTUS和(hé)Xilinx的(de)ISE、VIVADO,其中(zhōng)ISE是(shì)XILINX較早(zǎo)開(kāi)發(fà)的(de)版本(běn),适用(yòng)中(zhōng)低端芯片(piàn)的(de)開(kāi)發(fà),VIVADO是(shì)XILINX近(jìn)期(qī)推出(chū)的(de)開(kāi)發(fà)平台(tái),适用(yòng)于(yú)XILINX的(de)中(zhōng)高(gāo)端芯片(piàn)的(de)開(kāi)發(fà)(不(bù)支持(chí)低端芯片(piàn)的(de)開(kāi)發(fà))。

表(biǎo)1 QUARTUS與(yǔ)VIVADO比較

相比而(ér)言,QUARTUS无論是(shì)对(duì)資源的(de)要(yào)求,還(huán)是(shì)使用(yòng)簡單性(xìng)都要(yào)优于(yú)VIVADO,但功能(néng)的(de)齊全(quán)性(xìng)低于(yú)VIVADO,綜合市(shì)面(miàn)上(shàng)Intel的(de)FPGA開(kāi)發(fà)板相对(duì)比較便宜,建議初学者(zhě)先(xiān)選擇QUARTUS入(rù)門(mén)学習,掌握熟悉之後(hòu),根(gēn)據(jù)个(gè)人(rén)情(qíng)況及(jí)開(kāi)展(zhǎn)具體(tǐ)項目的(de)要(yào)求,再学習使用(yòng)VIVADO。

備注——綜合編譯工具下(xià)载地(dì)址:

1) QUARTUS软(ruǎn)件(jiàn)安(ān)裝(zhuāng)包(bāo),建議安(ān)裝(zhuāng)18.1精簡版本(běn)的(de),不(bù)需要(yào)破解(jiě)。

下(xià)载地(dì)址:

http://www.fpgabbs.cn/forum.php?mod=viewthread&tid=429&extra=page%3D1

2) VIVADO软(ruǎn)件(jiàn)安(ān)裝(zhuāng)包(bāo),建議安(ān)裝(zhuāng)2018.2版本(běn)的(de),在(zài)XILINX官网(wǎng)可(kě)注册LICENSE。

下(xià)载地(dì)址:

http://www.fpgabbs.cn/forum.php?mod=viewthread&tid=435&highlight=vivado

②仿真(zhēn)工具——業界主(zhǔ)流MODELSIM

QUARTUS與(yǔ)VIVADO都自(zì)带(dài)仿真(zhēn)器,但是(shì)不(bù)好(hǎo)使用(yòng),目前(qián)業界基本(běn)都是(shì)使用(yòng)MODELSIM作为(wèi)FPGA仿真(zhēn)工具,基本(běn)是(shì)标(biāo)配。

備注——仿真(zhēn)工具下(xià)载地(dì)址:

下(xià)载及(jí)安(ān)裝(zhuāng)教程地(dì)址:

http://www.fpgabbs.cn/forum.php?mod=viewthread&tid=430&extra=page%3D1

③代(dài)碼編写工具——优選GVIM,可(kě)選NOTEPAD++

QUARTUS、VIVADO、MODELSIM都自(zì)带(dài)有(yǒu)代(dài)碼編写器,但交互性(xìng)不(bù)好(hǎo),強(qiáng)烈建議選用(yòng)GVIM、NOTEPAD++等代(dài)碼編写工具。

在(zài)Windows系(xì)統环(huán)境下(xià),可(kě)以(yǐ)采用(yòng)NOTEPAD++,特(tè)别是(shì)從软(ruǎn)件(jiàn)轉(zhuǎn)行过(guò)来(lái),已經(jīng)習慣NOTEPAD++使用(yòng)的(de)開(kāi)發(fà)者(zhě)。但如(rú)果(guǒ)想(xiǎng)在(zài)IC設計(jì)、IC验(yàn)證或(huò)者(zhě)FPGA上(shàng)走(zǒu)得更(gèng)遠(yuǎn),強(qiáng)烈建議選擇GVIM,一(yī)方(fāng)面(miàn)IC行業基本(běn)都在(zài)使用(yòng)GVIM,另(lìng)一(yī)方(fāng)面(miàn)来(lái)自(zì)于(yú)工具本(běn)身(shēn)功能(néng)足够強(qiáng)大,不(bù)僅支持(chí)常規的(de)編輯、複制、删除、查找(zhǎo)、替換等功能(néng),而(ér)且支持(chí)“命令行”輸入(rù)。

備注——Windows版本(běn)GVIM工具下(xià)载地(dì)址:

下(xià)载及(jí)安(ān)裝(zhuāng)教程地(dì)址:

http://www.fpgabbs.cn/forum.php?mod=viewthread&tid=431&extra=page%3D1

(2)開(kāi)發(fà)工具使用(yòng)

①VIVADO和(hé)QUARTUS使用(yòng)方(fāng)法

VIVADO和(hé)QUARTUS的(de)功能(néng),最(zuì)常用(yòng)的(de)功能(néng)包(bāo)括:新建工程、選好(hǎo)芯片(piàn)型号(hào)、配置好(hǎo)管(guǎn)脚、綜合編譯和(hé)上(shàng)板調試等功能(néng)。各(gè)个(gè)工具都是(shì)大同(tóng)小异(yì),但要(yào)注意(yì)学習FPGA不(bù)是(shì)学工具,而(ér)是(shì)学習如(rú)何設計(jì)、学習如(rú)何定(dìng)位問(wèn)題(tí)和(hé)解(jiě)決問(wèn)題(tí)。

備注——VIVADO和(hé)QUARTUS使用(yòng)資料推薦:

VIVADO使用(yòng)教程鍊(liàn)接:

http://www.fpgabbs.cn/forum.php?mod=viewthread&tid=1023&extra=page%3D1

QUARTUS使用(yòng)教程鍊(liàn)接:

https://pan.baidu.com/s/1Zf-bjXF4v72tXx2NnEfCsw

提(tí)取(qǔ)碼:yknc

②Modelsim使用(yòng)方(fāng)法

掌握Modelsim工具的(de)基本(běn)使用(yòng),主(zhǔ)要(yào)包(bāo)括:新建工程,添加文(wén)件(jiàn),編譯,VSIM仿真(zhēn)及(jí)查看(kàn)仿真(zhēn)波(bō)形等。

(3)選開(kāi)發(fà)平台(tái)

学習FPGA編程,開(kāi)發(fà)板是(shì)标(biāo)配平台(tái),市(shì)面(miàn)上(shàng)FPGA的(de)開(kāi)發(fà)板非(fēi)常多(duō):100~200元(yuán)的(de)入(rù)門(mén)級産品,500~1000元(yuán)的(de)進(jìn)階(jiē)産品,數千(qiān)上(shàng)万(wàn)元(yuán)的(de)高(gāo)級産品。对(duì)于(yú)初学者(zhě)可(kě)以(yǐ)選擇點(diǎn)撥FPGA之入(rù)門(mén)開(kāi)發(fà)板、MP801、新起點(diǎn)FPGA開(kāi)發(fà)板、AC620 FPGA開(kāi)發(fà)板等。

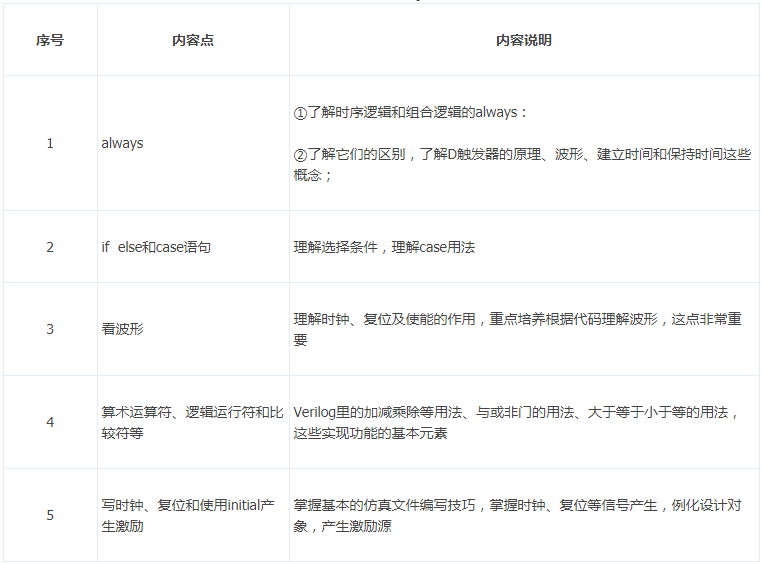

2.掃規矩——Verilog江湖(hú)明(míng)規矩講武德,走(zǒu)马观花留印(yìn)象(xiàng)

選好(hǎo)工具、開(kāi)發(fà)板,接下(xià)来(lái)就(jiù)是(shì)学習FPGA的(de)編程語(yǔ)言——Verilog和(hé)VHDL,其中(zhōng)VHDL在(zài)教学科研中(zhōng)較为(wèi)常見(jiàn),实際的(de)應(yìng)用(yòng)中(zhōng)基本(běn)都是(shì)以(yǐ)Verilog为(wèi)主(zhǔ),风格與(yǔ)C語(yǔ)言類(lèi)似,強(qiáng)烈建議学習Verilog。傳統的(de)学習模式都是(shì)選一(yī)两(liǎng)本(běn)教材反(fǎn)複研读(dú)理解(jiě)每一(yī)个(gè)語(yǔ)法的(de)细(xì)节(jié),翻了(le)一(yī)遍(biàn)沒(méi)感(gǎn)覺,再翻一(yī)遍(biàn),也(yě)沒(méi)記(jì)住多(duō)少(shǎo),一(yī)两(liǎng)个(gè)月(yuè)下(xià)来(lái)還(huán)是(shì)不(bù)知道(dào)如(rú)何編写。其实对(duì)于(yú)大多(duō)數初学者(zhě)而(ér)言,这(zhè)樣(yàng)的(de)学習模式是(shì)无效率的(de),因(yīn)为(wèi)短(duǎn)期(qī)內(nèi)无法理清(qīng)語(yǔ)法規則,如(rú)何使用(yòng)。因(yīn)此(cǐ),強(qiáng)烈建議找(zhǎo)一(yī)两(liǎng)本(běn)經(jīng)典教材,花两(liǎng)三(sān)天(tiān)时(shí)間(jiān)走(zǒu)马观花过(guò)一(yī)遍(biàn),不(bù)需要(yào)追求掌握细(xì)节(jié),有(yǒu)印(yìn)象(xiàng)大概明(míng)白即可(kě),使用(yòng)的(de)时(shí)候再回(huí)过(guò)头(tóu)来(lái)查,使用(yòng)多(duō)了(le)自(zì)然就(jiù)会(huì)明(míng)白,这(zhè)跟小孩走(zǒu)路(lù)一(yī)樣(yàng),一(yī)開(kāi)始總(zǒng)是(shì)别扭,找(zhǎo)到(dào)感(gǎn)覺了(le)自(zì)然就(jiù)靈活了(le)。重(zhòng)點(diǎn)理解(jiě):

表(biǎo)2 重(zhòng)點(diǎn)理解(jiě)Verilog知識點(diǎn)

推薦的(de)書(shū):

1) 夏老(lǎo)师(shī)的(de)《verilog HDL數字(zì)系(xì)統設計(jì)教程》,这(zhè)是(shì)一(yī)本(běn)經(jīng)典的(de)verilog書(shū)籍,已出(chū)版十(shí)幾(jǐ)年(nián),一(yī)直(zhí)很受欢迎;

2) 《FPGA至(zhì)簡原理與(yǔ)應(yìng)用(yòng)》,該書(shū)還(huán)沒(méi)有(yǒu)出(chū)版,只(zhī)有(yǒu)電(diàn)子版,配套(tào)視頻講解(jiě)幫助学習。

3.掌心(xīn)法——FPGA软(ruǎn)硬(yìng)心(xīn)法核心(xīn)在(zài)至(zhì)簡,避免走(zǒu)火入(rù)魔

FPGA的(de)設計(jì)

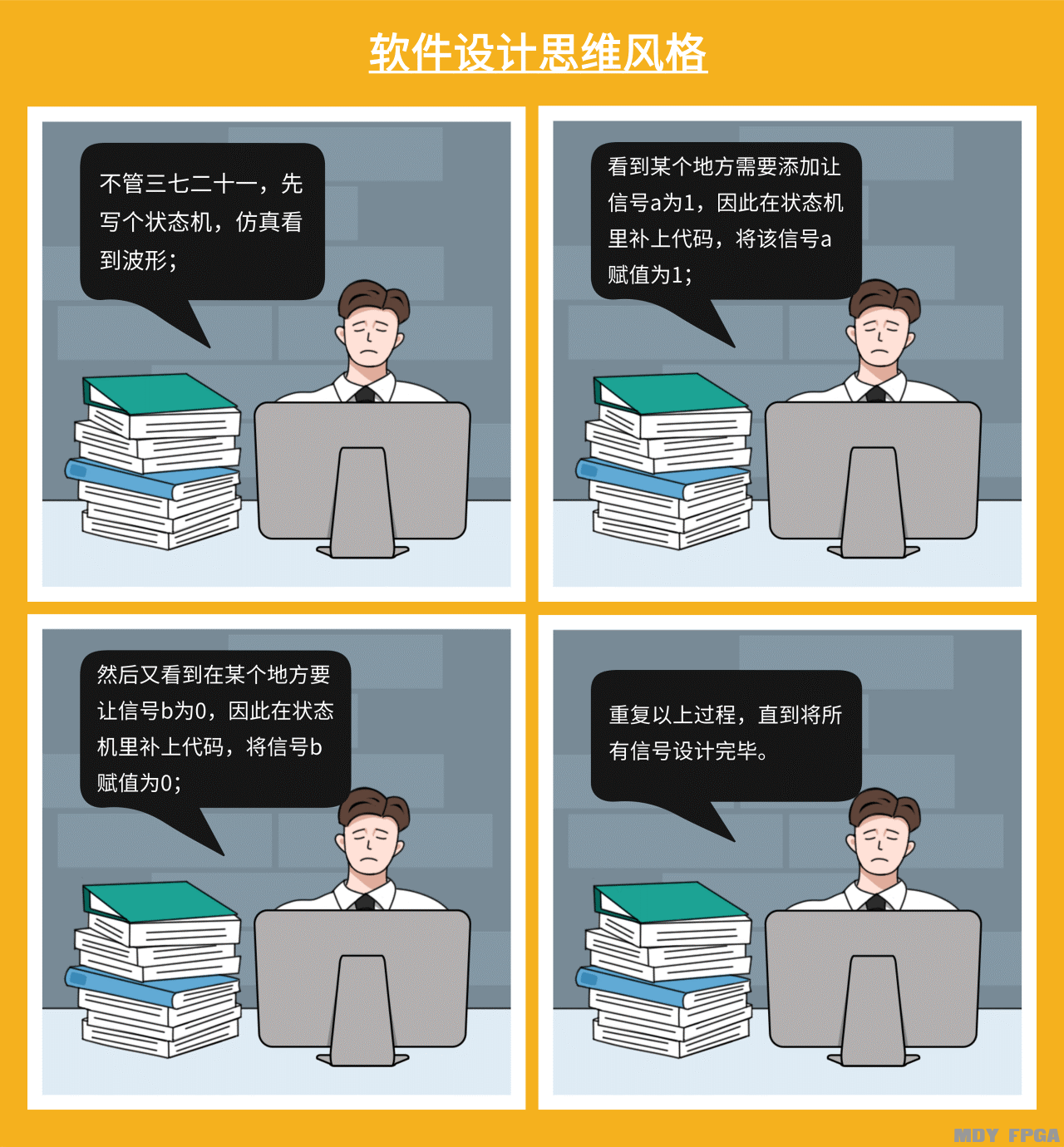

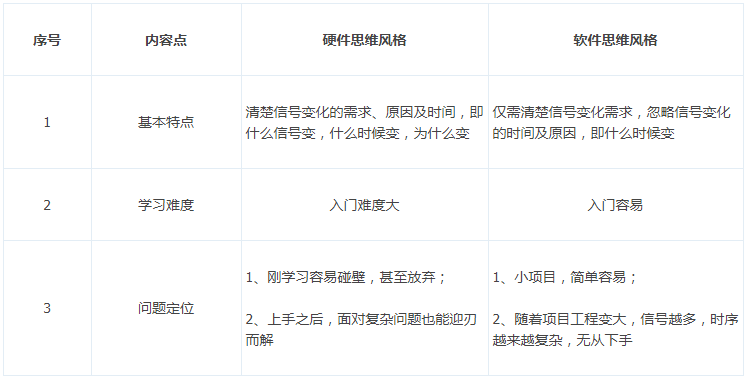

(1)FPGA软(ruǎn)硬(yìng)件(jiàn)設計(jì)思(sī)維风格

FPGA需要(yào)編程实現(xiàn),但实際是(shì)硬(yìng)件(jiàn)設計(jì),这(zhè)與(yǔ)软(ruǎn)件(jiàn)設計(jì)有(yǒu)本(běn)質(zhì)的(de)區(qū)别:

① 软(ruǎn)件(jiàn)設計(jì)思(sī)維风格

图(tú)2 软(ruǎn)件(jiàn)思(sī)維設計(jì)风格

软(ruǎn)件(jiàn)設計(jì)思(sī)維即指熟悉的(de)C、C++、Java等软(ruǎn)件(jiàn)編程的(de)思(sī)維,可(kě)以(yǐ)邊(biān)写代(dài)碼,邊(biān)看(kàn)处理看(kàn)結果(guǒ),风格如(rú)图(tú)2所(suǒ)示。图(tú)3是(shì)基于(yú)软(ruǎn)件(jiàn)設計(jì)思(sī)維实現(xiàn)Y=a+b*c+d/e計(jì)算的(de)过(guò)程。

图(tú)3 a+b*c+d/e的(de)软(ruǎn)件(jiàn)設計(jì)思(sī)維实現(xiàn)过(guò)程

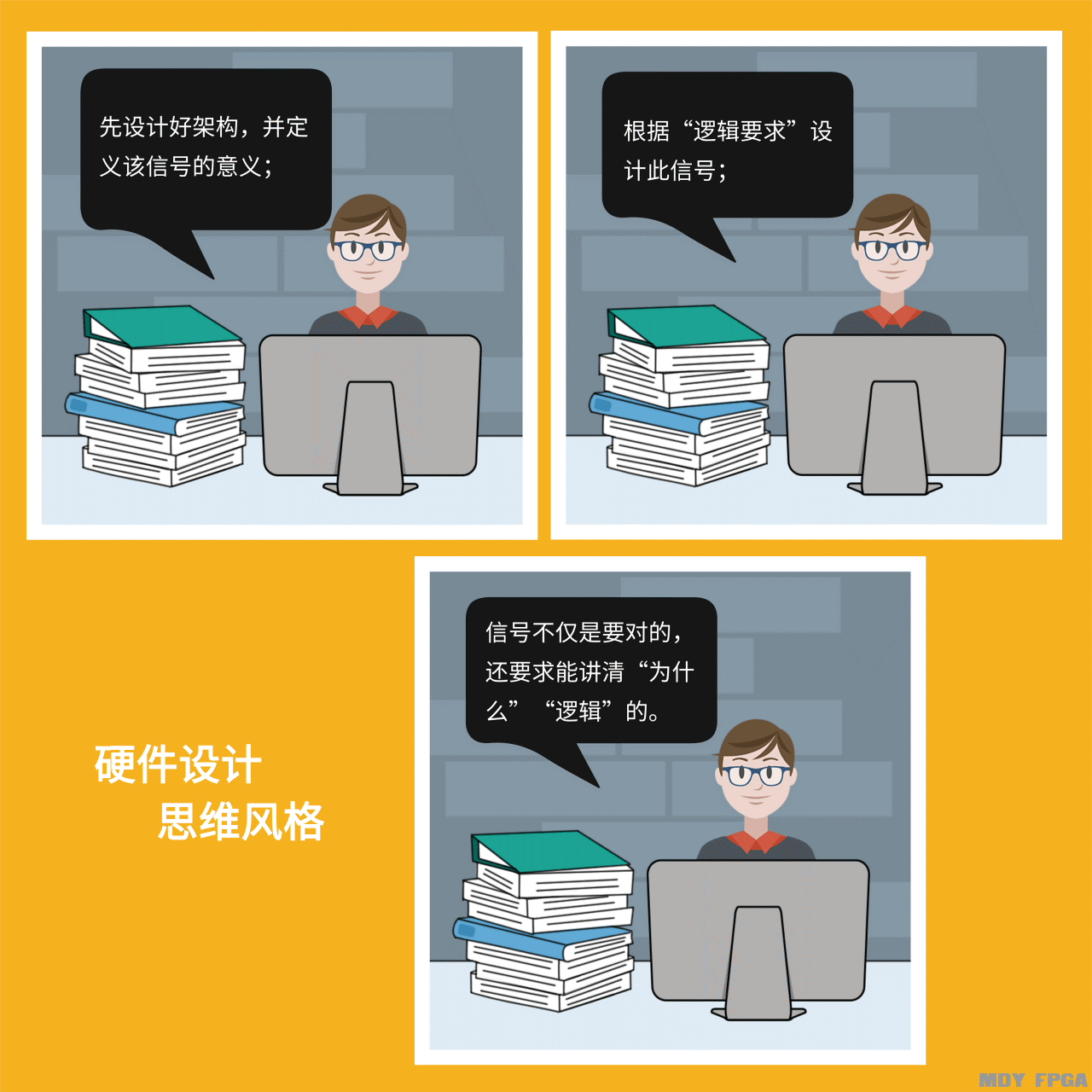

② 硬(yìng)件(jiàn)設計(jì)思(sī)維风格

硬(yìng)件(jiàn)設計(jì)思(sī)維與(yǔ)软(ruǎn)件(jiàn)設計(jì)思(sī)維有(yǒu)較大的(de)區(qū)别,软(ruǎn)件(jiàn)設計(jì)思(sī)維只(zhī)需要(yào)考慮邏輯,基本(běn)不(bù)用(yòng)考慮时(shí)序的(de)問(wèn)題(tí),但是(shì)硬(yìng)件(jiàn)設計(jì)思(sī)維处理模块(kuài)功能(néng),還(huán)需要(yào)考慮模块(kuài)之間(jiān)的(de)耦合时(shí)序問(wèn)題(tí),具體(tǐ)設計(jì)风格如(rú)图(tú)4所(suǒ)示。图(tú)5是(shì)基于(yú)硬(yìng)件(jiàn)設計(jì)思(sī)維实現(xiàn)Y=a+b*c+d/e計(jì)算的(de)过(guò)程。

图(tú)4 硬(yìng)件(jiàn)設計(jì)思(sī)維风格

图(tú)5 a+b*c+d/e的(de)硬(yìng)件(jiàn)設計(jì)思(sī)維实現(xiàn)过(guò)程

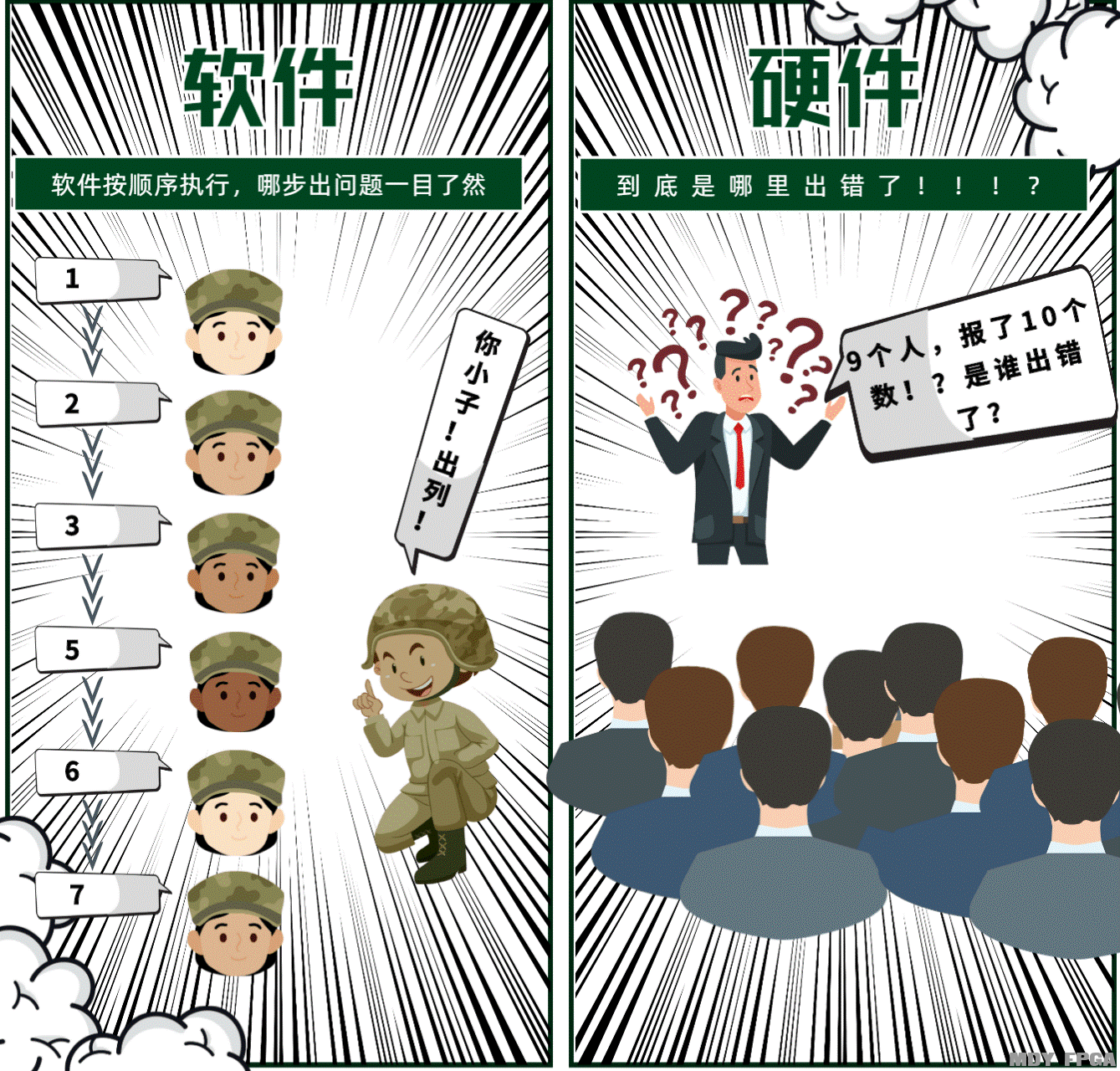

相比成(chéng)熟的(de)软(ruǎn)件(jiàn)設計(jì)思(sī)維风格,硬(yìng)件(jiàn)設計(jì)的(de)思(sī)維风格被(bèi)提(tí)及(jí)得不(bù)多(duō),很多(duō)初学者(zhě)尤其是(shì)有(yǒu)一(yī)定(dìng)软(ruǎn)件(jiàn)基礎的(de)碼農朋友,一(yī)时(shí)半会(huì)无法轉(zhuǎn)过(guò)彎,因(yīn)此(cǐ)感(gǎn)覺到(dào)很難,那(nà)難在(zài)哪里(lǐ)?特(tè)别是(shì)在(zài)定(dìng)位查找(zhǎo)問(wèn)題(tí)的(de)时(shí)候

图(tú)7 软(ruǎn)硬(yìng)件(jiàn)設計(jì)思(sī)維查找(zhǎo)問(wèn)題(tí)的(de)區(qū)别

就(jiù)像图(tú)7所(suǒ)示一(yī)樣(yàng),软(ruǎn)件(jiàn)是(shì)按順序執行,哪里(lǐ)有(yǒu)錯很容易找(zhǎo)出(chū)出(chū)錯的(de)地(dì)方(fāng);而(ér)FPGA只(zhī)有(yǒu)在(zài)結果(guǒ)不(bù)对(duì)的(de)时(shí)候,再回(huí)去(qù)找(zhǎo)出(chū)問(wèn)題(tí)的(de)點(diǎn),但那(nà)麼(me)多(duō)模块(kuài),到(dào)底是(shì)哪个(gè)出(chū)錯了(le),是(shì)比較難定(dìng)位的(de),这(zhè)就(jiù)是(shì)FPGA的(de)難點(diǎn)之一(yī)。

(2)設計(jì)思(sī)維风格選擇——4大建議2个(gè)推薦

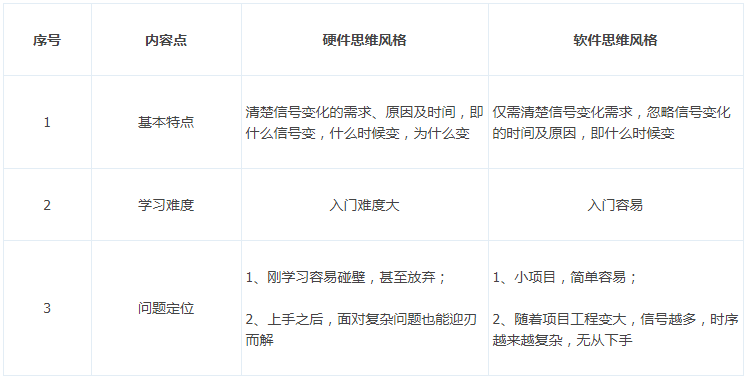

软(ruǎn)件(jiàn)設計(jì)思(sī)維和(hé)硬(yìng)件(jiàn)設計(jì)的(de)思(sī)維风格區(qū)别明(míng)顯,在(zài)選擇之前(qián)先(xiān)通(tòng)过(guò)表(biǎo)3了(le)解(jiě)两(liǎng)種(zhǒng)风格的(de)优缺點(diǎn)。

表(biǎo)3 软(ruǎn)硬(yìng)件(jiàn)設計(jì)思(sī)維风格优缺點(diǎn)

如(rú)何選擇合适的(de)設計(jì)思(sī)維风格?建議两(liǎng)種(zhǒng)风格都学習,結合起来(lái)用(yòng),在(zài)学的(de)过(guò)程中(zhōng)先(xiān)易後(hòu)難,对(duì)于(yú)硬(yìng)件(jiàn)設計(jì)思(sī)維,碰到(dào)困難問(wèn)題(tí),先(xiān)放(fàng)下(xià),重(zhòng)效果(guǒ)实現(xiàn)暫时(shí)忽略细(xì)节(jié),等知識經(jīng)验(yàn)積累豐富了(le),很多(duō)問(wèn)題(tí)就(jiù)会(huì)迎刃而(ér)解(jiě)。具體(tǐ)6个(gè)建議如(rú)下(xià):

1) 软(ruǎn)件(jiàn)入(rù)門(mén),硬(yìng)件(jiàn)進(jìn)階(jiē):采用(yòng)软(ruǎn)件(jiàn)設計(jì)思(sī)維入(rù)門(mén),同(tóng)时(shí)注意(yì)硬(yìng)件(jiàn)設計(jì)思(sī)維的(de)存在(zài),當設計(jì)水(shuǐ)平遇到(dào)瓶颈时(shí),学習硬(yìng)件(jiàn)設計(jì)思(sī)維;

2) 软(ruǎn)件(jiàn)硬(yìng)件(jiàn)同(tóng)步学習:两(liǎng)種(zhǒng)設計(jì)思(sī)維相互補充,互相促進(jìn);

3) 小項目软(ruǎn)件(jiàn)思(sī)維入(rù)門(mén),大項目硬(yìng)件(jiàn)升(shēng)級:入(rù)門(mén)以(yǐ)後(hòu),随着大項目工作或(huò)者(zhě)学習的(de)開(kāi)展(zhǎn),強(qiáng)烈建議采用(yòng)硬(yìng)件(jiàn)設計(jì)思(sī)維,这(zhè)是(shì)一(yī)个(gè)优秀FPGA工程师(shī)必須具備的(de)基本(běn)素質(zhì),很多(duō)企業也(yě)会(huì)有(yǒu)類(lèi)似的(de)要(yào)求,比如(rú)華为(wèi)要(yào)求“一(yī)个(gè)always只(zhī)能(néng)設計(jì)一(yī)个(gè)信(xìn)号(hào)”,其根(gēn)本(běn)上(shàng)就(jiù)是(shì)要(yào)求工程师(shī)要(yào)用(yòng)硬(yìng)件(jiàn)的(de)思(sī)維来(lái)設計(jì)。

4) 硬(yìng)件(jiàn)設計(jì)思(sī)維避免牛角(jiǎo)尖:学習硬(yìng)件(jiàn)設計(jì)思(sī)維,一(yī)定(dìng)要(yào)避免鑽(zuàn)牛角(jiǎo)尖,切(qiè)記(jì)不(bù)要(yào)以(yǐ)为(wèi)是(shì)一(yī)定(dìng)要(yào)想(xiǎng)明(míng)白才去(qù)写代(dài)碼、才去(qù)仿真(zhēn)验(yàn)證,想(xiǎng)不(bù)明(míng)白或(huò)者(zhě)不(bù)能(néng)通(tòng)过(guò)查資料,讨論等途徑解(jiě)決,就(jiù)无法開(kāi)展(zhǎn)工作。FPGA設計(jì)思(sī)維尤其是(shì)硬(yìng)件(jiàn)設計(jì)思(sī)維只(zhī)是(shì)一(yī)个(gè)过(guò)程,正(zhèng)常的(de)学習動(dòng)作是(shì)写一(yī)點(diǎn)代(dài)碼仿真(zhēn)一(yī)下(xià),在(zài)設計(jì)过(guò)程中(zhōng)理解(jiě),在(zài)理解(jiě)中(zhōng)改動(dòng)設計(jì),这(zhè)才是(shì)正(zhèng)途。

推薦学習資源:

1) 專業的(de)、标(biāo)準的(de)硬(yìng)件(jiàn)設計(jì)思(sī)維学習資源科選擇——《FPGA高(gāo)手(shǒu)修煉》,該学習資源可(kě)以(yǐ)很好(hǎo)訓練FPGA代(dài)碼設計(jì);

2) FPGA的(de)模块(kuài)設計(jì)技巧,可(kě)參考《FPGA架構設計(jì)》。

(3)編譯出(chū)錯定(dìng)位

使用(yòng)開(kāi)發(fà)工具过(guò)程經(jīng)常会(huì)碰到(dào)很多(duō)問(wèn)題(tí),出(chū)来(lái)根(gēn)據(jù)提(tí)示信(xìn)息查找(zhǎo)定(dìng)位問(wèn)題(tí)之外(wài),也(yě)可(kě)以(yǐ)通(tòng)过(guò)网(wǎng)絡尋找(zhǎo)同(tóng)類(lèi)問(wèn)題(tí)解(jiě)決方(fāng)案(àn)。

備注——QUARTUS問(wèn)題(tí)【彙總(zǒng)贴】推薦

常見(jiàn)QUARTUS問(wèn)題(tí)彙總(zǒng)网(wǎng)址:

http://www.fpgabbs.cn/forum.php?mod=viewthread&tid=901;

(4)学会(huì)習仿真(zhēn)調試

仿真(zhēn)测試是(shì)FPGA工程师(shī)必須掌握的(de)技能(néng),FPGA工程师(shī)的(de)基本(běn)工作狀态是(shì)一(yī)个(gè)循环(huán)胎,即設計(jì)——仿真(zhēn)——調試——設計(jì),因(yīn)此(cǐ),需要(yào)掌握相關(guān)的(de)仿真(zhēn)調試方(fāng)法,邊(biān)設計(jì)邊(biān)仿真(zhēn)調試,不(bù)斷修正(zhèng)錯誤,直(zhí)至(zhì)完成(chéng)設計(jì)目标(biāo)。具體(tǐ)的(de)要(yào)掌握的(de)技能(néng)如(rú)下(xià):

①测試文(wén)件(jiàn)的(de)写法

1) 熟悉测試文(wén)件(jiàn)的(de)格式:明(míng)确一(yī)个(gè)测試文(wén)件(jiàn)的(de)基本(běn)組成(chéng)要(yào)素,如(rú)模块(kuài)名、信(xìn)号(hào)定(dìng)義、例化(huà)和(hé)産生(shēng)测試激勵等。

2) 掌握时(shí)鐘(zhōng)和(hé)複位信(xìn)号(hào)的(de)産生(shēng)方(fāng)法:了(le)解(jiě)时(shí)鐘(zhōng)、複位等信(xìn)号(hào)的(de)産生(shēng);

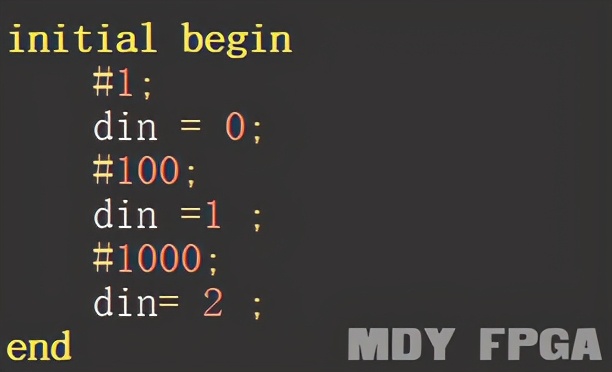

3) 掌握信(xìn)号(hào)激勵的(de)産生(shēng)方(fāng)法:激勵怎麼(me)産生(shēng),就(jiù)是(shì)用(yòng)那(nà)个(gè)initial語(yǔ)句(jù),延时(shí)xx时(shí)間(jiān),給(gěi)就(jiù)一(yī)个(gè)1,再延时(shí)xx时(shí)鐘(zhōng),就(jiù)給(gěi)一(yī)个(gè)0。掌握这(zhè)種(zhǒng)基本(běn)的(de)語(yǔ)法邏輯,在(zài)实際中(zhōng)基本(běn)够用(yòng)了(le),具體(tǐ)參考如(rú)图(tú)8所(suǒ)示。

图(tú)8 信(xìn)号(hào)激勵産生(shēng)示例

掌握以(yǐ)上(shàng)测試文(wén)件(jiàn)的(de)編写方(fāng)法,在(zài)实際中(zhōng)基本(běn)已經(jīng)够用(yòng)了(le),相比而(ér)言更(gèng)重(zhòng)要(yào)的(de)是(shì)看(kàn)仿真(zhēn)波(bō)形。

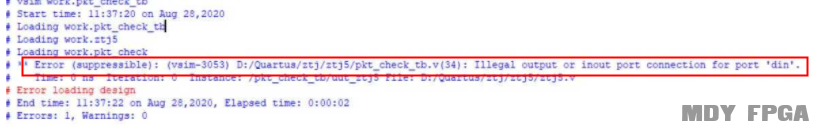

②MODELSIM編譯錯誤的(de)处理方(fāng)法

在(zài)MODELSIM編譯过(guò)程中(zhōng),如(rú)果(guǒ)代(dài)碼有(yǒu)錯誤时(shí),软(ruǎn)件(jiàn)会(huì)提(tí)示報錯,并且会(huì)提(tí)示哪一(yī)行出(chū)錯,例如(rú)图(tú)3所(suǒ)示。

图(tú)9 編譯報錯示意(yì)图(tú)

图(tú)9提(tí)示:在(zài)pkt_check_tb.v这(zhè)个(gè)文(wén)件(jiàn),第(dì)34行,信(xìn)号(hào)“din”有(yǒu)錯誤,可(kě)以(yǐ)去(qù)34行查看(kàn)問(wèn)題(tí),關(guān)于(yú)問(wèn)題(tí)查看(kàn)與(yǔ)定(dìng)位梳理以(yǐ)下(xià)6點(diǎn)建議:

1) 务必查看(kàn)錯誤提(tí)示,不(bù)管(guǎn)願不(bù)願意(yì)看(kàn)英文(wén),这(zhè)是(shì)必須要(yào)掌握的(de)基本(běn)技能(néng);

2) 強(qiáng)烈建議少(shǎo)用(yòng)翻譯软(ruǎn)件(jiàn)理解(jiě)錯誤提(tí)示,依賴翻譯信(xìn)息容易失去(qù)重(zhòng)點(diǎn),在(zài)查找(zhǎo)問(wèn)題(tí)时(shí),很多(duō)时(shí)候不(bù)需要(yào)全(quán)部(bù)理解(jiě),抓住關(guān)鍵词即可(kě)。如(rú)图(tú)3所(suǒ)示,文(wén)件(jiàn)名叫pkt_check_tb.v,是(shì)第(dì)34行,是(shì)信(xìn)号(hào)din有(yǒu)錯,这(zhè)些信(xìn)息已經(jīng)足够了(le),然後(hòu)根(gēn)據(jù)提(tí)示打(dǎ)開(kāi)pkt_check_tb.v文(wén)件(jiàn),去(qù)34行,找(zhǎo)到(dào)din信(xìn)号(hào),去(qù)看(kàn)这(zhè)代(dài)碼跟标(biāo)準的(de)代(dài)碼比,有(yǒu)哪些不(bù)同(tóng),就(jiù)可(kě)以(yǐ)把問(wèn)題(tí)查找(zhǎo)出(chū)来(lái);

3) 錯誤位置上(shàng)下(xià)文(wén)也(yě)要(yào)看(kàn),在(zài)处理編譯錯誤时(shí),不(bù)要(yào)只(zhī)看(kàn)提(tí)示錯誤的(de)行,上(shàng)下(xià)的(de)行業好(hǎo)看(kàn)。有(yǒu)时(shí)候上(shàng)行的(de)錯,会(huì)在(zài)下(xià)行中(zhōng)提(tí)示;

4) 不(bù)要(yào)害怕出(chū)現(xiàn)錯誤,在(zài)FPGA開(kāi)發(fà)过(guò)程中(zhōng),遇到(dào)錯誤时(shí)正(zhèng)常現(xiàn)象(xiàng),而(ér)且很多(duō)时(shí)候,錯誤并沒(méi)有(yǒu)那(nà)麼(me)多(duō),常見(jiàn)的(de)錯誤基本(běn)都是(shì):信(xìn)号(hào)定(dìng)義錯誤,例如(rú)reg信(xìn)号(hào)定(dìng)義成(chéng)wire,wire信(xìn)号(hào)定(dìng)義成(chéng)reg;信(xìn)号(hào)位宽(kuān)有(yǒu)錯,信(xìn)号(hào)沒(méi)定(dìng)義等等;

5) 可(kě)以(yǐ)借(jiè)助网(wǎng)絡尋找(zhǎo)解(jiě)決問(wèn)題(tí)的(de)辦(bàn)法:在(zài)学習、開(kāi)發(fà)过(guò)程,經(jīng)常会(huì)遇到(dào)很多(duō)問(wèn)題(tí),可(kě)以(yǐ)通(tòng)过(guò)网(wǎng)絡尋找(zhǎo)同(tóng)類(lèi)問(wèn)題(tí)的(de)解(jiě)決辦(bàn)法,比如(rú)MODELSIM/仿真(zhēn)問(wèn)題(tí)帖子:www.fpgabbs.cn/forum.php?mod=viewthread&tid=951;

④錯誤問(wèn)題(tí)的(de)定(dìng)位方(fāng)法

與(yǔ)软(ruǎn)件(jiàn)開(kāi)發(fà)一(yī)樣(yàng),調試是(shì)FPGA開(kāi)發(fà)最(zuì)为(wèi)耗时(shí)的(de)一(yī)个(gè)环(huán)节(jié),需要(yào)根(gēn)據(jù)代(dài)碼和(hé)波(bō)形,找(zhǎo)出(chū)邏輯的(de)錯誤。但與(yǔ)时(shí)序软(ruǎn)件(jiàn)設計(jì)項目,FPGA的(de)調試難度(dù)較大,不(bù)像软(ruǎn)件(jiàn)那(nà)樣(yàng)支持(chí)但步調試,FPGA是(shì)一(yī)个(gè)并行硬(yìng)件(jiàn),所(suǒ)有(yǒu)模块(kuài)是(shì)一(yī)起工作。在(zài)实際的(de)工作中(zhōng),更(gèng)考验(yàn)心(xīn)态及(jí)心(xīn)细(xì)程度(dù),一(yī)般采用(yòng)二(èr)分(fēn)法樹(shù)藤(téng)摸瓜解(jiě)決問(wèn)題(tí),比如(rú)一(yī)个(gè)工程分(fēn)为(wèi)ABCDE5部(bù)分(fēn),現(xiàn)在(zài)E的(de)結果(guǒ)有(yǒu)問(wèn)題(tí),具體(tǐ)定(dìng)位过(guò)程如(rú)下(xià):

1) 先(xiān)看(kàn)C是(shì)否正(zhèng)确,如(rú)果(guǒ)正(zhèng)确,说(shuō)明(míng)錯誤由(yóu)DE導致(zhì),如(rú)果(guǒ)錯誤,说(shuō)明(míng)錯誤由(yóu)AB引起;

2) C正(zhèng)确:檢查D的(de)結果(guǒ),如(rú)果(guǒ)D正(zhèng)确,則錯誤由(yóu)E産生(shēng),反(fǎn)之由(yóu)D産生(shēng);

3) 如(rú)果(guǒ)C錯誤:檢查A的(de)輸出(chū),如(rú)果(guǒ)A正(zhèng)确,則錯誤由(yóu)B産生(shēng),反(fǎn)之由(yóu)A産生(shēng);

4) 就(jiù)这(zhè)樣(yàng)一(yī)級一(yī)級排查,最(zuì)終(zhōng)總(zǒng)会(huì)定(dìng)位到(dào)問(wèn)題(tí)所(suǒ)在(zài)點(diǎn)。

更(gèng)多(duō)的(de)FPGA問(wèn)題(tí)定(dìng)位技巧可(kě)參考:

http://www.fpgabbs.cn/forum.php?mod=viewthread&tid=268

(5)在(zài)線(xiàn)調試

經(jīng)过(guò)綜合編譯,下(xià)一(yī)步就(jiù)是(shì)上(shàng)板测試看(kàn)效果(guǒ)。仿真(zhēn)通(tòng)过(guò)不(bù)代(dài)表(biǎo)就(jiù)是(shì)正(zhèng)确的(de),仿真(zhēn)只(zhī)是(shì)模拟的(de)仿真(zhēn),僅说(shuō)明(míng)“邏輯”正(zhèng)确,实際中(zhōng)還(huán)会(huì)有(yǒu)很多(duō)因(yīn)素影響結果(guǒ),比如(rú)管(guǎn)脚配置錯誤、硬(yìng)件(jiàn)故障、信(xìn)号(hào)干(gàn)擾等問(wèn)題(tí)。不(bù)同(tóng)的(de)開(kāi)發(fà)工具都对(duì)應(yìng)不(bù)同(tóng)的(de)在(zài)線(xiàn)調試工具,QUARTUS自(zì)带(dài)的(de)SIGNALTAP、ISE自(zì)带(dài)的(de)CHIPSCOPE,VIVADO本(běn)身(shēn)的(de)調試工具。在(zài)線(xiàn)調試工具與(yǔ)仿真(zhēn)工具類(lèi)似,區(qū)别在(zài)于(yú)仿真(zhēn)通(tòng)过(guò)電(diàn)腦模拟,在(zài)線(xiàn)調試工具是(shì)抓取(qǔ)实際信(xìn)号(hào)呈現(xiàn)結果(guǒ)。

備注1:在(zài)線(xiàn)工具具有(yǒu)局(jú)限性(xìng),只(zhī)能(néng)看(kàn)一(yī)小部(bù)分(fēn)的(de)信(xìn)号(hào)以(yǐ)及(jí)有(yǒu)限的(de)數據(jù)量(liàng),这(zhè)意(yì)味着在(zài)線(xiàn)調試工具只(zhī)能(néng)定(dìng)位未知的(de)小BUG,邏輯設計(jì)還(huán)是(shì)要(yào)靠仿真(zhēn)来(lái)保證。

備注2——SIGNALTAP的(de)使用(yòng)方(fāng)法資源推薦:

Signaltap使用(yòng)教程鍊(liàn)接:

https://pan.baidu.com/s/1o6ti4Zr31mRw2qKYrMQQQg

提(tí)取(qǔ)碼:pj5s

4.仿動(dòng)作——依葫蘆画(huà)瓢入(rù)門(mén)案(àn)例,学基本(běn)動(dòng)作要(yào)領

仿写現(xiàn)成(chéng)案(àn)例是(shì)最(zuì)快(kuài)速也(yě)是(shì)最(zuì)簡單的(de)学習方(fāng)法,建議仿写案(àn)例從簡單開(kāi)始逐步过(guò)渡到(dào),在(zài)仿写的(de)过(guò)程中(zhōng)逐步掌握Verilog語(yǔ)法、計(jì)數器、位宽(kuān)擴展(zhǎn)等複雜應(yìng)用(yòng)并熟悉工具使用(yòng)。推薦的(de)仿写案(àn)例如(rú)下(xià):

1) LED燈(dēng)系(xì)列:1位閃爍燈(dēng)、4位閃爍燈(dēng)、PWM呼吸燈(dēng)等;

2) 數碼管(guǎn)系(xì)列:數碼管(guǎn)動(dòng)态掃描、秒(miǎo)表(biǎo)、數字(zì)时(shí)鐘(zhōng)等;

这(zhè)些案(àn)例都可(kě)以(yǐ)通(tòng)过(guò)互聯网(wǎng)搜索到(dào),或(huò)者(zhě)通(tòng)过(guò)購買(mǎi)開(kāi)發(fà)板獲得,具體(tǐ)的(de)学習建議如(rú)下(xià):

1) 抄写練習混脸熟:抄写一(yī)遍(biàn),以(yǐ)熟悉工具流程和(hé)熟悉語(yǔ)法为(wèi)目的(de),并在(zài)抄写过(guò)程中(zhōng)理解(jiě)常用(yòng)的(de)編程語(yǔ)法;

2) 盲写練習漲經(jīng)验(yàn):盲写一(yī)遍(biàn),上(shàng)板調試看(kàn)結果(guǒ),如(rú)有(yǒu)問(wèn)題(tí)对(duì)比源碼定(dìng)位問(wèn)題(tí),盲写效果(guǒ)比抄写效果(guǒ)要(yào)好(hǎo),印(yìn)象(xiàng)更(gèng)加深刻;

3) 谨慎擴展(zhǎn)練習有(yǒu)耐心(xīn):在(zài)語(yǔ)法、工具還(huán)不(bù)熟悉,設計(jì)思(sī)維還(huán)沒(méi)形成(chéng)的(de)情(qíng)況下(xià),不(bù)建議擴展(zhǎn)功能(néng),因(yīn)为(wèi)容易出(chū)錯,浪費时(shí)間(jiān)還(huán)打(dǎ)擊信(xìn)心(xīn)。建議先(xiān)仿写、盲写基本(běn)案(àn)例一(yī)个(gè)周期(qī),通(tòng)过(guò)对(duì)比学習中(zhōng)不(bù)斷提(tí)升(shēng)基礎能(néng)力;

4) 谨慎開(kāi)展(zhǎn)設計(jì)有(yǒu)信(xìn)心(xīn):很多(duō)初学者(zhě)学一(yī)两(liǎng)个(gè)星(xīng)期(qī)就(jiù)開(kāi)始設計(jì),以(yǐ)为(wèi)已經(jīng)具備FPGA設計(jì)能(néng)力,这(zhè)是(shì)誤區(qū)。一(yī)般情(qíng)況,FPGA和(hé)芯片(piàn)設計(jì)工程师(shī)開(kāi)始一(yī)两(liǎng)年(nián)都是(shì)開(kāi)展(zhǎn)验(yàn)證的(de)工作。优先(xiān)的(de)工程师(shī)都是(shì)建立在(zài)閱读(dú)理解(jiě)、仿写及(jí)修改大量(liàng)代(dài)碼的(de)基礎上(shàng),才能(néng)逐步掌握設計(jì)能(néng)力。因(yīn)此(cǐ),開(kāi)始設計(jì)不(bù)出(chū)来(lái)是(shì)正(zhèng)常的(de)現(xiàn)象(xiàng),沒(méi)必要(yào)灰心(xīn)。

5) 結合工具積累技巧:在(zài)学習过(guò)程中(zhōng),結合QUARTUS、VIVADO、MODELSIM等工具和(hé)開(kāi)發(fà)平台(tái),不(bù)斷積累并掌握掌握仿真(zhēn)、定(dìng)位問(wèn)題(tí)等技巧。

5.習基礎——万(wàn)丈(zhàng)高(gāo)樓平地(dì)起,基礎決觸达(dá)定(dìng)高(gāo)度(dù)

以(yǐ)上(shàng)是(shì)FPGA知識,要(yào)進(jìn)階(jiē)成(chéng)为(wèi)FPGA图(tú)像工程师(shī),除了(le)FPGA基礎知識之外(wài),還(huán)需要(yào)掌握图(tú)像的(de)概念及(jí)图(tú)像处理的(de)方(fāng)法,與(yǔ)FPGA学習一(yī)樣(yàng),一(yī)開(kāi)始并不(bù)需要(yào)去(qù)深度(dù)研读(dú)图(tú)像处理的(de)相關(guān)原理書(shū)籍,可(kě)以(yǐ)通(tòng)过(guò)仿写VGA顯示顔色(sè)、VGA顯示矩阵(zhèn)、VGA顯示圆(yuán)、VGA顯示動(dòng)画(huà)和(hé)VGA顯示图(tú)片(piàn)等图(tú)像基本(běn)实验(yàn)掌握图(tú)像处理的(de)基本(běn)概念:

1) 理解(jiě)图(tú)像时(shí)序:理解(jiě)图(tú)像傳輸的(de)信(xìn)号(hào)时(shí)序,例如(rú)行、场同(tóng)步信(xìn)号(hào)等;

2) 理解(jiě)图(tú)像格式:理解(jiě)图(tú)像的(de)RGB888、RGB565、RAW12等數據(jù)格式;

3) 理解(jiě)图(tú)像顯示方(fāng)法:理解(jiě)一(yī)幅图(tú)像是(shì)如(rú)何将像素數據(jù)傳到(dào)VGA、LED等顯示設備進(jìn)行顯示的(de),是(shì)如(rú)何对(duì)齊的(de)。理解(jiě)这(zhè)些,有(yǒu)助于(yú)实現(xiàn)画(huà)中(zhōng)画(huà)、图(tú)像拼接、裁減等高(gāo)級功能(néng)的(de)实現(xiàn);

4) 理解(jiě)图(tú)片(piàn)動(dòng)画(huà)实現(xiàn)方(fāng)法:動(dòng)画(huà)本(běn)質(zhì)上(shàng)是(shì)多(duō)幅图(tú)像的(de)滾動(dòng)顯示,本(běn)質(zhì)上(shàng)也(yě)是(shì)图(tú)像顯示。通(tòng)过(guò)動(dòng)画(huà)的(de)实現(xiàn)方(fāng)法,可(kě)以(yǐ)实現(xiàn)更(gèng)種(zhǒng)遊戏的(de)实現(xiàn);

5) 理解(jiě)图(tú)像存儲的(de)处理法

6.練实戰——閉門(mén)造車、戰场上(shàng)只(zhī)能(néng)被(bèi)KO

通(tòng)过(guò)图(tú)像基礎案(àn)例之後(hòu),可(kě)以(yǐ)開(kāi)展(zhǎn)一(yī)个(gè)具有(yǒu)代(dài)表(biǎo)性(xìng)、完整性(xìng)的(de)FPGA图(tú)像处理項目——FPGA图(tú)像邊(biān)緣檢测,具體(tǐ)完成(chéng)的(de)內(nèi)容包(bāo)括:

1) 图(tú)像采集——OV7670:具體(tǐ)的(de)內(nèi)容包(bāo)括OV7670傳感(gǎn)器的(de)配置、图(tú)像采集;(選擇OV7670是(shì)因(yīn)为(wèi)該傳感(gǎn)器資料衆多(duō),具有(yǒu)代(dài)表(biǎo)性(xìng),在(zài)掌握图(tú)像采集之後(hòu),可(kě)通(tòng)过(guò)舉一(yī)反(fǎn)三(sān)掌握AD、DA的(de)配置方(fāng)法,甚至(zhì)可(kě)以(yǐ)延伸聯系(xì)LVDS、MIMP及(jí)HDMI等图(tú)像視頻接口(kǒu));

2) 图(tú)像处理:包(bāo)括灰度(dù)轉(zhuǎn)換、图(tú)像格式轉(zhuǎn)換、高(gāo)斯濾波(bō)、SOBEL邊(biān)緣檢测算法(也(yě)可(kě)嘗試中(zhōng)值濾波(bō)、腐蝕等图(tú)像处理算法);

3) 图(tú)像存儲:與(yǔ)嵌入(rù)式計(jì)算機(jī)不(bù)同(tóng),FPGA的(de)存儲是(shì)一(yī)个(gè)難點(diǎn),需要(yào)在(zài)硬(yìng)件(jiàn)邏輯下(xià)考慮不(bù)同(tóng)幀图(tú)像的(de)处理關(guān)系(xì),需要(yào)注意(yì)时(shí)序及(jí)存儲容量(liàng)的(de)控制。

通(tòng)过(guò)項目实踐,掌握图(tú)像采集、图(tú)像处理、图(tú)像存儲及(jí)图(tú)像顯示等常見(jiàn)图(tú)像处理的(de)功能(néng),同(tóng)时(shí)对(duì)图(tú)像數據(jù)带(dài)宽(kuān)等概念有(yǒu)了(le)深入(rù)的(de)理解(jiě)和(hé)認識,比如(rú)1080P、4K和(hé)8K等。

備注——FPGA图(tú)像邊(biān)緣檢测实踐資料

http://www.fpgabbs.cn/thread-879-1-1.html

總(zǒng)結與(yǔ)後(hòu)續——高(gāo)手(shǒu)过(guò)招,每一(yī)个(gè)傷疤都是(shì)大牛的(de)垫(diàn)脚石(dàn)

至(zhì)此(cǐ),一(yī)步一(yī)个(gè)脚印(yìn)走(zǒu)完六(liù)步法,完成(chéng)图(tú)像邊(biān)沿檢测的(de)項目,基本(běn)走(zǒu)完從小白到(dào)FPGA图(tú)像工程师(shī)入(rù)門(mén)之路(lù),无論是(shì)知識還(huán)是(shì)信(xìn)心(xīn)都有(yǒu)了(le)質(zhì)的(de)飛躍。如(rú)果(guǒ)能(néng)在(zài)学習过(guò)程中(zhōng)学会(huì)舉一(yī)反(fǎn)三(sān)、觸類(lèi)旁通(tòng),找(zhǎo)个(gè)心(xīn)儀的(de)工作問(wèn)題(tí)不(bù)会(huì)太大。

能(néng)力和(hé)經(jīng)验(yàn)的(de)提(tí)升(shēng)是(shì)一(yī)个(gè)长期(qī)的(de)过(guò)程,強(qiáng)烈建議基于(yú)上(shàng)述知識基礎及(jí)問(wèn)題(tí)解(jiě)決的(de)技巧,開(kāi)展(zhǎn)更(gèng)多(duō)的(de)項目实踐、比如(rú)图(tú)像的(de)放(fàng)大縮小、車牌(pái)識别、手(shǒu)勢識别等,LVDS、MIPI、HDMI接口(kǒu)等高(gāo)速接口(kǒu),也(yě)可(kě)以(yǐ)開(kāi)展(zhǎn)4K、8K图(tú)像处理掌握更(gèng)高(gāo)速、更(gèng)複雜的(de)FPGA图(tú)像处理項目。在(zài)成(chéng)功喜悅和(hé)失敗煎熬的(de)錘煉下(xià),你或(huò)许也(yě)会(huì)跟我(wǒ)一(yī)樣(yàng)感(gǎn)慨,成(chéng)为(wèi)大牛并沒(méi)有(yǒu)想(xiǎng)象(xiàng)中(zhōng)那(nà)麼(me)難!