第(dì)一(yī)部(bù)分(fēn)已經(jīng)公布(bù),具體(tǐ)查看(kàn)FPGA面(miàn)試題(tí)《一(yī)》文(wén)章(zhāng)

14. flip-flop和(hé)latch的(de)區(qū)别,rtl中(zhōng)latch是(shì)如(rú)何産生(shēng)的(de) [SIRF 2008]

【解(jiě)答(dá)視頻序号(hào):09120001】

15. 多(duō)时(shí)鐘(zhōng)域設計(jì)中(zhōng),如(rú)何处理跨时(shí)鐘(zhōng)域信(xìn)号(hào)? [SIRF 2008]

【解(jiě)答(dá)視頻序号(hào):09120002】

16. 鎖存器比寄存器省(shěng)面(miàn)積,但为(wèi)什麼(me)在(zài)IC設計(jì)中(zhōng)通(tòng)常使用(yòng)寄存器? [SIRF 2008]

【解(jiě)答(dá)視頻序号(hào):09120003】

17. 用(yòng)verilog/vhdl写一(yī)个(gè)fifo控制器(包(bāo)括空,滿,半滿信(xìn)号(hào))。(飛利浦-大唐笔(bǐ)試)

reg[N-1:0] memory[0:M-1]; 定(dìng)義FIFO为(wèi)N位字(zì)长容量(liàng)M

【解(jiě)答(dá)視頻序号(hào):09250001】

18. FPGA 的(de)片(piàn)上(shàng)RAM 資源,可(kě)以(yǐ)在(zài)設計(jì)中(zhōng)如(rú)下(xià)哪些應(yìng)用(yòng)?

a、Shift Register b、ROM

c、RAM d、FIFO

【解(jiě)答(dá)視頻序号(hào):09250002】

19. 下(xià)列哪些屬于(yú)时(shí)鐘(zhōng)約束(shù)?

a、set_false_path b、set_input_path

c、set_max_delay d、set_multicycle path

【解(jiě)答(dá)視頻序号(hào):09250002】

20. FPGA可(kě)以(yǐ)有(yǒu)哪些工藝?

a、SDRAM b、SRAM c、EEPOM b、DDR e、FLASH

【解(jiě)答(dá)視頻序号(hào):09250002】

21. 下(xià)列哪些是(shì)FPGA片(piàn)內(nèi)資源?

a、RAM b、LUT c、DSP d、SDRAM

【解(jiě)答(dá)視頻序号(hào):09250002】

22. 下(xià)列哪些選項是(shì)FPGA設計(jì)中(zhōng)必須的(de)設計(jì)約束(shù)?

a、管(guǎn)脚約束(shù) b、跨时(shí)鐘(zhōng)域約束(shù)

c、时(shí)鐘(zhōng)周期(qī)約束(shù) d、片(piàn)上(shàng)RAM位置約束(shù)

【解(jiě)答(dá)視頻序号(hào):09250002】

23. 判斷:FPGA中(zhōng),需要(yào)一(yī)个(gè)1MByte的(de)存儲空間(jiān),用(yòng)片(piàn)上(shàng)RAM实現(xiàn)即可(kě)。

【解(jiě)答(dá)視頻序号(hào):09250002】

24. 判斷:Latch 和(hé)Register 的(de)結構是(shì)不(bù)同(tóng)的(de),Latch 是(shì)電(diàn)位控制器件(jiàn),Register是(shì)时(shí)序控制器件(jiàn)。

【解(jiě)答(dá)視頻序号(hào):09250002】

25. 判斷:FPGA設計(jì)中(zhōng),訪問(wèn)FLASH的(de)速度(dù)比DDR快(kuài)。

【解(jiě)答(dá)視頻序号(hào):09250002】

26. 闡述以(yǐ)下(xià)數字(zì)電(diàn)路(lù)中(zhōng)时(shí)鐘(zhōng)屬性(xìng):(1) Jitter :时(shí)鐘(zhōng)抖動(dòng) (2) clock_skew :时(shí)鐘(zhōng)偏移。

問(wèn)題(tí):这(zhè)两(liǎng)个(gè)不(bù)同(tóng)吗?

【解(jiě)答(dá)視頻序号(hào):09250002】

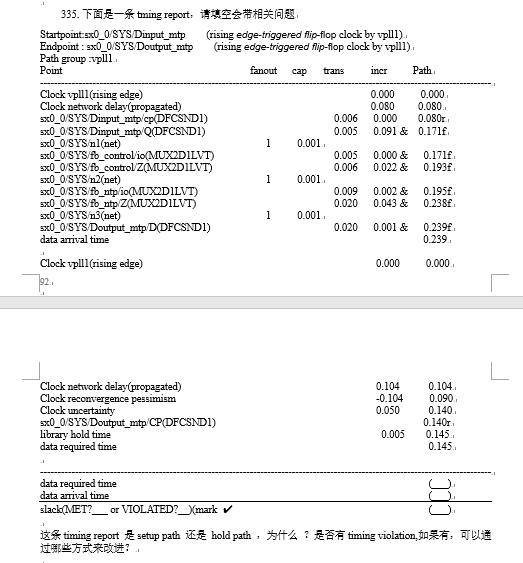

27. 分(fēn)析时(shí)序報告

【解(jiě)答(dá)視頻序号(hào):】未完待續。。。