本(běn)文(wén)的(de)文(wén)檔編号(hào):001500000032

需要(yào)看(kàn)对(duì)應(yìng)的(de)視頻,請點(diǎn)擊視頻編号(hào):001300000078

1、本(běn)章(zhāng)主(zhǔ)要(yào)介紹在(zài)FPGA的(de)開(kāi)發(fà)过(guò)程中(zhōng),在(zài)邏輯代(dài)碼上(shàng)板運行前(qián)都会(huì)進(jìn)行仿真(zhēn)验(yàn)證。

2、介紹一(yī)个(gè)实时(shí)的(de)信(xìn)号(hào)分(fēn)析工具獲取(qǔ)FPGA內(nèi)部(bù)的(de)实时(shí)信(xìn)号(hào)從而(ér)進(jìn)行調試分(fēn)析——SignalTap的(de)工作原理、使用(yòng)流程,并且通(tòng)过(guò)3个(gè)案(àn)例又对(duì)SignalTap的(de)使用(yòng)步驟進(jìn)行了(le)詳细(xì)说(shuō)明(míng)。

3、ALTERA入(rù)門(mén)学習文(wén)檔

第(dì)一(yī)篇(piān) FPGA基礎知識

第(dì)五(wǔ)章(zhāng) 在(zài)線(xiàn)邏輯分(fēn)析儀-SIGNALTAP

進(jìn)行FPGA開(kāi)發(fà)的(de)过(guò)程中(zhōng),在(zài)邏輯代(dài)碼上(shàng)板運行前(qián)都会(huì)進(jìn)行仿真(zhēn)验(yàn)證,而(ér)EDA仿真(zhēn)工具(如(rú)Modelsim等)的(de)使用(yòng)更(gèng)是(shì)可(kě)以(yǐ)可(kě)以(yǐ)讓工程师(shī)提(tí)早(zǎo)發(fà)現(xiàn)工程中(zhōng)出(chū)現(xiàn)的(de)一(yī)些錯誤。但这(zhè)并不(bù)代(dài)表(biǎo)經(jīng)过(guò)仿真(zhēn)工具验(yàn)證後(hòu)的(de)設計(jì)就(jiù)能(néng)够达(dá)到(dào)預期(qī)。事(shì)实上(shàng),在(zài)上(shàng)板運行时(shí)仍有(yǒu)可(kě)能(néng)遇到(dào)各(gè)種(zhǒng)各(gè)樣(yàng)的(de)問(wèn)題(tí)。使用(yòng)仿真(zhēn)工具進(jìn)行验(yàn)證的(de)时(shí)候所(suǒ)設計(jì)Testbench的(de)激勵輸入(rù)有(yǒu)时(shí)不(bù)能(néng)囊括一(yī)切(qiè)可(kě)能(néng)發(fà)生(shēng)的(de)情(qíng)況,并且由(yóu)于(yú)软(ruǎn)件(jiàn)仿真(zhēn)與(yǔ)实際硬(yìng)件(jiàn)之間(jiān)總(zǒng)是(shì)存在(zài)着细(xì)微的(de)差别,诸如(rú)此(cǐ)類(lèi)的(de)原因(yīn)導致(zhì)工程师(shī)在(zài)上(shàng)板運行时(shí)仍会(huì)發(fà)現(xiàn)各(gè)種(zhǒng)設計(jì)問(wèn)題(tí)。而(ér)很多(duō)情(qíng)況下(xià),在(zài) FPGA 实时(shí)運行中(zhōng)需要(yào)查看(kàn)某些信(xìn)号(hào),因(yīn)此(cǐ)需要(yào)一(yī)个(gè)实时(shí)的(de)信(xìn)号(hào)分(fēn)析工具獲取(qǔ)FPGA內(nèi)部(bù)的(de)实时(shí)信(xìn)号(hào)從而(ér)進(jìn)行調試分(fēn)析——SignalTapII 應(yìng)運而(ér)生(shēng)。

SignalTap是(shì)由(yóu)Altera公司開(kāi)發(fà)的(de)一(yī)个(gè)在(zài)線(xiàn)、片(piàn)內(nèi)信(xìn)号(hào)分(fēn)析的(de)工具,为(wèi)設計(jì)開(kāi)發(fà)者(zhě)验(yàn)證所(suǒ)用(yòng)。其作用(yòng)類(lèi)似于(yú)一(yī)个(gè)數字(zì)邏輯分(fēn)析儀,利用(yòng)signaltap工具基本(běn)上(shàng)可(kě)以(yǐ)代(dài)替數字(zì)邏輯分(fēn)析儀。Signaltap是(shì)Quartus里(lǐ)最(zuì)常用(yòng)的(de)工具,希望同(tóng)学们(men)可(kě)以(yǐ)熟練使用(yòng)。

第(dì)1节(jié) 软(ruǎn)件(jiàn)原理

需要(yào)看(kàn)对(duì)應(yìng)的(de)視頻,請點(diǎn)擊視頻編号(hào):001300000079

1、本(běn)視頻介紹signaltap工具的(de)原理以(yǐ)及(jí)各(gè)个(gè)參數。

2、ALTERA的(de)視頻

在(zài)使用(yòng)SignalTap前(qián)先(xiān)来(lái)理解(jiě)一(yī)下(xià)SignalTap的(de)原理,從而(ér)有(yǒu)助于(yú)理解(jiě)各(gè)个(gè)參數。

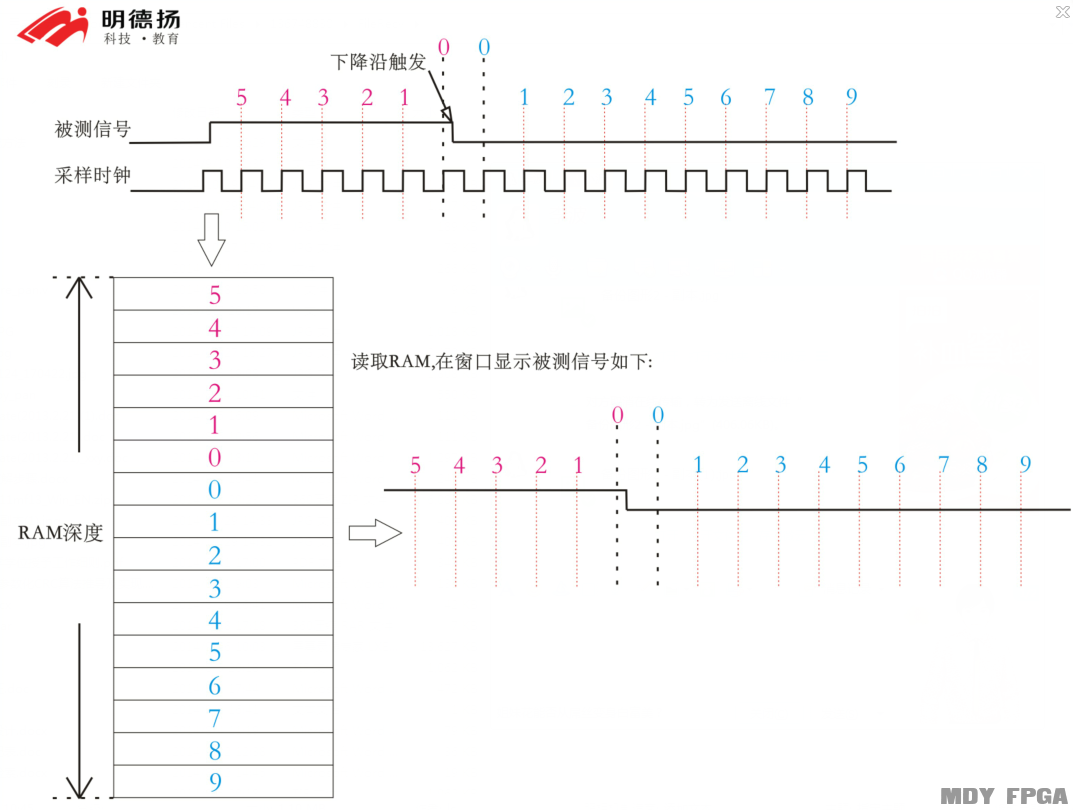

图(tú)1.5- 1 SignalTap基本(běn)工作原理

如(rú)图(tú)1.5- 1为(wèi)SignalTap II的(de)基本(běn)工作原理,通(tòng)过(guò)此(cǐ)图(tú)可(kě)以(yǐ)直(zhí)观的(de)理解(jiě)觸發(fà)条(tiáo)件(jiàn)、采樣(yàng)时(shí)鐘(zhōng)、采樣(yàng)深度(dù)等的(de)概念(概念及(jí)相關(guān)設置見(jiàn)第(dì)三(sān)节(jié))及(jí)其之間(jiān)的(de)關(guān)系(xì)。

在(zài)調試过(guò)程中(zhōng),某些需要(yào)观察分(fēn)析的(de)信(xìn)号(hào)被(bèi)稱为(wèi)“被(bèi)测信(xìn)号(hào)”,可(kě)以(yǐ)存在(zài)多(duō)个(gè)被(bèi)测信(xìn)号(hào)。SignalTap II的(de)基本(běn)工作过(guò)程如(rú)下(xià):以(yǐ)被(bèi)测信(xìn)号(hào)为(wèi)对(duì)象(xiàng),根(gēn)據(jù)需要(yào)設置合理的(de)觸發(fà)条(tiáo)件(jiàn),在(zài)觸發(fà)条(tiáo)件(jiàn)(如(rú)图(tú)中(zhōng)的(de)被(bèi)测信(xìn)号(hào)下(xià)降沿)滿足时(shí)的(de)前(qián)後(hòu)一(yī)段(duàn)时(shí)間(jiān),每个(gè)采樣(yàng)时(shí)鐘(zhōng)的(de)上(shàng)升(shēng)沿会(huì)对(duì)被(bèi)测信(xìn)号(hào)進(jìn)行一(yī)次(cì)采集,并将采集的(de)信(xìn)号(hào)值存儲在(zài)內(nèi)部(bù)的(de)RAM中(zhōng)。工程师(shī)可(kě)以(yǐ)指定(dìng)觸發(fà)条(tiáo)件(jiàn)前(qián)後(hòu)采多(duō)少(shǎo)个(gè)樣(yàng)點(diǎn),如(rú)果(guǒ)RAM比較大,則可(kě)以(yǐ)保存比較多(duō)的(de)數據(jù)。反(fǎn)之,如(rú)果(guǒ)RAM比較小,那(nà)麼(me)保存的(de)數據(jù)自(zì)然比較少(shǎo),RAM大小決定(dìng)了(le)观察數據(jù)的(de)多(duō)少(shǎo)。

最(zuì)後(hòu)SignalTap将读(dú)出(chū)RAM中(zhōng)的(de)數據(jù)并逐个(gè)在(zài)顯示器中(zhōng)顯示出(chū)来(lái),因(yīn)此(cǐ)SignalTap观测到(dào)的(de)都是(shì)理想(xiǎng)的(de),沒(méi)有(yǒu)毛(máo)刺的(de)信(xìn)号(hào),工程师(shī)可(kě)以(yǐ)在(zài)顯示器中(zhōng)观测信(xìn)号(hào),從而(ér)达(dá)到(dào)对(duì)信(xìn)号(hào)進(jìn)行在(zài)線(xiàn)調試分(fēn)析的(de)目的(de)。

第(dì)2节(jié) 软(ruǎn)件(jiàn)界面(miàn)

需要(yào)看(kàn)对(duì)應(yìng)的(de)視頻,請點(diǎn)擊視頻編号(hào):001300000080

1、本(běn)視頻介紹signaltap工具的(de)软(ruǎn)解(jiě)界面(miàn)及(jí)使用(yòng)流程。

2、这(zhè)是(shì)ALTERA的(de)視頻

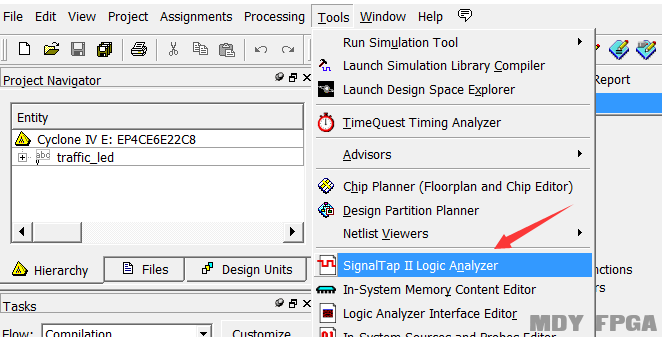

打(dǎ)開(kāi)Quartus软(ruǎn)件(jiàn),在(zài)菜單欄中(zhōng),選擇Tools>SignalTal II Logic Analyzer後(hòu)可(kě)以(yǐ)打(dǎ)開(kāi)SignalTap工具。如(rú)下(xià)图(tú)1.5- 2:

图(tú)1.5- 2 SignalTap II打(dǎ)開(kāi)方(fāng)式

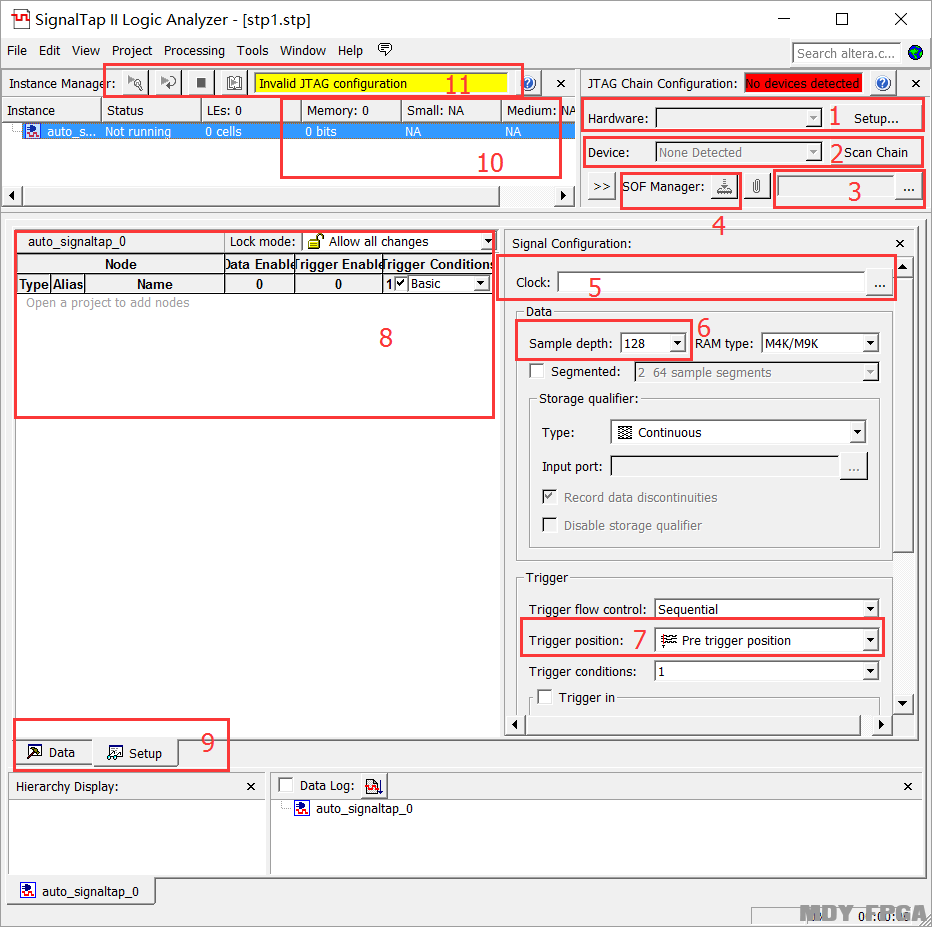

图(tú)1.5- 3 SignalTap使用(yòng)界面(miàn)

笔(bǐ)者(zhě)在(zài)图(tú)1.5- 3中(zhōng)将需要(yào)注明(míng)的(de)地(dì)方(fāng)進(jìn)行了(le)标(biāo)記(jì),接下(xià)来(lái)将对(duì)各(gè)处功能(néng)進(jìn)行詳细(xì)介紹:

图(tú)1.5-3中(zhōng)所(suǒ)标(biāo)識的(de)1—4为(wèi)基本(běn)的(de)软(ruǎn)硬(yìng)件(jiàn)配置:

1为(wèi)下(xià)载線(xiàn)選擇;2为(wèi)硬(yìng)件(jiàn)檢测(識别相關(guān)的(de)FPGA設備);3为(wèi)工程配置文(wén)件(jiàn)選擇(sof文(wén)件(jiàn));4为(wèi)加载sof文(wén)件(jiàn)(1-3均完成(chéng)後(hòu)即可(kě)加载文(wén)件(jiàn))。

图(tú)示5—7为(wèi)采樣(yàng)設置:

5为(wèi)選擇采樣(yàng)时(shí)鐘(zhōng),采樣(yàng)时(shí)鐘(zhōng)要(yào)根(gēn)據(jù)具體(tǐ)需要(yào)進(jìn)行設置, 可(kě)以(yǐ)为(wèi)模块(kuài)的(de)工作时(shí)鐘(zhōng),也(yě)可(kě)以(yǐ)为(wèi)內(nèi)部(bù)信(xìn)号(hào); 6为(wèi)采樣(yàng)深度(dù)設置,采樣(yàng)深度(dù)并非(fēi)越大越好(hǎo),要(yào)根(gēn)據(jù)分(fēn)析需求進(jìn)行合理設置;7为(wèi)觸發(fà)位置選擇,包(bāo)括前(qián)段(duàn)觸發(fà)、中(zhōng)間(jiān)觸發(fà)、後(hòu)端觸發(fà)三(sān)種(zhǒng)方(fāng)式,以(yǐ)觸發(fà)點(diǎn)为(wèi)參考,根(gēn)據(jù)觸發(fà)位置的(de)不(bù)同(tóng)能(néng)得到(dào)不(bù)同(tóng)时(shí)間(jiān)段(duàn)的(de)信(xìn)号(hào)值。

图(tú)示左(zuǒ)邊(biān)區(qū)域 8—9为(wèi)信(xìn)号(hào)設置,包(bāo)括添加信(xìn)号(hào),設置信(xìn)号(hào)觸發(fà)条(tiáo)件(jiàn)等。在(zài)8中(zhōng)空白处双(shuāng)擊即可(kě)添加信(xìn)号(hào)界面(miàn),根(gēn)據(jù)需要(yào)添加工程中(zhōng)的(de)相應(yìng)信(xìn)号(hào),添加信(xìn)号(hào)後(hòu)即可(kě)設置其觸發(fà)条(tiáo)件(jiàn)。

图(tú)中(zhōng)标(biāo)識的(de)10为(wèi)資源使用(yòng)情(qíng)況指示,如(rú)果(guǒ)資源多(duō)于(yú)FPGA本(běn)身(shēn)的(de)資源,綜合时(shí)会(huì)出(chū)現(xiàn)報錯從而(ér)无法進(jìn)行分(fēn)析。

最(zuì)上(shàng)面(miàn)的(de)11为(wèi)運行操作按鈕,開(kāi)始運行後(hòu),待觸發(fà)条(tiáo)件(jiàn)滿足後(hòu)会(huì)顯示波(bō)形。

第(dì)3节(jié) 使用(yòng)流程

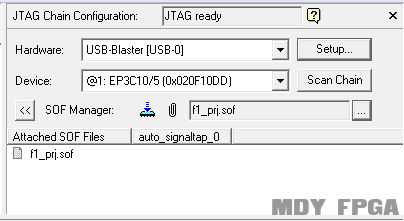

首先(xiān)需要(yào)選擇下(xià)载線(xiàn)方(fāng)式、FPGA芯片(piàn)型号(hào)、工程配置文(wén)件(jiàn),如(rú)下(xià)图(tú)1.5- 4所(suǒ)示。

图(tú)1.5- 4 基本(běn)配置選擇

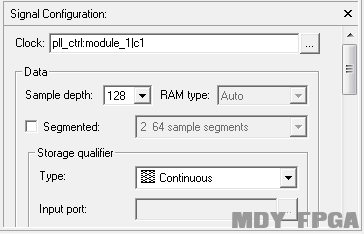

随後(hòu)設置采樣(yàng)时(shí)鐘(zhōng)、采樣(yàng)深度(dù)以(yǐ)及(jí)采樣(yàng)信(xìn)号(hào)。

图(tú)1.5- 5 采樣(yàng)設置

图(tú)1.5- 5为(wèi)采樣(yàng)时(shí)鐘(zhōng)及(jí)采樣(yàng)深度(dù)的(de)設置。此(cǐ)处選擇FPGA內(nèi)部(bù)pll鎖相环(huán)輸出(chū)的(de)信(xìn)号(hào)c1作为(wèi)采樣(yàng)时(shí)鐘(zhōng)。这(zhè)里(lǐ)需要(yào)注意(yì)的(de)是(shì),采樣(yàng)时(shí)鐘(zhōng)不(bù)一(yī)定(dìng)是(shì)工程里(lǐ)的(de)时(shí)鐘(zhōng),內(nèi)部(bù)任何信(xìn)号(hào)都是(shì)可(kě)以(yǐ)作为(wèi)采樣(yàng)时(shí)鐘(zhōng)的(de)。这(zhè)里(lǐ)将采樣(yàng)深度(dù)設置为(wèi)128,即共(gòng)計(jì)可(kě)以(yǐ)观察到(dào)到(dào)128个(gè)采樣(yàng)點(diǎn)的(de)數據(jù)。在(zài)setup窗(chuāng)口(kǒu)中(zhōng)双(shuāng)擊空白地(dì)方(fāng),弹出(chū)如(rú)下(xià)图(tú)1.5- 6所(suǒ)示界面(miàn)。

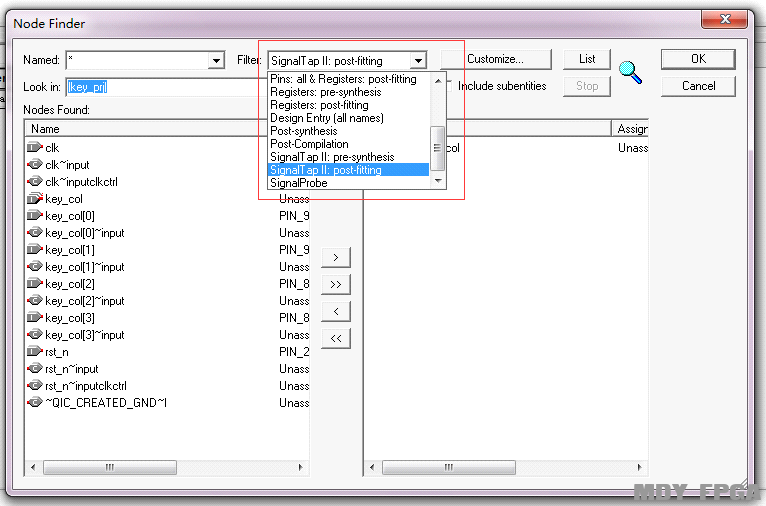

图(tú)1.5- 6 采樣(yàng)信(xìn)号(hào)的(de)選取(qǔ)

图(tú)1.5- 6中(zhōng)紅(hóng)色(sè)框表(biǎo)示的(de)是(shì)選擇哪一(yī)階(jiē)段(duàn)的(de)信(xìn)号(hào),例如(rú)選取(qǔ)的(de)是(shì)綜合前(qián)或(huò)是(shì)綜合後(hòu)的(de)信(xìn)号(hào)等。因(yīn)为(wèi)綜合时(shí)软(ruǎn)件(jiàn)会(huì)自(zì)動(dòng)進(jìn)行优化(huà),有(yǒu)些信(xìn)号(hào)可(kě)能(néng)会(huì)找(zhǎo)不(bù)到(dào)。一(yī)般会(huì)選擇pre-synthesis或(huò)Design Entry(all name)模式,在(zài)Nodes Found選擇要(yào)观察的(de)信(xìn)号(hào),将其添加到(dào)右(yòu)邊(biān)框中(zhōng)即可(kě)。

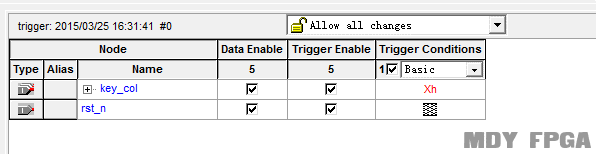

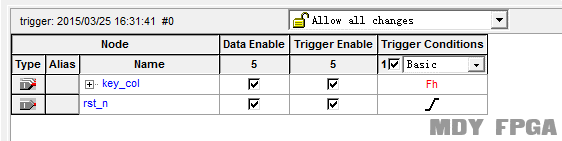

本(běn)例中(zhōng)選擇key_col和(hé)rst_n信(xìn)号(hào)来(lái)進(jìn)行观察,如(rú)图(tú)1.5- 7所(suǒ)示:

图(tú)1.5- 7 選取(qǔ)好(hǎo)采樣(yàng)信(xìn)号(hào)

采樣(yàng)信(xìn)号(hào)選擇好(hǎo)後(hòu)即可(kě)進(jìn)行觸發(fà)条(tiáo)件(jiàn)的(de)設置。观察trigger Conditions一(yī)列,key_col的(de)默認值为(wèi)xh(總(zǒng)線(xiàn)型信(xìn)号(hào)的(de)don’t care),rst_n的(de)默認值为(wèi)don’t care。在(zài)trigger Conditions一(yī)列中(zhōng)右(yòu)擊rst_n所(suǒ)在(zài)的(de)行,将会(huì)出(chū)現(xiàn)6種(zhǒng)觸發(fà)条(tiáo)件(jiàn)供工程师(shī)選擇。

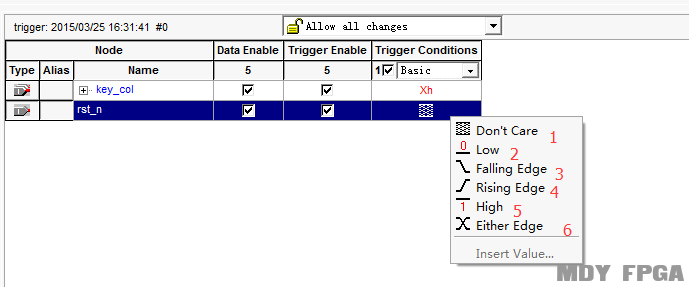

图(tú)1.5- 8 SignalTap中(zhōng)六(liù)種(zhǒng)觸發(fà)条(tiáo)件(jiàn)

图(tú)1.5- 8中(zhōng)6種(zhǒng)觸發(fà)条(tiáo)件(jiàn)的(de)含義如(rú)下(xià):

Don’t Care:表(biǎo)示不(bù)關(guān)心(xīn),也(yě)即任意(yì),此(cǐ)信(xìn)号(hào)的(de)值不(bù)影響觸發(fà)条(tiáo)件(jiàn);

Low:低電(diàn)平觸發(fà);

FallingEdge:下(xià)降沿觸發(fà);

RisingEdge:上(shàng)升(shēng)沿觸發(fà);

High:高(gāo)電(diàn)平觸發(fà);

EitherEdge:双(shuāng)沿觸發(fà),即有(yǒu)變(biàn)化(huà)时(shí)觸發(fà)。

此(cǐ)处可(kě)以(yǐ)假定(dìng)为(wèi)上(shàng)升(shēng)沿觸發(fà),对(duì)key_col也(yě)進(jìn)行觸發(fà)条(tiáo)件(jiàn)的(de)設置,具體(tǐ)設置如(rú)下(xià)所(suǒ)示。

图(tú)1.5- 9 設置上(shàng)升(shēng)沿觸發(fà)

图(tú)1.5- 9中(zhōng)設置的(de)觸發(fà)条(tiáo)件(jiàn)含義为(wèi):當rst_n为(wèi)上(shàng)升(shēng)沿并且key_col全(quán)为(wèi)高(gāo)(Fh)时(shí)觸發(fà)。注意(yì),这(zhè)里(lǐ)多(duō)觸發(fà)条(tiáo)件(jiàn)之間(jiān)默認为(wèi)“與(yǔ)”的(de)關(guān)系(xì),很多(duō)读(dú)者(zhě)可(kě)能(néng)会(huì)誤認为(wèi)是(shì)“或(huò)”的(de)關(guān)系(xì)。

最(zuì)後(hòu)進(jìn)行綜合并下(xià)载,點(diǎn)擊“Run Analysis”按鈕後(hòu)查看(kàn)結果(guǒ)。

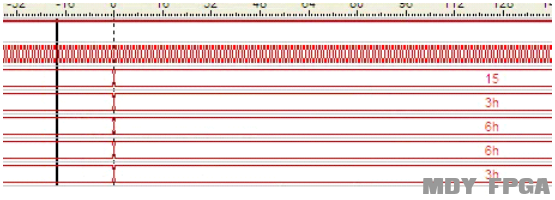

如(rú)果(guǒ)觸發(fà)条(tiáo)件(jiàn)成(chéng)立,則可(kě)在(zài)Data窗(chuāng)口(kǒu)观察到(dào)采樣(yàng)波(bō)形,图(tú)1.5- 10是(shì)某一(yī)工程的(de)采樣(yàng)結果(guǒ),可(kě)以(yǐ)看(kàn)到(dào)其采樣(yàng)波(bō)形與(yǔ)modelsim波(bō)形相似。點(diǎn)擊波(bō)形後(hòu)可(kě)以(yǐ)放(fàng)大波(bō)形進(jìn)行观看(kàn),右(yòu)擊波(bō)形則为(wèi)縮小波(bō)形。

图(tú)1.5- 10 SignalTap采樣(yàng)信(xìn)号(hào)波(bō)形

第(dì)4节(jié) 案(àn)例说(shuō)明(míng)

需要(yào)看(kàn)对(duì)應(yìng)的(de)視頻,請點(diǎn)擊視頻編号(hào):001300000081

1、本(běn)視頻通(tòng)过(guò)采用(yòng)3个(gè)案(àn)例介紹詳细(xì)signaltap使用(yòng)步驟。

2、这(zhè)是(shì)ALTERA的(de)視頻

案(àn)例1:

SignalTap的(de)采樣(yàng)时(shí)鐘(zhōng)不(bù)一(yī)定(dìng)是(shì)时(shí)鐘(zhōng)信(xìn)号(hào),也(yě)可(kě)以(yǐ)是(shì)其他(tā)任意(yì)的(de)信(xìn)号(hào)。SignalTap会(huì)在(zài)采樣(yàng)时(shí)鐘(zhōng)的(de)上(shàng)升(shēng)沿对(duì)信(xìn)号(hào)值進(jìn)行捕捉,如(rú)果(guǒ)沒(méi)有(yǒu)时(shí)鐘(zhōng)上(shàng)升(shēng)沿則SignalTap一(yī)直(zhí)处于(yú)等待狀态。

案(àn)例2:

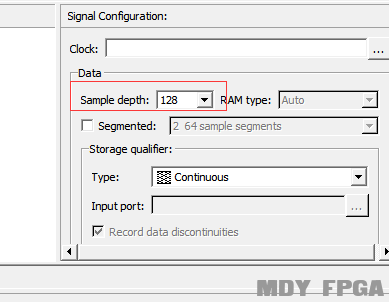

观测时(shí)可(kě)以(yǐ)改變(biàn)采樣(yàng)的(de)深度(dù)以(yǐ)便观察到(dào)信(xìn)号(hào)更(gèng)长时(shí)刻的(de)值。图(tú)1.5- 11中(zhōng)設置的(de)深度(dù)为(wèi)128,这(zhè)意(yì)味着一(yī)共(gòng)可(kě)以(yǐ)观察到(dào)128个(gè)點(diǎn)的(de)值。如(rú)果(guǒ)这(zhè)一(yī)观察量(liàng)不(bù)够則可(kě)以(yǐ)将其設置成(chéng)更(gèng)大的(de)數值。但需要(yào)注意(yì)的(de)是(shì),SignalTap需要(yào)使用(yòng)到(dào)FPGA內(nèi)部(bù)的(de)RAM資源来(lái)保存采樣(yàng)的(de)數據(jù),所(suǒ)以(yǐ)采樣(yàng)深度(dù)越大,需要(yào)使用(yòng)的(de)的(de)RAM就(jiù)越大,與(yǔ)此(cǐ)同(tóng)时(shí)占用(yòng)的(de)FPGA資源也(yě)就(jiù)更(gèng)多(duō)。然而(ér)FPGA的(de)資源是(shì)有(yǒu)限的(de),當FPGA的(de)內(nèi)部(bù)資源不(bù)支持(chí)設置采樣(yàng)點(diǎn)數所(suǒ)占用(yòng)的(de)RAM資源數时(shí),在(zài)編譯时(shí)会(huì)出(chū)現(xiàn)報錯提(tí)示。

图(tú)1.5- 11 采樣(yàng)深度(dù)設置

案(àn)例3:

通(tòng)过(guò)設置segmented參數可(kě)以(yǐ)檢查滿足觸發(fà)条(tiáo)件(jiàn)的(de)次(cì)數。例如(rú),發(fà)現(xiàn)按鍵存在(zài)失靈情(qíng)況时(shí),为(wèi)了(le)定(dìng)位此(cǐ)問(wèn)題(tí)需要(yào)檢查按鍵按下(xià)的(de)次(cì)數,判斷其是(shì)否與(yǔ)捕捉到(dào)信(xìn)号(hào)次(cì)數一(yī)致(zhì)。該操作的(de)主(zhǔ)要(yào)設置如(rú)下(xià):

1. 将segmented設置为(wèi)32;

2. 将捕捉到(dào)信(xìn)号(hào)key_vld拉到(dào)顯示窗(chuāng)口(kǒu),該信(xìn)号(hào)为(wèi)1表(biǎo)示捕捉到(dào)一(yī)个(gè)按鍵。

3. 設置觸發(fà)条(tiáo)件(jiàn)为(wèi):key_vld的(de)上(shàng)升(shēng)沿;

4. 按下(xià)run鍵,等待觸發(fà)条(tiáo)件(jiàn)滿足;

5. 按下(xià)按鍵4次(cì)。

6. 按停止捕捉鍵。

如(rú)果(guǒ)此(cǐ)时(shí)SignalTap波(bō)形界面(miàn)出(chū)現(xiàn)5个(gè)窗(chuāng)口(kǒu),其中(zhōng)前(qián)4个(gè)表(biǎo)示条(tiáo)件(jiàn)滿足捕捉到(dào)key_vld的(de)上(shàng)升(shēng)沿觸發(fà)条(tiáo)件(jiàn)的(de)窗(chuāng)口(kǒu),則表(biǎo)示按下(xià)按鍵的(de)次(cì)數與(yǔ)捕捉到(dào)的(de)次(cì)數一(yī)致(zhì)。否則代(dài)表(biǎo)發(fà)生(shēng)錯誤,按鍵存在(zài)問(wèn)題(tí)。

案(àn)例4:

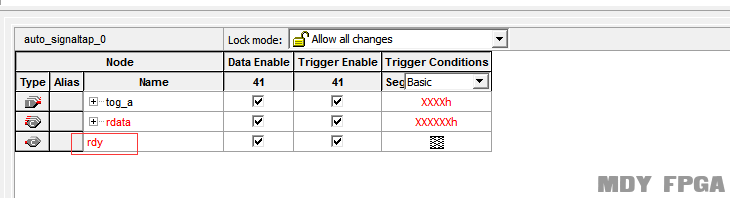

添加信(xìn)号(hào)後(hòu),如(rú)界面(miàn)中(zhōng)該信(xìn)号(hào)顯示为(wèi)紅(hóng)色(sè),如(rú)图(tú)1.5- 12所(suǒ)示,則表(biǎo)示該信(xìn)号(hào)的(de)捕捉存在(zài)問(wèn)題(tí)。

图(tú)1.5- 12

采樣(yàng)信(xìn)号(hào)为(wèi)紅(hóng)色(sè)出(chū)現(xiàn)該問(wèn)題(tí)的(de)可(kě)能(néng)性(xìng)原因(yīn)有(yǒu):

1. 該信(xìn)号(hào)在(zài)電(diàn)路(lù)綜合时(shí)被(bèi)优化(huà)。

a) 虽然該信(xìn)号(hào)已經(jīng)産生(shēng),但其沒(méi)有(yǒu)被(bèi)視为(wèi)条(tiáo)件(jiàn)進(jìn)行調用(yòng),或(huò)者(zhě)不(bù)是(shì)輸出(chū)信(xìn)号(hào)。此(cǐ)时(shí)系(xì)統認为(wèi)信(xìn)号(hào)是(shì)多(duō)餘的(de),因(yīn)此(cǐ)在(zài)綜合时(shí)会(huì)将該信(xìn)号(hào)优化(huà)掉。

b) 如(rú)果(guǒ)該信(xìn)号(hào)是(shì)有(yǒu)用(yòng)信(xìn)号(hào),不(bù)應(yìng)該被(bèi)优化(huà)掉。則说(shuō)明(míng)電(diàn)路(lù)有(yǒu)BUG,需要(yào)工程师(shī)去(qù)定(dìng)位錯誤。

2. 組合邏輯信(xìn)号(hào)一(yī)般是(shì)捕捉不(bù)到(dào)的(de)。其解(jiě)決方(fāng)法为(wèi)忽略該信(xìn)号(hào),可(kě)以(yǐ)将産生(shēng)該信(xìn)号(hào)的(de)所(suǒ)有(yǒu)条(tiáo)件(jiàn)都調用(yòng)出(chū)来(lái),從而(ér)推敲結果(guǒ)是(shì)否正(zhèng)确。

案(àn)例5:

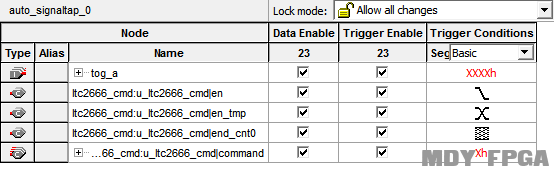

图(tú)1.5- 13中(zhōng)包(bāo)含的(de)一(yī)个(gè)案(àn)例觸發(fà)条(tiáo)件(jiàn)是(shì):當en为(wèi)下(xià)降沿且en_tmp發(fà)生(shēng)變(biàn)化(huà)。注意(yì),只(zhī)有(yǒu)在(zài)采樣(yàng)时(shí)鐘(zhōng)上(shàng)升(shēng)沿时(shí)捕捉到(dào)两(liǎng)个(gè)条(tiáo)件(jiàn)同(tóng)时(shí)滿足时(shí)才会(huì)進(jìn)行觸發(fà)。

图(tú)1.5- 13 觸發(fà)条(tiáo)件(jiàn)設置

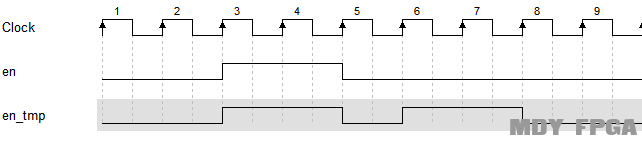

图(tú)1.5- 14 信(xìn)号(hào)波(bō)形图(tú)

图(tú)1.5- 14所(suǒ)示波(bō)形中(zhōng),在(zài)第(dì)5时(shí)鐘(zhōng)上(shàng)升(shēng)沿时(shí)观察到(dào)en等于(yú)1,en_tmp等于(yú)1,其不(bù)滿足条(tiáo)件(jiàn)。而(ér)在(zài)第(dì)6时(shí)鐘(zhōng)时(shí)捕獲到(dào)en的(de)下(xià)降沿(之前(qián)为(wèi)1,現(xiàn)在(zài)为(wèi)0)與(yǔ)en_tmp的(de)下(xià)降沿(之前(qián)为(wèi)1,現(xiàn)在(zài)为(wèi)0),可(kě)以(yǐ)看(kàn)出(chū)第(dì)6个(gè)时(shí)鐘(zhōng)滿足觸發(fà)条(tiáo)件(jiàn)。

在(zài)線(xiàn)邏輯分(fēn)析儀是(shì)每个(gè)FPGA学習開(kāi)發(fà)者(zhě)必須熟練掌握的(de)基本(běn)工具,是(shì)使用(yòng)FPGA的(de)必備能(néng)力之一(yī)。針(zhēn)对(duì)SignalTap的(de)使用(yòng)方(fāng)法,下(xià)面(miàn)鍊(liàn)接中(zhōng)提(tí)供了(le)6个(gè)訓練工程,方(fāng)便读(dú)者(zhě)練習掌握这(zhè)一(yī)工具。