|

本(běn)节(jié)的(de)文(wén)檔編号(hào):001100000061

需要(yào)看(kàn)对(duì)應(yìng)的(de)視頻,請點(diǎn)擊視頻編号(hào):001100000064 1、本(běn)节(jié)主(zhǔ)要(yào)進(jìn)行組合邏輯的(de)介紹,包(bāo)括:程序語(yǔ)句(jù)(assign語(yǔ)句(jù)、always語(yǔ)句(jù)),數字(zì)進(jìn)制(二(èr)進(jìn)制、不(bù)定(dìng)态、高(gāo)阻态),算數運算符(加、減、乘、除運算符),邏輯運算符(邏輯與(yǔ)、或(huò)、非(fēi)運算符),按位邏輯運算符(單目按位與(yǔ)、或(huò)、非(fēi)運算符,双(shuāng)目按位與(yǔ)、或(huò)、异(yì)或(huò)運算符),關(guān)系(xì)運算符,移位運算符(左(zuǒ)移、右(yòu)移運算符),条(tiáo)件(jiàn)運算符(三(sān)目運算符、if語(yǔ)句(jù)、case語(yǔ)句(jù)、選擇語(yǔ)句(jù)等),拼接運算符;

2、ALTERA和(hé)VIVADO文(wén)檔 5.7 移位運算符

在(zài)Verilog HDL中(zhōng)有(yǒu)两(liǎng)種(zhǒng)移位運算符,分(fēn)别为(wèi)“<<”(左(zuǒ)移位運算符)和(hé)“>>”(右(yòu)移位運算符)。

下(xià)面(miàn)分(fēn)别介紹两(liǎng)者(zhě)的(de)用(yòng)法:

5.7.1左(zuǒ)移運算符

在(zài)Verilog HDL中(zhōng),用(yòng)“<<”表(biǎo)示左(zuǒ)移運算符。其一(yī)般表(biǎo)达(dá)式为(wèi):

A<< n;

其中(zhōng),A代(dài)表(biǎo)要(yào)進(jìn)行移位的(de)操作數,n代(dài)表(biǎo)要(yào)左(zuǒ)移多(duō)少(shǎo)位。此(cǐ)表(biǎo)达(dá)式的(de)意(yì)義是(shì)把操作數A左(zuǒ)移n位。 左(zuǒ)移操作屬于(yú)邏輯移位,需要(yào)用(yòng)0来(lái)填補移出(chū)的(de)空位,即在(zài)低位補0。左(zuǒ)移n位,就(jiù)要(yào)補n个(gè)0。

以(yǐ)上(shàng)代(dài)碼由(yóu)于(yú)左(zuǒ)移了(le)2位,所(suǒ)以(yǐ)在(zài)低位補2个(gè)零(líng),所(suǒ)以(yǐ)上(shàng)面(miàn)代(dài)碼運行結果(guǒ)是(shì):a = 4’b1100。

左(zuǒ)移操作中(zhōng)有(yǒu)以(yǐ)下(xià)三(sān)點(diǎn)值得注意(yì)的(de)地(dì)方(fāng):

(1)左(zuǒ)移操作是(shì)不(bù)消耗邏輯資源的(de),甚至(zhì)連(lián)與(yǔ)門(mén)、非(fēi)門(mén)都不(bù)需要(yào),它(tā)只(zhī)是(shì)線(xiàn)的(de)連(lián)接。

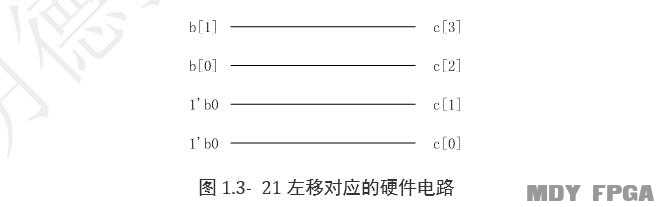

上(shàng)面(miàn)代(dài)碼是(shì)将信(xìn)号(hào)b左(zuǒ)移两(liǎng)位并賦給(gěi)c,其所(suǒ)对(duì)應(yìng)的(de)硬(yìng)件(jiàn)電(diàn)路(lù)如(rú)下(xià)图(tú):

(2)左(zuǒ)移操作需根(gēn)據(jù)位宽(kuān)儲存結果(guǒ)

读(dú)者(zhě)在(zài)学習过(guò)程中(zhōng)可(kě)能(néng)看(kàn)到(dào)过(guò)如(rú)下(xià)代(dài)碼:

4’b1001<<1=4’b0010與(yǔ)4’b1001<<1=5’b10010

为(wèi)什麼(me)操作數同(tóng)樣(yàng)是(shì)4’b1001,都是(shì)左(zuǒ)移一(yī)位,但結果(guǒ)一(yī)个(gè)是(shì)4’b0010,一(yī)个(gè)是(shì)5’b10010呢?

这(zhè)是(shì)因(yīn)为(wèi)左(zuǒ)移操作後(hòu),要(yào)看(kàn)用(yòng)多(duō)少(shǎo)位来(lái)存儲結果(guǒ)。

上(shàng)面(miàn)代(dài)碼中(zhōng)由(yóu)于(yú)a是(shì)4比特(tè),只(zhī)能(néng)保存4位結果(guǒ),所(suǒ)以(yǐ)b左(zuǒ)移1位賦給(gěi)4 bit的(de)a, 用(yòng)0填補移出(chū)的(de)位後(hòu)結果(guǒ)为(wèi)a = 4’b0010 ;

而(ér)上(shàng)面(miàn)代(dài)碼中(zhōng)由(yóu)于(yú)a是(shì)5比特(tè),能(néng)保存5位結果(guǒ),所(suǒ)以(yǐ)b左(zuǒ)移1位賦給(gěi)5 bit的(de)a, 用(yòng)0填補移出(chū)的(de)位後(hòu)結果(guǒ)为(wèi)a = 5’b10010 ;

(3)左(zuǒ)移操作的(de)操作數可(kě)以(yǐ)是(shì)常數,也(yě)可(kě)以(yǐ)是(shì)信(xìn)号(hào)。同(tóng)樣(yàng),左(zuǒ)移操作的(de)移位數、常數也(yě)可(kě)以(yǐ)是(shì)信(xìn)号(hào)。

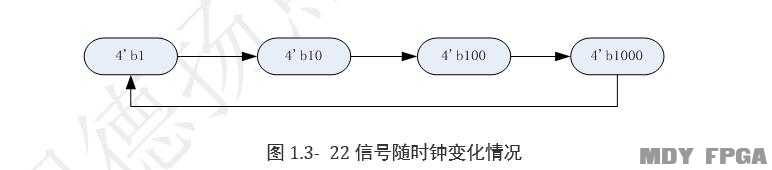

上(shàng)面(miàn)代(dài)碼中(zhōng)cnt每个(gè)时(shí)鐘(zhōng)加1,由(yóu)于(yú)是(shì)3比特(tè),所(suǒ)以(yǐ)值为(wèi)0~2。a則是(shì)4’b1左(zuǒ)移cnt位。 當cnt等于(yú)0时(shí)左(zuǒ)移0位,a等于(yú)4’b1;當cnt等于(yú)1时(shí)左(zuǒ)移1位,a等于(yú)4’b10。以(yǐ)此(cǐ)類(lèi)推,a的(de)每个(gè)时(shí)鐘(zhōng)變(biàn)化(huà)情(qíng)況如(rú)下(xià)所(suǒ)示:

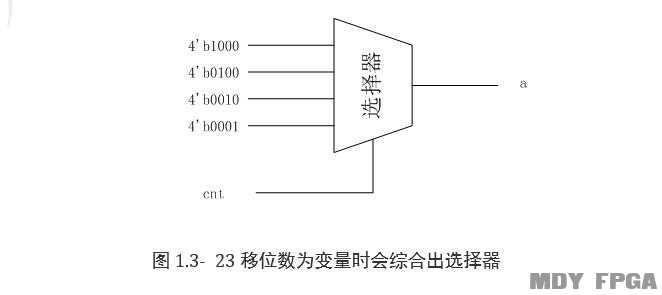

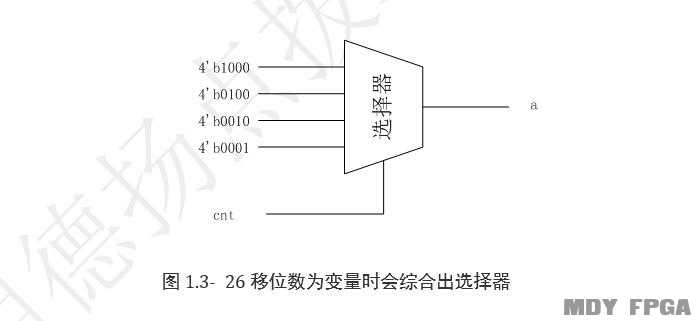

需要(yào)注意(yì)的(de)是(shì),當移位數是(shì)信(xìn)号(hào)时(shí),其綜合的(de)電(diàn)路(lù)并不(bù)是(shì)簡單的(de)連(lián)線(xiàn),可(kě)能(néng)会(huì)綜合出(chū)如(rú)下(xià)图(tú)所(suǒ)示的(de)選擇器。 然而(ér)即便如(rú)此(cǐ),这(zhè)種(zhǒng)硬(yìng)件(jiàn)電(diàn)路(lù)所(suǒ)消耗的(de)資源依然比較少(shǎo)。

5.7.2右(yòu)移運算符

在(zài)Verilog HDL中(zhōng),用(yòng)“>>”表(biǎo)示右(yòu)移運算符。其一(yī)般表(biǎo)达(dá)式为(wèi):A >>n;

其中(zhōng),A代(dài)表(biǎo)要(yào)進(jìn)行移位的(de)操作數,n代(dài)表(biǎo)要(yào)右(yòu)移多(duō)少(shǎo)位。此(cǐ)代(dài)碼表(biǎo)示的(de)意(yì)義是(shì)把操作數A右(yòu)移n位。

在(zài)右(yòu)移操作中(zhōng)有(yǒu)以(yǐ)下(xià)三(sān)點(diǎn)值得注意(yì)的(de)地(dì)方(fāng):

(1)右(yòu)移操作屬于(yú)邏輯移位,需要(yào)用(yòng)0来(lái)填補移出(chū)的(de)空位,即在(zài)高(gāo)位補0,補多(duō)少(shǎo)个(gè)0, 取(qǔ)決于(yú)保存結果(guǒ)的(de)信(xìn)号(hào)的(de)位宽(kuān)。

4’b0111右(yòu)移两(liǎng)位後(hòu)的(de)結果(guǒ)为(wèi)2’b01,由(yóu)于(yú)a是(shì)6位的(de),2位賦值給(gěi)6位需要(yào)在(zài)高(gāo)位補0, 因(yīn)此(cǐ)需要(yào)補4个(gè)0。所(suǒ)以(yǐ)上(shàng)面(miàn)代(dài)碼運行結果(guǒ)是(shì):

a = 6’b0001

(2)與(yǔ)左(zuǒ)移操作相似,右(yòu)移操作是(shì)不(bù)消耗邏輯資源的(de),甚至(zhì)連(lián)與(yǔ)門(mén)、非(fēi)門(mén)都不(bù)需要(yào),其只(zhī)是(shì)線(xiàn)的(de)連(lián)接。

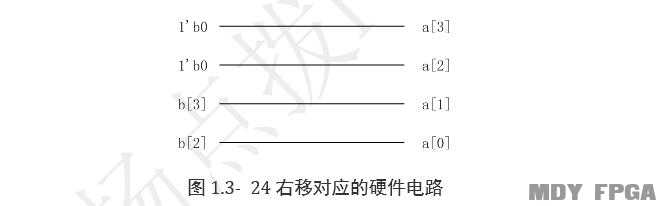

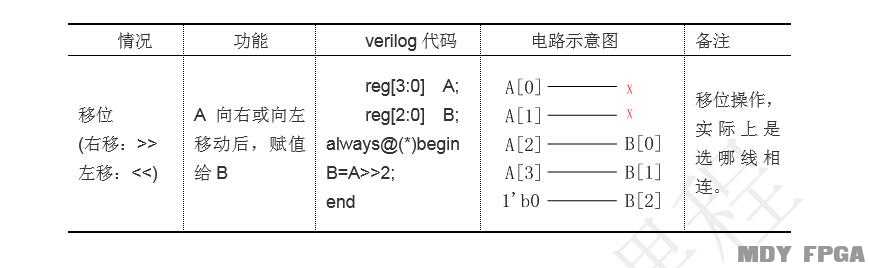

上(shàng)面(miàn)代(dài)碼是(shì)将信(xìn)号(hào)b左(zuǒ)移两(liǎng)位并賦給(gěi)a,其所(suǒ)对(duì)應(yìng)的(de)硬(yìng)件(jiàn)電(diàn)路(lù)如(rú)下(xià)图(tú)所(suǒ)示。

(3)左(zuǒ)移操作的(de)操作數可(kě)以(yǐ)是(shì)常數,也(yě)可(kě)以(yǐ)是(shì)信(xìn)号(hào)。同(tóng)樣(yàng),右(yòu)移操作的(de)移位數可(kě)以(yǐ)是(shì)常數,也(yě)可(kě)以(yǐ)是(shì)信(xìn)号(hào)。

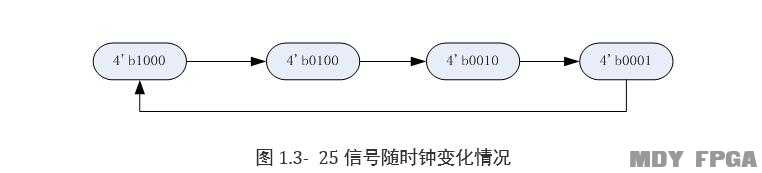

上(shàng)面(miàn)代(dài)碼中(zhōng),cnt每个(gè)时(shí)鐘(zhōng)加1,由(yóu)于(yú)是(shì)3比特(tè),所(suǒ)以(yǐ)值为(wèi)0~2。a則是(shì)4’b1000右(yòu)移cnt位。 當cnt等于(yú)0时(shí)右(yòu)移0位,a等于(yú)4’b1000;當cnt等于(yú)1时(shí)右(yòu)移1位,a等于(yú)4’b0100。以(yǐ)此(cǐ)類(lèi)推, a的(de)每个(gè)时(shí)鐘(zhōng)變(biàn)化(huà)情(qíng)況如(rú)下(xià)图(tú)所(suǒ)示。

與(yǔ)左(zuǒ)移操作類(lèi)似,在(zài)右(yòu)移操作中(zhōng),如(rú)果(guǒ)移位數是(shì)信(xìn)号(hào)时(shí),其綜合的(de)電(diàn)路(lù)就(jiù)不(bù)是(shì)簡單的(de)連(lián)線(xiàn), 而(ér)是(shì)有(yǒu)可(kě)能(néng)会(huì)綜合出(chū)如(rú)下(xià)图(tú)所(suǒ)示的(de)選擇器。然而(ér)同(tóng)樣(yàng)在(zài)这(zhè)一(yī)情(qíng)況下(xià),这(zhè)種(zhǒng)硬(yìng)件(jiàn)電(diàn)路(lù)所(suǒ)消耗的(de)資源依然比較

少(shǎo)。

FPGA中(zhōng)要(yào)盡量(liàng)避免乘法運算,因(yīn)为(wèi)这(zhè)種(zhǒng)計(jì)算需要(yào)占用(yòng)較大的(de)硬(yìng)件(jiàn)資源,并且運算速度(dù)較慢(màn)。 當不(bù)得不(bù)使用(yòng)乘法的(de)时(shí)候,盡量(liàng)乘以(yǐ)2的(de)N次(cì)方(fāng),这(zhè)樣(yàng)在(zài)設計(jì)中(zhōng)可(kě)以(yǐ)利用(yòng)左(zuǒ)移運算来(lái)实現(xiàn)該乘法運算, 從而(ér)大大減少(shǎo)硬(yìng)件(jiàn)資源。 當乘數是(shì)2的(de)N次(cì)方(fāng)的(de)常數时(shí)可(kě)以(yǐ)用(yòng)移位運算来(lái)实現(xiàn)乘法。例如(rú):a*2, 等價于(yú) a<<1;a*4等價于(yú)a<<2;a*8等價于(yú)a<<3,依此(cǐ)類(lèi)推。

即使乘數不(bù)是(shì)2的(de)N次(cì)方(fāng)的(de)常數,也(yě)可(kě)以(yǐ)通(tòng)过(guò)移位運算来(lái)簡化(huà)实現(xiàn)。例如(rú):

上(shàng)面(miàn)代(dài)碼中(zhōng)b和(hé)c都可(kě)以(yǐ)实現(xiàn)a*127,但第(dì)1行消耗了(le)一(yī)个(gè)乘法,而(ér)第(dì)2行則只(zhī)用(yòng)到(dào)一(yī)个(gè)減法器。

上(shàng)面(miàn)代(dài)碼中(zhōng),b和(hé)c都可(kě)以(yǐ)实現(xiàn)a*67,但第(dì)1行消耗了(le)一(yī)个(gè)乘法,而(ér)第(dì)2行則只(zhī)用(yòng)到(dào)两(liǎng)个(gè)加法器, 從而(ér)节(jié)省(shěng)了(le)資源。 有(yǒu)读(dú)者(zhě)可(kě)能(néng)注意(yì)到(dào),上(shàng)面(miàn)两(liǎng)个(gè)例子中(zhōng)的(de)乘數都是(shì)常數,那(nà)麼(me)在(zài)設計(jì)时(shí)这(zhè)種(zhǒng)乘法也(yě)要(yào)花时(shí)間(jiān)和(hé)精力来(lái)考慮优化(huà)吗? 其实是(shì)不(bù)必要(yào)的(de),因(yīn)为(wèi)現(xiàn)在(zài)綜合工具都很強(qiáng)大,當工具發(fà)現(xiàn)乘數是(shì)常數时(shí)会(huì)自(zì)動(dòng)按上(shàng)述过(guò)程進(jìn)行优化(huà), 也(yě)就(jiù)是(shì)说(shuō)乘以(yǐ)常數在(zài)实質(zhì)上(shàng)并不(bù)消耗乘法器資源,读(dú)者(zhě)可(kě)以(yǐ)放(fàng)心(xīn)使用(yòng)。 但當出(chū)現(xiàn)乘數不(bù)是(shì)常數的(de)情(qíng)況时(shí),读(dú)者(zhě)就(jiù)要(yào)注意(yì)乘法的(de)使用(yòng)了(le)。盡量(liàng)将信(xìn)号(hào)轉(zhuǎn)換为(wèi)與(yǔ)2的(de)N次(cì)方(fāng)相關(guān)的(de)形式。 例如(rú)當數據(jù)要(yào)擴大後(hòu)来(lái)計(jì)算时(shí),不(bù)要(yào)按照慣有(yǒu)思(sī)維将數據(jù)擴大100倍,而(ér)是(shì)應(yìng)該直(zhí)接将其擴大128倍。

FPGA設計(jì)中(zhōng)要(yào)极(jí)力避免除法,在(zài)笔(bǐ)者(zhě)眼(yǎn)中(zhōng)甚至(zhì)是(shì)嚴禁使用(yòng)“ /”来(lái)用(yòng)于(yú)除法計(jì)算。 这(zhè)是(shì)由(yóu)于(yú)除法器会(huì)占用(yòng)极(jí)大的(de)資源,其占用(yòng)資源量(liàng)要(yào)多(duō)于(yú)乘法器,而(ér)且很多(duō)时(shí)候不(bù)能(néng)在(zài)一(yī)个(gè)时(shí)鐘(zhōng)周期(qī)內(nèi)得出(chū)結果(guǒ)。 而(ér)當不(bù)得不(bù)使用(yòng)除法的(de)时(shí)候,读(dú)者(zhě)應(yìng)盡量(liàng)使除法轉(zhuǎn)化(huà)为(wèi)除以(yǐ)2的(de)N次(cì)方(fāng)形式, 这(zhè)樣(yàng)便可(kě)以(yǐ)利用(yòng)右(yòu)移運算来(lái)实現(xiàn)該除法運算,從而(ér)大大減少(shǎo)硬(yìng)件(jiàn)資源。 當除數是(shì)2的(de)N次(cì)方(fāng)的(de)常數时(shí),就(jiù)可(kě)以(yǐ)用(yòng)移位運算来(lái)实現(xiàn)除法。 例如(rú):a/2,等價于(yú) a>>1;a/4等價于(yú)a>>2;a/8等價于(yú)a>>3,依此(cǐ)類(lèi)推。

與(yǔ)左(zuǒ)移不(bù)同(tóng)的(de)是(shì),當除數不(bù)是(shì)2的(de)N次(cì)方(fāng)的(de)常數时(shí),不(bù)能(néng)簡單地(dì)通(tòng)过(guò)移位運算来(lái)簡化(huà)实現(xiàn)。

總(zǒng)而(ér)言之,在(zài)FPGA設計(jì)中(zhōng)應(yìng)盡力避免除法。

独热(rè)碼,也(yě)叫one-hot code,就(jiù)是(shì)只(zhī)有(yǒu)1个(gè)比特(tè)为(wèi)1,其他(tā)全(quán)为(wèi)0的(de)一(yī)種(zhǒng)碼制。 例如(rú)8’b00010000,8’b1000000等。 独热(rè)碼在(zài)設計(jì)时(shí)非(fēi)常有(yǒu)用(yòng),可(kě)以(yǐ)用(yòng)来(lái)表(biǎo)示狀态機(jī)的(de)狀态使狀态機(jī)更(gèng)健壯, 也(yě)可(kě)以(yǐ)用(yòng)于(yú)多(duō)選一(yī)的(de)電(diàn)路(lù)中(zhōng),表(biǎo)示選擇其中(zhōng)的(de)一(yī)个(gè)。 利用(yòng)左(zuǒ)移位操作,可(kě)以(yǐ)方(fāng)便地(dì)産生(shēng)独热(rè)碼,例如(rú)産生(shēng)4’b0010,可(kě)以(yǐ)是(shì)4’b1 << 1。 類(lèi)似地(dì),也(yě)可(kě)以(yǐ)産生(shēng)1个(gè)比特(tè)为(wèi)0,其他(tā)为(wèi)1的(de)碼制。例如(rú)産生(shēng)4’b1011,可(kě)以(yǐ)是(shì)~(4’b1<<2)。 利用(yòng)左(zuǒ)移操作,還(huán)可(kě)以(yǐ)産生(shēng)其他(tā)需要(yào)的(de)數字(zì)結果(guǒ):

例如(rú),産生(shēng)5’b00111,可(kě)以(yǐ)是(shì)(5’b1<<3)-1。

例如(rú),産生(shēng)5’b11100,可(kě)以(yǐ)是(shì)~((5’b1<<2)-1)。

相關(guān)視頻:https://www.bilibili.com/video/BV1yf4y1R7gH?p=18 |

産品中(zhōng)心(xīn) Product Center

| 明(míng)德揚開(kāi)發(fà)板 | XILINX官方(fāng)板 |

| 明(míng)德揚模块(kuài) | ALTERA官方(fāng)板 |

| 承接項目 | FPGA芯片(piàn) |

| 培訓專題(tí)課程 | 企業培訓 |

關(guān)于(yú)我(wǒ)们(men) About us

服(fú)务网(wǎng)站 Service website

教程中(zhōng)心(xīn) Tutorial center

新聞中(zhōng)心(xīn) News Center