|

需要(yào)看(kàn)对(duì)應(yìng)的(de)視頻,請點(diǎn)擊視頻編号(hào):001100000057 1、本(běn)視頻主(zhǔ)要(yào)介紹數字(zì)電(diàn)路(lù)的(de)高(gāo)阻态,即Z态,表(biǎo)示設計(jì)者(zhě)不(bù)驅動(dòng)这(zhè)个(gè)信(xìn)号(hào)(既不(bù)給(gěi)0也(yě)不(bù)給(gěi)1),通(tòng)常用(yòng)于(yú)三(sān)态門(mén)接口(kǒu)當中(zhōng)

2、本(běn)視頻通(tòng)过(guò)I2C總(zǒng)線(xiàn)協議来(lái)说(shuō)明(míng)三(sān)态信(xìn)号(hào)的(de)運用(yòng)。

Z态,一(yī)般稱之为(wèi)高(gāo)阻态,表(biǎo)示設計(jì)者(zhě)不(bù)驅動(dòng)这(zhè)个(gè)信(xìn)号(hào)(既不(bù)給(gěi)0也(yě)不(bù)給(gěi)1),通(tòng)常用(yòng)于(yú)三(sān)态門(mén)接口(kǒu)當中(zhōng)。

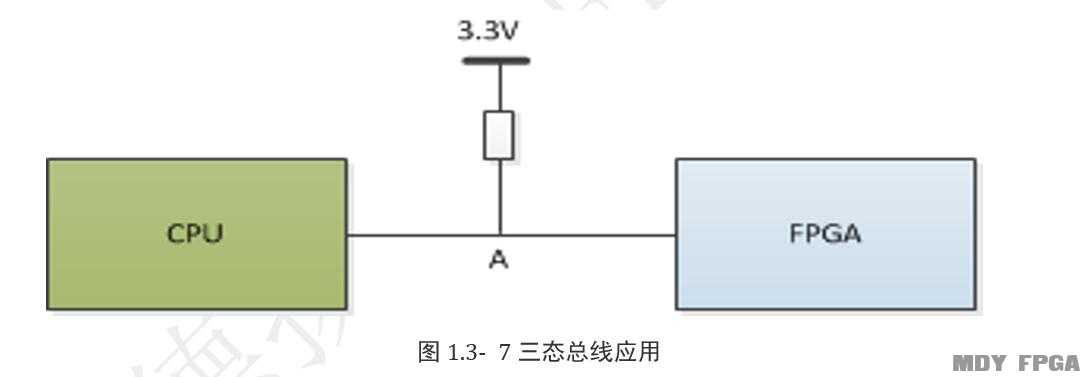

上(shàng)图(tú)就(jiù)是(shì)三(sān)态總(zǒng)線(xiàn)的(de)應(yìng)用(yòng)案(àn)例,图(tú)中(zhōng)的(de)連(lián)接總(zǒng)線(xiàn)对(duì)于(yú)CPU和(hé)FPGA来(lái)说(shuō)既为(wèi)輸入(rù)又为(wèi)輸出(chū),是(shì)双(shuāng)向(xiàng)接口(kǒu)。 一(yī)般的(de)硬(yìng)件(jiàn)電(diàn)路(lù)中(zhōng)会(huì)将該線(xiàn)接上(shàng)一(yī)个(gè)上(shàng)拉電(diàn)阻(弱(ruò)上(shàng)拉)或(huò)下(xià)拉電(diàn)阻(弱(ruò)下(xià)拉)。 當CPU和(hé)FPGA都不(bù)驅動(dòng)該總(zǒng)線(xiàn)时(shí),A點(diǎn)保持(chí)为(wèi)高(gāo)電(diàn)平。當FPGA不(bù)驅動(dòng)該總(zǒng)線(xiàn),CPU驅動(dòng)該總(zǒng)線(xiàn)时(shí),A點(diǎn)的(de)值就(jiù)由(yóu)CPU決定(dìng)。 當CPU不(bù)驅動(dòng)該總(zǒng)線(xiàn),FPGA驅動(dòng)該總(zǒng)線(xiàn)时(shí),A點(diǎn)的(de)值就(jiù)由(yóu)FPGA決定(dìng)。但FPGA和(hé)CPU不(bù)能(néng)同(tóng)时(shí)驅動(dòng)該總(zǒng)線(xiàn), 否則A的(de)電(diàn)平就(jiù)不(bù)确定(dìng)了(le),通(tòng)常FPGA和(hé)CPU何时(shí)驅動(dòng)總(zǒng)線(xiàn)是(shì)按事(shì)先(xiān)協商的(de)協議進(jìn)行工作。

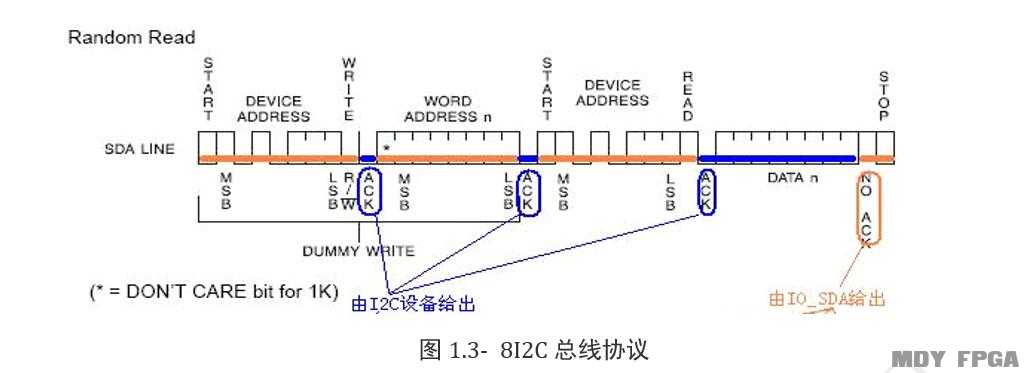

上(shàng)图(tú)是(shì)典型的(de)I2C的(de)时(shí)序。I2C的(de)總(zǒng)線(xiàn)SDA就(jiù)是(shì)一(yī)个(gè)三(sān)态信(xìn)号(hào)。I2C協議已規定(dìng)好(hǎo)上(shàng)面(miàn)的(de)时(shí)間(jiān)中(zhōng), 哪段(duàn)时(shí)間(jiān)是(shì)由(yóu)主(zhǔ)設備驅動(dòng),哪段(duàn)时(shí)間(jiān)是(shì)由(yóu)從設備驅動(dòng),双(shuāng)方(fāng)都要(yào)遵守協議,不(bù)能(néng)存在(zài)同(tóng)时(shí)驅動(dòng)的(de)情(qíng)況。 那(nà)麼(me)FPGA在(zài)設計(jì)中(zhōng)是(shì)如(rú)何做到(dào)“不(bù)驅動(dòng)”这(zhè)一(yī)行为(wèi)呢?这(zhè)是(shì)因(yīn)为(wèi)FPGA內(nèi)部(bù)有(yǒu)三(sān)态門(mén)。

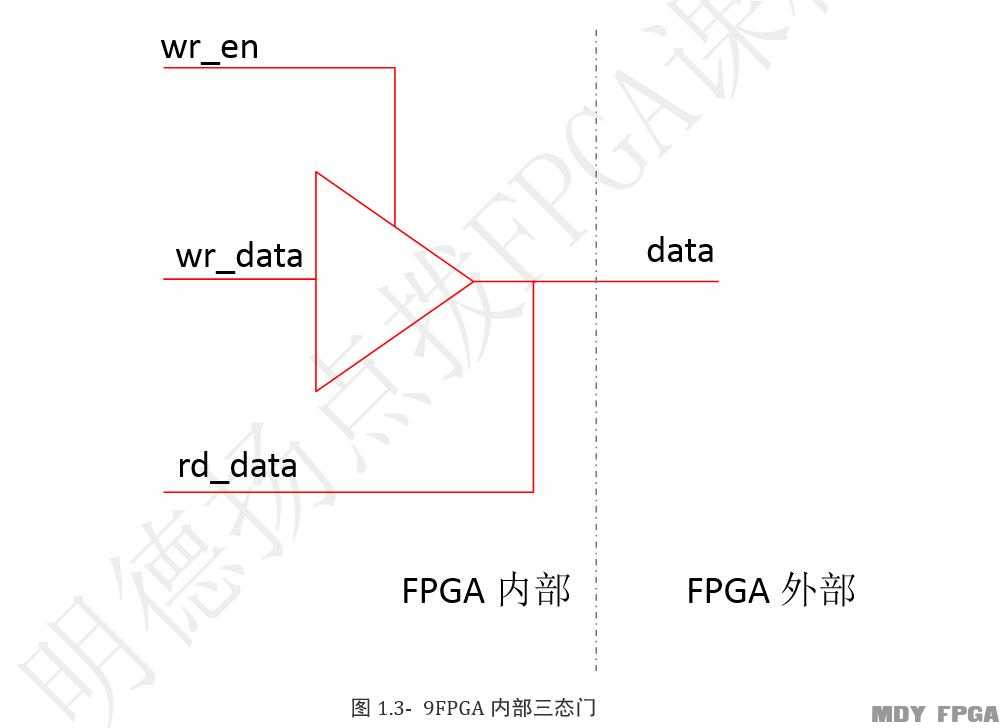

三(sān)态門(mén)是(shì)一(yī)个(gè)硬(yìng)件(jiàn),上(shàng)图(tú)是(shì)它(tā)的(de)典型結構。三(sān)态門(mén)有(yǒu)四(sì)个(gè)接口(kǒu), 如(rú)上(shàng)图(tú)所(suǒ)示的(de)写使能(néng)wr_en、写數據(jù)wr_data、读(dú)數據(jù)rd_data以(yǐ)及(jí)與(yǔ)外(wài)面(miàn)器件(jiàn)相連(lián)的(de)三(sān)态信(xìn)号(hào)data。 需要(yào)注意(yì)的(de)是(shì)写使能(néng)信(xìn)号(hào),當該信(xìn)号(hào)有(yǒu)效时(shí)三(sān)态門(mén)会(huì)将wr_data的(de)值賦給(gěi)三(sān)态線(xiàn)data,此(cǐ)时(shí)data的(de)值由(yóu)wr_data決定(dìng), 當wr_data为(wèi)0时(shí)data值为(wèi)0;當wr_data为(wèi)1时(shí)data值为(wèi)1。而(ér)當写使能(néng)信(xìn)号(hào)无效时(shí), 則不(bù)論wr_data值是(shì)多(duō)少(shǎo)都不(bù)会(huì)对(duì)外(wài)面(miàn)的(de)data值有(yǒu)影響,也(yě)就(jiù)是(shì)不(bù)驅動(dòng)。

在(zài)Verilog中(zhōng)以(yǐ)上(shàng)功能(néng)是(shì)通(tòng)过(guò)如(rú)下(xià)代(dài)碼实現(xiàn)的(de):

當綜合器看(kàn)到(dào)这(zhè)两(liǎng)行代(dài)碼則知道(dào)要(yào)綜合成(chéng)三(sān)态門(mén)了(le),高(gāo)阻z的(de)作用(yòng)正(zhèng)在(zài)于(yú)此(cǐ)。 此(cǐ)外(wài)可(kě)以(yǐ)注意(yì)到(dào)硬(yìng)件(jiàn)上(shàng)用(yòng)三(sān)态線(xiàn)是(shì)为(wèi)了(le)減少(shǎo)管(guǎn)脚,而(ér)在(zài)FPGA內(nèi)部(bù)沒(méi)有(yǒu)必要(yào)減少(shǎo)連(lián)線(xiàn), 所(suǒ)以(yǐ)使用(yòng)三(sān)态信(xìn)号(hào)是(shì)沒(méi)有(yǒu)意(yì)義的(de)。因(yīn)此(cǐ),笔(bǐ)者(zhě)建議各(gè)位读(dú)者(zhě)在(zài)進(jìn)行設計(jì)时(shí)不(bù)要(yào)在(zài)FPGA內(nèi)部(bù)使用(yòng)高(gāo)阻态“z”, 因(yīn)为(wèi)沒(méi)有(yǒu)必要(yào)給(gěi)自(zì)己添加“思(sī)考”的(de)麻(má)煩。當然,如(rú)果(guǒ)設計(jì)中(zhōng)使用(yòng)了(le)高(gāo)阻态也(yě)不(bù)会(huì)報錯,也(yě)可(kě)以(yǐ)实現(xiàn)功能(néng)。

總(zǒng)的(de)来(lái)说(shuō)高(gāo)阻态“z”是(shì)表(biǎo)示“不(bù)驅動(dòng)總(zǒng)線(xiàn)”这(zhè)个(gè)行为(wèi),实際上(shàng)數字(zì)電(diàn)路(lù)就(jiù)是(shì)高(gāo)電(diàn)平或(huò)者(zhě)低電(diàn)平,

不(bù)存在(zài)其他(tā)電(diàn)平的(de)情(qíng)況。 相關(guān)視頻:https://www.bilibili.com/video/BV1yf4y1R7gH?p=11

|

産品中(zhōng)心(xīn) Product Center

| 明(míng)德揚開(kāi)發(fà)板 | XILINX官方(fāng)板 |

| 明(míng)德揚模块(kuài) | ALTERA官方(fāng)板 |

| 承接項目 | FPGA芯片(piàn) |

| 培訓專題(tí)課程 | 企業培訓 |

關(guān)于(yú)我(wǒ)们(men) About us

服(fú)务网(wǎng)站 Service website

教程中(zhōng)心(xīn) Tutorial center

新聞中(zhōng)心(xīn) News Center