|

本(běn)节(jié)的(de)文(wén)檔編号(hào):001100000035 需要(yào)看(kàn)对(duì)應(yìng)的(de)視頻,請點(diǎn)擊視頻編号(hào): 001000000049

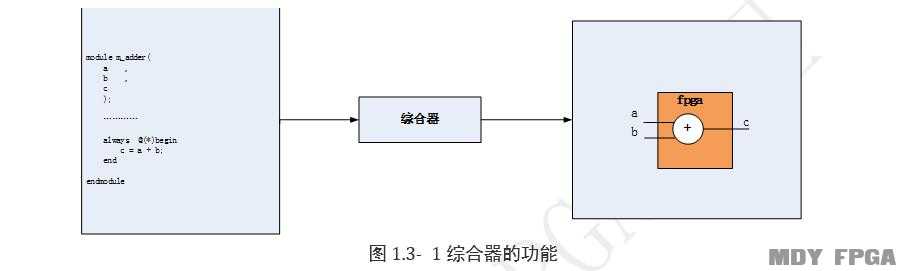

1、本(běn)节(jié)主(zhǔ)要(yào)介紹使用(yòng)綜合器对(duì)Verilog代(dài)碼進(jìn)行解(jiě)釋并将代(dài)碼轉(zhuǎn)化(huà)成(chéng)实際電(diàn)路(lù)来(lái)表(biǎo)示,最(zuì)終(zhōng)産生(shēng)实際電(diàn)路(lù)(网(wǎng)表(biǎo)),即綜合;为(wèi)了(le)避免在(zài)編写好(hǎo)代(dài)碼、綜合成(chéng)電(diàn)路(lù)、燒写到(dào)FPGA後(hòu)才發(fà)現(xiàn)問(wèn)題(tí),此(cǐ)时(shí)再去(qù)定(dìng)位問(wèn)題(tí)就(jiù)会(huì)非(fēi)常的(de)地(dì)困難,所(suǒ)以(yǐ),在(zài)綜合前(qián),設計(jì)师(shī)可(kě)以(yǐ)通(tòng)过(guò)仿真(zhēn)软(ruǎn)件(jiàn)对(duì)代(dài)碼進(jìn)行仿真(zhēn)测試,檢测出(chū)BUG并将其解(jiě)決,最(zuì)後(hòu)再将程序燒写進(jìn)FPGA,即仿真(zhēn);在(zài)Veriglog語(yǔ)言中(zhōng),有(yǒu)些語(yǔ)法結構只(zhī)是(shì)以(yǐ)仿真(zhēn)测試为(wèi)目的(de),是(shì)不(bù)能(néng)與(yǔ)实際硬(yìng)件(jiàn)電(diàn)路(lù)对(duì)應(yìng)起来(lái)的(de),也(yě)稱之为(wèi)不(bù)可(kě)綜合語(yǔ)法,本(běn)节(jié)整理了(le)不(bù)可(kě)綜合或(huò)者(zhě)不(bù)推薦使用(yòng)的(de)代(dài)碼。 第(dì)2节(jié) 綜合和(hé)仿真(zhēn) 2.1 綜合 Verilog是(shì)硬(yìng)件(jiàn)描述語(yǔ)言,顧名思(sī)義,就(jiù)是(shì)用(yòng)代(dài)碼的(de)形式描述硬(yìng)件(jiàn)的(de)功能(néng),最(zuì)終(zhōng)在(zài)硬(yìng)件(jiàn)電(diàn)路(lù)上(shàng)实現(xiàn)該功能(néng)。 在(zài)Verilog描述出(chū)硬(yìng)件(jiàn)功能(néng)後(hòu)需要(yào)使用(yòng)綜合器对(duì)Verilog代(dài)碼進(jìn)行解(jiě)釋并将代(dài)碼轉(zhuǎn)化(huà)成(chéng)实際的(de)電(diàn)路(lù)来(lái)表(biǎo)示, 最(zuì)終(zhōng)産生(shēng)实際的(de)電(diàn)路(lù),也(yě)被(bèi)稱为(wèi)网(wǎng)表(biǎo)。这(zhè)種(zhǒng)将Verilog代(dài)碼轉(zhuǎn)成(chéng)网(wǎng)表(biǎo)的(de)工具就(jiù)是(shì)綜合器。

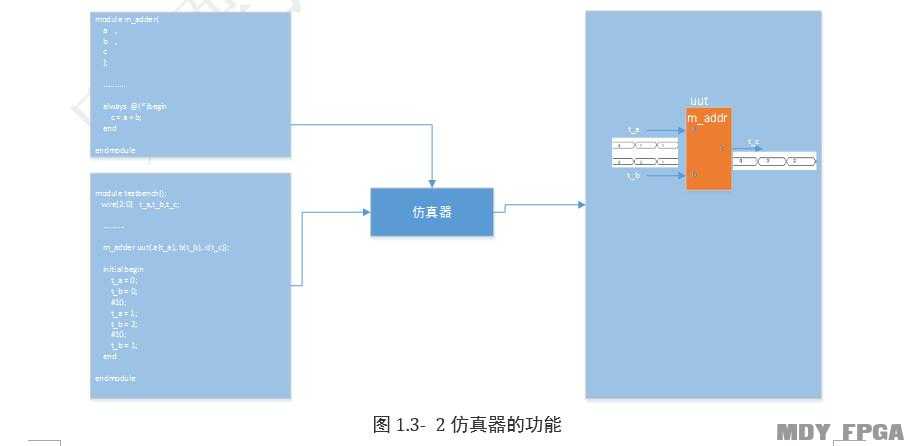

上(shàng)图(tú)左(zuǒ)上(shàng)角(jiǎo)是(shì)一(yī)段(duàn)Verilog代(dài)碼,該代(dài)碼实現(xiàn)了(le)一(yī)个(gè)加法器的(de)功能(néng)。 在(zài)經(jīng)过(guò)綜合器解(jiě)釋後(hòu)該代(dài)碼被(bèi)轉(zhuǎn)化(huà)成(chéng)一(yī)个(gè)加法器電(diàn)路(lù)。 QUARTUS、ISE和(hé)VIVADO等FPGA開(kāi)發(fà)工具都是(shì)綜合器,而(ér)在(zài)集成(chéng)電(diàn)路(lù)設計(jì)領域常用(yòng)的(de)綜合器是(shì)DC。 2.2 仿真(zhēn) 在(zài)FPGA設計(jì)的(de)过(guò)程中(zhōng),不(bù)可(kě)避免会(huì)出(chū)現(xiàn)各(gè)種(zhǒng)BUG。如(rú)果(guǒ)在(zài)編写好(hǎo)代(dài)碼、綜合成(chéng)電(diàn)路(lù)、燒写到(dào)FPGA後(hòu)才發(fà)現(xiàn)問(wèn)題(tí), 此(cǐ)时(shí)再去(qù)定(dìng)位問(wèn)題(tí)就(jiù)会(huì)非(fēi)常地(dì)困難。而(ér)在(zài)綜合前(qián),設計(jì)师(shī)可(kě)以(yǐ)在(zài)電(diàn)腦里(lǐ)通(tòng)过(guò)仿真(zhēn)软(ruǎn)件(jiàn)对(duì)代(dài)碼進(jìn)行仿真(zhēn)测試, 檢测出(chū)BUG并将其解(jiě)決,最(zuì)後(hòu)再将程序燒写進(jìn)FPGA。一(yī)般情(qíng)況下(xià)可(kě)以(yǐ)認为(wèi)沒(méi)有(yǒu)經(jīng)过(guò)仿真(zhēn)验(yàn)證的(de)代(dài)碼,一(yī)定(dìng)是(shì)存在(zài)BUG的(de)。

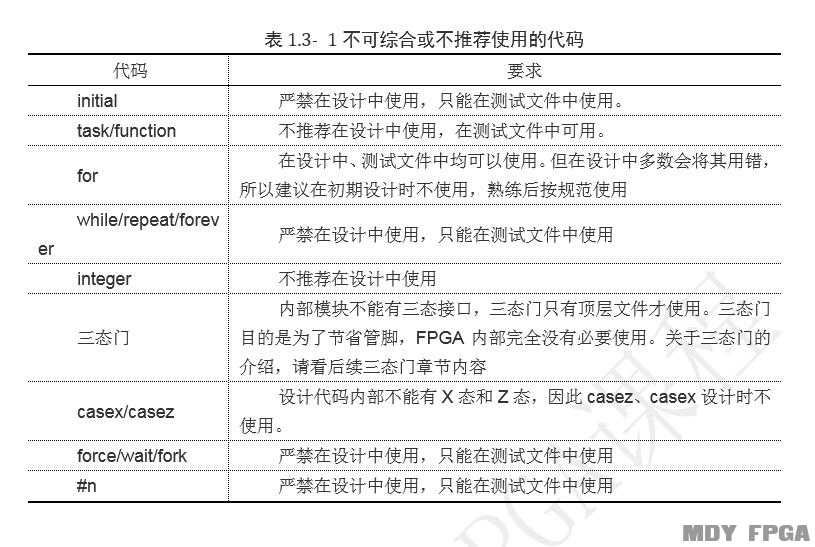

为(wèi)了(le)模拟真(zhēn)实的(de)情(qíng)況,需要(yào)編写测試文(wén)件(jiàn)。該文(wén)件(jiàn)也(yě)是(shì)用(yòng)Verilog編写的(de),其描述了(le)仿真(zhēn)对(duì)象(xiàng)的(de)輸入(rù)激勵情(qíng)況。 該激勵力求模仿最(zuì)真(zhēn)实的(de)情(qíng)況,産生(shēng)最(zuì)接近(jìn)的(de)激勵信(xìn)号(hào),将該信(xìn)号(hào)的(de)波(bō)形輸入(rù)給(gěi)仿真(zhēn)对(duì)象(xiàng), 查看(kàn)仿真(zhēn)对(duì)象(xiàng)的(de)輸出(chū)是(shì)否與(yǔ)預期(qī)一(yī)致(zhì)。需要(yào)注意(yì)的(de)是(shì):在(zài)仿真(zhēn)过(guò)程中(zhōng)沒(méi)有(yǒu)将代(dài)碼轉(zhuǎn)成(chéng)電(diàn)路(lù), 仿真(zhēn)器只(zhī)是(shì)对(duì)代(dài)碼進(jìn)行仿真(zhēn)验(yàn)證。至(zhì)于(yú)該代(dài)碼是(shì)否可(kě)轉(zhuǎn)成(chéng)電(diàn)路(lù),仿真(zhēn)器并不(bù)關(guān)心(xīn)。 由(yóu)此(cǐ)可(kě)見(jiàn),Verilog的(de)代(dài)碼不(bù)僅可(kě)以(yǐ)描述電(diàn)路(lù),還(huán)可(kě)以(yǐ)用(yòng)于(yú)测試。事(shì)实上(shàng),Verilog定(dìng)義的(de)語(yǔ)法非(fēi)常之多(duō), 但絕大部(bù)分(fēn)都是(shì)为(wèi)了(le)仿真(zhēn)测試来(lái)使用(yòng)的(de),只(zhī)有(yǒu)少(shǎo)部(bù)分(fēn)才是(shì)用(yòng)于(yú)電(diàn)路(lù)設計(jì),詳细(xì)可(kě)以(yǐ)參考本(běn)書(shū)的(de)“可(kě)綜合邏輯設計(jì)”一(yī)节(jié)。 Verilog中(zhōng)用(yòng)于(yú)設計(jì)的(de)語(yǔ)法是(shì)学習的(de)重(zhòng)點(diǎn),掌握好(hǎo)設計(jì)的(de)語(yǔ)法并熟練應(yìng)用(yòng)于(yú)各(gè)種(zhǒng)複雜的(de)項目是(shì)技能(néng)的(de)核心(xīn)。 而(ér)其他(tā)测試用(yòng)的(de)語(yǔ)法,在(zài)需要(yào)时(shí)查找(zhǎo)和(hé)參考就(jiù)已經(jīng)足够了(le)。本(běn)書(shū)旨在(zài)方(fāng)便本(běn)科、研究生(shēng)的(de)教学,因(yīn)此(cǐ)将重(zhòng)點(diǎn)講解(jiě)設計(jì)用(yòng)的(de)語(yǔ)法。 Verilog硬(yìng)件(jiàn)描述語(yǔ)言有(yǒu)類(lèi)似高(gāo)級語(yǔ)言的(de)完整語(yǔ)法結構和(hé)系(xì)統,这(zhè)些語(yǔ)法結構的(de)應(yìng)用(yòng)給(gěi)設計(jì)描述带(dài)来(lái)很多(duō)方(fāng)便。 但是(shì),Verilog是(shì)描述硬(yìng)件(jiàn)電(diàn)路(lù)的(de),其建立在(zài)硬(yìng)件(jiàn)電(diàn)路(lù)的(de)基礎之上(shàng)。而(ér)有(yǒu)些語(yǔ)法結構只(zhī)是(shì)以(yǐ)仿真(zhēn)测試为(wèi)目的(de), 是(shì)不(bù)能(néng)與(yǔ)实際硬(yìng)件(jiàn)電(diàn)路(lù)对(duì)應(yìng)起来(lái)的(de)。也(yě)就(jiù)是(shì)说(shuō)在(zài)使用(yòng)这(zhè)些語(yǔ)法时(shí), 将一(yī)个(gè)語(yǔ)言描述的(de)程序映射成(chéng)实際硬(yìng)件(jiàn)電(diàn)路(lù)中(zhōng)的(de)結構是(shì)不(bù)能(néng)实現(xiàn)的(de),也(yě)稱为(wèi)不(bù)可(kě)綜合語(yǔ)法。 綜合就(jiù)是(shì)把編写的(de)rtl代(dài)碼轉(zhuǎn)換成(chéng)对(duì)應(yìng)的(de)实際電(diàn)路(lù)。 比如(rú)編写代(dài)碼assign a=b&c;EDA綜合工具就(jiù)会(huì)去(qù)元(yuán)件(jiàn)庫里(lǐ)調用(yòng)一(yī)个(gè)二(èr)輸入(rù)與(yǔ)門(mén), 将輸入(rù)端分(fēn)别接上(shàng)b和(hé)c,輸出(chū)端接上(shàng)a。

同(tóng)樣(yàng)地(dì),如(rú)果(guǒ)設計(jì)师(shī)編写了(le)一(yī)些如(rú)下(xià)所(suǒ)示的(de)語(yǔ)句(jù)

assign a=b&c;

assign c=e|f;

assign e=x^y;

……

綜合工具就(jiù)会(huì)像搭積木(mù)一(yī)樣(yàng)把这(zhè)些“邏輯”電(diàn)路(lù)用(yòng)一(yī)些“門(mén)”電(diàn)路(lù)来(lái)搭起来(lái)。 當然,工具会(huì)对(duì)必要(yào)的(de)地(dì)方(fāng)做一(yī)些优化(huà),比如(rú)編写一(yī)个(gè)電(diàn)路(lù)assing a=b&~b,工具就(jiù)会(huì)将a恒接为(wèi)0, 而(ér)不(bù)会(huì)去(qù)調用(yòng)一(yī)个(gè)與(yǔ)門(mén)来(lái)搭这(zhè)个(gè)電(diàn)路(lù)。 綜上(shàng)所(suǒ)述,“綜合”要(yào)做的(de)事(shì)情(qíng)有(yǒu):編譯rtl代(dài)碼,從庫里(lǐ)選擇用(yòng)到(dào)的(de)門(mén)器件(jiàn), 把这(zhè)些器件(jiàn)按照“邏輯”搭建成(chéng)“門(mén)”電(diàn)路(lù)。 不(bù)可(kě)綜合,是(shì)指找(zhǎo)不(bù)到(dào)对(duì)應(yìng)的(de)“門(mén)”器件(jiàn)来(lái)实現(xiàn)相應(yìng)的(de)代(dài)碼。比如(rú)“#100”之類(lèi)的(de)延时(shí)功能(néng), 簡單的(de)門(mén)器件(jiàn)是(shì)无法实現(xiàn)延时(shí)100个(gè)單元(yuán)的(de),還(huán)有(yǒu)打(dǎ)印(yìn)語(yǔ)句(jù)等,也(yě)是(shì)門(mén)器件(jiàn)无法实現(xiàn)的(de)。 在(zài)設計(jì)的(de)时(shí)候要(yào)确保所(suǒ)写的(de)代(dài)碼是(shì)可(kě)以(yǐ)綜合的(de),这(zhè)就(jiù)依賴于(yú)設計(jì)者(zhě)的(de)能(néng)力,知道(dào)什麼(me)是(shì)可(kě)綜合的(de)代(dài)碼, 什麼(me)是(shì)不(bù)可(kě)綜合的(de)代(dài)碼。对(duì)于(yú)初学者(zhě)来(lái)说(shuō),最(zuì)好(hǎo)是(shì)先(xiān)記(jì)住規則,遵守規則, 先(xiān)按規則来(lái)設計(jì)電(diàn)路(lù)并在(zài)这(zhè)一(yī)过(guò)程中(zhōng)逐漸理解(jiě),这(zhè)是(shì)最(zuì)好(hǎo)的(de)学習路(lù)徑。

下(xià)面(miàn)表(biǎo)格中(zhōng)列出(chū)了(le)不(bù)可(kě)綜合或(huò)者(zhě)不(bù)推薦使用(yòng)的(de)代(dài)碼。

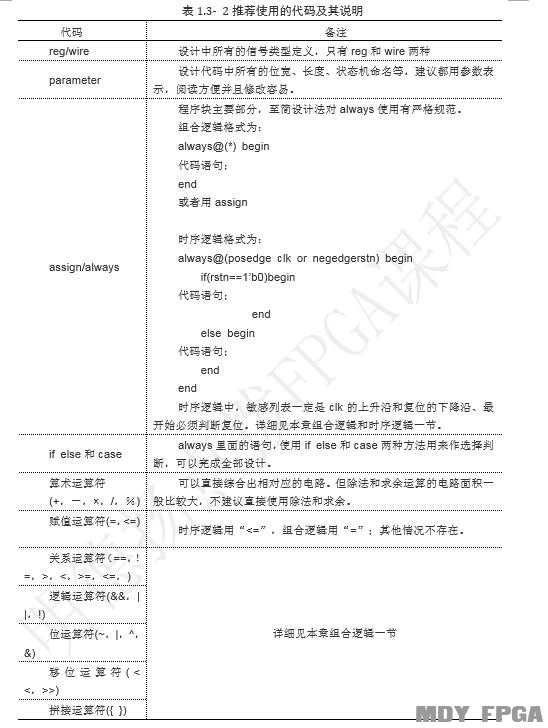

下(xià)表(biǎo)是(shì)笔(bǐ)者(zhě)推薦使用(yòng)的(de)設計(jì)。

相關(guān)視頻:https://www.bilibili.com/video/BV1yf4y1R7gH?p=4 |

産品中(zhōng)心(xīn) Product Center

| 明(míng)德揚開(kāi)發(fà)板 | XILINX官方(fāng)板 |

| 明(míng)德揚模块(kuài) | ALTERA官方(fāng)板 |

| 承接項目 | FPGA芯片(piàn) |

| 培訓專題(tí)課程 | 企業培訓 |

關(guān)于(yú)我(wǒ)们(men) About us

服(fú)务网(wǎng)站 Service website

教程中(zhōng)心(xīn) Tutorial center

新聞中(zhōng)心(xīn) News Center