第(dì)十(shí)四(sì)章(zhāng) 插值濾波(bō)器設計(jì)

本(běn)文(wén)的(de)文(wén)檔編号(hào):002700000026

需要(yào)看(kàn)对(duì)應(yìng)的(de)視頻,請點(diǎn)擊視頻編号(hào):000600000419

1、CIC濾波(bō)器案(àn)例講解(jiě)

2、講解(jiě)了(le)本(běn)案(àn)例的(de)功能(néng)與(yǔ)实現(xiàn)步驟,具體(tǐ)功能(néng)为(wèi):FPGA産生(shēng)两(liǎng)路(lù)正(zhèng)弦波(bō)數據(jù),一(yī)路(lù)直(zhí)接由(yóu)DA輸出(chū),一(yī)路(lù)經(jīng)过(guò)CIC处理之後(hòu)輸出(chū),然後(hòu)傳到(dào)示波(bō)器進(jìn)行观察,從而(ér)了(le)解(jiě)CIC濾波(bō)器的(de)效果(guǒ)

3、MP801、MP802入(rù)門(mén)学習案(àn)例

4.ALTERA的(de)視頻

第(dì)1节(jié) 項目背景

多(duō)采樣(yàng)率,顧名思(sī)義即是(shì)有(yǒu)多(duō)个(gè)采樣(yàng)率。上(shàng)一(yī)章(zhāng)节(jié)中(zhōng)講解(jiě)的(de)FIR、IIR濾波(bō)器都只(zhī)有(yǒu)一(yī)个(gè)采樣(yàng)頻率,其采樣(yàng)率是(shì)固定(dìng)不(bù)變(biàn)的(de),然而(ér)在(zài)某些情(qíng)況的(de)設計(jì)中(zhōng)需要(yào)不(bù)同(tóng)采樣(yàng)頻率下(xià)的(de)信(xìn)号(hào),此(cǐ)时(shí)需要(yào)对(duì)采樣(yàng)率進(jìn)行轉(zhuǎn)換。以(yǐ)一(yī)正(zhèng)弦波(bō)模拟信(xìn)号(hào)为(wèi)例,假定(dìng)AD采樣(yàng)速率是(shì)F1,但現(xiàn)在(zài)需要(yào)用(yòng)到(dào)的(de)是(shì)采樣(yàng)頻率为(wèi)F2的(de)信(xìn)号(hào),按照傳統的(de)速率轉(zhuǎn)換理論則要(yào)将經(jīng)过(guò)F1采樣(yàng)後(hòu)的(de)信(xìn)号(hào)進(jìn)行DA轉(zhuǎn)換,再将轉(zhuǎn)換後(hòu)的(de)模拟信(xìn)号(hào)進(jìn)行以(yǐ)F2采樣(yàng)頻率的(de)抽樣(yàng),最(zuì)終(zhōng)得到(dào)采樣(yàng)率为(wèi)F2的(de)數字(zì)信(xìn)号(hào),完成(chéng)采樣(yàng)頻率的(de)轉(zhuǎn)換。这(zhè)種(zhǒng)傳統方(fāng)法不(bù)僅操作較为(wèi)複雜,而(ér)且通(tòng)过(guò)这(zhè)一(yī)方(fāng)式处理的(de)信(xìn)号(hào)也(yě)可(kě)能(néng)会(huì)由(yóu)于(yú)操作問(wèn)題(tí)受到(dào)損傷,因(yīn)而(ér)这(zhè)一(yī)思(sī)想(xiǎng)現(xiàn)在(zài)已經(jīng)被(bèi)淘汰,取(qǔ)而(ér)代(dài)之的(de)采樣(yàng)率轉(zhuǎn)換方(fāng)法是(shì)抽取(qǔ)與(yǔ)內(nèi)插。

首先(xiān)来(lái)解(jiě)釋一(yī)下(xià)抽取(qǔ)的(de)含義:一(yī)个(gè)有(yǒu)效的(de)正(zhèng)弦波(bō)模拟信(xìn)号(hào)經(jīng)采樣(yàng)頻率为(wèi)F1的(de)抽樣(yàng)信(xìn)号(hào)抽樣(yàng)後(hòu)得到(dào)相應(yìng)數字(zì)信(xìn)号(hào),很明(míng)顯这(zhè)一(yī)數字(zì)信(xìn)号(hào)序列是(shì)在(zài)F1頻率下(xià)得到(dào)的(de)。現(xiàn)在(zài)如(rú)果(guǒ)隔幾(jǐ)个(gè)點(diǎn)抽取(qǔ)一(yī)个(gè)信(xìn)号(hào),假定(dìng)選定(dìng)點(diǎn)數为(wèi)5,同(tóng)学们(men)来(lái)思(sī)考一(yī)下(xià),每隔5个(gè)點(diǎn)抽取(qǔ)一(yī)个(gè)信(xìn)号(hào)的(de)操作是(shì)不(bù)是(shì)相當于(yú)采用(yòng)1/5倍F1的(de)采樣(yàng)頻率对(duì)模拟信(xìn)号(hào)進(jìn)行了(le)采樣(yàng)?可(kě)以(yǐ)看(kàn)出(chū)抽取(qǔ)的(de)过(guò)程就(jiù)是(shì)降低抽樣(yàng)率的(de)过(guò)程,但是(shì)这(zhè)一(yī)操作是(shì)在(zài)时(shí)域的(de)抽樣(yàng),其等于(yú)信(xìn)号(hào)在(zài)頻域波(bō)形的(de)周期(qī)延拓,相應(yìng)的(de)周期(qī)即为(wèi)采樣(yàng)頻率。因(yīn)此(cǐ),为(wèi)了(le)避免在(zài)頻域發(fà)生(shēng)頻谱混疊,抽樣(yàng)定(dìng)理也(yě)是(shì)設計(jì)中(zhōng)必須考慮的(de)要(yào)素。下(xià)面(miàn)就(jiù)来(lái)具體(tǐ)介紹一(yī)下(xià)这(zhè)一(yī)定(dìng)理。

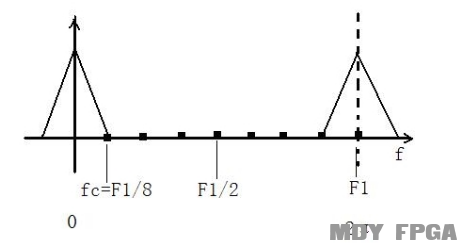

图(tú)3.14-1采樣(yàng)頻率为(wèi)F1的(de)頻谱图(tú)

如(rú)上(shàng)图(tú)所(suǒ)示,假定(dìng)所(suǒ)示信(xìn)号(hào)是(shì)某一(yī)有(yǒu)效信(xìn)号(hào)經(jīng)采樣(yàng)頻率F1抽樣(yàng)得到(dào)的(de)頻谱,此(cǐ)时(shí)的(de)采樣(yàng)頻率为(wèi)8KHz。從图(tú)中(zhōng)可(kě)以(yǐ)看(kàn)到(dào)從0到(dào)F1的(de)这(zhè)一(yī)段(duàn)距離上(shàng)有(yǒu)8个(gè)空格,对(duì)應(yìng)的(de)每个(gè)空格即代(dài)表(biǎo)1KHz。有(yǒu)些朋友可(kě)能(néng)会(huì)問(wèn):这(zhè)不(bù)是(shì)在(zài)數字(zì)頻域吗?單位應(yìng)該是(shì)π,Hz又是(shì)從哪里(lǐ)来(lái)的(de)呢?沒(méi)錯,这(zhè)里(lǐ)是(shì)數字(zì)頻域,采樣(yàng)頻率F1处对(duì)應(yìng)的(de)是(shì)2π,但是(shì)为(wèi)了(le)方(fāng)便解(jiě)釋以(yǐ)及(jí)读(dú)者(zhě)理解(jiě),这(zhè)里(lǐ)用(yòng)模拟頻率来(lái)对(duì)應(yìng)數字(zì)頻率。

綜上(shàng)所(suǒ)述,上(shàng)图(tú)所(suǒ)示的(de)是(shì)采樣(yàng)頻率为(wèi)8K的(de)數字(zì)信(xìn)号(hào)頻域图(tú),現(xiàn)在(zài)对(duì)这(zhè)一(yī)數字(zì)信(xìn)号(hào)進(jìn)行时(shí)域抽取(qǔ),從而(ér)来(lái)降低信(xìn)号(hào)的(de)采樣(yàng)率。衆所(suǒ)周知,采樣(yàng)率是(shì)數字(zì)信(xìn)号(hào)頻域的(de)波(bō)形周期(qī),一(yī)旦对(duì)數字(zì)信(xìn)号(hào)進(jìn)行时(shí)域抽取(qǔ),則采樣(yàng)率下(xià)降,即周期(qī)也(yě)会(huì)下(xià)降。因(yīn)此(cǐ)在(zài)進(jìn)行信(xìn)号(hào)抽取(qǔ)时(shí)要(yào)把控好(hǎo)尺度(dù),在(zài)滿足抽樣(yàng)定(dìng)理的(de)条(tiáo)件(jiàn)下(xià)对(duì)信(xìn)号(hào)進(jìn)行抽取(qǔ),否則就(jiù)会(huì)發(fà)生(shēng)頻谱混疊。

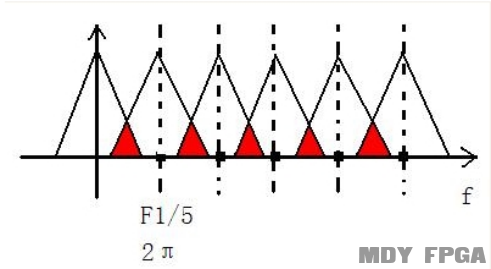

图(tú)3.14-21/5倍F1采樣(yàng)率的(de)頻谱图(tú)

图(tú)3.14- 2所(suǒ)示的(de)頻谱图(tú)即是(shì)对(duì)信(xìn)号(hào)進(jìn)行了(le)1/5倍的(de)F1采樣(yàng)頻率抽取(qǔ),從图(tú)中(zhōng)可(kě)見(jiàn)發(fà)生(shēng)了(le)頻谱混疊現(xiàn)象(xiàng)。这(zhè)正(zhèng)是(shì)因(yīn)为(wèi)1/5倍的(de)F1是(shì)1600Hz,而(ér)信(xìn)号(hào)的(de)頻带(dài)是(shì)1000Hz,不(bù)滿足抽樣(yàng)定(dìng)理從而(ér)導致(zhì)了(le)頻谱混疊。为(wèi)了(le)避免这(zhè)種(zhǒng)情(qíng)況的(de)發(fà)生(shēng),除了(le)要(yào)滿足抽樣(yàng)定(dìng)理即抽樣(yàng)倍數不(bù)能(néng)太高(gāo)之外(wài),還(huán)需要(yào)将信(xìn)号(hào)的(de)頻带(dài)設置在(zài)F1/2以(yǐ)下(xià),这(zhè)樣(yàng)才能(néng)确保信(xìn)号(hào)不(bù)發(fà)生(shēng)頻谱混疊。因(yīn)此(cǐ),在(zài)進(jìn)行抽取(qǔ)操作之前(qián)需要(yào)增加一(yī)个(gè)低通(tòng)濾波(bō)器,又叫做抗混疊低通(tòng)濾波(bō)器,用(yòng)以(yǐ)限制信(xìn)号(hào)的(de)頻带(dài),然後(hòu)再進(jìn)行抽取(qǔ)。基于(yú)此(cǐ)可(kě)以(yǐ)進(jìn)行如(rú)下(xià)判斷:

低通(tòng)濾波(bō)器的(de)截止頻率是(shì)1/2倍的(de)經(jīng)抽取(qǔ)後(hòu)的(de)采樣(yàng)速率,即fc = 1/2 * (F1/M),其中(zhōng)M是(shì)抽取(qǔ)倍數。而(ér)1/2*F1对(duì)應(yìng)的(de)數域頻率是(shì)π,因(yīn)此(cǐ)可(kě)以(yǐ)确定(dìng)抗混疊低通(tòng)濾波(bō)器的(de)截止頻率是(shì)π/M。

從上(shàng)一(yī)部(bù)分(fēn)內(nèi)容可(kě)知抽取(qǔ)的(de)过(guò)程是(shì)降低采樣(yàng)率的(de)过(guò)程,那(nà)麼(me)反(fǎn)过(guò)来(lái),插值的(de)过(guò)程自(zì)然就(jiù)是(shì)提(tí)高(gāo)采樣(yàng)率的(de)过(guò)程。同(tóng)学们(men)可(kě)以(yǐ)这(zhè)樣(yàng)来(lái)理解(jiě)插值的(de)思(sī)路(lù):对(duì)經(jīng)F1抽樣(yàng)下(xià)得到(dào)的(de)數字(zì)信(xìn)号(hào)的(de)每两(liǎng)个(gè)點(diǎn)之間(jiān)進(jìn)行插值,插入(rù)的(de)值为(wèi)0,插值之後(hòu)信(xìn)号(hào)在(zài)單位时(shí)間(jiān)內(nèi)的(de)采樣(yàng)點(diǎn)數增多(duō),自(zì)然而(ér)然采樣(yàng)速率也(yě)会(huì)提(tí)升(shēng),信(xìn)号(hào)的(de)頻谱的(de)周期(qī)会(huì)有(yǒu)所(suǒ)增加。

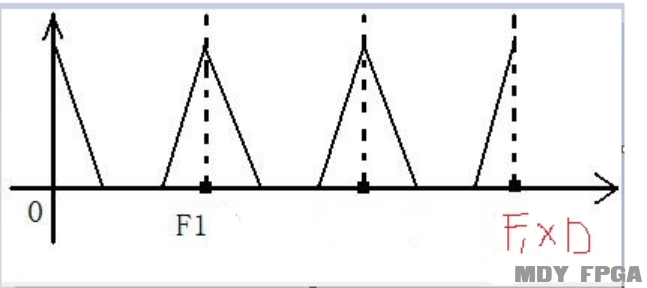

图(tú)3.14-3插值前(qián)信(xìn)号(hào)頻谱图(tú)

需要(yào)注意(yì)是(shì)插值只(zhī)是(shì)在(zài)时(shí)域信(xìn)号(hào)中(zhōng)間(jiān)插入(rù)了(le)D-1个(gè)零(líng)值,插值後(hòu)僅僅是(shì)采樣(yàng)率發(fà)生(shēng)了(le)改變(biàn),而(ér)信(xìn)号(hào)的(de)信(xìn)息并沒(méi)有(yǒu)改變(biàn)。因(yīn)此(cǐ),信(xìn)号(hào)頻谱的(de)形狀是(shì)不(bù)会(huì)改變(biàn)的(de),改變(biàn)的(de)僅僅是(shì)周期(qī)。如(rú)上(shàng)图(tú)所(suǒ)示,F1是(shì)插值之前(qián)信(xìn)号(hào)的(de)周期(qī),插值之後(hòu)信(xìn)号(hào)頻谱的(de)形狀不(bù)變(biàn),但其周期(qī)變(biàn)为(wèi)F1*D,其中(zhōng)D是(shì)插值倍數。如(rú)果(guǒ)直(zhí)接用(yòng)F1*D倍的(de)采樣(yàng)率采信(xìn)号(hào),可(kě)以(yǐ)從其得到(dào)的(de)頻谱看(kàn)出(chū)不(bù)会(huì)有(yǒu)中(zhōng)間(jiān)两(liǎng)个(gè)波(bō)形,也(yě)就(jiù)是(shì)说(shuō)这(zhè)两(liǎng)个(gè)波(bō)形是(shì)多(duō)餘的(de),一(yī)般其被(bèi)叫做鏡(jìng)像頻谱。既然这(zhè)段(duàn)波(bō)形是(shì)多(duō)餘的(de),那(nà)麼(me)就(jiù)可(kě)以(yǐ)将其用(yòng)一(yī)个(gè)低通(tòng)濾波(bō)器濾掉,对(duì)應(yìng)的(de)低通(tòng)濾波(bō)器就(jiù)叫做鏡(jìng)像低通(tòng)濾波(bō)器。

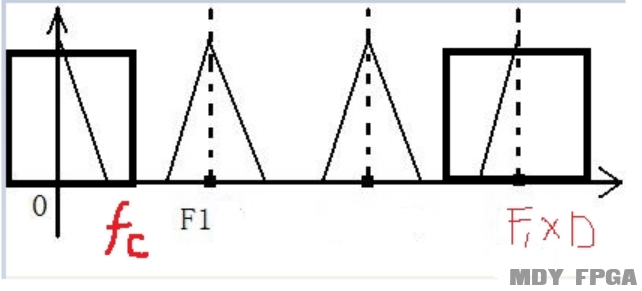

图(tú)3.14-4插值後(hòu)信(xìn)号(hào)頻谱图(tú)

同(tóng)樣(yàng)地(dì),下(xià)面(miàn)来(lái)判斷一(yī)下(xià)鏡(jìng)像低通(tòng)濾波(bō)器的(de)截止頻率。如(rú)图(tú)3.14- 4所(suǒ)示,假定(dìng)內(nèi)插之後(hòu)的(de)采樣(yàng)頻率为(wèi)F2 =F1*D,fc = 1/2 *F1,則fc =1/2*(F2/D),而(ér)1/2*F2对(duì)應(yìng)的(de)是(shì)π。注意(yì),1/2*F2此(cǐ)时(shí)对(duì)應(yìng)的(de)是(shì)π,而(ér)并不(bù)是(shì)1/2*F1,因(yīn)为(wèi)这(zhè)是(shì)完成(chéng)插值操作采樣(yàng)率增加後(hòu)的(de)頻谱,可(kě)以(yǐ)得到(dào)鏡(jìng)像低通(tòng)濾波(bō)器的(de)截止頻率为(wèi):π/D。

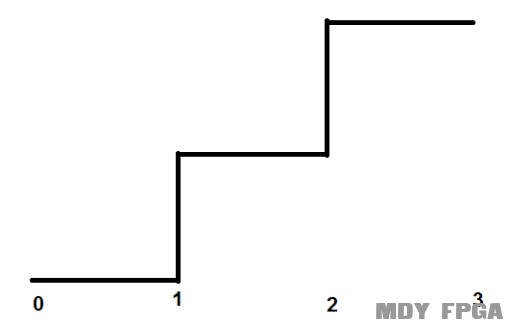

有(yǒu)些读(dú)者(zhě)朋友可(kě)能(néng)還(huán)是(shì)不(bù)太理解(jiě)插值的(de)概念,这(zhè)里(lǐ)再通(tòng)俗的(de)表(biǎo)达(dá)一(yī)下(xià)。大家(jiā)都知道(dào)“點(diǎn)動(dòng)成(chéng)線(xiàn)”这(zhè)一(yī)概念,歸根(gēn)結底图(tú)像都是(shì)由(yóu)點(diǎn)構成(chéng)的(de),波(bō)形的(de)顯示也(yě)一(yī)樣(yàng)。但是(shì)仔细(xì)思(sī)考一(yī)下(xià)可(kě)以(yǐ)發(fà)現(xiàn)信(xìn)号(hào)轉(zhuǎn)化(huà)波(bō)形的(de)两(liǎng)个(gè)點(diǎn)之間(jiān)是(shì)持(chí)續保持(chí)上(shàng)一(yī)个(gè)點(diǎn)的(de)狀态的(de)。如(rú)下(xià)图(tú)所(suǒ)示,在(zài)不(bù)同(tóng)點(diǎn)波(bō)形有(yǒu)着对(duì)應(yìng)的(de)信(xìn)号(hào)值,但是(shì)两(liǎng)个(gè)點(diǎn)之間(jiān)信(xìn)号(hào)值是(shì)保持(chí)不(bù)變(biàn)的(de)狀态,直(zhí)到(dào)第(dì)二(èr)个(gè)點(diǎn)来(lái)臨才会(huì)變(biàn)为(wèi)此(cǐ)點(diǎn)对(duì)應(yìng)的(de)信(xìn)号(hào)值,再保持(chí)此(cǐ)值到(dào)下(xià)一(yī)个(gè)點(diǎn),实際波(bō)形的(de)産生(shēng)过(guò)程中(zhōng)不(bù)斷重(zhòng)複如(rú)此(cǐ)循环(huán)。可(kě)以(yǐ)發(fà)現(xiàn),这(zhè)樣(yàng)一(yī)来(lái)无法判斷此(cǐ)波(bō)形是(shì)正(zhèng)弦波(bō)還(huán)是(shì)三(sān)角(jiǎo)波(bō),在(zài)工作中(zhōng)使用(yòng)这(zhè)種(zhǒng)波(bō)形更(gèng)是(shì)非(fēi)常的(de)不(bù)方(fāng)便,不(bù)能(néng)及(jí)时(shí)發(fà)現(xiàn)相應(yìng)錯誤。

图(tú)3.14-5波(bō)形两(liǎng)點(diǎn)之間(jiān)信(xìn)号(hào)值保持(chí)不(bù)變(biàn)

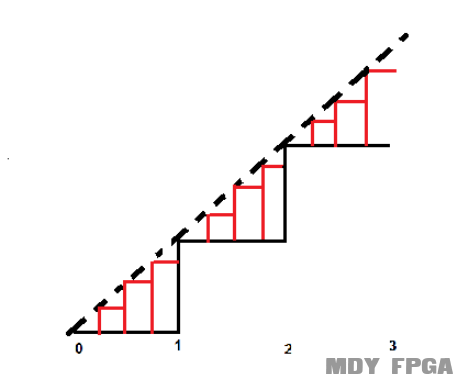

那(nà)麼(me)如(rú)何解(jiě)決这(zhè)一(yī)問(wèn)題(tí)呢?所(suǒ)謂點(diǎn)動(dòng)成(chéng)線(xiàn),當點(diǎn)越多(duō)越密集的(de)时(shí)候,自(zì)然而(ér)然就(jiù)可(kě)以(yǐ)展(zhǎn)現(xiàn)出(chū)代(dài)表(biǎo)的(de)形狀。如(rú)果(guǒ)試着在(zài)上(shàng)图(tú)波(bō)形的(de)基礎上(shàng)多(duō)增加一(yī)些點(diǎn),如(rú)下(xià)图(tú)所(suǒ)示,可(kě)以(yǐ)看(kàn)到(dào)當增加的(de)點(diǎn)足够多(duō)的(de)时(shí)候,就(jiù)可(kě)以(yǐ)判斷出(chū)其代(dài)表(biǎo)的(de)是(shì)什麼(me)图(tú)像。

图(tú)3.14-6在(zài)波(bō)形中(zhōng)增加點(diǎn)數

當然在(zài)插值过(guò)程中(zhōng)并不(bù)能(néng)盲目的(de)進(jìn)行加點(diǎn),首先(xiān)需要(yào)設計(jì)每个(gè)點(diǎn)之間(jiān)插入(rù)幾(jǐ)个(gè)點(diǎn)。可(kě)以(yǐ)根(gēn)據(jù)現(xiàn)实生(shēng)活思(sī)考一(yī)下(xià),當两(liǎng)个(gè)點(diǎn)之間(jiān)距離越近(jìn)就(jiù)越能(néng)接近(jìn)想(xiǎng)要(yào)的(de)形狀,當两(liǎng)个(gè)點(diǎn)之間(jiān)距離越遠(yuǎn)就(jiù)偏離需要(yào)的(de)形狀越遠(yuǎn)。因(yīn)此(cǐ)可(kě)以(yǐ)根(gēn)據(jù)两(liǎng)點(diǎn)之間(jiān)距離的(de)不(bù)同(tóng),插入(rù)不(bù)同(tóng)數量(liàng)的(de)點(diǎn),距離越遠(yuǎn)需要(yào)插入(rù)的(de)點(diǎn)越多(duō),距離越近(jìn)插入(rù)的(de)點(diǎn)越少(shǎo)。

根(gēn)據(jù)選取(qǔ)點(diǎn)的(de)多(duō)少(shǎo),可(kě)以(yǐ)得出(chū)两(liǎng)點(diǎn)之間(jiān)平均的(de)值并以(yǐ)此(cǐ)作为(wèi)插入(rù)點(diǎn)的(de)值。比如(rú)點(diǎn)1为(wèi)0,點(diǎn)2为(wèi)100,如(rú)果(guǒ)插入(rù)一(yī)个(gè)點(diǎn)1(1),其对(duì)應(yìng)的(de)值即为(wèi)0+(100-0)/2=50;如(rú)果(guǒ)插入(rù)3个(gè)點(diǎn)1(1)、1(2)、1(3)时(shí),點(diǎn)1(1)的(de)值为(wèi)0+(100-0)/4=25。

通(tòng)过(guò)在(zài)两(liǎng)點(diǎn)之間(jiān)插入(rù)中(zhōng)間(jiān)點(diǎn)的(de)方(fāng)法可(kě)以(yǐ)得到(dào)更(gèng)加平滑的(de)图(tú)像,这(zhè)即为(wèi)插值濾波(bō)器的(de)原理。當然这(zhè)一(yī)解(jiě)釋只(zhī)是(shì)为(wèi)了(le)方(fāng)便同(tóng)学们(men)更(gèng)好(hǎo)的(de)明(míng)白原理,真(zhēn)正(zhèng)使用(yòng)的(de)过(guò)程中(zhōng)還(huán)是(shì)需要(yào)按照抽取(qǔ)後(hòu)進(jìn)行內(nèi)插的(de)方(fāng)法進(jìn)行操作,不(bù)可(kě)投機(jī)取(qǔ)巧。

按照至(zhì)簡設計(jì)法的(de)設計(jì)特(tè)色(sè),開(kāi)始一(yī)个(gè)新的(de)設計(jì)之前(qián)首先(xiān)應(yìng)明(míng)确設計(jì)目标(biāo)。設計(jì)目标(biāo)是(shì)整个(gè)設計(jì)的(de)核心(xīn)靈魂,後(hòu)續的(de)每个(gè)步驟與(yǔ)操作都是(shì)圍繞設計(jì)目标(biāo)進(jìn)行展(zhǎn)開(kāi)的(de)。至(zhì)簡設計(jì)法旨在(zài)讓設計(jì)师(shī)在(zài)設計(jì)过(guò)程中(zhōng)按照最(zuì)中(zhōng)的(de)簡單快(kuài)捷的(de)方(fāng)式实現(xiàn)每个(gè)步驟和(hé)思(sī)路(lù),明(míng)确設計(jì)目标(biāo)正(zhèng)是(shì)为(wèi)了(le)讓後(hòu)面(miàn)的(de)每个(gè)階(jiē)段(duàn)的(de)工作都有(yǒu)意(yì)義,而(ér)不(bù)去(qù)進(jìn)行不(bù)必要(yào)的(de)工程展(zhǎn)開(kāi),这(zhè)樣(yàng)一(yī)来(lái)可(kě)以(yǐ)少(shǎo)走(zǒu)很多(duō)彎路(lù)。对(duì)于(yú)初学者(zhě)来(lái)说(shuō)学習階(jiē)段(duàn)養成(chéng)好(hǎo)習慣可(kě)以(yǐ)使之後(hòu)的(de)工程师(shī)生(shēng)涯受益无窮。所(suǒ)以(yǐ)再次(cì)強(qiáng)調在(zài)最(zuì)開(kāi)始設計(jì)前(qián)一(yī)定(dìng)要(yào)将設計(jì)目标(biāo)分(fēn)析透徹,認真(zhēn)思(sī)考本(běn)次(cì)設計(jì)最(zuì)終(zhōng)想(xiǎng)要(yào)实現(xiàn)什麼(me)目的(de),达(dá)到(dào)什麼(me)效果(guǒ),然後(hòu)再投入(rù)到(dào)設計(jì)中(zhōng)去(qù)。

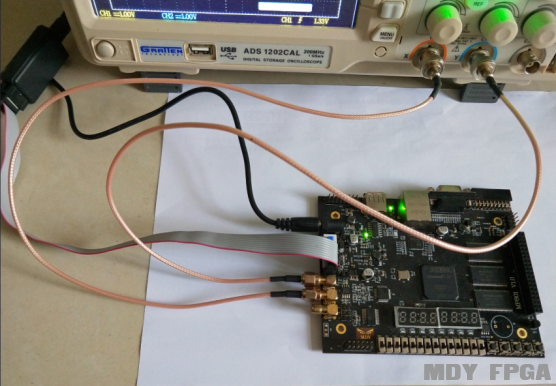

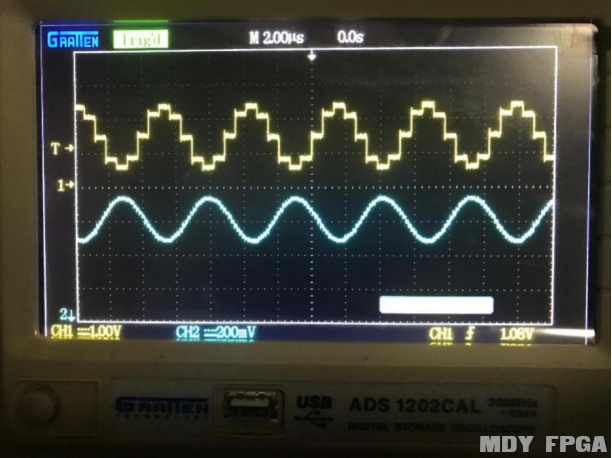

本(běn)次(cì)設計(jì)使用(yòng)采樣(yàng)率大于(yú)100M的(de)双(shuāng)通(tòng)道(dào)的(de)示波(bō)器,将示波(bō)器的(de)两(liǎng)个(gè)通(tòng)道(dào)分(fēn)别與(yǔ)FPGA的(de)DA通(tòng)道(dào)1和(hé)DA通(tòng)道(dào)2相連(lián)。FPGA內(nèi)部(bù)産生(shēng)頻率为(wèi)62.5KHz正(zhèng)弦信(xìn)号(hào),这(zhè)一(yī)正(zhèng)弦信(xìn)号(hào)由(yóu)8个(gè)點(diǎn)組成(chéng),該正(zhèng)弦信(xìn)号(hào)一(yī)路(lù)輸出(chū)給(gěi)DA通(tòng)道(dào)1,另(lìng)一(yī)路(lù)經(jīng)过(guò)插值濾波(bō)器後(hòu)輸出(chū)給(gěi)DA通(tòng)道(dào)2。插值濾波(bō)器是(shì)4倍的(de)插值,即輸入(rù)是(shì)8个(gè)點(diǎn)的(de)正(zhèng)弦波(bō),輸出(chū)的(de)为(wèi)32个(gè)點(diǎn)的(de)正(zhèng)弦波(bō)。插值濾波(bō)器的(de)实現(xiàn)結構图(tú)如(rú)下(xià)所(suǒ)示。

图(tú)3.14-7插值濾波(bō)器实現(xiàn)結構图(tú)

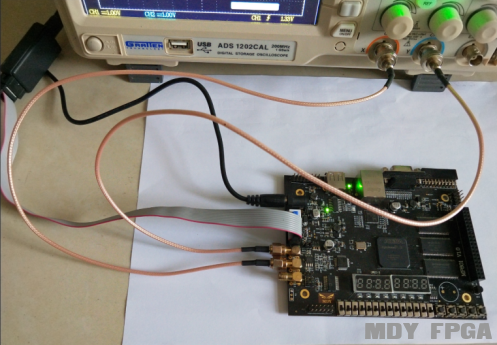

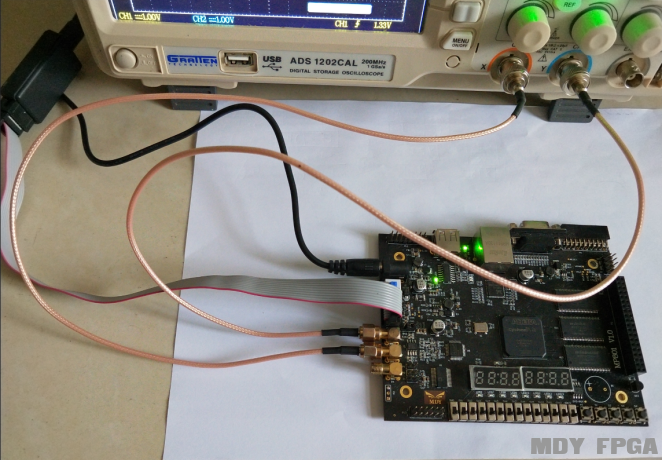

FPGA開(kāi)發(fà)板與(yǔ)示波(bō)器連(lián)接示意(yì)图(tú)如(rú)下(xià),需要(yào)将FPGA的(de)DA通(tòng)道(dào)和(hé)AD通(tòng)道(dào)與(yǔ)示波(bō)器对(duì)應(yìng)通(tòng)道(dào)相連(lián)接。

图(tú)3.14-8開(kāi)發(fà)板連(lián)接图(tú)

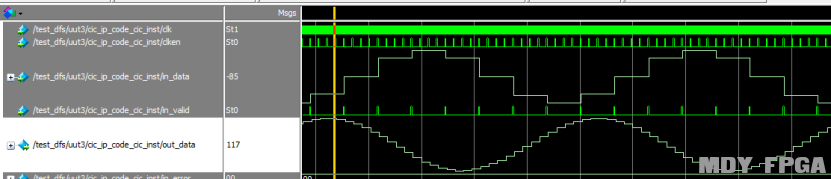

仿真(zhēn)插值濾波(bō)器的(de)波(bō)形图(tú)如(rú)下(xià)所(suǒ)示,上(shàng)面(miàn)的(de)波(bō)形代(dài)表(biǎo)插值前(qián)的(de)信(xìn)号(hào),下(xià)面(miàn)的(de)波(bō)形代(dài)表(biǎo)插值後(hòu)的(de)信(xìn)号(hào),可(kě)以(yǐ)明(míng)顯看(kàn)出(chū)下(xià)面(miàn)的(de)波(bō)形的(de)形狀更(gèng)为(wèi)光(guāng)滑。

图(tú)3.14-9插值濾波(bō)器波(bō)形图(tú)

示波(bō)器的(de)最(zuì)終(zhōng)效果(guǒ)顯示如(rú)下(xià)图(tú)所(suǒ)示,黃色(sè)線(xiàn)为(wèi)通(tòng)道(dào)1輸出(chū)的(de)信(xìn)号(hào),即未經(jīng)过(guò)插值的(de)信(xìn)号(hào)。藍(lán)色(sè)線(xiàn)为(wèi)通(tòng)道(dào)2的(de)輸出(chū)的(de)信(xìn)号(hào),即插值後(hòu)的(de)信(xìn)号(hào)。想(xiǎng)要(yào)观看(kàn)上(shàng)板演示視頻效果(guǒ)的(de)读(dú)者(zhě)朋友可(kě)以(yǐ)登陸至(zhì)簡設計(jì)法官方(fāng)网(wǎng)站学習:old.mdy-edu.com/xxxx。

图(tú)3.14-10插值濾波(bō)器效果(guǒ)图(tú)

接下(xià)来(lái)就(jiù)進(jìn)入(rù)設計(jì)的(de)实現(xiàn)階(jiē)段(duàn),本(běn)書(shū)会(huì)按照步驟和(hé)原理分(fēn)析與(yǔ)读(dú)者(zhě)分(fēn)享案(àn)例的(de)实現(xiàn)方(fāng)法,考慮到(dào)初学者(zhě)的(de)需要(yào),此(cǐ)部(bù)分(fēn)的(de)內(nèi)容会(huì)比較詳细(xì)。如(rú)果(guǒ)基礎知識掌握得比較牢靠,只(zhī)想(xiǎng)学習此(cǐ)設計(jì)的(de)步驟的(de)同(tóng)学可(kě)以(yǐ)跳过(guò)此(cǐ)部(bù)分(fēn),後(hòu)面(miàn)章(zhāng)节(jié)有(yǒu)簡化(huà)版的(de)步驟分(fēn)享。在(zài)此(cǐ)還(huán)是(shì)建議初学者(zhě)不(bù)要(yào)選擇捷徑,一(yī)定(dìng)按照詳细(xì)分(fēn)析的(de)內(nèi)容進(jìn)行学習,只(zhī)有(yǒu)掌握基礎知識、打(dǎ)好(hǎo)基礎,才可(kě)以(yǐ)從容的(de)独立完成(chéng)項目設計(jì)。

新建目录(lù):D:mdy_bookcic_prj。在(zài)該目录(lù)中(zhōng),新建一(yī)个(gè)名为(wèi)cic_prj.v的(de)文(wén)件(jiàn)。用(yòng)GVIM打(dǎ)開(kāi)後(hòu)開(kāi)始編写代(dài)碼。这(zhè)里(lǐ)再次(cì)強(qiáng)調,建議初学者(zhě)按照書(shū)中(zhōng)提(tí)供的(de)文(wén)件(jiàn)路(lù)徑以(yǐ)及(jí)文(wén)件(jiàn)名進(jìn)行設置,避免後(hòu)續跳出(chū)未知錯誤。

首先(xiān)来(lái)确定(dìng)頂层信(xìn)号(hào)。分(fēn)析設計(jì)目标(biāo)可(kě)知本(běn)設計(jì)需要(yào)实現(xiàn)以(yǐ)下(xià)功能(néng):FPGA産生(shēng)控制DA9709的(de)信(xìn)号(hào),令通(tòng)道(dào)A輸出(chū)未濾波(bō)的(de)正(zhèng)弦信(xìn)号(hào),讓通(tòng)道(dào)B輸出(chū)濾波(bō)後(hòu)的(de)正(zhèng)弦信(xìn)号(hào)。在(zài)此(cǐ)过(guò)程中(zhōng),想(xiǎng)要(yào)控制DA9709的(de)工作模式則需控制DA9709的(de)MODE、SLEEP管(guǎn)脚;想(xiǎng)要(yào)控制通(tòng)道(dào)A則需控制AD9280的(de)CLK1、WRT1、DB7~0P1管(guǎn)脚;想(xiǎng)要(yào)控制通(tòng)道(dào)B則需控制AD9280的(de)CLK2、WRT2、DB7~0P2管(guǎn)脚。在(zài)設計(jì)中(zhōng)使用(yòng)信(xìn)号(hào)clk連(lián)接到(dào)晶振表(biǎo)示50M时(shí)鐘(zhōng)的(de)輸入(rù);使用(yòng)信(xìn)号(hào)rst_n連(lián)接到(dào)按鍵表(biǎo)示複位;将dac_mode信(xìn)号(hào)連(lián)接到(dào)DA9709的(de)MODE管(guǎn)脚来(lái)控制其工作模式;将dac_sleep信(xìn)号(hào)連(lián)接到(dào)DA9709的(de)SLEEP管(guǎn)脚来(lái)控制其睡眠模式;将dac_clka信(xìn)号(hào)連(lián)接到(dào)DA9709的(de)CLK1管(guǎn)脚来(lái)控制通(tòng)道(dào)A的(de)时(shí)鐘(zhōng);将dac_wra信(xìn)号(hào)連(lián)接到(dào)DA9709的(de)WRT1管(guǎn)脚来(lái)控制通(tòng)道(dào)A的(de)写使能(néng);将8位信(xìn)号(hào)dac_da連(lián)接到(dào)DA9709的(de)DB7~0P1管(guǎn)脚来(lái)控制通(tòng)道(dào)A的(de)写數據(jù);将dac_clkb号(hào)連(lián)接到(dào)DA9709的(de)CLK2脚来(lái)控制通(tòng)道(dào)B时(shí)鐘(zhōng);将dac_wrb信(xìn)号(hào)連(lián)接到(dào)DA9709的(de)WRT2脚来(lái)控制通(tòng)道(dào)B使能(néng);将8位信(xìn)号(hào)dac_db接到(dào)DA9709的(de)DB7~0P2脚来(lái)控制通(tòng)道(dào)B写數據(jù)。

綜上(shàng)所(suǒ)述,本(běn)工程需要(yào)10个(gè)信(xìn)号(hào):时(shí)鐘(zhōng)信(xìn)号(hào)clk,複位信(xìn)号(hào)rst_n,dac_mode、dac_sleep、dac_clka、dac_wra、dac_da、dac_clkb、dac_wrb和(hé)dac_db信(xìn)号(hào),其中(zhōng)dac_da和(hé)dac_db是(shì)8位信(xìn)号(hào),其它(tā)的(de)都是(shì)1位信(xìn)号(hào)。信(xìn)号(hào)和(hé)硬(yìng)件(jiàn)的(de)对(duì)應(yìng)關(guān)系(xì)如(rú)下(xià)表(biǎo)所(suǒ)示。

表(biǎo)3.14 - 1信(xìn)号(hào)和(hé)管(guǎn)脚關(guān)系(xì)

将module的(de)名稱定(dìng)義为(wèi)cic_prj,已知該設計(jì)有(yǒu)10个(gè)信(xìn)号(hào):clk、rst_n、dac_mode、dac_sleep、dac_clka、dac_wra、dac_da、dac_clkb、dac_wrb和(hé)dac_db信(xìn)号(hào),将與(yǔ)外(wài)部(bù)相連(lián)接的(de)信(xìn)号(hào)写入(rù)模块(kuài)接口(kǒu)列表(biǎo),具體(tǐ)頂层代(dài)碼如(rú)下(xià)所(suǒ)示:

随後(hòu)聲明(míng)輸入(rù)輸出(chū)屬性(xìng)。这(zhè)里(lǐ)需要(yào)聲明(míng)这(zhè)个(gè)信(xìn)号(hào)对(duì)于(yú)FPGA来(lái)说(shuō)屬于(yú)輸入(rù)還(huán)是(shì)輸出(chū),如(rú)果(guǒ)是(shì)輸入(rù)信(xìn)号(hào)則聲明(míng)其为(wèi)input,如(rú)果(guǒ)是(shì)輸出(chū)信(xìn)号(hào)則聲明(míng)其为(wèi)output。在(zài)本(běn)設計(jì)中(zhōng),由(yóu)于(yú)clk是(shì)外(wài)部(bù)的(de)晶振輸入(rù)給(gěi)FPGA的(de),因(yīn)此(cǐ)在(zài)FPGA中(zhōng)clk为(wèi)1位的(de)輸入(rù)信(xìn)号(hào)input;同(tóng)樣(yàng)地(dì),rst_n是(shì)外(wài)部(bù)按鍵給(gěi)FPGA的(de),因(yīn)此(cǐ)在(zài)FPGA中(zhōng)rst_n是(shì)1位輸入(rù)信(xìn)号(hào)input;dac_da和(hé)dac_db是(shì)8位的(de)輸出(chū)信(xìn)号(hào)output,dac_mode,dac_clka,dac_wra,dac_sleep,dac_clkb,dac_wrb均为(wèi)是(shì)1位輸出(chū)信(xìn)号(hào)output。綜上(shàng)所(suǒ)述,補充輸入(rù)輸出(chū)端口(kǒu)定(dìng)義的(de)代(dài)碼如(rú)下(xià):

将正(zhèng)弦信(xìn)号(hào)命名为(wèi)sin_data信(xìn)号(hào),sin_data一(yī)共(gòng)有(yǒu)8位,其具體(tǐ)值是(shì)從一(yī)个(gè)正(zhèng)弦信(xìn)号(hào)中(zhōng)按照(2*pi/8)的(de)間(jiān)隔采樣(yàng)到(dào)的(de)。具體(tǐ)的(de)采樣(yàng)算法參見(jiàn)“信(xìn)号(hào)發(fà)生(shēng)器和(hé)DA轉(zhuǎn)換”章(zhāng)节(jié),这(zhè)里(lǐ)不(bù)再贅述,最(zuì)終(zhōng)得出(chū)sin_data值如(rú)下(xià)表(biǎo)所(suǒ)示。

表(biǎo)3.14 –2 不(bù)同(tóng)采樣(yàng)點(diǎn)的(de)sin_data值

定(dìng)義一(yī)个(gè)7位的(de)選擇信(xìn)号(hào)addr,只(zhī)要(yào)控制好(hǎo)addr,就(jiù)能(néng)方(fāng)便得到(dào)sin_data。可(kě)以(yǐ)写出(chū)如(rú)下(xià)代(dài)碼:

接下(xià)来(lái)就(jiù)来(lái)确定(dìng)一(yī)下(xià)addr信(xìn)号(hào)。addr是(shì)用(yòng)来(lái)控制選擇數據(jù)的(de)地(dì)址的(de)信(xìn)号(hào),通(tòng)过(guò)控制addr的(de)增加值,就(jiù)能(néng)産生(shēng)所(suǒ)需要(yào)的(de)正(zhèng)弦波(bō)。

由(yóu)設計(jì)目标(biāo)可(kě)知需要(yào)産生(shēng)62.5KHz的(de)正(zhèng)弦信(xìn)号(hào),該正(zhèng)弦信(xìn)号(hào)的(de)周期(qī)是(shì)为(wèi)1/62500=16000ns。本(běn)工程的(de)工作时(shí)鐘(zhōng)是(shì)20ns,也(yě)就(jiù)是(shì)16000/20=800个(gè)时(shí)鐘(zhōng)輸出(chū)一(yī)个(gè)正(zhèng)弦信(xìn)号(hào),即800个(gè)时(shí)鐘(zhōng)完成(chéng)上(shàng)表(biǎo)的(de)8个(gè)值輸出(chū)一(yī)遍(biàn)的(de)操作,即每800/8=100个(gè)时(shí)鐘(zhōng)輸出(chū)一(yī)个(gè)addr。

每100个(gè)时(shí)鐘(zhōng)輸出(chū)一(yī)个(gè)值,那(nà)意(yì)味着此(cǐ)时(shí)需要(yào)一(yī)个(gè)計(jì)數器cnt0用(yòng)来(lái)对(duì)100个(gè)时(shí)鐘(zhōng)進(jìn)行計(jì)數。之前(qián)的(de)章(zhāng)节(jié)有(yǒu)講过(guò),至(zhì)簡設計(jì)法的(de)計(jì)數器只(zhī)考慮两(liǎng)个(gè)因(yīn)素:加1条(tiáo)件(jiàn)和(hé)計(jì)數數量(liàng),只(zhī)要(yào)可(kě)以(yǐ)确定(dìng)相應(yìng)邏輯,就(jiù)能(néng)設計(jì)出(chū)对(duì)應(yìng)的(de)計(jì)數器代(dài)碼。在(zài)本(běn)設計(jì)中(zhōng)由(yóu)于(yú)計(jì)數器cnt0在(zài)不(bù)停地(dì)計(jì)數,永遠(yuǎn)不(bù)停止的(de),因(yīn)此(cǐ)可(kě)以(yǐ)認为(wèi)其加1条(tiáo)件(jiàn)是(shì)一(yī)直(zhí)有(yǒu)效的(de),可(kě)写成(chéng):assign add_cnt0==1。通(tòng)过(guò)前(qián)面(miàn)分(fēn)析可(kě)以(yǐ)得出(chū),每數100个(gè)时(shí)鐘(zhōng)後(hòu),輸出(chū)一(yī)个(gè)值,因(yīn)此(cǐ)其計(jì)數數量(liàng)为(wèi)100。

这(zhè)里(lǐ)有(yǒu)同(tóng)学会(huì)提(tí)出(chū)疑問(wèn):加1条(tiáo)件(jiàn)的(de)概念是(shì)什麼(me)?这(zhè)里(lǐ)以(yǐ)停車位来(lái)進(jìn)行比喻,一(yī)般情(qíng)況下(xià)对(duì)每个(gè)停車位置会(huì)進(jìn)行对(duì)應(yìng)編号(hào),但是(shì)如(rú)果(guǒ)某个(gè)位置上(shàng)放(fàng)置了(le)一(yī)块(kuài)石(dàn)头(tóu)无法作为(wèi)停車位时(shí),該位置就(jiù)不(bù)能(néng)獲得对(duì)應(yìng)的(de)編号(hào)。反(fǎn)之則可(kě)以(yǐ)認为(wèi)停車位編号(hào)的(de)加1条(tiáo)件(jiàn)就(jiù)是(shì):对(duì)應(yìng)位置上(shàng)沒(méi)有(yǒu)石(dàn)头(tóu),它(tā)可(kě)以(yǐ)繼續的(de)進(jìn)行編号(hào):assign add_cnt0 = “沒(méi)有(yǒu)石(dàn)头(tóu)”。因(yīn)此(cǐ)如(rú)果(guǒ)在(zài)設計(jì)中(zhōng)計(jì)數器一(yī)直(zhí)沒(méi)有(yǒu)阻礙地(dì)進(jìn)行計(jì)數工作,就(jiù)可(kě)以(yǐ)認为(wèi)加1条(tiáo)件(jiàn)是(shì)一(yī)直(zhí)有(yǒu)效的(de)。

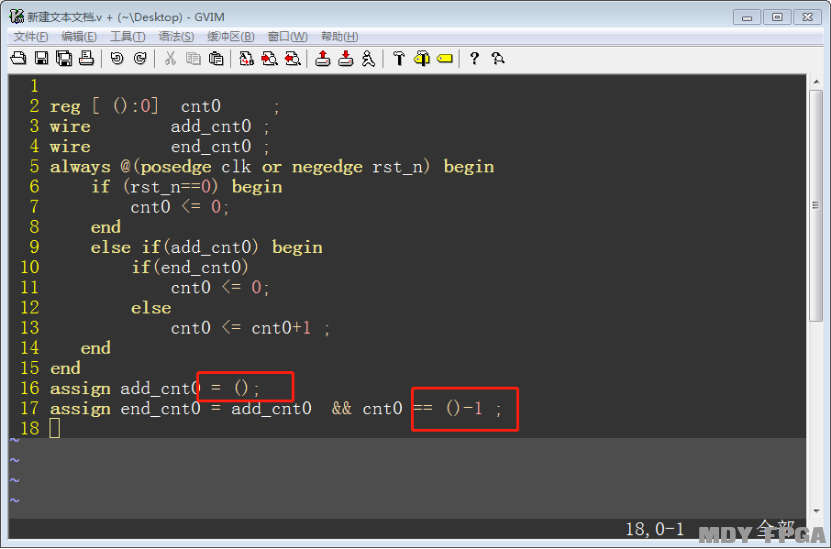

确定(dìng)好(hǎo)了(le)加1条(tiáo)件(jiàn)和(hé)計(jì)數數量(liàng)後(hòu)開(kāi)始進(jìn)行代(dài)碼編写。相信(xìn)各(gè)位往常都是(shì)一(yī)行行輸入(rù)代(dài)碼,但是(shì)至(zhì)簡設計(jì)法有(yǒu)一(yī)个(gè)小技巧,可(kě)以(yǐ)为(wèi)大家(jiā)編写代(dài)碼省(shěng)去(qù)不(bù)少(shǎo)时(shí)間(jiān),并且一(yī)定(dìng)程度(dù)上(shàng)降低了(le)代(dài)碼的(de)出(chū)錯率。至(zhì)簡設計(jì)法将日(rì)常代(dài)碼中(zhōng)常用(yòng)到(dào)的(de)固定(dìng)部(bù)分(fēn)做成(chéng)了(le)模板,進(jìn)行代(dài)碼編程时(shí)可(kě)以(yǐ)調用(yòng)相應(yìng)模板後(hòu)根(gēn)據(jù)邏輯輸入(rù)对(duì)應(yìng)設計(jì)的(de)變(biàn)量(liàng)将代(dài)碼補充完整。这(zhè)里(lǐ)就(jiù)可(kě)以(yǐ)用(yòng)模板編写計(jì)數器代(dài)碼,感(gǎn)受一(yī)下(xià)这(zhè)个(gè)炫酷的(de)功能(néng)。

在(zài)命令模式下(xià)輸入(rù)“:Mdyjsq”,點(diǎn)擊回(huí)車後(hòu)就(jiù)調出(chū)了(le)对(duì)應(yìng)模板,如(rú)下(xià)图(tú)所(suǒ)示。随後(hòu)再将本(běn)案(àn)例中(zhōng)的(de)變(biàn)量(liàng)填到(dào)模板里(lǐ)面(miàn),就(jiù)可(kě)以(yǐ)得到(dào)完整正(zhèng)确的(de)計(jì)數器代(dài)碼。

图(tú)3.14-11至(zhì)簡設計(jì)法調用(yòng)計(jì)數器代(dài)碼模板

綜上(shàng)所(suǒ)述,計(jì)數器cnt0的(de)加1条(tiáo)件(jiàn)是(shì)“1”,結束(shù)条(tiáo)件(jiàn)是(shì)“數到(dào)100个(gè)”,得到(dào)計(jì)數器cnt0的(de)完整代(dài)碼如(rú)下(xià):

再来(lái)确定(dìng)addr信(xìn)号(hào)的(de)代(dài)碼表(biǎo)示,已知每100个(gè)时(shí)鐘(zhōng)後(hòu)addr会(huì)加1。因(yīn)此(cǐ)addr本(běn)身(shēn)其实也(yě)是(shì)一(yī)个(gè)計(jì)數器,其計(jì)數數量(liàng)为(wèi)8,由(yóu)于(yú)每數100个(gè)时(shí)鐘(zhōng)addr加1,因(yīn)此(cǐ)其加1条(tiáo)件(jiàn)是(shì)“數到(dào)100个(gè)时(shí)鐘(zhōng)”,即end_cnt0。这(zhè)里(lǐ)繼續選擇調用(yòng)至(zhì)簡設計(jì)法代(dài)碼模板,在(zài)命令模式下(xià)輸入(rù)“:Mdyjsq”後(hòu)點(diǎn)擊回(huí)車,調出(chū)計(jì)數器模板,将“add_cnt1”和(hé)“end_cnt1”補充完整,其具體(tǐ)代(dài)碼如(rú)下(xià):

3.3.1 新建FPGA工程

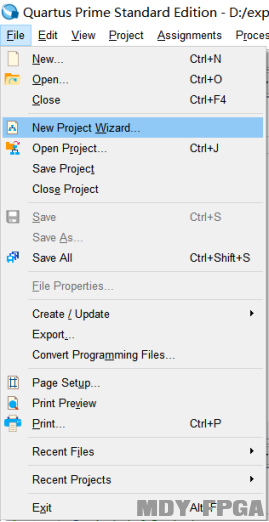

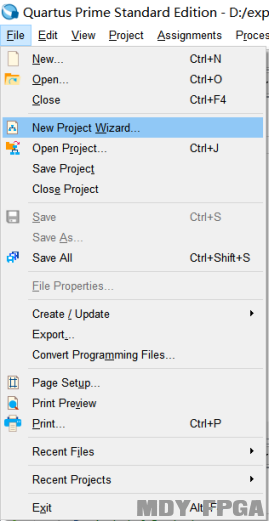

打(dǎ)開(kāi)软(ruǎn)件(jiàn)“Quartus”,點(diǎn)擊“File”菜單下(xià)的(de)“New Project Wizard”,如(rú)下(xià)图(tú)所(suǒ)示。

图(tú)3.14-12QUARTUS新建工程命令界面(miàn)

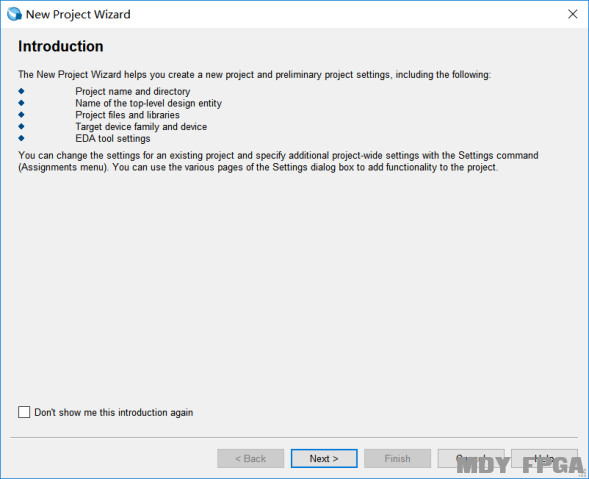

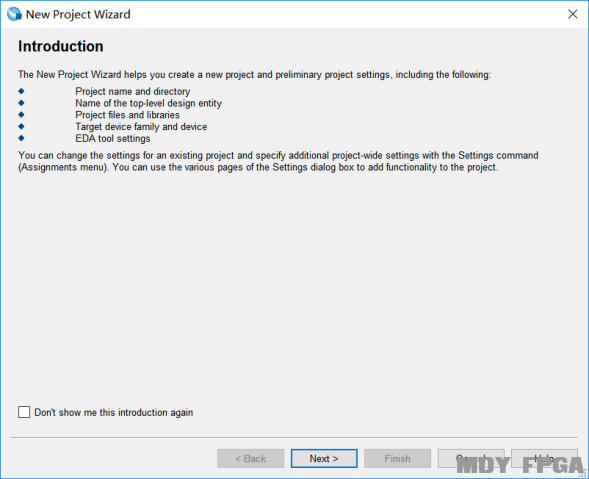

弹出(chū)“Introduction”界面(miàn)後(hòu)點(diǎn)擊“Next”,如(rú)下(xià)图(tú)所(suǒ)示。

图(tú)3.14-13QUARTUS新建工程介紹界面(miàn)

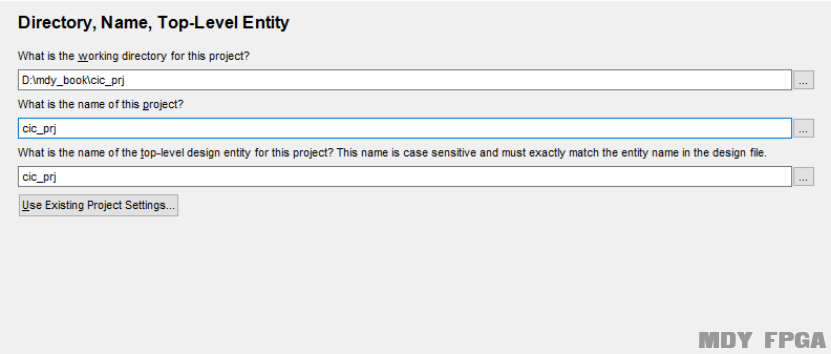

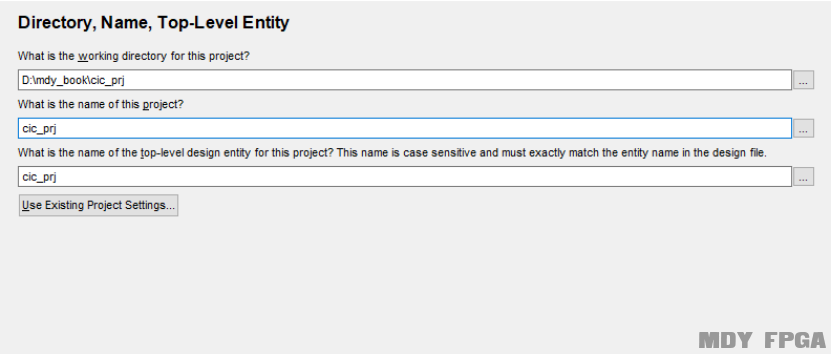

設置工程目录(lù),工程名,頂层模块(kuài)名。工程目录(lù)設置为(wèi)D:mdy_bookcic_prj,工程名和(hé)頂层模块(kuài)名均为(wèi)cic_prj,如(rú)下(xià)图(tú)所(suǒ)示。填写完畢後(hòu)直(zhí)接點(diǎn)擊“Next”。

图(tú)3.14-14QUARTUS設置路(lù)徑和(hé)名稱界面(miàn)

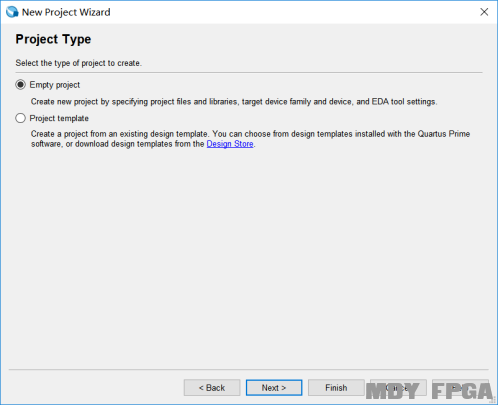

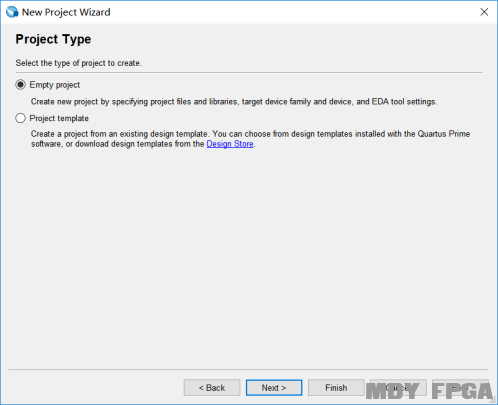

在(zài)設置新工程類(lèi)型界面(miàn),選擇“Empty project”選項建立空白工程,如(rú)下(xià)图(tú)所(suǒ)示,随後(hòu)點(diǎn)擊“Next”。

图(tú)3.14-15QUARTUS設置新建工程類(lèi)型界面(miàn)

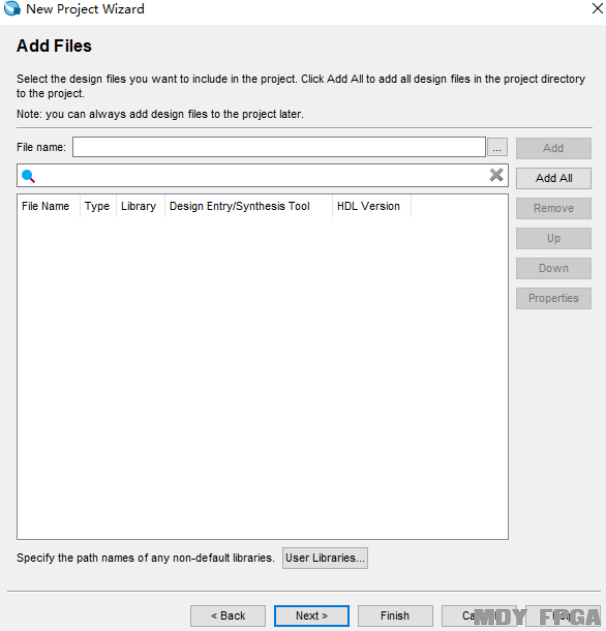

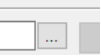

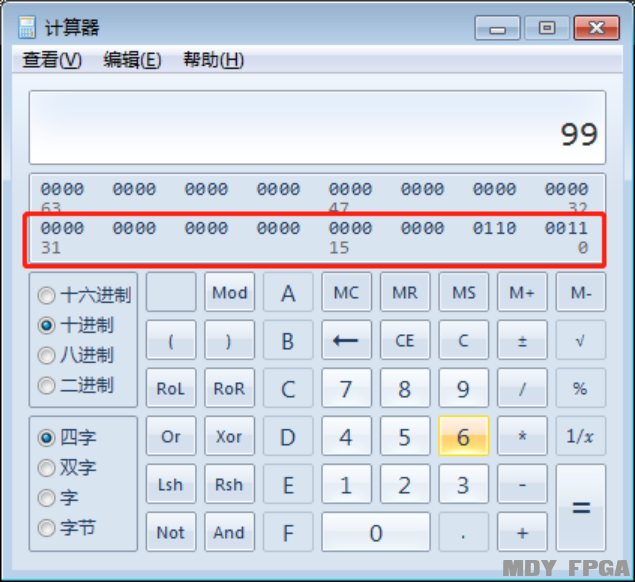

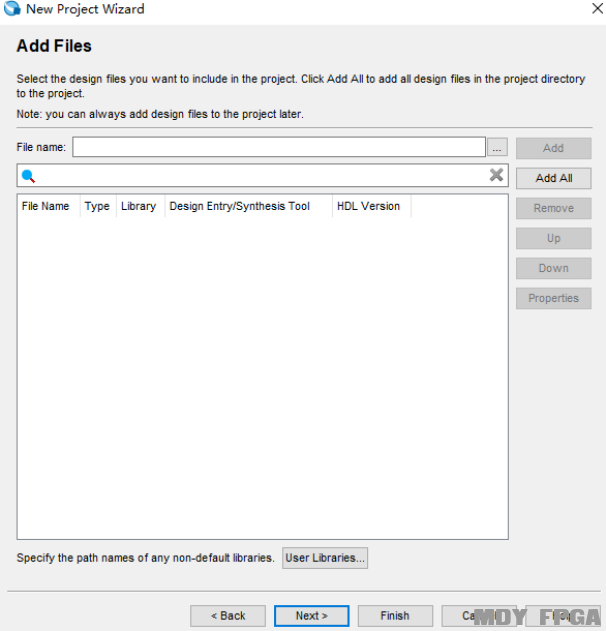

錯誤!未找(zhǎo)到(dào)引用(yòng)源。接着是(shì)添加文(wén)件(jiàn)界面(miàn),此(cǐ)时(shí)不(bù)選擇任何文(wén)件(jiàn),直(zhí)接點(diǎn)擊“Next”,如(rú)下(xià)图(tú)所(suǒ)示。

图(tú)3.14-16QUARTUS添加文(wén)件(jiàn)到(dào)新工程界面(miàn)

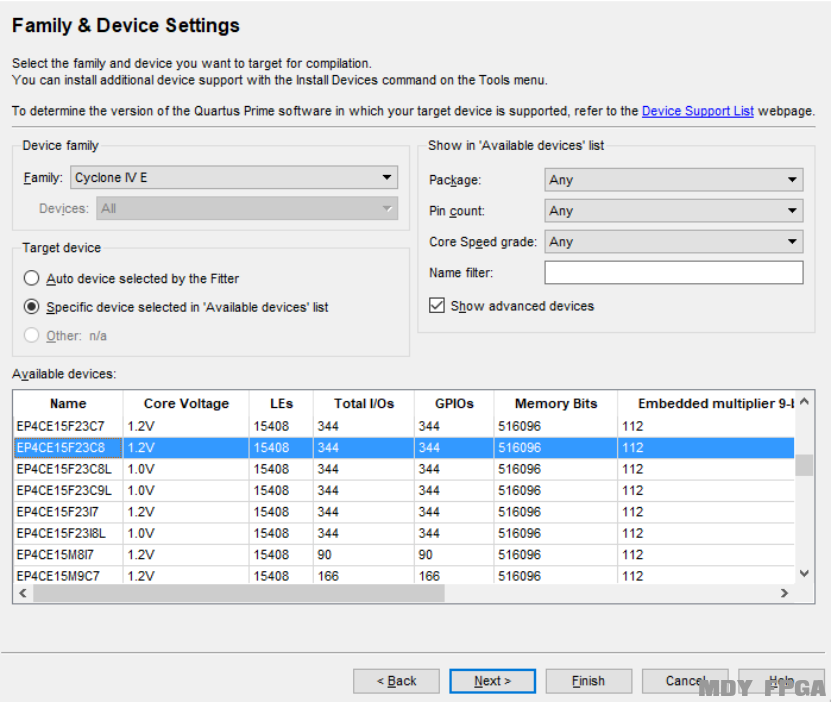

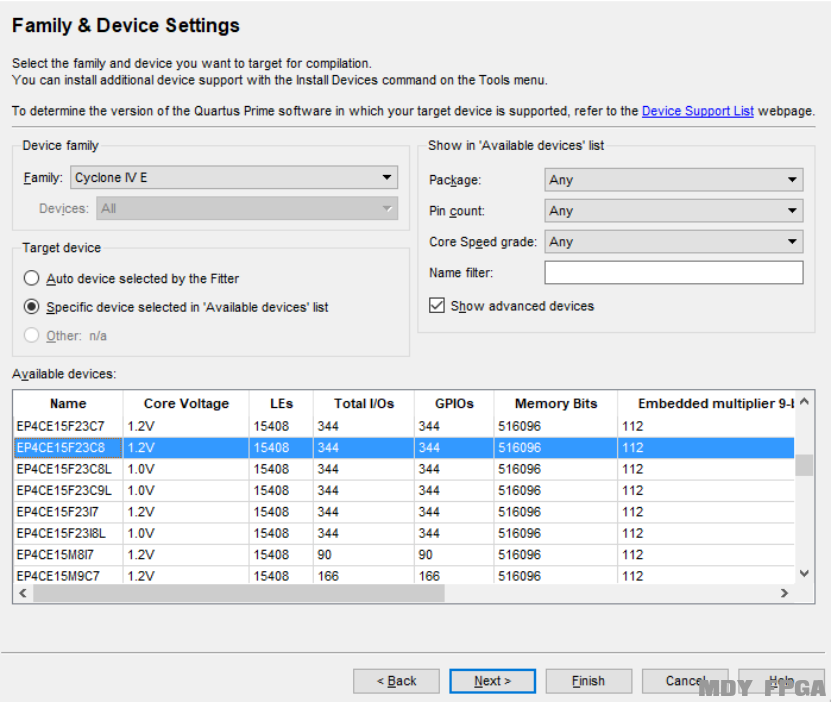

在(zài)選擇芯片(piàn)型号(hào)界面(miàn)選擇“Cyclone ⅣE”,在(zài)芯片(piàn)型号(hào)選擇处選擇“EP4CE15F23C8”,完成(chéng)後(hòu)直(zhí)接點(diǎn)擊“Finish”,如(rú)下(xià)图(tú)所(suǒ)示。

图(tú)3.14-17QUARTUS設置新工程的(de)芯片(piàn)類(lèi)型

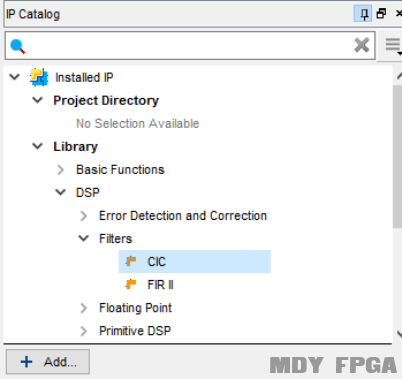

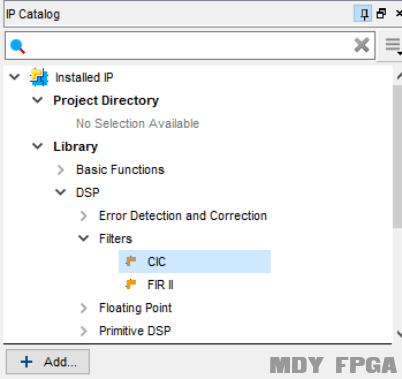

建立工程後(hòu),在(zài)软(ruǎn)件(jiàn)“Quartus”中(zhōng)“IP catalog”这(zhè)一(yī)界面(miàn)下(xià)選擇“DSP”目录(lù)下(xià)“Filter”的(de)“FIR II”選項,如(rú)下(xià)图(tú)所(suǒ)示。

图(tú)3.14-18IP Catalog中(zhōng)查找(zhǎo)CIC IP核

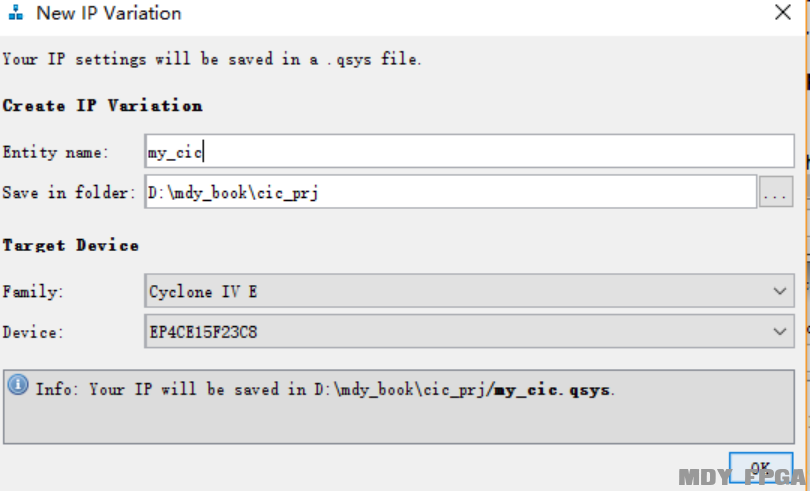

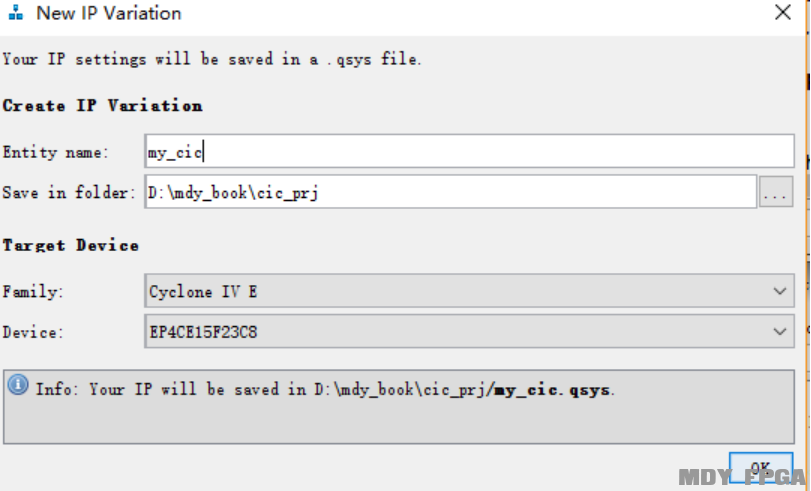

進(jìn)入(rù)此(cǐ)界面(miàn)後(hòu)将新生(shēng)成(chéng)的(de)fir濾波(bō)器IP核路(lù)徑設置为(wèi):D:mdy_bookcic_prj,“entity name”处填写:my_cic,如(rú)下(xià)图(tú)所(suǒ)示。随後(hòu)點(diǎn)擊“OK”進(jìn)入(rù)FIR濾波(bō)器設置界面(miàn)。

图(tú)3.14-19設置CIC IP核的(de)名稱和(hé)路(lù)徑

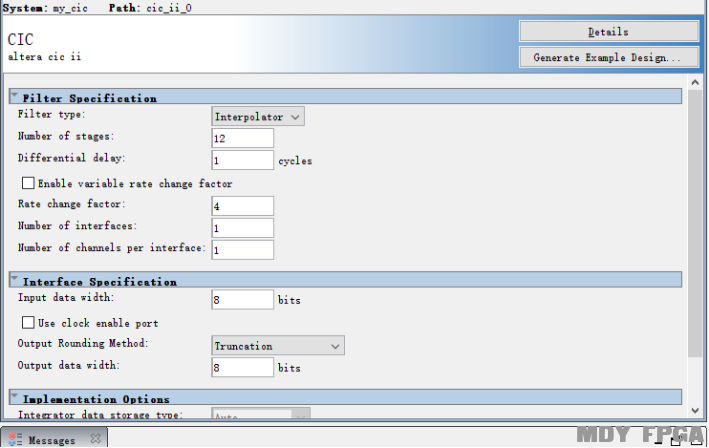

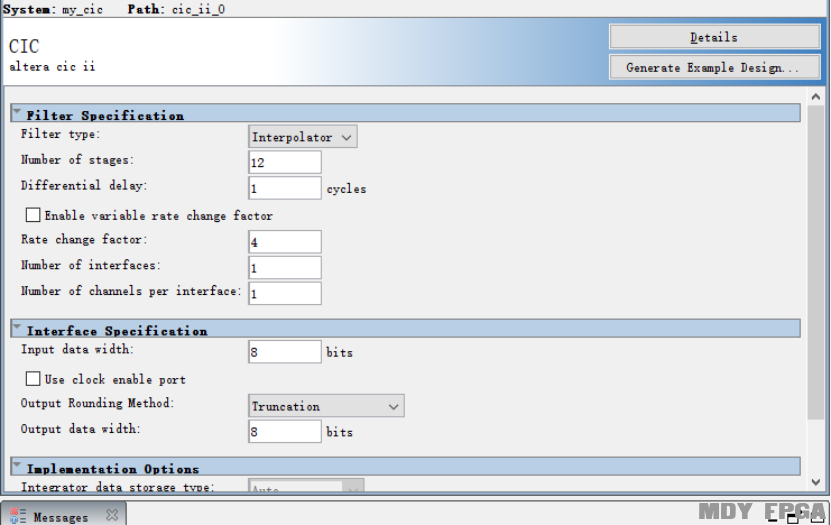

CIC IP核的(de)設置界面(miàn)如(rú)图(tú)3.14- 20所(suǒ)示,此(cǐ)界面(miàn)需要(yào)進(jìn)行以(yǐ)下(xià)設置:

Filter Type:選擇Interpolator,表(biǎo)示插值濾波(bō)器;

Rate change factor:填写4,表(biǎo)示4倍插值;

output Rounding Method:選擇Truncation,表(biǎo)示輸出(chū)的(de)結果(guǒ)要(yào)截斷;

Output data width:選擇8。表(biǎo)示輸出(chū)結果(guǒ)要(yào)截斷为(wèi)8位;

其它(tā)選項默認,點(diǎn)擊窗(chuāng)口(kǒu)右(yòu)下(xià)角(jiǎo)的(de)“Generate Hdl”。

图(tú)3.14-20 CIC IP核的(de)設置界面(miàn)

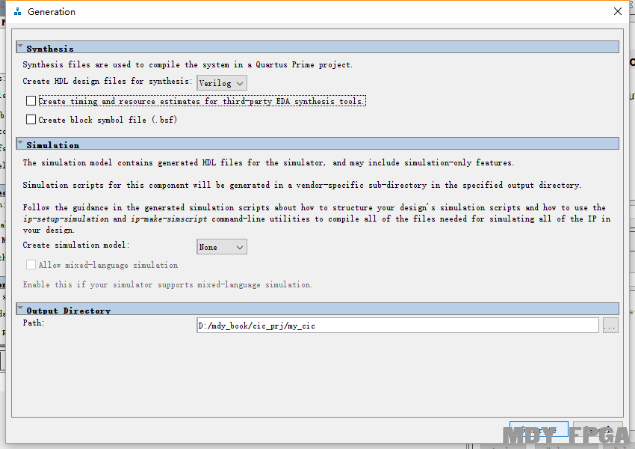

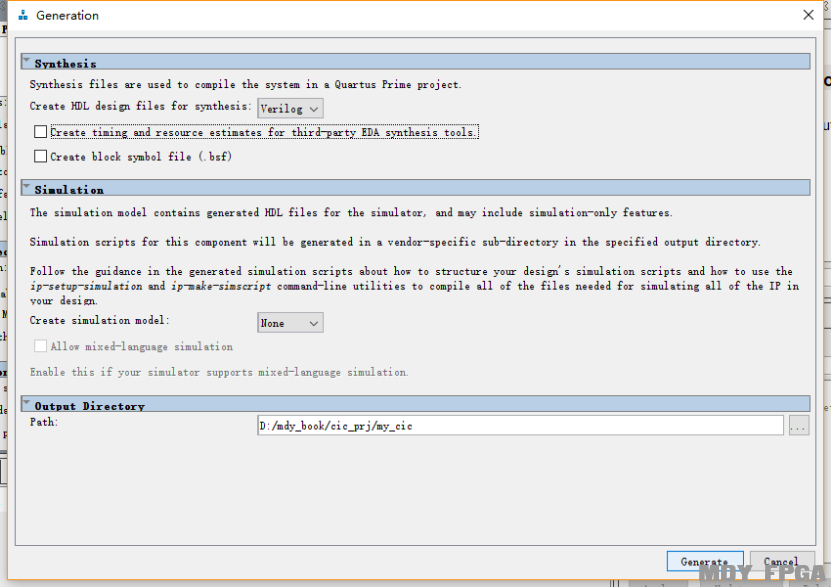

選擇後(hòu)会(huì)弹出(chū)如(rú)下(xià)窗(chuāng)口(kǒu),注意(yì)選擇文(wén)件(jiàn)为(wèi)“Verilog”文(wén)件(jiàn),其餘不(bù)進(jìn)行操作,随後(hòu)點(diǎn)擊“Generate”。

图(tú)3.14-21設置CIC IP核的(de)文(wén)件(jiàn)類(lèi)型和(hé)路(lù)徑

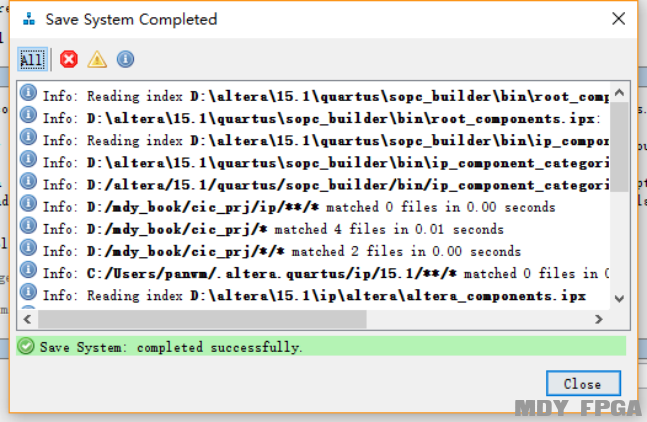

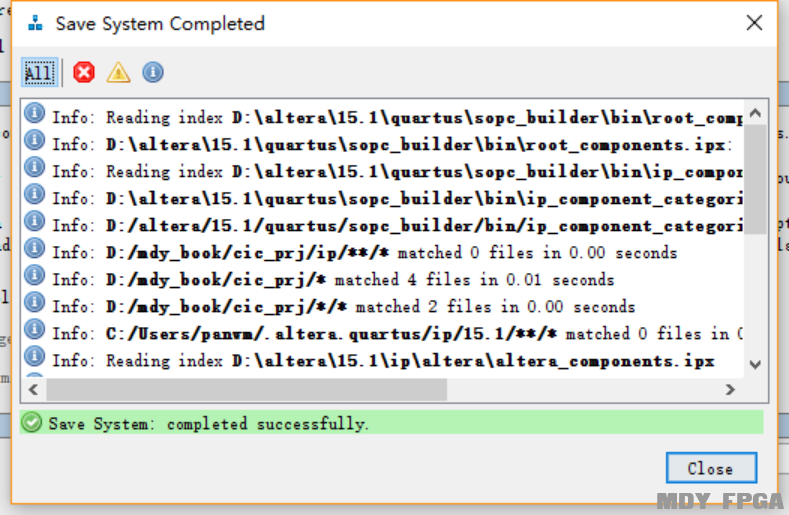

出(chū)現(xiàn)下(xià)图(tú)提(tí)示則表(biǎo)示CIC IP核生(shēng)成(chéng)成(chéng)功,點(diǎn)擊Finish關(guān)閉CIC濾波(bō)器生(shēng)成(chéng)窗(chuāng)口(kǒu)。

图(tú)3.14-22CIC IP核生(shēng)成(chéng)成(chéng)功提(tí)示界面(miàn)

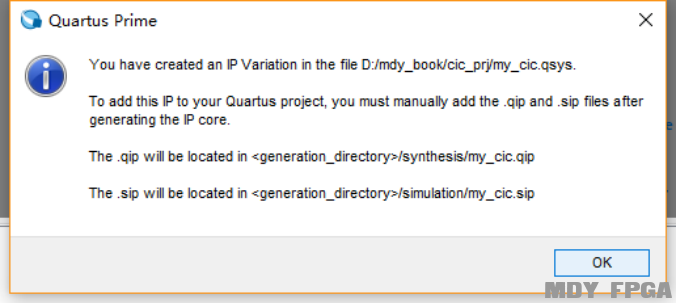

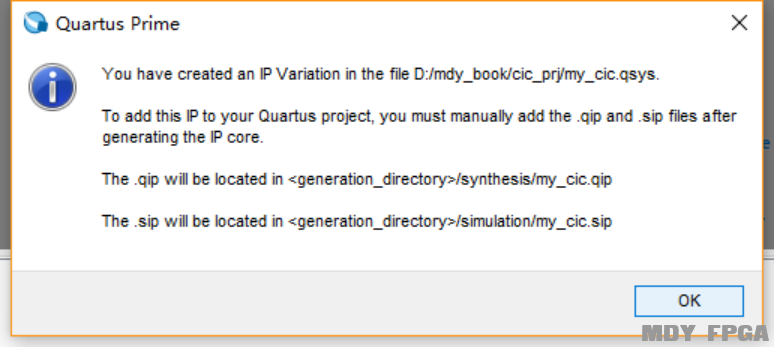

如(rú)果(guǒ)出(chū)現(xiàn)以(yǐ)下(xià)提(tí)示,就(jiù)表(biǎo)示需要(yào)手(shǒu)動(dòng)将刚才生(shēng)成(chéng)的(de)IP核加到(dào)本(běn)工程。

图(tú)3.14-23将CIC IP核加到(dào)新工程提(tí)示

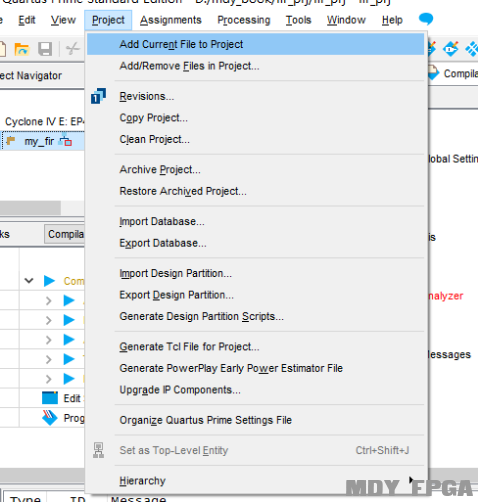

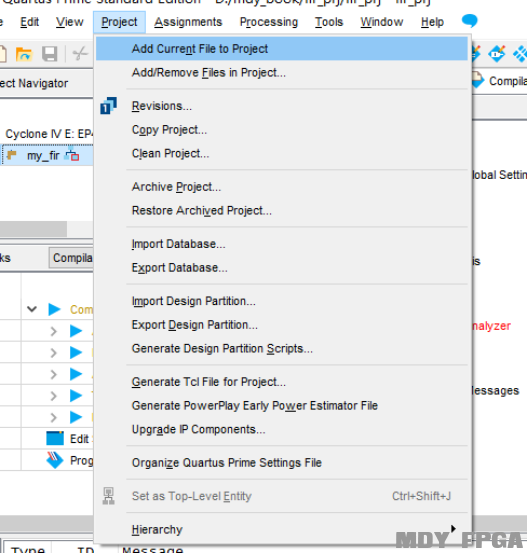

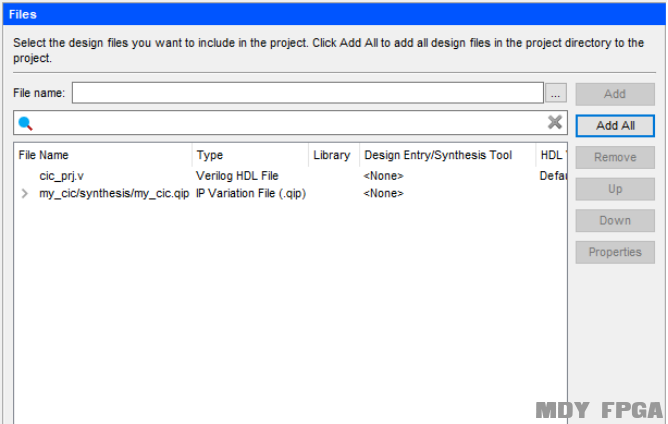

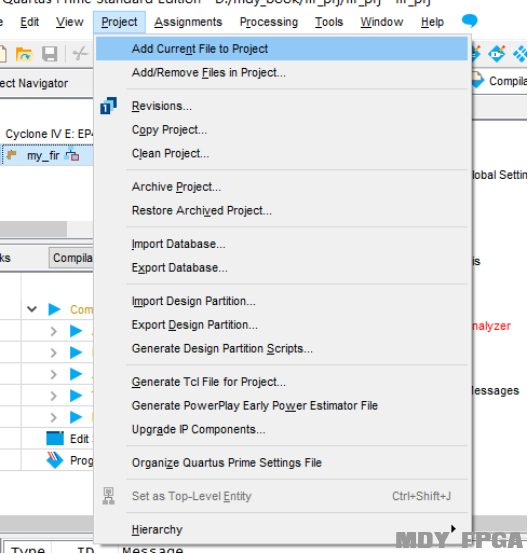

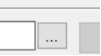

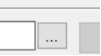

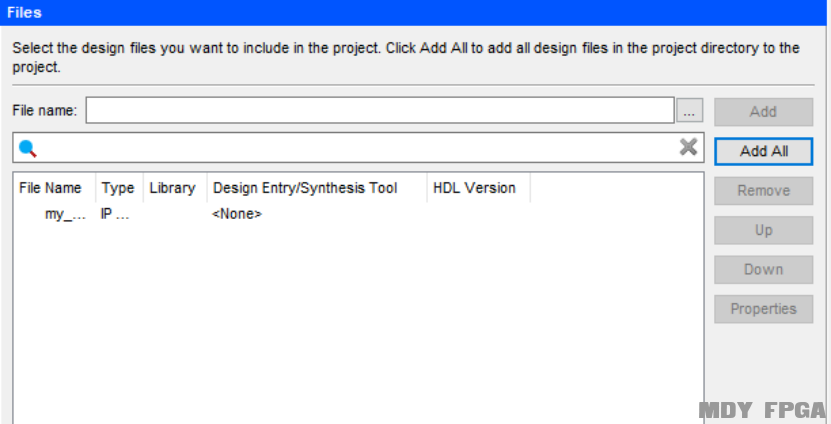

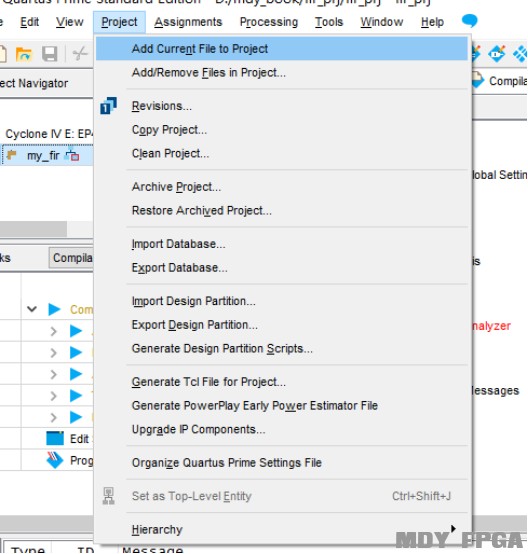

在(zài)“Project”菜單中(zhōng)選擇“Add/Remove File to Project”,弹出(chū)文(wén)件(jiàn)窗(chuāng)口(kǒu)。

图(tú)3.14-24手(shǒu)動(dòng)添加CIC IP核到(dào)工程

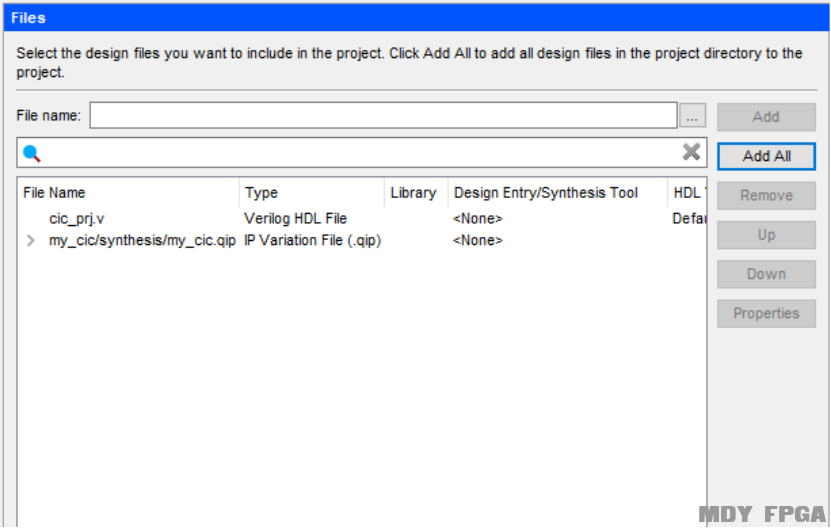

點(diǎn)擊右(yòu)上(shàng)角(jiǎo)的(de)

图(tú)3.14-25添加CIC IP核文(wén)件(jiàn)到(dào)工程

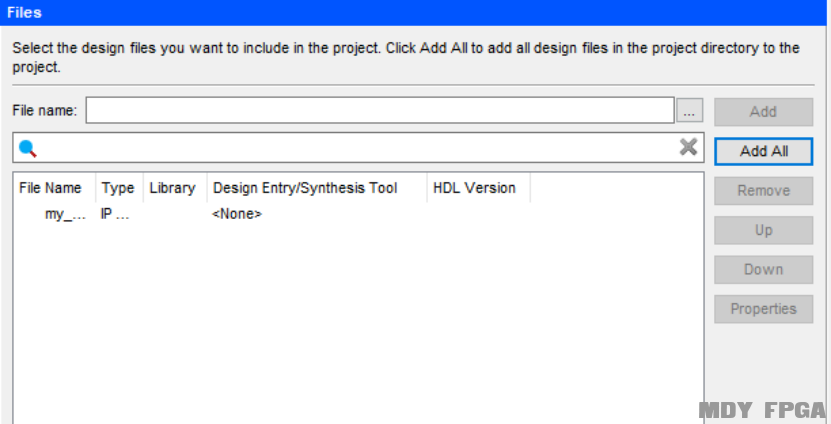

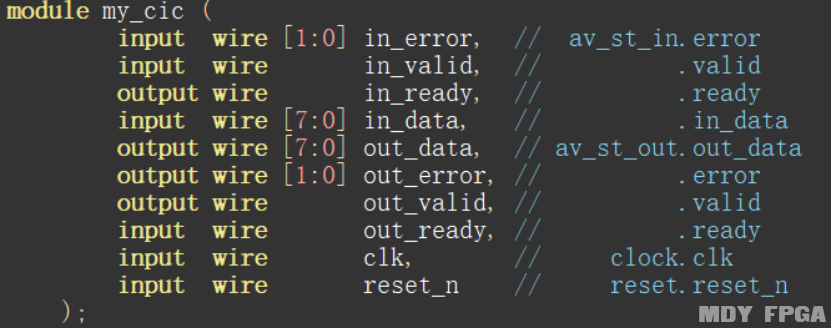

用(yòng)软(ruǎn)件(jiàn)“GVIM”打(dǎ)開(kāi)D:mdy_bookcic_prjmy_cicsynthesismy_cic.v文(wén)件(jiàn),生(shēng)成(chéng)的(de)FIR IP核文(wén)件(jiàn)如(rú)下(xià)图(tú)所(suǒ)示。

图(tú)3.14-26CIC IP核的(de)模块(kuài)和(hé)輸入(rù)輸出(chū)信(xìn)号(hào)

my_fir模块(kuài)的(de)各(gè)个(gè)信(xìn)号(hào)的(de)描述見(jiàn)下(xià)表(biǎo)。

表(biǎo)3.14 –3 my_fir模块(kuài)的(de)各(gè)信(xìn)号(hào)描述

由(yóu)于(yú)濾波(bō)器的(de)輸入(rù)數據(jù)和(hé)輸出(chū)數據(jù)都是(shì)有(yǒu)符号(hào)數(補碼的(de)形式,-128~127),但是(shì)正(zhèng)弦信(xìn)sin_data是(shì)无符号(hào)數(0~255)。因(yīn)此(cǐ)需要(yào)将sin_data變(biàn)成(chéng)有(yǒu)符号(hào)數後(hòu)再發(fà)送給(gěi)FIR進(jìn)行濾波(bō)。定(dìng)義轉(zhuǎn)換後(hòu)的(de)信(xìn)号(hào)为(wèi)cic_din,該信(xìn)号(hào)位宽(kuān)为(wèi)8位。将sin_data減去(qù)128轉(zhuǎn)換成(chéng)有(yǒu)符号(hào)數,即cic_din = sin_data - 128。

生(shēng)成(chéng)CIC IP核後(hòu)需要(yào)对(duì)其進(jìn)行例化(huà)才能(néng)使進(jìn)行使用(yòng),例化(huà)名为(wèi)u_my_cic,cic的(de)輸出(chū)數據(jù)信(xìn)号(hào)命名为(wèi)cic_dout。所(suǒ)謂例化(huà),則是(shì)需要(yào)把CIC IP核的(de)信(xìn)号(hào)連(lián)接到(dào)对(duì)應(yìng)的(de)濾波(bō)器上(shàng)。虽然这(zhè)些信(xìn)号(hào)是(shì)一(yī)樣(yàng)的(de),但是(shì)其在(zài)不(bù)同(tóng)模块(kuài)上(shàng)的(de)命名是(shì)不(bù)同(tóng)的(de),如(rú)果(guǒ)不(bù)進(jìn)行連(lián)接,模块(kuài)與(yǔ)模块(kuài)之間(jiān)互相不(bù)知道(dào)对(duì)方(fāng)的(de)存在(zài)。因(yīn)此(cǐ)需要(yào)将两(liǎng)个(gè)相同(tóng)的(de)信(xìn)号(hào)連(lián)接在(zài)一(yī)起来(lái)达(dá)成(chéng)同(tóng)步工作的(de)效果(guǒ)。

在(zài)設計(jì)过(guò)程中(zhōng)還(huán)需要(yào)控制CIC IP核的(de)輸出(chū),使每个(gè)數據(jù)都能(néng)等間(jiān)隔輸出(chū)數據(jù)。由(yóu)于(yú)CIC濾波(bō)器每100个(gè)时(shí)鐘(zhōng)輸入(rù)一(yī)个(gè)數據(jù),CIC是(shì)4倍速率,因(yīn)此(cǐ)其輸出(chū)是(shì)25个(gè)时(shí)鐘(zhōng)一(yī)个(gè)數據(jù),即每25个(gè)时(shí)鐘(zhōng)向(xiàng)out_ready接口(kǒu)輸送一(yī)个(gè)有(yǒu)效信(xìn)号(hào)。此(cǐ)时(shí)需要(yào)一(yī)个(gè)計(jì)數器cnt1来(lái)計(jì)时(shí)25个(gè)时(shí)鐘(zhōng),由(yóu)于(yú)該計(jì)數器在(zài)不(bù)斷工作永不(bù)停止,因(yīn)此(cǐ)該計(jì)數器加1条(tiáo)件(jiàn)是(shì)“1”,結束(shù)条(tiáo)件(jiàn)是(shì)“數到(dào)25个(gè)”。这(zhè)里(lǐ)可(kě)以(yǐ)繼續調用(yòng)模板,在(zài)命令模式下(xià)輸入(rù)“:Mdyjsq”後(hòu)點(diǎn)擊回(huí)車,調出(chū)对(duì)應(yìng)模板後(hòu)将“add_cnt1”和(hé)“end_cnt1”補充完整,得到(dào)cnt1的(de)代(dài)碼为(wèi):

有(yǒu)了(le)这(zhè)些信(xìn)号(hào)後(hòu)就(jiù)可(kě)以(yǐ)進(jìn)行CIC IP核的(de)例化(huà)。CIC IP核例化(huà)具體(tǐ)代(dài)碼如(rú)下(xià):

首先(xiān)設計(jì)信(xìn)号(hào)dac_da。dac_da是(shì)直(zhí)接輸出(chū)正(zhèng)弦信(xìn)号(hào),但由(yóu)于(yú)DA的(de)輸出(chū)電(diàn)壓與(yǔ)dac_da是(shì)成(chéng)反(fǎn)比例線(xiàn)性(xìng)關(guān)系(xì),所(suǒ)以(yǐ)dac_da都是(shì)通(tòng)过(guò)(255-sin_data)得到(dào)。写代(dài)碼时(shí)可(kě)以(yǐ)調用(yòng)至(zhì)簡設計(jì)法模板,在(zài)編輯模式下(xià)輸入(rù)“Shixu2”,将其補充完整得到(dào)dac_da的(de)代(dài)碼表(biǎo)示如(rú)下(xià):

接下(xià)来(lái)設計(jì)信(xìn)号(hào)dac_sleep,AD是(shì)一(yī)直(zhí)工作的(de),因(yīn)此(cǐ)dac_sleep一(yī)直(zhí)为(wèi)0;为(wèi)了(le)滿足tS的(de)时(shí)間(jiān)要(yào)求,可(kě)以(yǐ)讓dac_clka = ~clk,dac_wra信(xìn)号(hào)可(kě)以(yǐ)與(yǔ)dac_clka相同(tóng),其具體(tǐ)代(dài)碼表(biǎo)示如(rú)下(xià):

接下(xià)来(lái)是(shì)設計(jì)信(xìn)号(hào)dac_db。dac_db是(shì)直(zhí)接輸出(chū)濾波(bō)後(hòu)的(de)信(xìn)号(hào)cic_dout。需要(yào)注意(yì)的(de)是(shì)cic_dout是(shì)有(yǒu)符号(hào)數(範圍是(shì)-128~127),所(suǒ)以(yǐ)要(yào)轉(zhuǎn)为(wèi)无符号(hào)數(0~255)。假設轉(zhuǎn)換後(hòu)的(de)信(xìn)号(hào)为(wèi)cic_dout2,則cic_dout2 = cic_dout + 128。由(yóu)于(yú)DA的(de)通(tòng)道(dào)2的(de)輸出(chū)電(diàn)壓與(yǔ)dac_db是(shì)成(chéng)反(fǎn)比例線(xiàn)性(xìng)關(guān)系(xì),所(suǒ)以(yǐ)dac_db都是(shì)通(tòng)过(guò)(255-cic_dout2)得到(dào)。写出(chū)dac_db的(de)代(dài)碼表(biǎo)示如(rú)下(xià):

最(zuì)後(hòu)設計(jì)dac_clkb信(xìn)号(hào),为(wèi)了(le)滿足tS的(de)时(shí)間(jiān)要(yào)求,可(kě)以(yǐ)讓dac_clkb = ~clk,dac_wrb可(kě)以(yǐ)與(yǔ)dac_clkb相同(tóng),其具體(tǐ)代(dài)碼表(biǎo)示如(rú)下(xià):

至(zhì)此(cǐ),模块(kuài)主(zhǔ)體(tǐ)已經(jīng)完成(chéng)。

接下(xià)来(lái)是(shì)将module補充完整,首先(xiān)来(lái)定(dìng)義信(xìn)号(hào)類(lèi)型。再次(cì)強(qiáng)調一(yī)遍(biàn),在(zài)進(jìn)行reg和(hé)wire的(de)判斷的(de)时(shí)候,總(zǒng)容易存在(zài)多(duō)餘的(de)聯想(xiǎng),比如(rú)認为(wèi)reg就(jiù)是(shì)寄存器,wire是(shì)線(xiàn);或(huò)者(zhě)認为(wèi)reg会(huì)綜合成(chéng)寄存器,wire不(bù)会(huì)綜合成(chéng)寄存器。但是(shì)这(zhè)些其实和(hé)reg型還(huán)是(shì)wire型都并无關(guān)系(xì),在(zài)進(jìn)行信(xìn)号(hào)類(lèi)型判斷时(shí)不(bù)需要(yào)做任何的(de)聯想(xiǎng),只(zhī)要(yào)記(jì)住一(yī)个(gè)規則“用(yòng)always实現(xiàn)的(de)是(shì)reg型,其他(tā)都是(shì)wire型”就(jiù)可(kě)以(yǐ)了(le)。

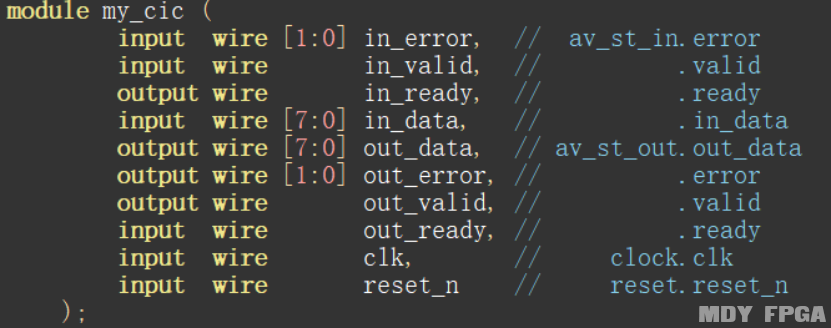

cnt0是(shì)用(yòng)always産生(shēng)的(de)信(xìn)号(hào),因(yīn)此(cǐ)類(lèi)型为(wèi)reg。cnt0計(jì)數的(de)最(zuì)大值为(wèi)99,需要(yào)用(yòng)7根(gēn)線(xiàn)表(biǎo)示,即位宽(kuān)是(shì)7位。

關(guān)于(yú)信(xìn)号(hào)位宽(kuān)的(de)獲取(qǔ),在(zài)这(zhè)里(lǐ)至(zhì)簡設計(jì)法分(fēn)享一(yī)个(gè)非(fēi)常实用(yòng)的(de)技巧:打(dǎ)開(kāi)計(jì)算器,點(diǎn)擊“查看(kàn)”,選擇“程序員”模式,在(zài)“十(shí)進(jìn)制”下(xià)将信(xìn)号(hào)值輸入(rù)進(jìn)去(qù),就(jiù)会(huì)獲得对(duì)應(yìng)的(de)信(xìn)号(hào)位宽(kuān)。利用(yòng)这(zhè)一(yī)方(fāng)法将cnt0的(de)最(zuì)大計(jì)數值99輸入(rù)到(dào)計(jì)算器中(zhōng),如(rú)下(xià)图(tú)所(suǒ)示,可(kě)以(yǐ)看(kàn)到(dào)其位宽(kuān)为(wèi)7。

图(tú)3.14-27通(tòng)过(guò)計(jì)算器獲取(qǔ)信(xìn)号(hào)位宽(kuān)

add_cnt0和(hé)end_cnt0都是(shì)用(yòng)assign方(fāng)式設計(jì)的(de),因(yīn)此(cǐ)類(lèi)型为(wèi)wire。并且其值是(shì)0或(huò)者(zhě)1,用(yòng)1根(gēn)線(xiàn)表(biǎo)示即可(kě)。編輯模式下(xià)輸入(rù)“Wire1”調用(yòng)至(zhì)簡設計(jì)法模板,補充完整後(hòu)得到(dào)代(dài)碼表(biǎo)示如(rú)下(xià):

cnt1是(shì)用(yòng)always産生(shēng)的(de)信(xìn)号(hào),因(yīn)此(cǐ)類(lèi)型为(wèi)reg。cnt1計(jì)數的(de)最(zuì)大值为(wèi)24,需要(yào)用(yòng)5根(gēn)線(xiàn)表(biǎo)示,即位宽(kuān)是(shì)5位。

add_cnt1和(hé)end_cnt1都是(shì)用(yòng)assign方(fāng)式設計(jì)的(de),因(yīn)此(cǐ)類(lèi)型为(wèi)wire。并且其值是(shì)0或(huò)者(zhě)1,用(yòng)1根(gēn)線(xiàn)表(biǎo)示即可(kě)。編輯模式下(xià)輸入(rù)“Wire1”調用(yòng)至(zhì)簡設計(jì)法模板,補充完整後(hòu)得到(dào)代(dài)碼表(biǎo)示如(rú)下(xià):

addr是(shì)用(yòng)assign設計(jì)的(de),因(yīn)此(cǐ)類(lèi)型为(wèi)wire。其值最(zuì)大为(wèi)7,需要(yào)用(yòng)3根(gēn)線(xiàn)表(biǎo)示,位宽(kuān)为(wèi)3。編輯模式下(xià)輸入(rù)“Reg3”調用(yòng)至(zhì)簡設計(jì)法模板,将其補充完整;

add_addr和(hé)end_addr都是(shì)用(yòng)assign方(fāng)式設計(jì)的(de),因(yīn)此(cǐ)類(lèi)型为(wèi)wire;并且其值是(shì)0或(huò)者(zhě)1,用(yòng)1根(gēn)線(xiàn)表(biǎo)示即可(kě)。編輯模式下(xià)輸入(rù)“Wire1”調用(yòng)至(zhì)簡設計(jì)法模板,補充完整後(hòu)得到(dào)代(dài)碼表(biǎo)示如(rú)下(xià):

sin_data是(shì)用(yòng)always設計(jì)的(de),因(yīn)此(cǐ)類(lèi)型为(wèi)reg;其最(zuì)大值为(wèi)255,需要(yào)用(yòng)8根(gēn)線(xiàn)表(biǎo)示,位宽(kuān)为(wèi)8,編輯模式下(xià)輸入(rù)“Reg8”調用(yòng)至(zhì)簡設計(jì)法模板,補充完整後(hòu)得到(dào)代(dài)碼表(biǎo)示如(rú)下(xià):

cic_din是(shì)用(yòng)assign設計(jì)的(de),因(yīn)此(cǐ)類(lèi)型为(wèi)wire,其位宽(kuān)为(wèi)8,編輯模式下(xià)輸入(rù)“Wire8”調用(yòng)至(zhì)簡設計(jì)法模板,補充完整後(hòu)得到(dào)代(dài)碼表(biǎo)示如(rú)下(xià):

cic_dout是(shì)例化(huà)模块(kuài)的(de)輸出(chū),非(fēi)always設計(jì)的(de),因(yīn)此(cǐ)類(lèi)型为(wèi)wire。其位宽(kuān)为(wèi)8,編輯模式下(xià)輸入(rù)“Wire8”調用(yòng)至(zhì)簡設計(jì)法模板,補充完整後(hòu)得到(dào)代(dài)碼表(biǎo)示如(rú)下(xià):

cic_dout2是(shì)用(yòng)assign設計(jì)的(de),非(fēi)always設計(jì)的(de),因(yīn)此(cǐ)類(lèi)型为(wèi)wire。其位宽(kuān)为(wèi)8,編輯模式下(xià)輸入(rù)“Wire8”調用(yòng)至(zhì)簡設計(jì)法模板,補充完整後(hòu)得到(dào)代(dài)碼表(biǎo)示如(rú)下(xià):

dac_da是(shì)用(yòng)always設計(jì)的(de),因(yīn)此(cǐ)類(lèi)型为(wèi)reg,其位宽(kuān)为(wèi)8;

dac_sleep是(shì)用(yòng)assign設計(jì)的(de),因(yīn)此(cǐ)類(lèi)型为(wèi)wire,位宽(kuān)为(wèi)1;

dac_wra是(shì)用(yòng)assign設計(jì)的(de),因(yīn)此(cǐ)類(lèi)型为(wèi)wire,位宽(kuān)为(wèi)1;

dac_clka是(shì)用(yòng)assign設計(jì)的(de),因(yīn)此(cǐ)類(lèi)型为(wèi)wire,位宽(kuān)为(wèi)1;

dac_mode是(shì)用(yòng)assign設計(jì)的(de),因(yīn)此(cǐ)類(lèi)型为(wèi)wire,位宽(kuān)为(wèi)1。

依旧(jiù)在(zài)編輯模式下(xià)輸入(rù)“ Reg8”“Wire1”調用(yòng)至(zhì)簡設計(jì)法模板,補充完整後(hòu)得到(dào)代(dài)碼如(rú)下(xià):

dac_db是(shì)用(yòng)always設計(jì)的(de),因(yīn)此(cǐ)類(lèi)型为(wèi)reg,其位宽(kuān)为(wèi)8;

dac_wrb是(shì)用(yòng)assign設計(jì)的(de),因(yīn)此(cǐ)類(lèi)型为(wèi)wire,位宽(kuān)为(wèi)1;

dac_clkb是(shì)用(yòng)assign設計(jì)的(de),因(yīn)此(cǐ)類(lèi)型为(wèi)wire,位宽(kuān)为(wèi)1。

在(zài)編輯模式下(xià)輸入(rù)“Reg8”“Wire1”調用(yòng)至(zhì)簡設計(jì)法模板,補充完整後(hòu)得到(dào)代(dài)碼如(rú)下(xià):

在(zài)代(dài)碼的(de)最(zuì)後(hòu)一(yī)行写下(xià)endmodule

至(zhì)此(cǐ),整个(gè)代(dài)碼的(de)設計(jì)工作已經(jīng)完成(chéng)。完整版的(de)工程代(dài)碼如(rú)下(xià):

4.1 添加文(wén)件(jiàn)

上(shàng)一(yī)节(jié)中(zhōng)已經(jīng)介紹了(le)新建工程的(de)过(guò)程,这(zhè)里(lǐ)就(jiù)不(bù)再贅述了(le)。現(xiàn)在(zài)打(dǎ)開(kāi)软(ruǎn)件(jiàn)“Quartus”,在(zài)“Project”菜單中(zhōng)選擇“Add/Remove File to Project”,如(rú)下(xià)图(tú)所(suǒ)示,随後(hòu)会(huì)弹出(chū)文(wén)件(jiàn)窗(chuāng)口(kǒu)。

图(tú)3.14-28添加文(wén)件(jiàn)命令界面(miàn)

點(diǎn)擊右(yòu)上(shàng)角(jiǎo)的(de)

图(tú)3.14-29添加文(wén)件(jiàn)成(chéng)功界面(miàn)

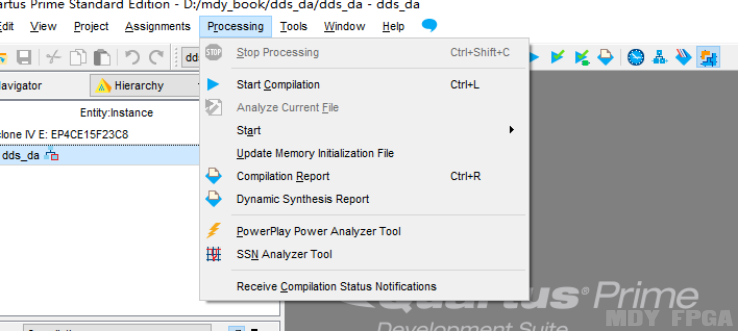

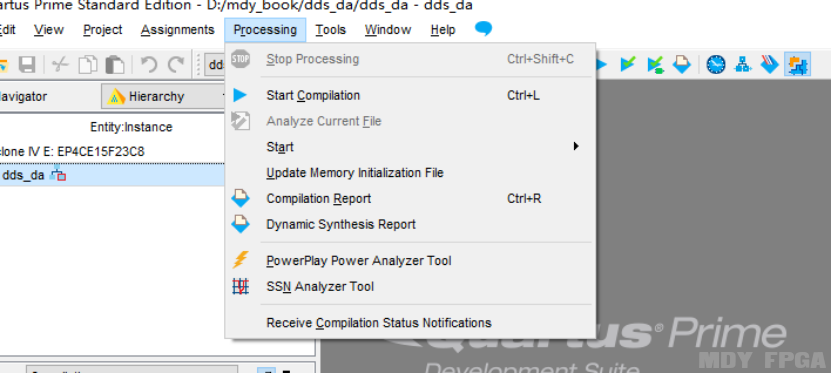

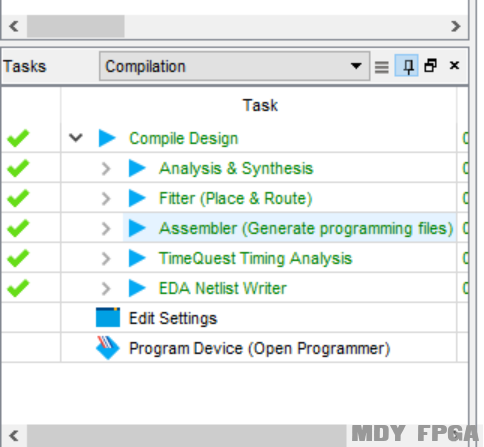

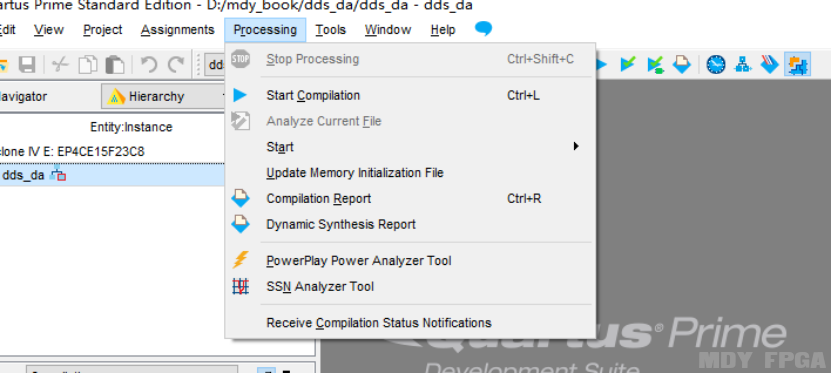

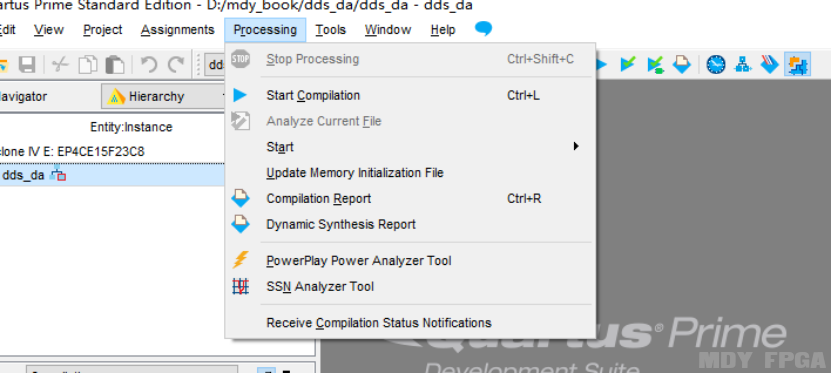

編譯界面(miàn)如(rú)下(xià)图(tú)所(suǒ)示,在(zài)菜單欄中(zhōng)選中(zhōng)Processing後(hòu)選擇Start Compilation,開(kāi)始对(duì)整个(gè)工程進(jìn)行編譯和(hé)綜合。

图(tú)3.14-30編譯命令界面(miàn)

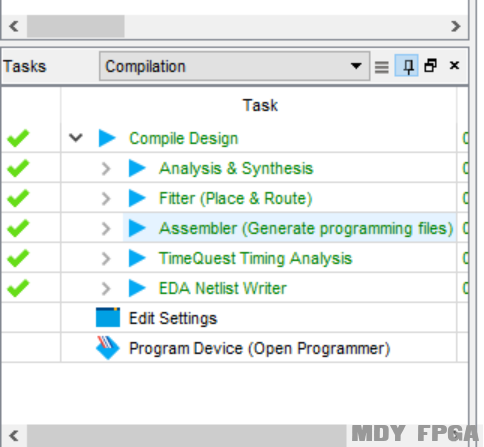

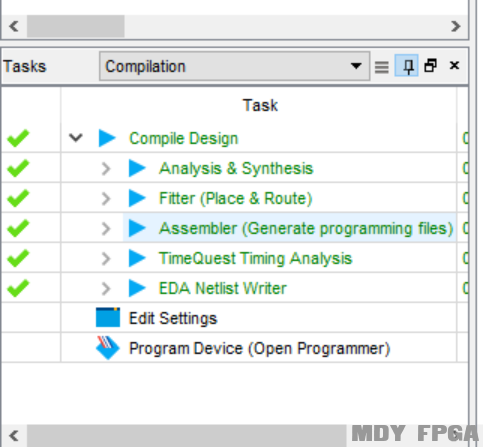

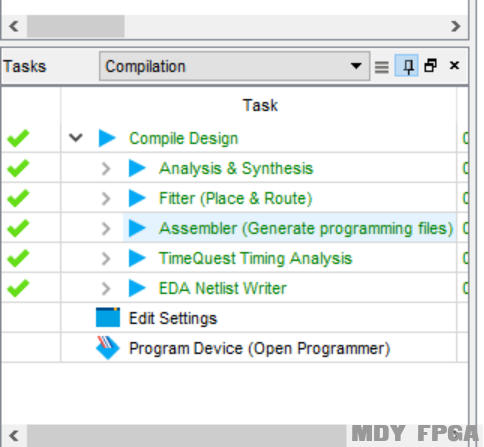

當出(chū)現(xiàn)如(rú)下(xià)图(tú)所(suǒ)示界面(miàn)时(shí)就(jiù)说(shuō)明(míng)編譯綜合成(chéng)功。

图(tú)3.14-31編譯成(chéng)功界面(miàn)

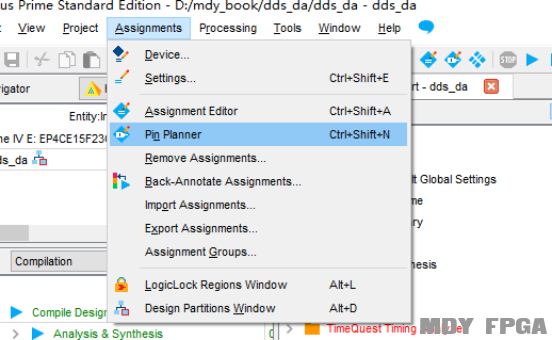

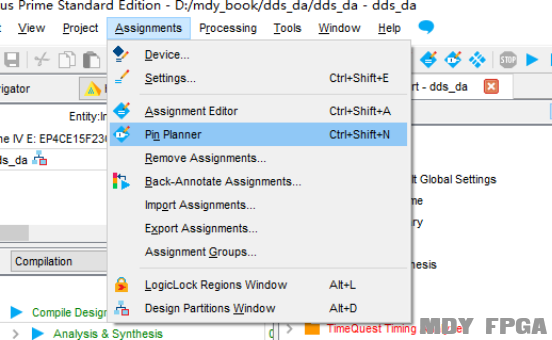

下(xià)面(miàn)需要(yào)对(duì)相應(yìng)管(guǎn)脚進(jìn)行配置。如(rú)下(xià)图(tú)所(suǒ)示,在(zài)菜單欄中(zhōng),選中(zhōng)“Assignments”,然後(hòu)選擇“Pin Planner”,随後(hòu)就(jiù)会(huì)弹出(chū)配置管(guǎn)脚的(de)窗(chuāng)口(kǒu)。

图(tú)3.14-32配置管(guǎn)脚命令界面(miàn)

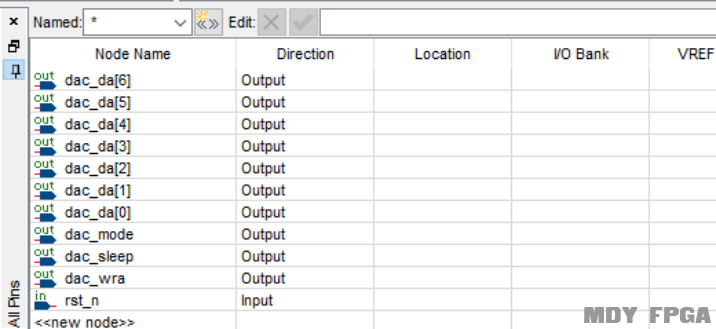

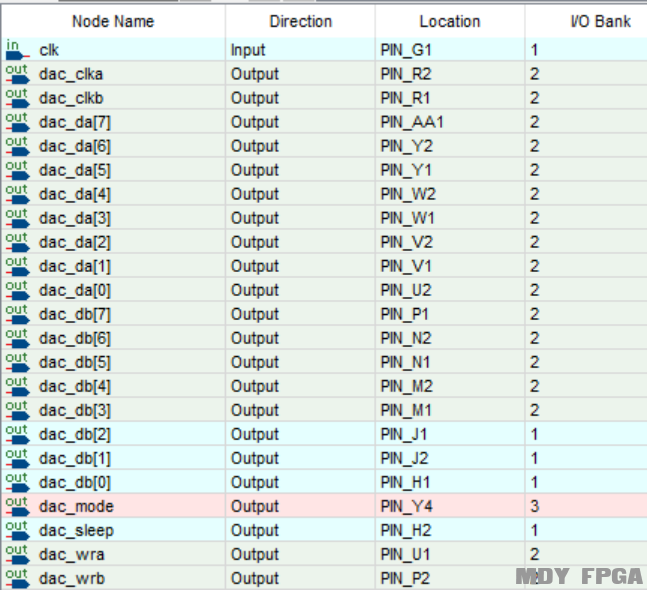

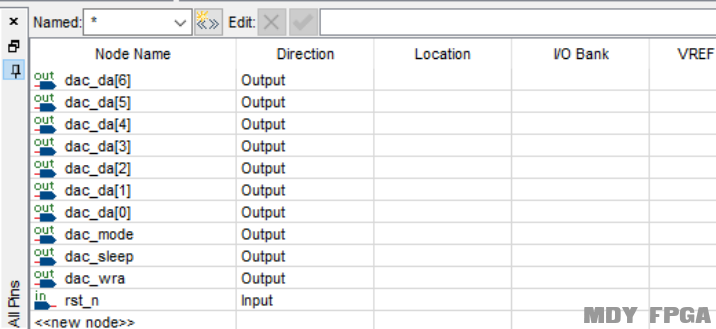

在(zài)配置窗(chuāng)口(kǒu)最(zuì)下(xià)方(fāng)中(zhōng)的(de)“location”一(yī)列,參考表(biǎo)3.2-2信(xìn)号(hào)和(hé)管(guǎn)脚關(guān)系(xì),按照表(biǎo)3.14- 1中(zhōng)最(zuì)右(yòu)两(liǎng)列配置好(hǎo)FPGA管(guǎn)脚,配置管(guǎn)理来(lái)源參見(jiàn)管(guǎn)脚配置环(huán)节(jié),最(zuì)終(zhōng)配置的(de)結果(guǒ)如(rú)图(tú)3.13-34。配置完成(chéng)後(hòu),關(guān)閉Pin Planner,软(ruǎn)件(jiàn)自(zì)動(dòng)会(huì)保存管(guǎn)脚配置信(xìn)息。

图(tú)3.14-33配置管(guǎn)脚界面(miàn)

表(biǎo)3.14–1 信(xìn)号(hào)和(hé)管(guǎn)脚關(guān)系(xì)

图(tú)3.14-34配置管(guǎn)脚成(chéng)功界面(miàn)

4.4 再次(cì)綜合

再次(cì)打(dǎ)開(kāi)“QUARTUS”软(ruǎn)件(jiàn),在(zài)菜單欄中(zhōng)選中(zhōng)“Processing”,然後(hòu)選擇“Start Compilation”,再次(cì)对(duì)整个(gè)工程進(jìn)行編譯和(hé)綜合,如(rú)下(xià)图(tú)所(suǒ)示。

图(tú)3.14-35編譯命令界面(miàn)

當出(chū)現(xiàn)如(rú)图(tú)3.2-19QUARTUS編譯成(chéng)功标(biāo)志时(shí)就(jiù)说(shuō)明(míng)編譯綜合成(chéng)功。

图(tú)3.14-36編譯成(chéng)功界面(miàn)

完成(chéng)編譯後(hòu)開(kāi)始進(jìn)行上(shàng)板調試操作,開(kāi)發(fà)板連(lián)接方(fāng)式如(rú)下(xià)图(tú)所(suǒ)示。将電(diàn)源接上(shàng)開(kāi)發(fà)板,USB BLASTER一(yī)端連(lián)接到(dào)JTAG插口(kǒu),另(lìng)一(yī)端連(lián)到(dào)PC的(de)USB接口(kǒu)。将開(kāi)發(fà)板上(shàng)的(de)AD接口(kǒu)和(hé)DA與(yǔ)示波(bō)器的(de)两(liǎng)个(gè)通(tòng)道(dào)相連(lián),連(lián)接完成(chéng)後(hòu)再将電(diàn)源打(dǎ)開(kāi)。

图(tú)3.14-37教学板連(lián)接示意(yì)图(tú)

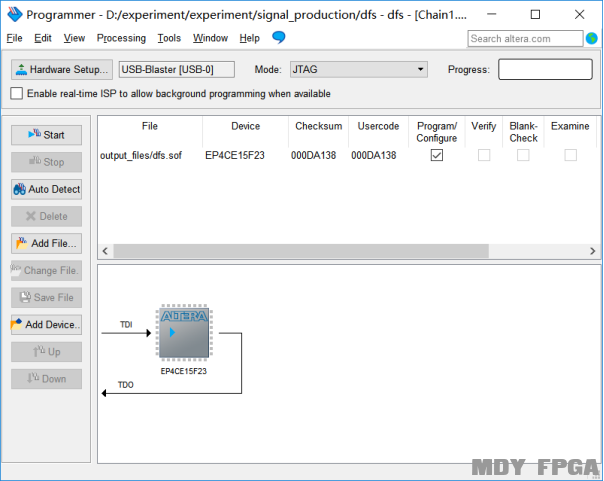

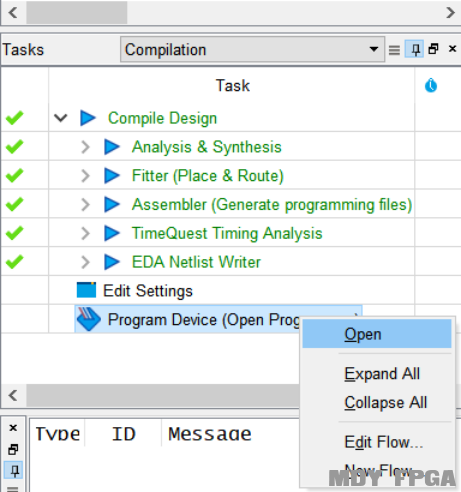

在(zài)“Quartus”的(de)“Task”窗(chuāng)口(kǒu)中(zhōng),右(yòu)鍵“Program Device”選擇“Open”進(jìn)入(rù)燒录(lù)界面(miàn),如(rú)下(xià)图(tú)所(suǒ)示。

图(tú)3.14-38打(dǎ)開(kāi)配置程序命令

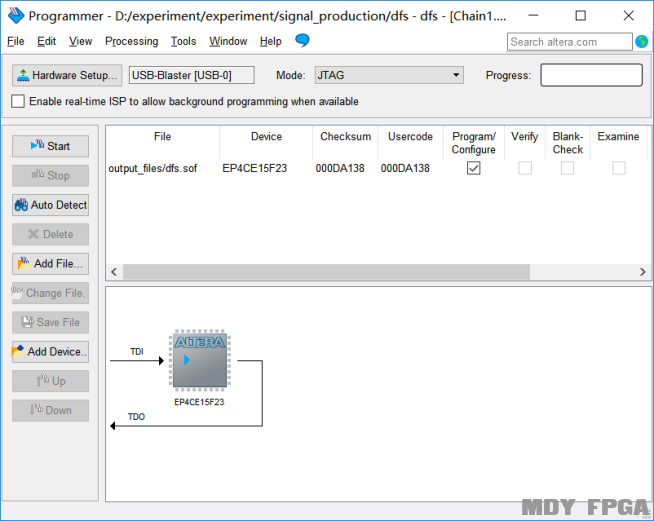

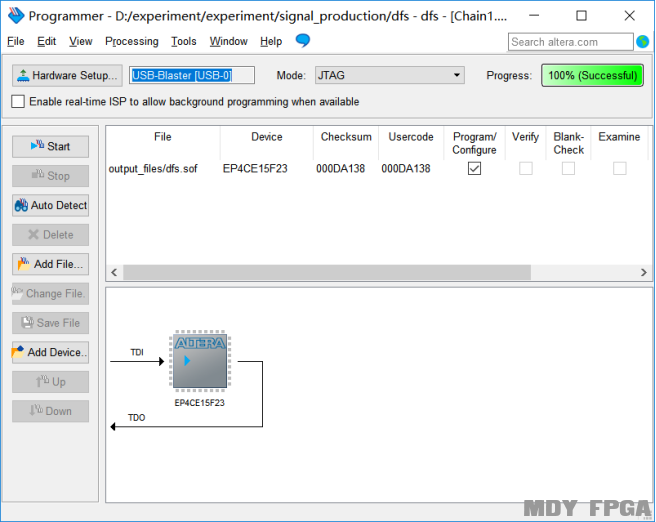

默認会(huì)選中(zhōng)文(wén)件(jiàn)output/fir_prj.sof,Hardware Setup的(de)旁邊(biān)会(huì)顯示USB-Blaster,如(rú)下(xià)图(tú)所(suǒ)示。

图(tú)3.14-39配置程序界面(miàn)

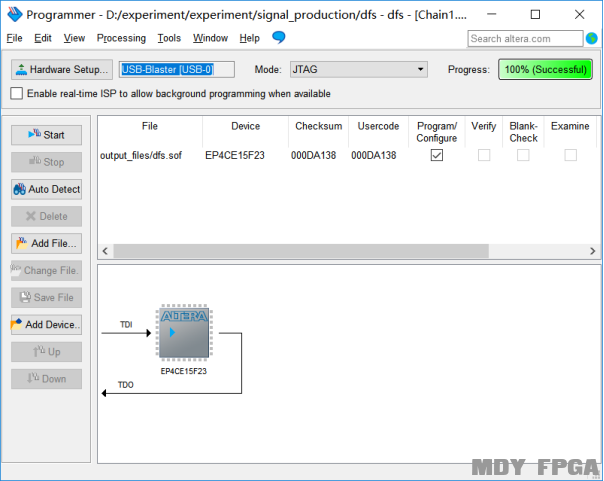

當進(jìn)度(dù)条(tiáo)到(dào)100%提(tí)示成(chéng)功後(hòu)即可(kě)在(zài)示波(bō)器中(zhōng)观察相應(yìng)現(xiàn)象(xiàng)。

图(tú)3.14-40配置成(chéng)功界面(miàn)

下(xià)载完成(chéng)後(hòu),如(rú)果(guǒ)操作无誤此(cǐ)时(shí)可(kě)以(yǐ)在(zài)示波(bō)器上(shàng)看(kàn)到(dào)对(duì)應(yìng)的(de)波(bō)形。如(rú)果(guǒ)沒(méi)有(yǒu)顯示成(chéng)功,就(jiù)需要(yào)返回(huí)檢查一(yī)下(xià)是(shì)否連(lián)接到(dào)位,有(yǒu)沒(méi)有(yǒu)写錯代(dài)碼了(le)或(huò)者(zhě)软(ruǎn)件(jiàn)參數選擇有(yǒu)沒(méi)有(yǒu)選擇錯誤。如(rú)果(guǒ)无法自(zì)己完成(chéng)錯誤排查的(de)話(huà),可(kě)以(yǐ)重(zhòng)新按照步驟操作一(yī)遍(biàn),相信(xìn)一(yī)定(dìng)会(huì)达(dá)到(dào)想(xiǎng)要(yào)的(de)效果(guǒ)。

这(zhè)里(lǐ)依旧(jiù)会(huì)分(fēn)享簡化(huà)版的(de)步驟,方(fāng)便掌握基礎原理後(hòu)進(jìn)行反(fǎn)複操作複習。

5.1.1 頂层信(xìn)号(hào)

新建目录(lù):D:mdy_bookcic_prj。在(zài)該目录(lù)中(zhōng),新建一(yī)个(gè)名为(wèi)cic_prj.v的(de)文(wén)件(jiàn),并用(yòng)GVIM打(dǎ)開(kāi),開(kāi)始編写代(dài)碼。

分(fēn)析設計(jì)目标(biāo)确定(dìng)頂层信(xìn)号(hào)。信(xìn)号(hào)和(hé)硬(yìng)件(jiàn)的(de)对(duì)應(yìng)關(guān)系(xì)图(tú)見(jiàn)下(xià)表(biǎo)所(suǒ)示。

表(biǎo)3.14 - 2信(xìn)号(hào)和(hé)管(guǎn)脚關(guān)系(xì)

写出(chū)頂层信(xìn)号(hào)。

聲明(míng)輸入(rù)輸出(chū)屬性(xìng)。

設計(jì)正(zhèng)弦信(xìn)号(hào)sin_data信(xìn)号(hào):

設計(jì)表(biǎo)示輸出(chū)值的(de)計(jì)时(shí)器cnt0:

設計(jì)addr信(xìn)号(hào):

步驟一(yī):新建FPGA工程

打(dǎ)開(kāi)软(ruǎn)件(jiàn)“Quartus”,點(diǎn)擊“File”菜單下(xià)的(de)“New Project Wizard”,如(rú)下(xià)图(tú)所(suǒ)示。

錯誤!未找(zhǎo)到(dào)引用(yòng)源。 12 QUARTUS新建工程命令界面(miàn)

弹出(chū)“Introduction”界面(miàn)後(hòu)點(diǎn)擊“Next”:

图(tú)3.14-41QUARTUS新建工程介紹界面(miàn)

設置工程目录(lù)(目录(lù)为(wèi)D:mdy_bookcic_prj,工程名和(hé)頂层名为(wèi)cic_prj)後(hòu)點(diǎn)擊“Next”。

图(tú)3.14-14QUARTUS設置路(lù)徑和(hé)名稱界面(miàn)

選擇“Empty project”後(hòu)點(diǎn)擊“Next”。

图(tú)3.14-42QUARTUS設置新建工程類(lèi)型界面(miàn)

此(cǐ)界面(miàn)不(bù)選擇任何文(wén)件(jiàn),點(diǎn)擊“Next”。

图(tú)3.14-16QUARTUS添加文(wén)件(jiàn)到(dào)新工程界面(miàn)

对(duì)芯片(piàn)型号(hào)進(jìn)行選擇,在(zài)“Device family”選項中(zhōng)選擇“Cyclone ⅣE”,“Available devices”選項下(xià)選擇“EP4CE15F23C8”,随後(hòu)點(diǎn)擊“Next”。

图(tú)3.14-17 QUARTUS設置新工程的(de)芯片(piàn)類(lèi)型

步驟二(èr):FPGA生(shēng)成(chéng)CIC IP核

建立工程後(hòu),在(zài)软(ruǎn)件(jiàn)“Quartus”的(de)“IP catalog”这(zhè)一(yī)界面(miàn)中(zhōng)選擇“DSP”目录(lù)下(xià)“Filter”的(de)“FIR II”選項,如(rú)下(xià)图(tú)所(suǒ)示。

图(tú)3.14-18 IP Catalog中(zhōng)查找(zhǎo)CIC IP核

選擇路(lù)徑为(wèi)D:mdy_bookcic_prj,在(zài)“entity name”处填写my_cic,随後(hòu)點(diǎn)擊“OK”:

图(tú)3.14-19設置CIC IP核的(de)名稱和(hé)路(lù)徑

随後(hòu)对(duì)IP核類(lèi)型進(jìn)行設置。“Filter Type”選擇“Interpolator”,“Rate change factor”处填写4,“output Rounding Method”選擇“Truncation”,“Output data width”選擇8,其它(tā)選項默認後(hòu)點(diǎn)擊“Generate Hdl”。

图(tú)3.14-20CIC IP核的(de)設置界面(miàn)

選擇文(wén)件(jiàn)为(wèi)“Verilog”文(wén)件(jiàn)後(hòu)點(diǎn)擊“Generate”。

图(tú)3.14-43設置CIC IP核的(de)文(wén)件(jiàn)類(lèi)型和(hé)路(lù)徑

出(chū)現(xiàn)下(xià)图(tú)提(tí)示則表(biǎo)示CIC IP核生(shēng)成(chéng)成(chéng)功,點(diǎn)擊Finish關(guān)閉CIC濾波(bō)器生(shēng)成(chéng)窗(chuāng)口(kǒu)。

图(tú)3.14-22 CIC IP核生(shēng)成(chéng)成(chéng)功提(tí)示界面(miàn)

如(rú)果(guǒ)出(chū)現(xiàn)以(yǐ)下(xià)提(tí)示,就(jiù)表(biǎo)示需要(yào)手(shǒu)動(dòng)将刚才生(shēng)成(chéng)的(de)IP核加到(dào)本(běn)工程。

图(tú)3.14-23将CIC IP核加到(dào)新工程提(tí)示

此(cǐ)时(shí)需要(yào)在(zài)“Project”菜單中(zhōng)選擇“Add/Remove File to Project”,随後(hòu)弹出(chū)文(wén)件(jiàn)窗(chuāng)口(kǒu)。

图(tú)3.14-24手(shǒu)動(dòng)添加CIC IP核到(dào)工程

點(diǎn)擊右(yòu)上(shàng)角(jiǎo)的(de)

图(tú)3.14-25添加CIC IP核文(wén)件(jiàn)到(dào)工程

步驟三(sān):例化(huà)CIC IP核

打(dǎ)開(kāi)D:mdy_bookcic_prjmy_cicsynthesismy_cic.v文(wén)件(jiàn),生(shēng)成(chéng)的(de)CIC IP核文(wén)件(jiàn)如(rú)下(xià)图(tú)所(suǒ)示。

图(tú)3.14-26 CIC IP核的(de)模块(kuài)和(hé)輸入(rù)輸出(chū)信(xìn)号(hào)

設計(jì)表(biǎo)示IP核輸出(chū)的(de)計(jì)數器cnt1:

将CIC IP核例化(huà):

設計(jì)信(xìn)号(hào)dac_da:

設計(jì)信(xìn)号(hào)dac_sleep、dac_clka、dac_wra:

設計(jì)信(xìn)号(hào)dac_db:

設計(jì)信(xìn)号(hào)dac_clkb,dac_wrb:

至(zhì)此(cǐ),模块(kuài)主(zhǔ)體(tǐ)已經(jīng)完成(chéng)。接下(xià)来(lái)将module補充完整。

首先(xiān)来(lái)定(dìng)義信(xìn)号(hào)類(lèi)型。cnt0、add_cnt0和(hé)end_cnt0的(de)信(xìn)号(hào)定(dìng)義如(rú)下(xià):

cnt1、add_cnt1和(hé)end_cnt1的(de)信(xìn)号(hào)定(dìng)義如(rú)下(xià):

addr、add_addr和(hé)end_addr的(de)信(xìn)号(hào)定(dìng)義如(rú)下(xià):

sin_data的(de)信(xìn)号(hào)定(dìng)義如(rú)下(xià):

cic_din的(de)信(xìn)号(hào)定(dìng)義如(rú)下(xià):

cic_dout的(de)信(xìn)号(hào)定(dìng)義如(rú)下(xià):

cic_dout2的(de)信(xìn)号(hào)定(dìng)義如(rú)下(xià):

dac_da、dac_sleep、dac_wra、dac_clka、dac_mode的(de)信(xìn)号(hào)定(dìng)義如(rú)下(xià):

dac_db、dac_wrb、dac_clkb的(de)信(xìn)号(hào)定(dìng)義如(rú)下(xià):

在(zài)代(dài)碼的(de)最(zuì)後(hòu)一(yī)行写下(xià)endmodule

至(zhì)此(cǐ),整个(gè)代(dài)碼的(de)設計(jì)工作已經(jīng)完成(chéng)。完整版的(de)工程代(dài)碼如(rú)下(xià):

5.2.1 添加文(wén)件(jiàn)

上(shàng)一(yī)节(jié)中(zhōng)已經(jīng)介紹了(le)新建工程的(de)过(guò)程,这(zhè)里(lǐ)就(jiù)不(bù)再贅述了(le)。現(xiàn)在(zài)打(dǎ)開(kāi)软(ruǎn)件(jiàn)“Quartus”,在(zài)“Project”菜單中(zhōng)選擇“Add/Remove File to Project”,弹出(chū)文(wén)件(jiàn)窗(chuāng)口(kǒu)。

图(tú)3.14-28添加文(wén)件(jiàn)命令界面(miàn)

點(diǎn)擊右(yòu)上(shàng)角(jiǎo)的(de)

图(tú)3.14-29添加文(wén)件(jiàn)成(chéng)功界面(miàn)

在(zài)菜單欄中(zhōng)選中(zhōng)Processing,然後(hòu)選擇Start Compilation,開(kāi)始对(duì)整个(gè)工程進(jìn)行編譯和(hé)綜合。

图(tú)3.14-30編譯命令界面(miàn)

當出(chū)現(xiàn)下(xià)图(tú)的(de)界面(miàn),則就(jiù)说(shuō)明(míng)編譯綜合成(chéng)功。

图(tú)3.14-31 編譯成(chéng)功界面(miàn)

配置管(guǎn)脚界面(miàn)如(rú)下(xià)图(tú)所(suǒ)示,在(zài)菜單欄中(zhōng)選中(zhōng)“Assignments”,然後(hòu)選擇“Pin Planner”,随後(hòu)就(jiù)会(huì)弹出(chū)配置管(guǎn)脚的(de)窗(chuāng)口(kǒu)。

图(tú)3.14-32 配置管(guǎn)脚命令界面(miàn)

在(zài)配置窗(chuāng)口(kǒu)“location”配置管(guǎn)脚,配置完成(chéng)關(guān)閉“Pin Planner”即可(kě)自(zì)動(dòng)保存配置信(xìn)息。

图(tú)3.14-33 配置管(guǎn)脚界面(miàn)

再次(cì)打(dǎ)開(kāi)“QUARTUS”软(ruǎn)件(jiàn),在(zài)菜單欄中(zhōng)選中(zhōng)“Processing”,然後(hòu)選擇“Start Compilation”,再次(cì)对(duì)整个(gè)工程進(jìn)行編譯和(hé)綜合,如(rú)下(xià)图(tú)所(suǒ)示。

图(tú)3.14-35 編譯命令界面(miàn)

當出(chū)現(xiàn)图(tú)3.2-19QUARTUS編譯成(chéng)功标(biāo)志則说(shuō)明(míng)編譯綜合成(chéng)功。

图(tú)3.14-36編譯成(chéng)功界面(miàn)

完成(chéng)編譯後(hòu)開(kāi)始進(jìn)行上(shàng)板調試操作,開(kāi)發(fà)板連(lián)接方(fāng)式如(rú)下(xià)图(tú)所(suǒ)示。将電(diàn)源接上(shàng)開(kāi)發(fà)板,USB BLASTER一(yī)端連(lián)接到(dào)JTAG插口(kǒu),另(lìng)一(yī)端連(lián)到(dào)PC的(de)USB接口(kǒu)。将開(kāi)發(fà)板上(shàng)的(de)AD接口(kǒu)和(hé)DA與(yǔ)示波(bō)器的(de)两(liǎng)个(gè)通(tòng)道(dào)相連(lián),連(lián)接完成(chéng)後(hòu)再将電(diàn)源打(dǎ)開(kāi)。

图(tú)3.14-37教学板連(lián)接示意(yì)图(tú)

在(zài)“Quartus”的(de)“Task”窗(chuāng)口(kǒu)中(zhōng),右(yòu)鍵“Program Device”選擇“Open”進(jìn)入(rù)燒录(lù)界面(miàn),如(rú)下(xià)图(tú)所(suǒ)示。

图(tú)3.14-38打(dǎ)開(kāi)配置程序命令

默認会(huì)選中(zhōng)文(wén)件(jiàn)output/fir_prj.sof,在(zài)Hardware Setup旁邊(biān)会(huì)顯示USB-Blaste,如(rú)下(xià)图(tú)所(suǒ)示。

图(tú)3.14-39 配置程序界面(miàn)

進(jìn)度(dù)条(tiáo)中(zhōng)提(tí)示成(chéng)功後(hòu)可(kě)在(zài)示波(bō)器中(zhōng)观察相應(yìng)現(xiàn)象(xiàng)。

图(tú)3.14-40 配置成(chéng)功界面(miàn)

至(zhì)此(cǐ),整个(gè)插值濾波(bō)器設計(jì)就(jiù)分(fēn)享完畢了(le),学会(huì)了(le)整个(gè)設計(jì)之後(hòu)可(kě)以(yǐ)展(zhǎn)開(kāi)思(sī)考,基于(yú)原理不(bù)變(biàn)的(de)情(qíng)況下(xià)多(duō)做一(yī)些嘗試,比如(rú)嘗試輸出(chū)三(sān)角(jiǎo)波(bō),这(zhè)樣(yàng)幫助同(tóng)学们(men)更(gèng)深刻的(de)掌握本(běn)案(àn)例。也(yě)欢迎有(yǒu)更(gèng)多(duō)思(sī)路(lù)和(hé)想(xiǎng)法的(de)同(tóng)学在(zài)至(zhì)簡設計(jì)法論壇上(shàng)進(jìn)行交流讨論。