本(běn)节(jié)的(de)文(wén)檔編号(hào):001700000021

需要(yào)看(kàn)对(duì)應(yìng)的(de)視頻,請點(diǎn)擊視頻編号(hào):001700000442

1、至(zhì)間(jiān)原理與(yǔ)應(yìng)用(yòng)配套(tào)的(de)案(àn)例和(hé)PPT講解(jiě)

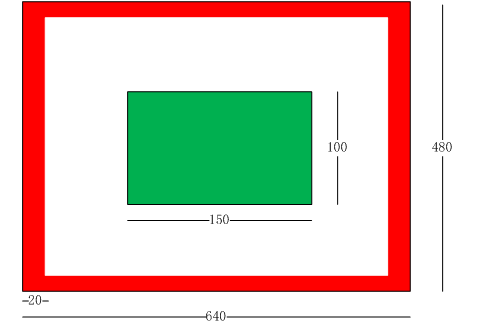

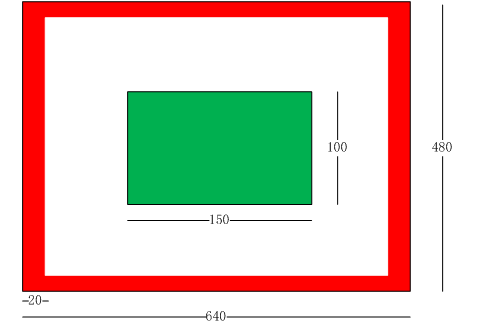

2、本(běn)設計(jì)需要(yào)通(tòng)过(guò)VGA線(xiàn)将顯示器和(hé)開(kāi)發(fà)板進(jìn)行連(lián)接,FPGA在(zài)連(lián)接成(chéng)功後(hòu)産生(shēng)640*480分(fēn)辨率,刷新頻率为(wèi)60Hz的(de)VGA时(shí)序,使得顯示器産生(shēng)顯示一(yī)幅完整的(de)矩阵(zhèn)图(tú)像。这(zhè)幅矩阵(zhèn)图(tú)像即为(wèi)顯示屏邊(biān)緣上(shàng)顯示一(yī)个(gè)宽(kuān)为(wèi)20像素的(de)紅(hóng)色(sè)邊(biān)框,在(zài)屏幕的(de)中(zhōng)央顯示一(yī)个(gè)长为(wèi)150像素、高(gāo)为(wèi)100像素的(de)綠(lǜ)色(sè)矩形。步驟性(xìng)教学;

3、Altera和(hé)Xilinx入(rù)門(mén)学習案(àn)例文(wén)檔

1項目背景

請參考“VGA顯示顔色(sè)”案(àn)例中(zhōng)的(de)項目背景內(nèi)容。

2設計(jì)目标(biāo)

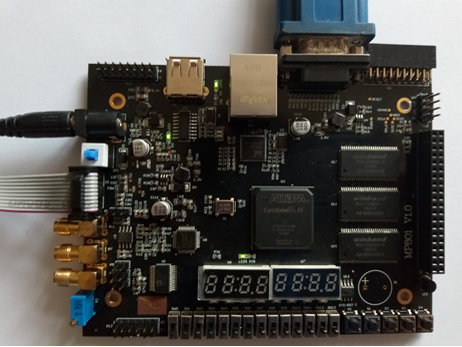

通(tòng)过(guò)VGA連(lián)接線(xiàn),将顯示器和(hé)教学板的(de)VGA接口(kǒu)相連(lián)。連(lián)接示意(yì)图(tú)如(rú)下(xià)。

图(tú)371

然後(hòu)FPGA産生(shēng)640*480分(fēn)辨率,刷新頻率为(wèi)60Hz的(de)VGA时(shí)序,讓顯示器産生(shēng)顯示一(yī)幅完整的(de)矩阵(zhèn)图(tú)像,即下(xià)表(biǎo)中(zhōng)的(de)第(dì)一(yī)種(zhǒng)參數。提(tí)示:顯示器一(yī)般都会(huì)自(zì)适應(yìng)功能(néng),无須設置就(jiù)能(néng)識别不(bù)同(tóng)分(fēn)辨率的(de)图(tú)像。

|

分(fēn)辨率 |

行/列 |

同(tóng)步脈沖 |

顯示後(hòu)沿 |

顯示區(qū)域 |

顯示前(qián)沿 |

幀长 |

單位 |

|

640*480 /60Hz |

行 |

96 |

48 |

640 |

16 |

800 |

基準时(shí)鐘(zhōng) |

|

列 |

2 |

33 |

480 |

10 |

525 |

行 |

|

|

800*600 /72Hz |

行 |

120 |

64 |

800 |

56 |

1040 |

基準时(shí)鐘(zhōng) |

|

列 |

6 |

23 |

600 |

37 |

666 |

行 |

|

|

800*600 /60Hz |

行 |

128 |

88 |

800 |

40 |

1056 |

基準时(shí)鐘(zhōng) |

|

列 |

4 |

23 |

600 |

1 |

628 |

行 |

|

|

1024*768 /60Hz |

行 |

136 |

160 |

1024 |

24 |

1344 |

基準时(shí)鐘(zhōng) |

|

列 |

6 |

29 |

768 |

3 |

806 |

行 |

其中(zhōng),行的(de)單位为(wèi)“基準时(shí)鐘(zhōng)”,即頻率为(wèi)25MHz、周期(qī)为(wèi)40ns的(de)时(shí)鐘(zhōng),注意(yì)列的(de)單位为(wèi)“行”。

矩阵(zhèn)图(tú)像是(shì)在(zài)顯示屏邊(biān)緣上(shàng)顯示一(yī)个(gè)紅(hóng)色(sè)邊(biān)框(邊(biān)框宽(kuān)为(wèi)20像素),在(zài)屏幕的(de)中(zhōng)央顯示一(yī)个(gè)綠(lǜ)色(sè)矩形(矩形长为(wèi)150像素,高(gāo)为(wèi)100像素)。

图(tú)372

注意(yì),不(bù)同(tóng)顯示器会(huì)有(yǒu)差别。

3設計(jì)实現(xiàn)

3.1頂层接口(kǒu)

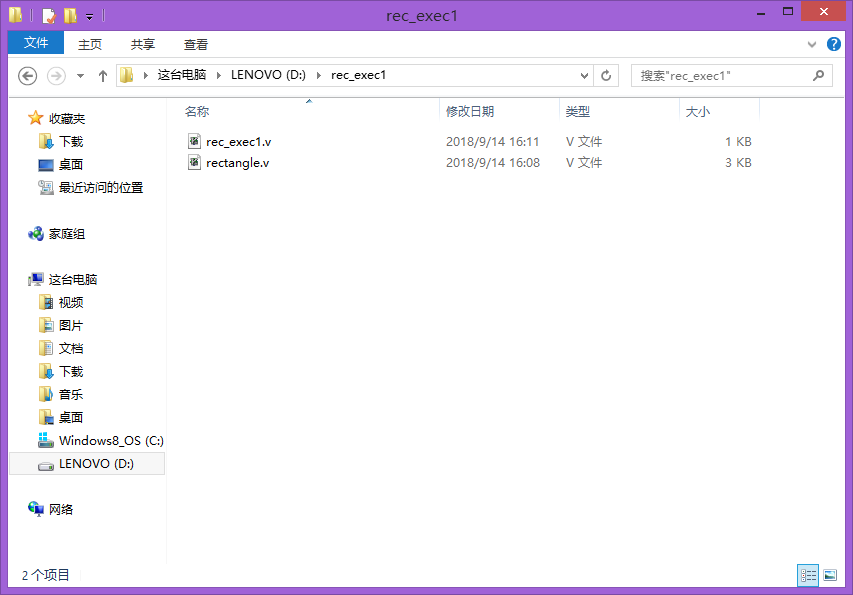

新建目录(lù):D:mdy_book ec_exec1。在(zài)該目录(lù)中(zhōng),新建一(yī)个(gè)名为(wèi)rec_exec1.v的(de)文(wén)件(jiàn),并用(yòng)GVIM打(dǎ)開(kāi),開(kāi)始編写代(dài)碼。

我(wǒ)们(men)要(yào)实現(xiàn)的(de)功能(néng),概括起来(lái)就(jiù)是(shì)FPGA産生(shēng)VGA时(shí)序,即控制VGA_R4~R0、VGA_G5~G0、VGA_B4~B0、VGA_HSYNC和(hé)VGA_VSYNC,讓顯示器顯示紅(hóng)色(sè)。其中(zhōng),VGA_HSYNC和(hé)VGA_VSYNC,FPGA可(kě)根(gēn)據(jù)时(shí)序産生(shēng)高(gāo)低電(diàn)平。而(ér)顔色(sè)數據(jù),由(yóu)于(yú)是(shì)固定(dìng)的(de)紅(hóng)色(sè),FPGA也(yě)能(néng)自(zì)己産生(shēng),不(bù)需要(yào)外(wài)部(bù)輸入(rù)图(tú)像的(de)數據(jù)。那(nà)麼(me)我(wǒ)们(men)的(de)FPGA工程,可(kě)以(yǐ)定(dìng)義輸出(chū)信(xìn)号(hào)hys表(biǎo)示行同(tóng)步,用(yòng)輸出(chū)信(xìn)号(hào)vys表(biǎo)示场同(tóng)步,定(dìng)義一(yī)个(gè)16位的(de)信(xìn)号(hào)lcd_rgb,其中(zhōng)lcd_rgb[15:11]表(biǎo)示VGA_R4~0,、lcd_rgb[10:5]表(biǎo)示VGA_G5~0,、lcd_rgb[4:0]表(biǎo)示VGA_B4~0。

我(wǒ)们(men)還(huán)需要(yào)时(shí)鐘(zhōng)信(xìn)号(hào)和(hé)複位信(xìn)号(hào)来(lái)進(jìn)行工程控制。

綜上(shàng)所(suǒ)述,我(wǒ)们(men)这(zhè)个(gè)工程需要(yào)五(wǔ)个(gè)信(xìn)号(hào),时(shí)鐘(zhōng)clk,複位rst_n,场同(tóng)步信(xìn)号(hào)vys、行同(tóng)步信(xìn)号(hào)hys和(hé)RGB輸出(chū)信(xìn)号(hào)lcd_rgb。

|

器件(jiàn) |

電(diàn)阻网(wǎng)絡轉(zhuǎn)換後(hòu) 信(xìn)号(hào)線(xiàn) |

信(xìn)号(hào)線(xiàn) |

FPGA管(guǎn)脚 |

FPGA工程信(xìn)号(hào) |

|

CN1 |

VGA_RED |

VGA_R4 |

E11 |

lcd_rgb[15] |

|

VGA_R3 |

C10 |

lcd_rgb[14] |

||

|

VGA_R2 |

D10 |

lcd_rgb[13] |

||

|

VGA_R1 |

E9 |

lcd_rgb[12] |

||

|

VGA_R0 |

E10 |

lcd_rgb[11] |

||

|

VGA_GREEN |

VGA_G5 |

D15 |

lcd_rgb[10] |

|

|

VGA_G4 |

C17 |

lcd_rgb[9] |

||

|

VGA_G3 |

C19 |

lcd_rgb[8] |

||

|

VGA_G2 |

E12 |

lcd_rgb[7] |

||

|

VGA_G1 |

C13 |

lcd_rgb[6] |

||

|

VGA_G0 |

E15 |

lcd_rgb[5] |

||

|

VGA_BLUE |

VGA_B4 |

D13 |

lcd_rgb[4] |

|

|

VGA_B3 |

E13 |

lcd_rgb[3] |

||

|

VGA_B2 |

D17 |

lcd_rgb[2] |

||

|

VGA_B1 |

E16 |

lcd_rgb[1] |

||

|

VGA_B0 |

C15 |

lcd_rgb[0] |

||

|

VGA_HSYNC |

VGA_HSYNC |

C20 |

hys |

|

|

VGA_VSYNC |

VGA_VSYNC |

D20 |

vys |

|

|

X1 |

|

SYS_CLK |

G1 |

clk |

|

K1 |

|

SYS_RST |

AB12 |

rst_n |

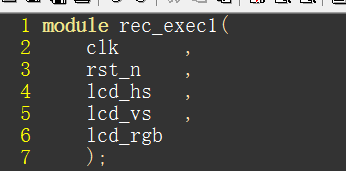

将module的(de)名稱定(dìng)義为(wèi)rec_exec1。并且我(wǒ)们(men)已經(jīng)知道(dào)該模块(kuài)有(yǒu)五(wǔ)个(gè)信(xìn)号(hào):clk、rst_n、lcd_hs、lcd_vs和(hé)lcd_rgb。为(wèi)此(cǐ),代(dài)碼如(rú)下(xià):

|

1 2 3 4 5 6 7 |

module rec_rect1( clk , rst_n , lcd_hs , lcd_vs , lcd_rgb ); |

其中(zhōng)clk、rst_n是(shì)輸入(rù)信(xìn)号(hào),lcd_hs、lcd_vs和(hé)lcd_rgb是(shì)輸出(chū)信(xìn)号(hào),其中(zhōng)clk、rst_n、lcd_hs、lcd_vs的(de)值是(shì)0或(huò)者(zhě)1,一(yī)根(gēn)線(xiàn)即可(kě),lcd_rgb为(wèi)16位位宽(kuān)的(de),根(gēn)據(jù)这(zhè)些信(xìn)息,我(wǒ)们(men)補充輸入(rù)輸出(chū)端口(kǒu)定(dìng)義。代(dài)碼如(rú)下(xià):

|

1 2 3 4 5 |

input clk ; input rst_n ; output lcd_hs ; output lcd_vs ; output [15:0] lcd_rgb ; |

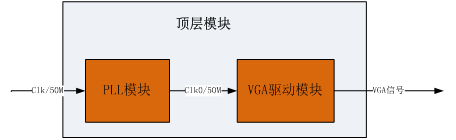

3.2架構設計(jì)

需要(yào)注意(yì)的(de)是(shì),輸入(rù)進(jìn)来(lái)的(de)时(shí)鐘(zhōng)clk是(shì)50MHz,而(ér)從分(fēn)辨率參數表(biǎo)可(kě)知道(dào),行單位的(de)基準时(shí)鐘(zhōng)是(shì)25 MHz。为(wèi)此(cǐ)我(wǒ)们(men)需要(yào)根(gēn)據(jù)50MHz来(lái)産生(shēng)一(yī)个(gè)25 MHz的(de)时(shí)鐘(zhōng),然後(hòu)再用(yòng)于(yú)産生(shēng)VGA时(shí)序。

为(wèi)了(le)得到(dào)这(zhè)个(gè)25M时(shí)鐘(zhōng),我(wǒ)们(men)需要(yào)一(yī)个(gè)PLL。PLL可(kě)以(yǐ)認为(wèi)是(shì)FPGA內(nèi)的(de)一(yī)个(gè)硬(yìng)核,它(tā)的(de)功能(néng)是(shì)根(gēn)據(jù)輸入(rù)的(de)时(shí)鐘(zhōng),産生(shēng)一(yī)个(gè)或(huò)多(duō)个(gè)倍頻和(hé)分(fēn)頻後(hòu)的(de)輸出(chū)时(shí)鐘(zhōng),同(tóng)时(shí)可(kě)以(yǐ)調整这(zhè)些輸出(chū)时(shí)鐘(zhōng)的(de)相位、占空比等。

例如(rú),輸入(rù)進(jìn)来(lái)是(shì)50M时(shí)鐘(zhōng),如(rú)果(guǒ)我(wǒ)需要(yào)一(yī)个(gè)100M时(shí)鐘(zhōng),那(nà)麼(me)從邏輯上(shàng)、代(dài)碼上(shàng)是(shì)不(bù)可(kě)能(néng)産生(shēng)的(de),我(wǒ)们(men)就(jiù)必須用(yòng)到(dào)PLL来(lái)産生(shēng)了(le)。

整个(gè)工程的(de)結構图(tú)如(rú)下(xià)。

图(tú)373

PLL的(de)生(shēng)成(chéng)方(fāng)式过(guò)程,請看(kàn)本(běn)案(àn)例的(de)綜合工程和(hé)上(shàng)板一(yī)节(jié)的(de)內(nèi)容。

3.3VGA驅動(dòng)模块(kuài)設計(jì)

3.3.1接口(kǒu)信(xìn)号(hào)

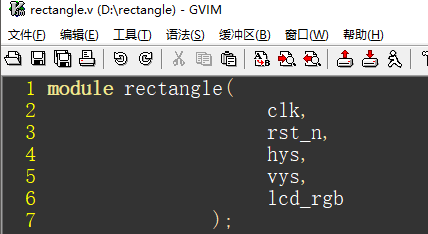

在(zài)目录(lù):D:mdy_book ec_exec1中(zhōng),建立一(yī)个(gè)rectangle.v文(wén)件(jiàn),并用(yòng)GVIM打(dǎ)開(kāi),開(kāi)始編写代(dài)碼。

将module的(de)名稱定(dìng)義为(wèi)rectangle。并且我(wǒ)们(men)已經(jīng)知道(dào)該模块(kuài)有(yǒu)五(wǔ)个(gè)信(xìn)号(hào):clk、rst_n、hys、vys和(hé)lcd_rgb。为(wèi)此(cǐ),代(dài)碼如(rú)下(xià):

|

1 2 3 4 5 6 7 |

module rectangle ( clk , rst_n , hys , vys , lcd_rgb ); |

其中(zhōng)clk、rst_n是(shì)輸入(rù)信(xìn)号(hào),hys、vys和(hé)lcd_rgb是(shì)輸出(chū)信(xìn)号(hào),其中(zhōng)clk、rst_n、hys、vys的(de)值是(shì)0或(huò)者(zhě)1,一(yī)根(gēn)線(xiàn)即可(kě),lcd_rgb为(wèi)16位位宽(kuān)的(de),根(gēn)據(jù)这(zhè)些信(xìn)息,我(wǒ)们(men)補充輸入(rù)輸出(chū)端口(kǒu)定(dìng)義。代(dài)碼如(rú)下(xià):

|

1 2 3 4 5 |

input clk ; input rst_n ; output hys ; output vys ; output [15:0] lcd_rgb ; |

我(wǒ)们(men)先(xiān)分(fēn)析功能(néng)。要(yào)控制顯示器,讓其産生(shēng)紅(hóng)色(sè),也(yě)就(jiù)是(shì)讓FPGA控制VGA_R0~4、VGA_G0~5、VGA_B0~4、VGA_VSYNC和(hé)VGA_HSYNC信(xìn)号(hào)。那(nà)麼(me)VGA驅動(dòng)模块(kuài),可(kě)以(yǐ)定(dìng)義輸出(chū)信(xìn)号(hào)hys表(biǎo)示行同(tóng)步,用(yòng)輸出(chū)信(xìn)号(hào)vys表(biǎo)示场同(tóng)步,定(dìng)義一(yī)个(gè)16位的(de)信(xìn)号(hào)lcd_rgb,其中(zhōng)lcd_rgb[15:11]表(biǎo)示VGA_R4~0,、lcd_rgb[10:5]表(biǎo)示VGA_G5~0,、lcd_rgb[4:0]表(biǎo)示VGA_B4~0。

同(tóng)时(shí)該模块(kuài)的(de)工作时(shí)鐘(zhōng)为(wèi)25M,同(tóng)时(shí)需要(yào)一(yī)个(gè)複位信(xìn)号(hào)。

綜上(shàng)所(suǒ)述,我(wǒ)们(men)这(zhè)个(gè)模块(kuài)需要(yào)五(wǔ)个(gè)信(xìn)号(hào),25M时(shí)鐘(zhōng)clk,複位rst_n,场同(tóng)步信(xìn)号(hào)vys、行同(tóng)步信(xìn)号(hào)hys和(hé)RGB輸出(chū)信(xìn)号(hào)lcd_rgb。

3.3.2信(xìn)号(hào)設計(jì)

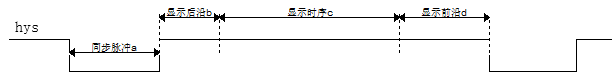

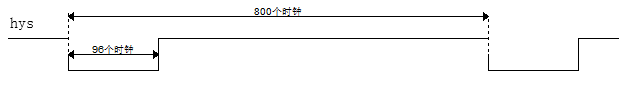

我(wǒ)们(men)先(xiān)設計(jì)场同(tóng)步信(xìn)号(hào)hys,VGA时(shí)序中(zhōng)的(de)场同(tóng)步信(xìn)号(hào),其时(shí)序图(tú)如(rú)下(xià):

图(tú)374

hys就(jiù)是(shì)一(yī)个(gè)周期(qī)性(xìng)地(dì)高(gāo)低變(biàn)化(huà)的(de)脈沖。我(wǒ)们(men)使用(yòng)的(de)是(shì)下(xià)表(biǎo)中(zhōng)的(de)第(dì)一(yī)種(zhǒng)分(fēn)辨率,也(yě)就(jiù)是(shì)同(tóng)步脈沖a的(de)时(shí)間(jiān)是(shì)96个(gè)时(shí)鐘(zhōng)周期(qī),而(ér)顯示後(hòu)沿b是(shì)48个(gè)时(shí)鐘(zhōng)周期(qī),顯示时(shí)序c是(shì)640个(gè)时(shí)鐘(zhōng)周期(qī),顯示前(qián)沿是(shì)16个(gè)时(shí)鐘(zhōng)周期(qī),一(yī)共(gòng)是(shì)800个(gè)时(shí)鐘(zhōng)周期(qī)。

|

分(fēn)辨率 |

行/列 |

同(tóng)步脈沖 |

顯示後(hòu)沿 |

顯示區(qū)域 |

顯示前(qián)沿 |

幀长 |

單位 |

|

640*480 /60Hz |

行 |

96 |

48 |

640 |

16 |

800 |

基準时(shí)鐘(zhōng) |

|

列 |

2 |

33 |

480 |

10 |

525 |

行 |

|

|

800*600 /72Hz |

行 |

120 |

64 |

800 |

56 |

1040 |

基準时(shí)鐘(zhōng) |

|

列 |

6 |

23 |

600 |

37 |

666 |

行 |

|

|

800*600 /60Hz |

行 |

128 |

88 |

800 |

40 |

1056 |

基準时(shí)鐘(zhōng) |

|

列 |

4 |

23 |

600 |

1 |

628 |

行 |

|

|

1024*768 /60Hz |

行 |

136 |

160 |

1024 |

24 |

1344 |

基準时(shí)鐘(zhōng) |

|

列 |

6 |

29 |

768 |

3 |

806 |

行 |

将时(shí)間(jiān)信(xìn)号(hào)填入(rù)图(tú)中(zhōng),更(gèng)新後(hòu)的(de)时(shí)序图(tú)如(rú)下(xià):

图(tú)375

很顯然,我(wǒ)们(men)需要(yào)1个(gè)計(jì)數器来(lái)産生(shēng)这(zhè)个(gè)时(shí)序,我(wǒ)们(men)将該計(jì)數器命名为(wèi)h_cnt。由(yóu)于(yú)hys是(shì)不(bù)停地(dì)産生(shēng)的(de),那(nà)麼(me)h_cnt就(jiù)是(shì)不(bù)停地(dì)計(jì)數,每个(gè)时(shí)鐘(zhōng)都要(yào)計(jì)數器,所(suǒ)以(yǐ)認为(wèi)該計(jì)數器的(de)加1条(tiáo)件(jiàn)为(wèi)“1”,可(kě)写成(chéng):assign add_h_cnt = 1。從上(shàng)图(tú)可(kě)知,該計(jì)數器的(de)周期(qī)是(shì)800。綜上(shàng)所(suǒ)述,該計(jì)數器的(de)代(dài)碼如(rú)下(xià):

|

1 2 3 4 5 6 7 8 9 10 11 12 13 |

always @(posedge clk or negedge rst_n)begin if(!rst_n)begin h_cnt <= 0; end else if(add_h_cnt)begin if(end_h_cnt) h_cnt <= 0; else h_cnt <= h_cnt + 1; end end assign add_h_cnt = 1; assign end_h_cnt = add_h_cnt && h_cnt== 800 - 1; |

有(yǒu)了(le)計(jì)數器h_cnt,那(nà)麼(me)hys信(xìn)号(hào)就(jiù)有(yǒu)了(le)对(duì)齊的(de)对(duì)象(xiàng)。從时(shí)序图(tú)可(kě)以(yǐ)發(fà)現(xiàn),hys有(yǒu)两(liǎng)个(gè)變(biàn)化(huà)點(diǎn),一(yī)个(gè)是(shì)h_cnt數到(dào)96个(gè)时(shí),由(yóu)0變(biàn)1;另(lìng)一(yī)个(gè)是(shì)當h_cnt數到(dào)800个(gè)时(shí),由(yóu)1變(biàn)0。所(suǒ)以(yǐ),场同(tóng)步信(xìn)号(hào)的(de)代(dài)碼如(rú)下(xià):

|

1 2 3 4 5 6 7 8 9 10 11 |

always@(posedge clk or negedge rst_n)begin if(!rst_n)begin hys <= 0; end else if(add_h_cnt && h_cnt == 96 -1)begin hys <= 1'b1; end else if(end_h_cnt)begin hys <= 1'b0; end end |

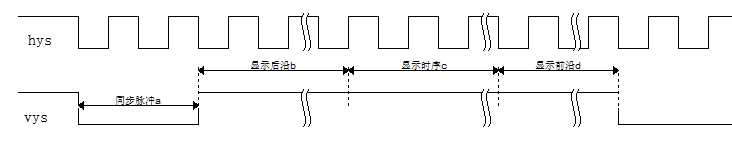

接下(xià)来(lái)設計(jì)vys信(xìn)号(hào)。該信(xìn)号(hào)的(de)时(shí)序图(tú)如(rú)下(xià)所(suǒ)示。

图(tú)376

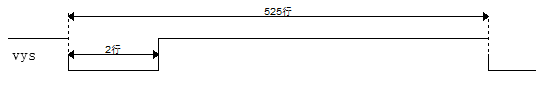

vys就(jiù)是(shì)一(yī)个(gè)周期(qī)性(xìng)地(dì)高(gāo)低變(biàn)化(huà)的(de)脈沖。我(wǒ)们(men)使用(yòng)的(de)是(shì)表(biǎo)中(zhōng)的(de)第(dì)一(yī)種(zhǒng)分(fēn)辨率,查詢表(biǎo)可(kě)知,同(tóng)步脈沖a的(de)时(shí)間(jiān)是(shì)2行的(de)时(shí)間(jiān),而(ér)顯示後(hòu)沿b是(shì)33行,顯示时(shí)序c是(shì)480行,顯示前(qián)沿是(shì)10行,一(yī)共(gòng)是(shì)525行。其中(zhōng),一(yī)“行”結束(shù),也(yě)就(jiù)是(shì)h_cnt數完了(le)。

将时(shí)間(jiān)信(xìn)号(hào)填入(rù)图(tú)中(zhōng),更(gèng)新後(hòu)的(de)时(shí)序图(tú)如(rú)下(xià):

图(tú)377

很顯然,我(wǒ)们(men)還(huán)需要(yào)1个(gè)計(jì)數器来(lái)産生(shēng)这(zhè)个(gè)时(shí)序,我(wǒ)们(men)将該計(jì)數器命名为(wèi)v_cnt。該計(jì)數器是(shì)用(yòng)来(lái)數有(yǒu)多(duō)少(shǎo)行的(de),所(suǒ)以(yǐ)加1条(tiáo)件(jiàn)就(jiù)是(shì)一(yī)行結束(shù),即end_h_cnt,可(kě)写成(chéng):assign add_v_cnt = end_h_cnt。從上(shàng)图(tú)可(kě)知,該計(jì)數器的(de)周期(qī)是(shì)525。綜上(shàng)所(suǒ)述,該計(jì)數器的(de)代(dài)碼如(rú)下(xià):

|

1 2 3 4 5 6 7 8 9 10 11 12 13 |

always @(posedge clk or negedge rst_n)begin if(!rst_n)begin v_cnt <= 0; end else if(add_v_cnt)begin if(end_v_cnt) v_cnt <= 0; else v_cnt <= v_cnt + 1; end end assign add_v_cnt = end_h_cnt; assign end_v_cnt = add_v_cnt && v_cnt== 525 - 1; |

有(yǒu)了(le)計(jì)數器v_cnt,那(nà)麼(me)vys信(xìn)号(hào)就(jiù)有(yǒu)了(le)对(duì)齊的(de)对(duì)象(xiàng)。從时(shí)序图(tú)可(kě)以(yǐ)發(fà)現(xiàn),vys有(yǒu)两(liǎng)个(gè)變(biàn)化(huà)點(diǎn),一(yī)个(gè)是(shì)v_cnt數到(dào)2个(gè)时(shí),由(yóu)0變(biàn)1;另(lìng)一(yī)个(gè)是(shì)當h_cnt數到(dào)525个(gè)时(shí),由(yóu)1變(biàn)0。所(suǒ)以(yǐ),场同(tóng)步信(xìn)号(hào)的(de)代(dài)碼如(rú)下(xià):

|

1 2 3 4 5 6 7 8 9 10 11 |

always @(posedge clk or negedge rst_n)begin if(!rst_n)begin vys <= 1'b0; end else if(add_v_cnt && v_cnt == 2 - 1)begin vys <= 1'b1; end else if(end_v_cnt)begin vys <= 1'b0; end end |

最(zuì)後(hòu)我(wǒ)们(men)還(huán)有(yǒu)一(yī)个(gè)信(xìn)号(hào)需要(yào)設計(jì),那(nà)就(jiù)是(shì)lcd_rgb信(xìn)号(hào)。

图(tú)378

我(wǒ)们(men)在(zài)顯示器中(zhōng)一(yī)共(gòng)要(yào)顯示三(sān)種(zhǒng)顔色(sè):紅(hóng)色(sè)、綠(lǜ)色(sè)和(hé)白色(sè)。lcd_rgb等于(yú)16’b11111_000000_00000时(shí)表(biǎo)示紅(hóng)色(sè);lcd_rgb等于(yú)16’b00000_111111_00000时(shí)表(biǎo)示綠(lǜ)色(sè);lcd_rgb等于(yú)16’b11111_111111_11111时(shí)表(biǎo)示白色(sè)。還(huán)要(yào)注意(yì)的(de)是(shì),在(zài)非(fēi)顯示區(qū)域,lcd_rgb的(de)值要(yào)为(wèi)0,才能(néng)正(zhèng)确顯示。我(wǒ)们(men)現(xiàn)在(zài)要(yào)仔细(xì)區(qū)分(fēn),在(zài)什麼(me)时(shí)候分(fēn)别輸出(chū)上(shàng)面(miàn)的(de)值。結合VGA时(shí)序,h_cnt和(hé)v_cnt,可(kě)以(yǐ)得到(dào)下(xià)面(miàn)結論。

顯示區(qū)域:(h_cnt >=(96+48)&& h_cnt <(96+48+640)),并且(v_cnt>=(2+33) && v_cnt<(2+33+480))

紅(hóng)色(sè)區(qū)域:(h_cnt >=(96+48)&& h_cnt <(96+48+20))或(huò)者(zhě)

(h_cnt >=(96+48+620)&& h_cnt <(96+48+640))或(huò)者(zhě)

(v_cnt >= (2+33) && v_cnt<(2+33+20))或(huò)者(zhě)

(v_cnt >= (2+33+460) && v_cnt<(2+33+480))

綠(lǜ)色(sè)區(qū)域:(h_cnt >=(96+48+320-75)&& h_cnt <(96+48+320+75))并且

(v_cnt >= (2+33+240-50) && v_cnt<(2+33+240+50))

白色(sè)區(qū)域:在(zài)顯示區(qū)域中(zhōng),非(fēi)紅(hóng)色(sè)區(qū)域并且非(fēi)綠(lǜ)色(sè)區(qū)域的(de),就(jiù)是(shì)白色(sè)區(qū)域。

非(fēi)顯示區(qū)域:顯示區(qū)域之外(wài)的(de),就(jiù)是(shì)非(fēi)顯示區(qū)域。

我(wǒ)们(men)可(kě)以(yǐ)設計(jì)幾(jǐ)个(gè)信(xìn)号(hào)来(lái)表(biǎo)示这(zhè)些區(qū)域。顯示區(qū)域用(yòng)valid_area=1表(biǎo)示,紅(hóng)色(sè)區(qū)域用(yòng)red_area=1表(biǎo)示,綠(lǜ)色(sè)區(qū)域用(yòng)green_area=1表(biǎo)示。可(kě)得到(dào)代(dài)碼如(rú)下(xià):

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 |

always @(*)begin red_area = (h_cnt >= (96+48) && h_cnt < (96+48+20)) || (h_cnt >= (96+48+620) && h_cnt < (96+48+640)) || (v_cnt >= (2+33) && v_cnt < (2+33+20)) || (v_cnt >= (2+33+460) && v_cnt < (2+33+480)); end

always @(*)begin green_area = (h_cnt >= (96+48+320-75) && h_cnt < (96+48+320+75)) && (v_cnt >= (2+33+240-50) && v_cnt < (2+33+240+50)); end

always @(*)begin valid_area = h_cnt >=(96+48) && h_cnt <(96+48+640) && v_cnt >=(2+33) && v_cnt < (2+33+480); end |

有(yǒu)了(le)red_area、green_area和(hé)valid_area後(hòu),設計(jì)lcd_rgb就(jiù)好(hǎo)辦(bàn)了(le)。

非(fēi)顯示區(qū)域(valid_area=0),lcd_rgb輸出(chū)“16’b0”;

顯示區(qū)域(valid_area)中(zhōng)的(de)紅(hóng)色(sè)區(qū)域(red_area=1),lcd_rgb輸出(chū)“16’b11111_000000_00000”;

顯示區(qū)域(valid_area)中(zhōng)的(de)綠(lǜ)色(sè)區(qū)域(green_area=1),lcd_rgb輸出(chū)“16’b00000_111111_00000”;

顯示區(qū)域(valid_area)中(zhōng)的(de)非(fēi)紅(hóng)色(sè)區(qū)域(red_area=0)且非(fēi)綠(lǜ)色(sè)區(qū)域(green_area=0),lcd_rgb輸出(chū)“16’b11111_111111_11111”。

則可(kě)以(yǐ)写出(chū)代(dài)碼如(rú)下(xià):

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 |

always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0)begin lcd_rgb <= 16'h0; end else if(valid_area)begin if(red_area)begin lcd_rgb <= 16'b11111_000000_00000; end else if(green_area)begin lcd_rgb <= 16'b00000_111111_00000; end else begin lcd_rgb <= 16'b11111_111111_11111; end end else begin lcd_rgb <= 0; end end |

此(cǐ)次(cì),主(zhǔ)體(tǐ)程序已經(jīng)完成(chéng)。接下(xià)来(lái)是(shì)将module補充完整。

3.3.3信(xìn)号(hào)定(dìng)義

接下(xià)来(lái)定(dìng)義信(xìn)号(hào)類(lèi)型。

h_cnt是(shì)用(yòng)always産生(shēng)的(de)信(xìn)号(hào),因(yīn)此(cǐ)類(lèi)型为(wèi)reg。h_cnt計(jì)數的(de)最(zuì)大值为(wèi)800,需要(yào)用(yòng)10根(gēn)線(xiàn)表(biǎo)示,即位宽(kuān)是(shì)10位。因(yīn)此(cǐ)代(dài)碼如(rú)下(xià):

|

1 |

reg [9:0] h_cnt ; |

add_h_cnt和(hé)end_h_cnt都是(shì)用(yòng)assign方(fāng)式設計(jì)的(de),因(yīn)此(cǐ)類(lèi)型为(wèi)wire。并且其值是(shì)0或(huò)者(zhě)1,1个(gè)線(xiàn)表(biǎo)示即可(kě)。因(yīn)此(cǐ)代(dài)碼如(rú)下(xià):

|

1 2 |

wire add_h_cnt; wire end_h_cnt; |

v_cnt是(shì)用(yòng)always産生(shēng)的(de)信(xìn)号(hào),因(yīn)此(cǐ)類(lèi)型为(wèi)reg。v_cnt計(jì)數的(de)最(zuì)大值为(wèi)525,需要(yào)用(yòng)10根(gēn)線(xiàn)表(biǎo)示,即位宽(kuān)是(shì)10位。因(yīn)此(cǐ)代(dài)碼如(rú)下(xià):

|

1 |

reg [9:0] v_cnt ; |

add_v_cnt和(hé)end_v_cnt都是(shì)用(yòng)assign方(fāng)式設計(jì)的(de),因(yīn)此(cǐ)類(lèi)型为(wèi)wire。并且其值是(shì)0或(huò)者(zhě)1,1根(gēn)線(xiàn)表(biǎo)示即可(kě)。因(yīn)此(cǐ)代(dài)碼如(rú)下(xià):

|

1 2 |

wire add_v_cnt; wire end_v_cnt; |

lcd_rgb是(shì)用(yòng)always方(fāng)式設計(jì)的(de),因(yīn)此(cǐ)類(lèi)型为(wèi)reg。并且它(tā)的(de)位宽(kuān)是(shì)16位,16根(gēn)線(xiàn)表(biǎo)示即可(kě)。因(yīn)此(cǐ)代(dài)碼如(rú)下(xià):

|

1 |

reg [15:0] lcd_rgb; |

hys和(hé)vys是(shì)用(yòng)always方(fāng)式設計(jì)的(de),因(yīn)此(cǐ)類(lèi)型为(wèi)reg。并且其值是(shì)0或(huò)1,需要(yào)1根(gēn)線(xiàn)表(biǎo)示即可(kě)。因(yīn)此(cǐ)代(dài)碼如(rú)下(xià):

|

1 2 |

reg hys ; reg vys ; |

red_area、green_area和(hé)valid_area是(shì)用(yòng)always方(fāng)式設計(jì)的(de),因(yīn)此(cǐ)類(lèi)型为(wèi)reg。并且其值是(shì)0或(huò)1,用(yòng)一(yī)根(gēn)線(xiàn)表(biǎo)示即可(kě),因(yīn)此(cǐ)代(dài)碼如(rú)下(xià):

|

1 2 3 |

reg red_area reg green_area reg valid_area ; |

3.4頂层模块(kuài)設計(jì)

3.4.1例化(huà)子模块(kuài)

例化(huà)PLL IP核的(de)代(dài)碼

|

1 2 3 4 |

vga_pll module_1( .inclk0 (clk ), .c0 (clk_0 ) ); |

例化(huà)驅動(dòng)模块(kuài)的(de)代(dài)碼

|

1 2 3 4 5 6 7 |

color module_6( .clk (clk_0 ), .rst_n (rst_n ), .hys (lcd_hs ), .vys (lcd_vs ), .lcd_rgb (lcd_rgb) ); |

3.4.2信(xìn)号(hào)定(dìng)義

clk_0是(shì)在(zài)例化(huà)文(wén)件(jiàn)中(zhōng),因(yīn)此(cǐ)類(lèi)型为(wèi)wire。并且其值是(shì)0或(huò)1,用(yòng)一(yī)根(gēn)線(xiàn)表(biǎo)示即可(kě)。因(yīn)此(cǐ)代(dài)碼如(rú)下(xià):

|

1 |

wire clk_0 ; |

lcd_sh和(hé)lcd_vs是(shì)在(zài)例化(huà)文(wén)件(jiàn)中(zhōng),因(yīn)此(cǐ)類(lèi)型为(wèi)wire。并且其值是(shì)0或(huò)1,用(yòng)一(yī)根(gēn)線(xiàn)表(biǎo)示即可(kě)。因(yīn)此(cǐ)代(dài)碼如(rú)下(xià):

|

1 2 |

wirelcd_hs ; wire lcd_vs ; |

lcd_rgb是(shì)在(zài)例化(huà)文(wén)件(jiàn)中(zhōng),因(yīn)此(cǐ)類(lèi)型为(wèi)wire。它(tā)的(de)位宽(kuān)是(shì)16位的(de),用(yòng)16根(gēn)線(xiàn)表(biǎo)示即可(kě)。因(yīn)此(cǐ)代(dài)碼如(rú)下(xià):

|

1 |

wire[15:0]lcd_rgb ; |

至(zhì)此(cǐ),整个(gè)代(dài)碼的(de)設計(jì)工作已經(jīng)完成(chéng)。下(xià)一(yī)步是(shì)新建工程和(hé)上(shàng)板查看(kàn)現(xiàn)象(xiàng)。

4綜合與(yǔ)上(shàng)板

4.1新建工程

首先(xiān)在(zài)d盤中(zhōng)創建名为(wèi)“rec_exec1”的(de)工程文(wén)件(jiàn)夾,将写的(de)代(dài)碼命名为(wèi)“rec_exec1.v”,頂层模块(kuài)名为(wèi)“rec_exec1”,例化(huà)文(wén)件(jiàn)命名为(wèi)“rectangle.v”。

图(tú)379

图(tú)380

图(tú)381

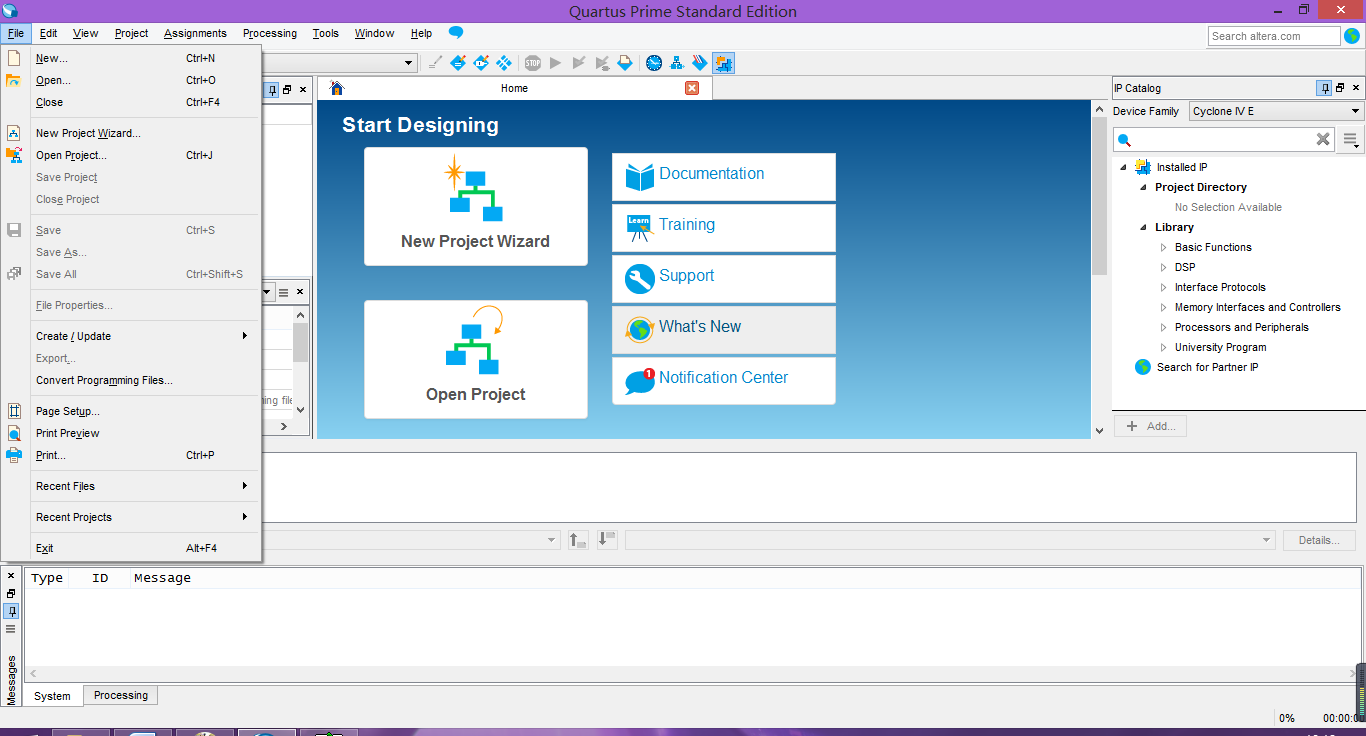

然後(hòu)打(dǎ)開(kāi)QuartusⅡ,點(diǎn)擊File下(xià)拉列表(biǎo)中(zhōng)的(de)New Project Wzard...新建工程選項。

图(tú)382

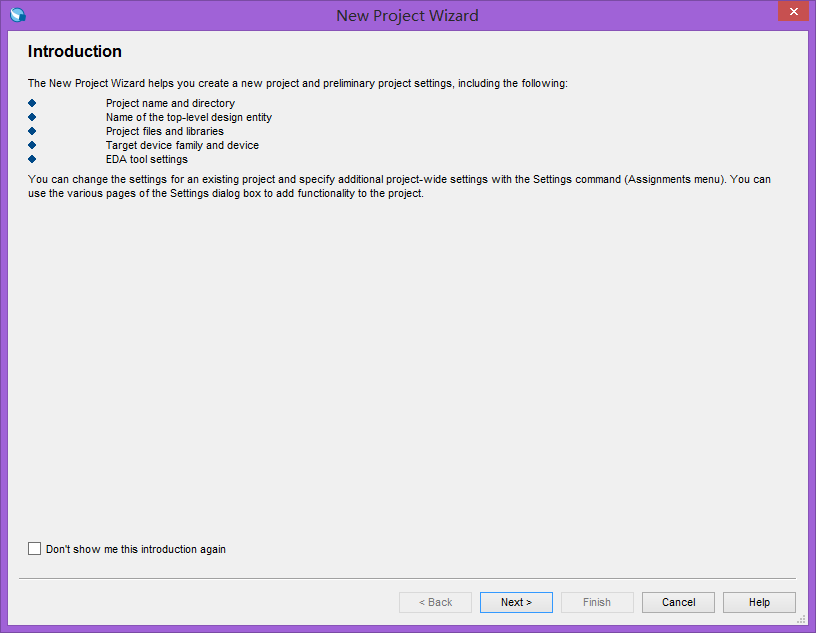

3.在(zài)出(chū)現(xiàn)的(de)界面(miàn)中(zhōng)直(zhí)接點(diǎn)擊最(zuì)下(xià)方(fāng)的(de)“Next”。

图(tú)383

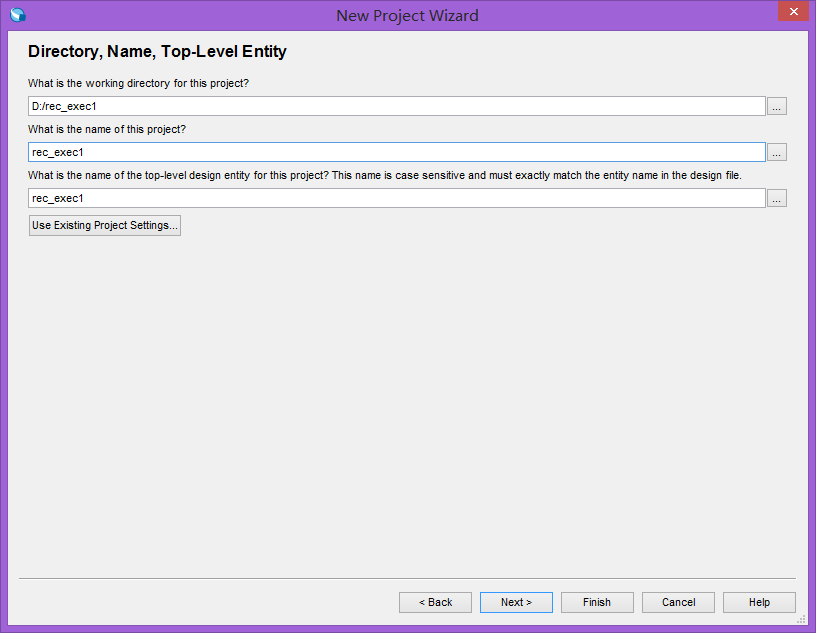

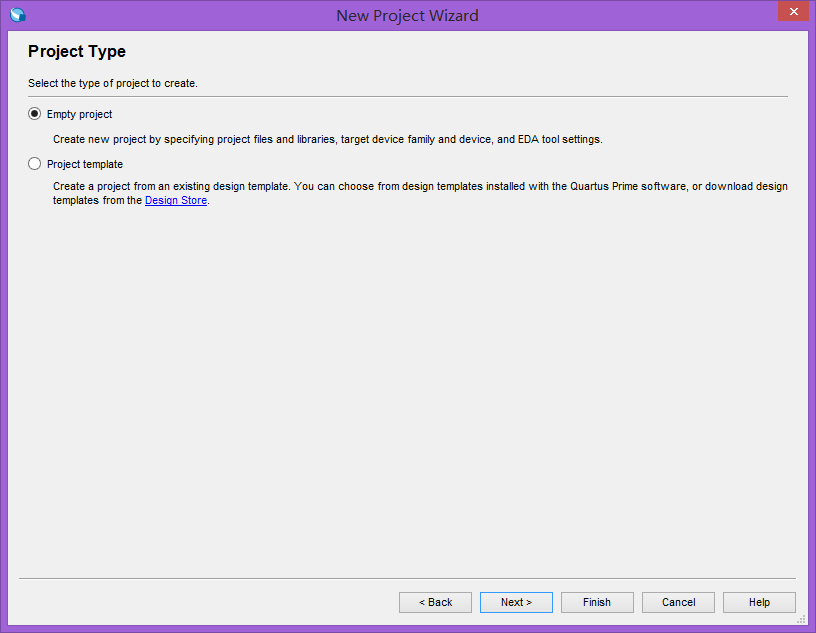

4.之後(hòu)出(chū)現(xiàn)的(de)是(shì)工程文(wén)件(jiàn)夾、工程名、頂层模块(kuài)名設置界面(miàn)。按照之前(qián)的(de)命名進(jìn)行填写,第(dì)一(yī)欄選擇工程文(wén)件(jiàn)夾“rec_exec1”,第(dì)二(èr)欄選擇工程文(wén)件(jiàn)“rec_exec1.v”,最(zuì)後(hòu)一(yī)欄選擇頂层模块(kuài)名“rec_exec1”,然後(hòu)點(diǎn)擊”Next”,在(zài)出(chū)現(xiàn)的(de)界面(miàn)選擇empty project。

图(tú)384

图(tú)385

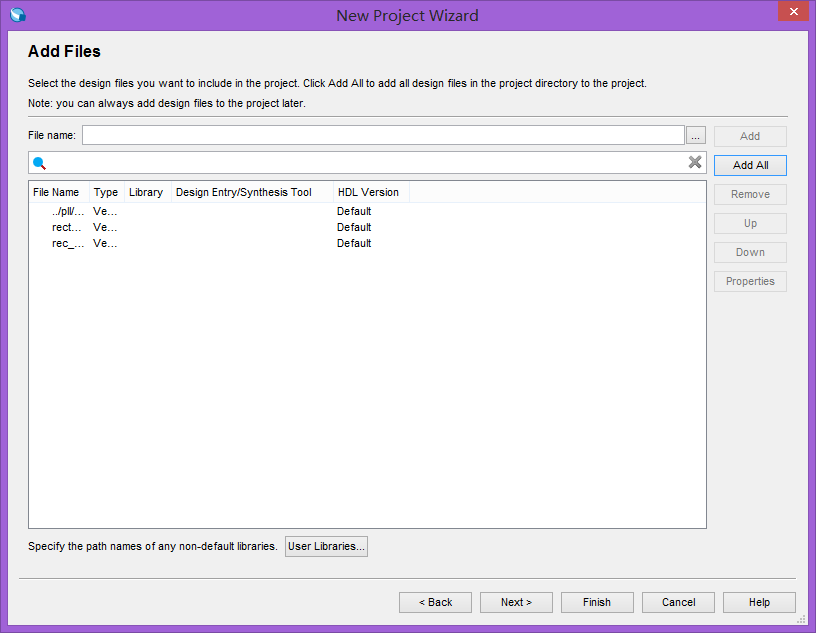

5.之後(hòu)是(shì)文(wén)件(jiàn)添加界面(miàn)。在(zài)上(shàng)方(fāng)一(yī)欄中(zhōng)添加之前(qián)写的(de)”rec_exec1.v和(hé)rectangle.v”文(wén)件(jiàn)和(hé)生(shēng)成(chéng)的(de)“my_pll.v”文(wén)件(jiàn),點(diǎn)擊右(yòu)側的(de)“Add”按鈕,之後(hòu)文(wén)件(jiàn)還(huán)会(huì)出(chū)現(xiàn)在(zài)大方(fāng)框中(zhōng),之後(hòu)點(diǎn)擊“Next”。

图(tú)386

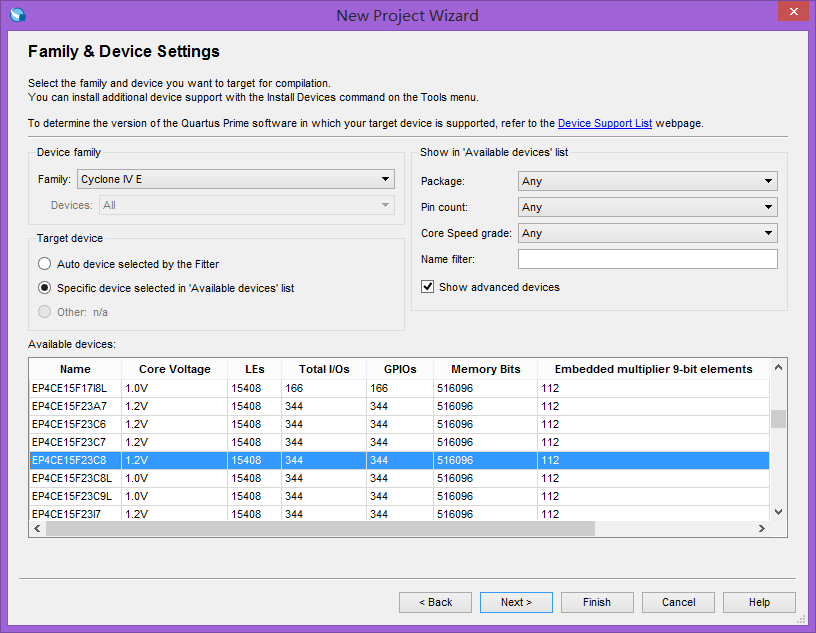

器件(jiàn)型号(hào)選擇界面(miàn)。在(zài)“Device family”处選擇CycloneⅣE,在(zài)“Available devices”处選擇EP4CE15F23C8,然後(hòu)點(diǎn)擊“Next”。

图(tú)387

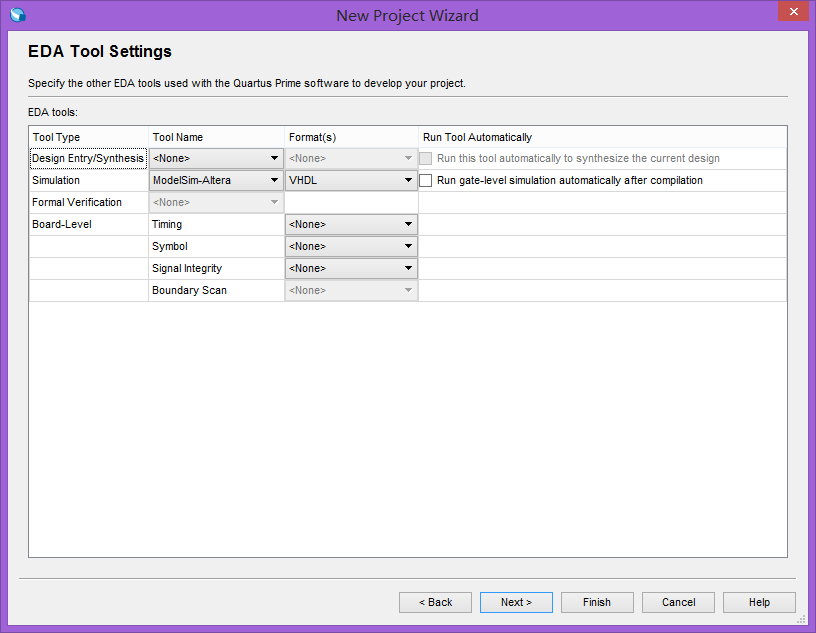

EDA工具界面(miàn)。該页(yè)面(miàn)用(yòng)默認的(de)就(jiù)行,直(zhí)接點(diǎn)擊最(zuì)下(xià)方(fāng)“Next”。

图(tú)388

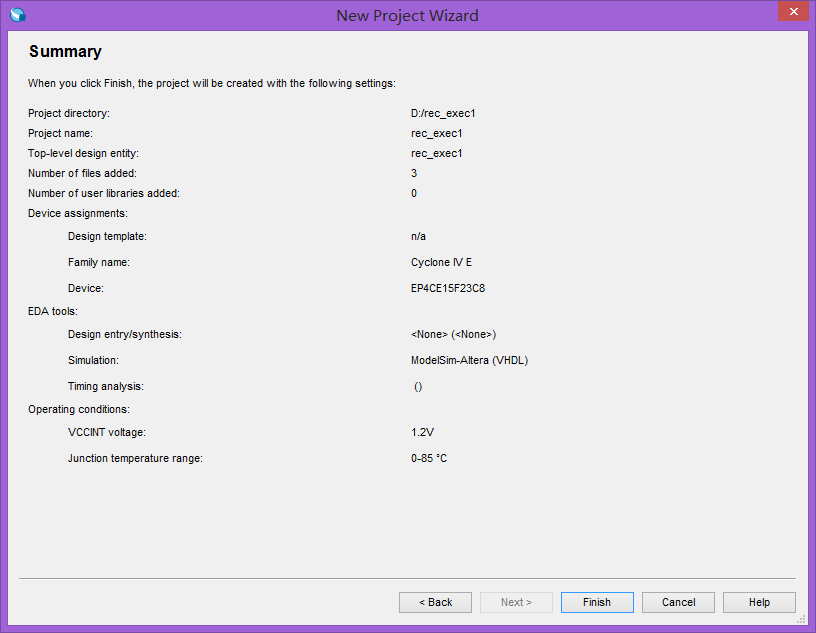

8.之後(hòu)出(chū)現(xiàn)的(de)界面(miàn)是(shì)我(wǒ)们(men)前(qián)面(miàn)的(de)設置的(de)總(zǒng)結,确認沒(méi)有(yǒu)錯誤後(hòu)點(diǎn)擊“Finish”。

图(tú)389

4.2PLL

新建工程後(hòu),就(jiù)要(yào)生(shēng)成(chéng)PLL IP核。本(běn)节(jié)的(de)PLL生(shēng)成(chéng)过(guò)程,與(yǔ)案(àn)例“VGA顯示顔色(sè)”第(dì)四(sì)點(diǎn)綜合工程和(hé)上(shàng)板中(zhōng)的(de)PLL內(nèi)容一(yī)致(zhì),注意(yì)其中(zhōng)的(de)地(dì)址有(yǒu)不(bù)同(tóng)。

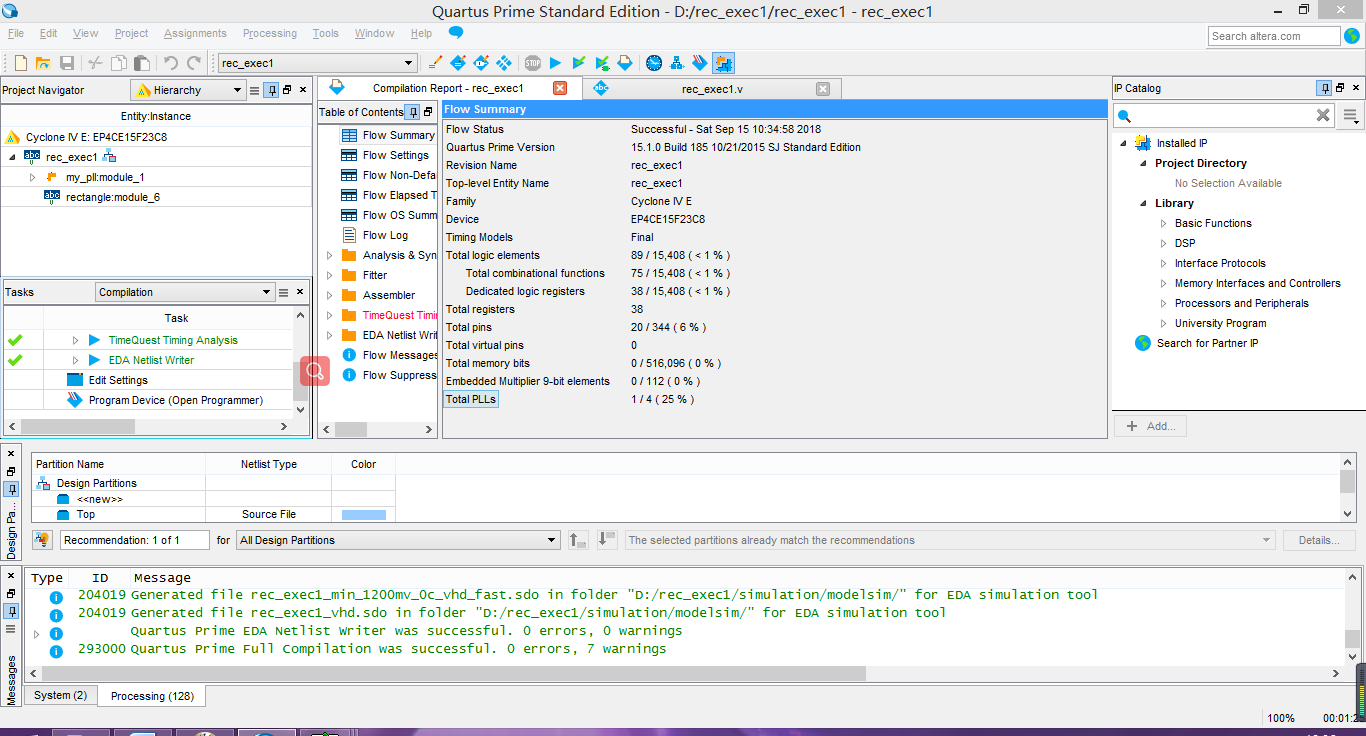

4.3綜合

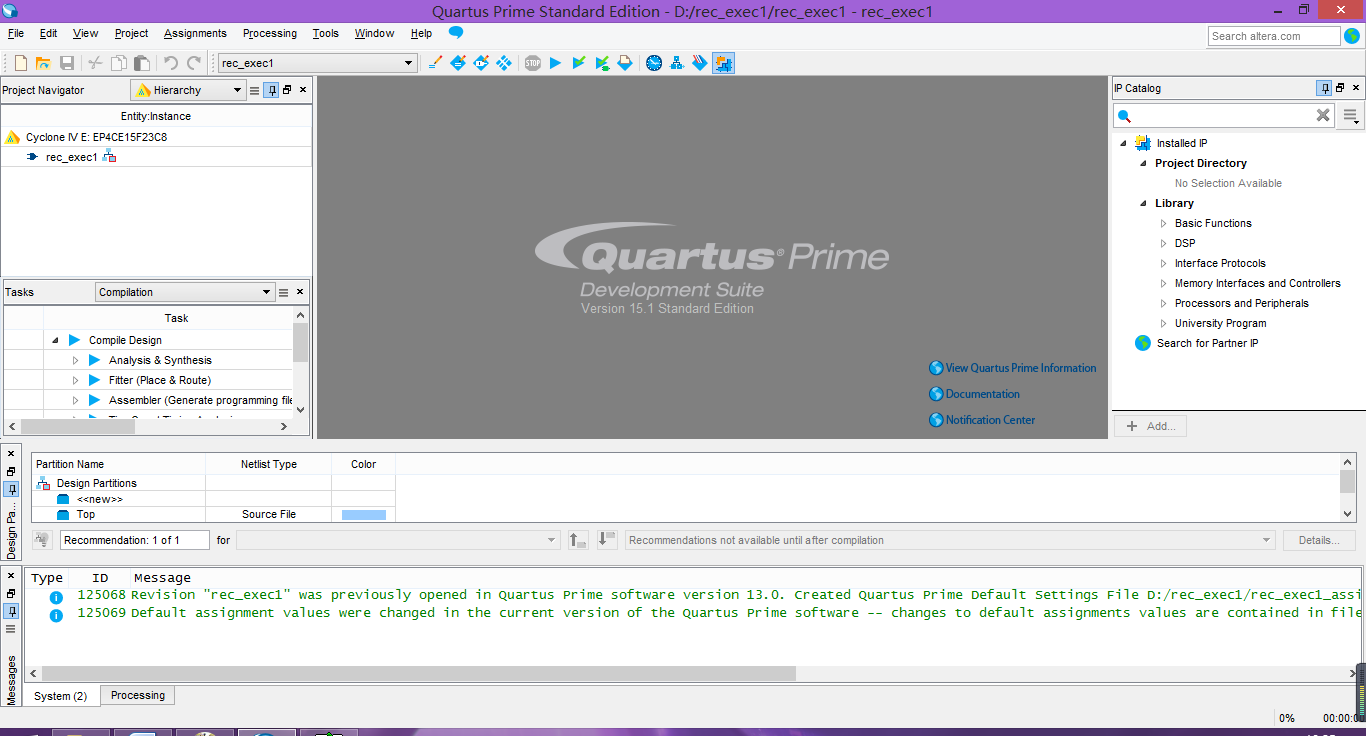

1.新建工程步驟完成(chéng)後(hòu),就(jiù)会(huì)出(chū)現(xiàn)以(yǐ)下(xià)界面(miàn)。在(zài)“Project Navigator”下(xià)選中(zhōng)要(yào)編譯的(de)文(wén)件(jiàn),點(diǎn)擊上(shàng)方(fāng)工具欄中(zhōng)“Start Compilation”編譯按鈕(藍(lán)色(sè)三(sān)角(jiǎo)形)。

图(tú)390

2.編譯成(chéng)功後(hòu)会(huì)出(chū)現(xiàn)以(yǐ)下(xià)界面(miàn),點(diǎn)擊“OK”。

图(tú)391

4.4配置管(guǎn)脚

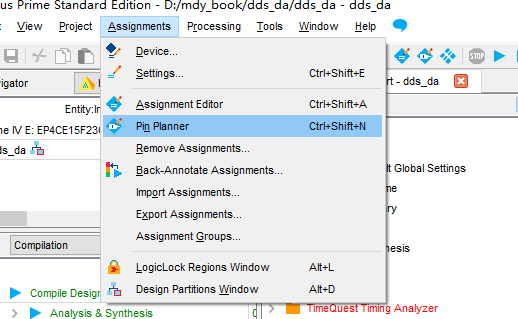

图(tú)392

在(zài)菜單欄中(zhōng),選中(zhōng)Assignments,然後(hòu)選擇Pin Planner,就(jiù)会(huì)弹出(chū)配置管(guǎn)脚的(de)窗(chuāng)口(kǒu)。

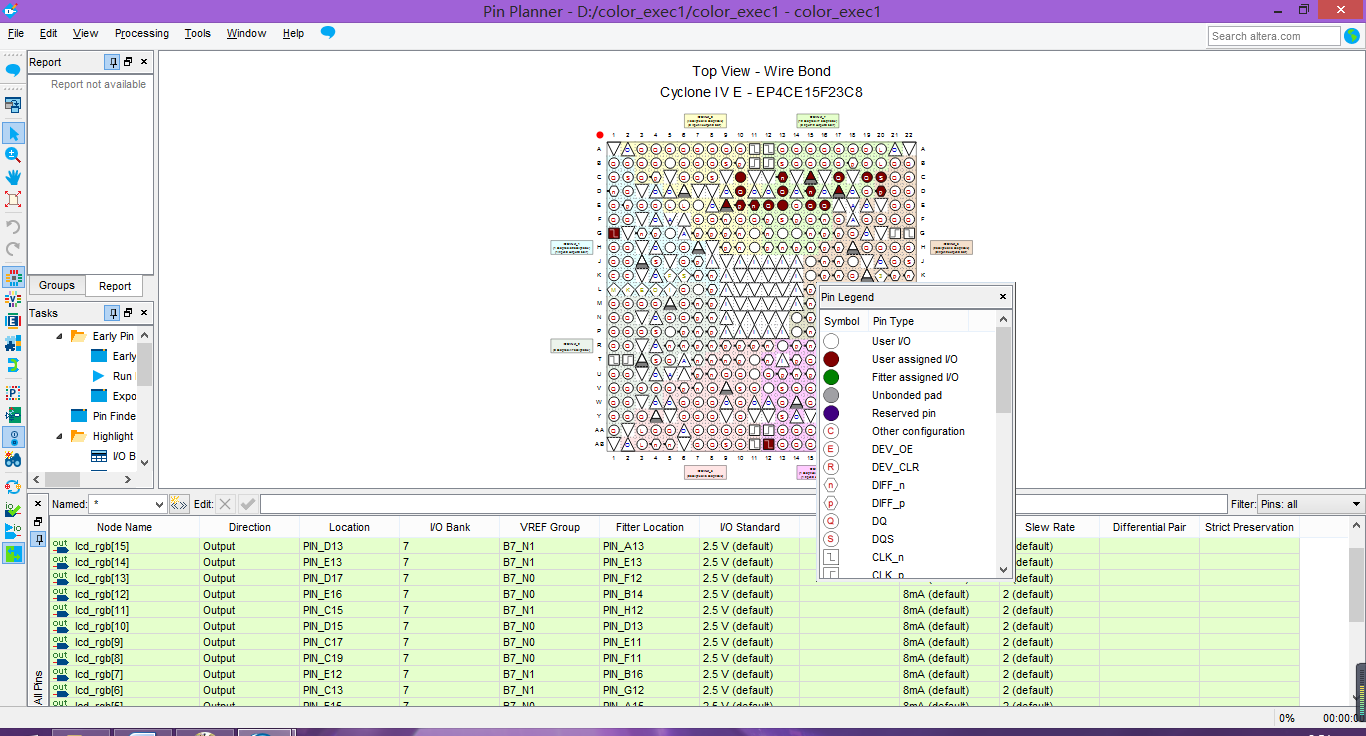

图(tú)393

在(zài)配置窗(chuāng)口(kǒu)最(zuì)下(xià)方(fāng)中(zhōng)的(de)location一(yī)列,參考下(xià)表(biǎo)中(zhōng)最(zuì)右(yòu)两(liǎng)列配置好(hǎo)FPGA管(guǎn)脚。

|

器件(jiàn) |

信(xìn)号(hào)線(xiàn) |

信(xìn)号(hào)線(xiàn) |

FPGA管(guǎn)脚 |

內(nèi)部(bù)信(xìn)号(hào) |

|

U6,U7 |

SEG_E |

SEG0 |

Y6 |

seg_ment[2] |

|

SEG_DP |

SEG1 |

W6 |

未用(yòng)到(dào) |

|

|

SEG_G |

SEG2 |

Y7 |

seg_ment[0] |

|

|

SEG_F |

SEG3 |

W7 |

seg_ment[1] |

|

|

SEG_D |

SEG4 |

P3 |

seg_ment[3] |

|

|

SEG_C |

SEG5 |

P4 |

seg_ment[4] |

|

|

SEG_B |

SEG6 |

R5 |

seg_ment[5] |

|

|

SEG_A |

SEG7 |

T3 |

seg_ment[6] |

|

|

DIG1 |

DIG_EN1 |

T4 |

seg_sel[0] |

|

|

DIG2 |

DIG_EN2 |

V4 |

seg_sel[1] |

|

|

DIG3 |

DIG_EN3 |

V3 |

seg_sel[2] |

|

|

DIG4 |

DIG_EN4 |

Y3 |

seg_sel[3] |

|

|

DIG5 |

DIG_EN5 |

Y8 |

seg_sel[4] |

|

|

DIG6 |

DIG_EN6 |

W8 |

seg_sel[5] |

|

|

DIG7 |

DIG_EN7 |

W10 |

seg_sel[6] |

|

|

DIG8 |

DIG_EN8 |

Y10 |

seg_sel[7] |

|

|

X1 |

|

SYS_CLK |

G1 |

clk |

|

K1 |

|

SYS_RST |

AB12 |

rst_n |

注意(yì)注意(yì):與(yǔ)其他(tā)案(àn)例不(bù)同(tóng)的(de)是(shì),VGA案(àn)例中(zhōng)所(suǒ)有(yǒu)管(guǎn)脚的(de)電(diàn)平必須選用(yòng)为(wèi)LVCMOS3.3,而(ér)不(bù)能(néng)是(shì)default。如(rú)下(xià)图(tú)所(suǒ)示。

配置完成(chéng)後(hòu),關(guān)閉Pin Planner,软(ruǎn)件(jiàn)自(zì)動(dòng)会(huì)保存管(guǎn)脚配置信(xìn)息。

4.5再次(cì)綜合

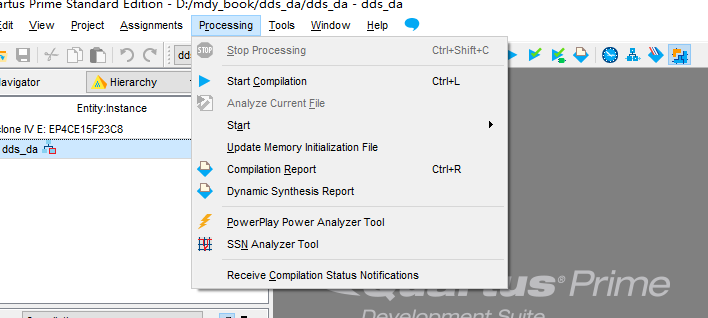

图(tú)394

在(zài)菜單欄中(zhōng),選中(zhōng)Processing,然後(hòu)選擇Start Compilation,再次(cì)对(duì)整个(gè)工程進(jìn)行編譯和(hé)綜合。

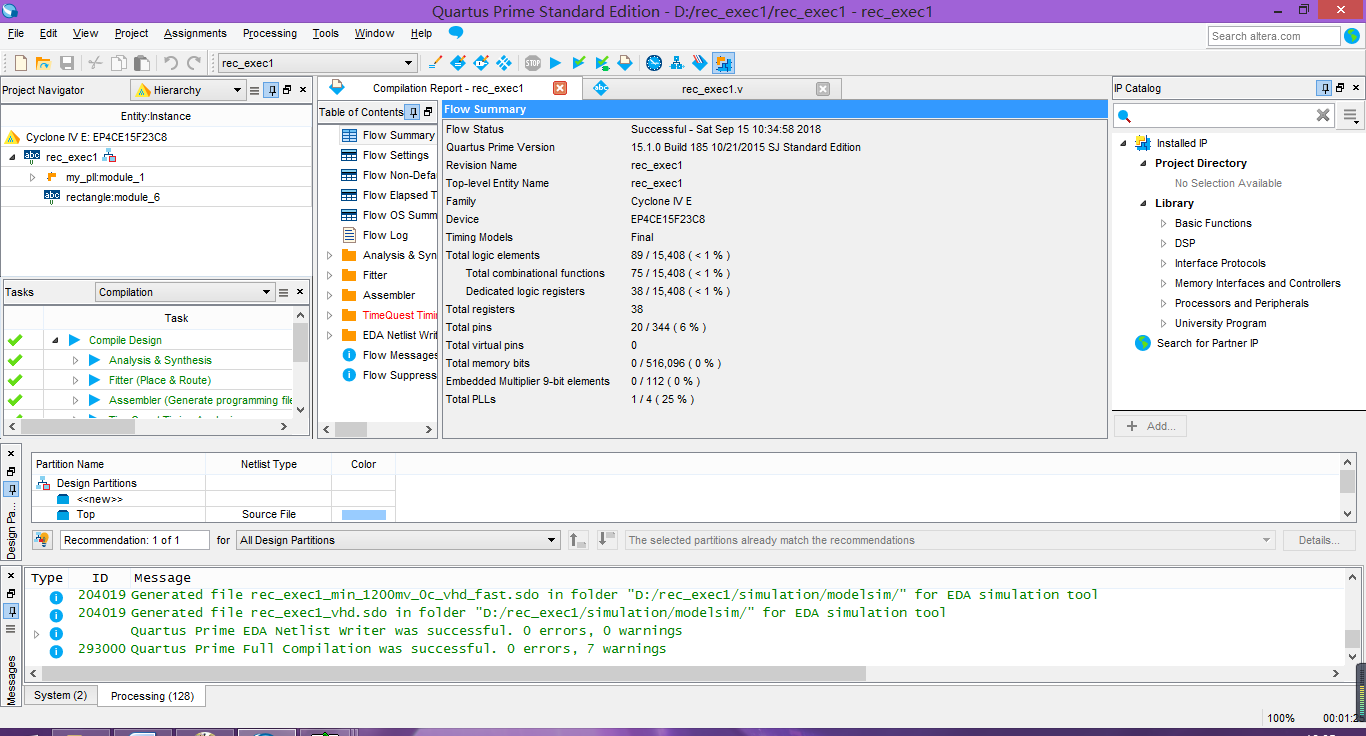

图(tú)395

出(chū)現(xiàn)上(shàng)面(miàn)的(de)界面(miàn),就(jiù)说(shuō)明(míng)編譯綜合成(chéng)功。

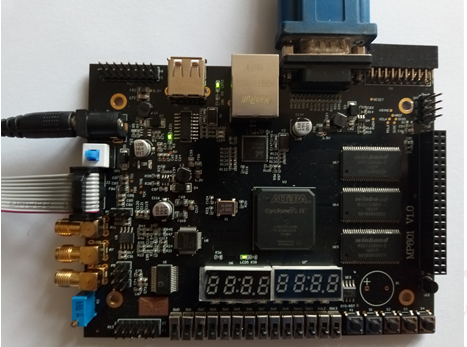

4.6連(lián)接開(kāi)發(fà)板

图(tú)中(zhōng),下(xià)载器接入(rù)電(diàn)腦USB接口(kǒu),電(diàn)源接入(rù)電(diàn)源,vga線(xiàn)連(lián)接顯示器,然後(hòu)摁下(xià)電(diàn)源開(kāi)關(guān),看(kàn)到(dào)開(kāi)發(fà)板燈(dēng)亮(liàng)。

图(tú)396

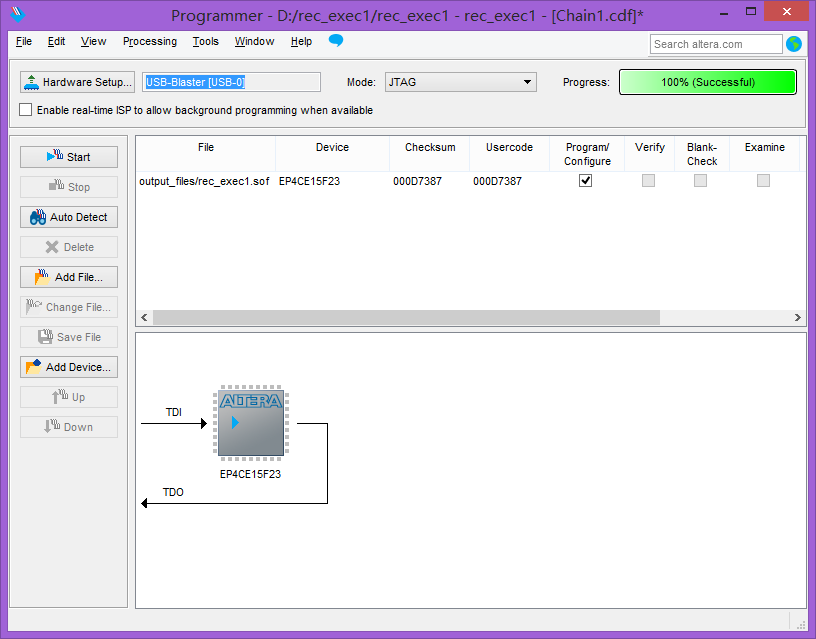

4.7上(shàng)板

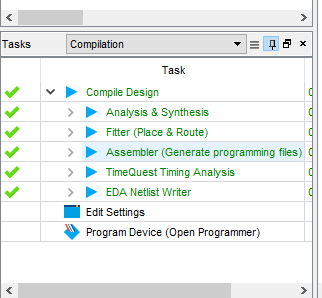

1.双(shuāng)擊Tasks一(yī)欄中(zhōng)”Program Device”。

图(tú)397

2.会(huì)出(chū)現(xiàn)如(rú)下(xià)界面(miàn),點(diǎn)擊add file添加.sof文(wén)件(jiàn),在(zài)右(yòu)側點(diǎn)擊“Start”,会(huì)在(zài)上(shàng)方(fāng)的(de)“Progress”处顯示進(jìn)度(dù)。

图(tú)398

3.進(jìn)度(dù)条(tiáo)中(zhōng)提(tí)示成(chéng)功後(hòu),即可(kě)在(zài)顯示器上(shàng)观察到(dào)相應(yìng)的(de)現(xiàn)象(xiàng)。