第(dì)三(sān)章(zhāng) VERILOG

4 Verilog HDL基本(běn)語(yǔ)句(jù)

4.1 順序块(kuài)語(yǔ)句(jù)

語(yǔ)句(jù)块(kuài)块(kuài)提(tí)供将两(liǎng)条(tiáo)或(huò)更(gèng)多(duō)条(tiáo)語(yǔ)句(jù)組合成(chéng)語(yǔ)法結構上(shàng)相當于(yú)一(yī)条(tiáo)語(yǔ)句(jù)的(de)機(jī)制。这(zhè)里(lǐ)主(zhǔ)要(yào)講Verilog HDL的(de)順序語(yǔ)句(jù)块(kuài)(begin . . . end):語(yǔ)句(jù)块(kuài)中(zhōng)的(de)語(yǔ)句(jù)按給(gěi)定(dìng)次(cì)序順序執行。順序語(yǔ)句(jù)块(kuài)中(zhōng)的(de)語(yǔ)句(jù)按順序方(fāng)式執行。每条(tiáo)語(yǔ)句(jù)中(zhōng)的(de)时(shí)延值與(yǔ)其前(qián)面(miàn)的(de)語(yǔ)句(jù)執行的(de)模拟时(shí)間(jiān)相關(guān)。一(yī)旦順序語(yǔ)句(jù)块(kuài)執行結束(shù),跟随順序語(yǔ)句(jù)块(kuài)过(guò)程的(de)下(xià)一(yī)条(tiáo)語(yǔ)句(jù)繼續執行。順序語(yǔ)句(jù)块(kuài)的(de)語(yǔ)法如(rú)下(xià):

begin [ :block_id{declarations} ]

procedural_statement ( s )

end

例如(rú):

/ / 産生(shēng)波(bō)形:

begin

#2 Stream = 1;

#5 Stream = 0;

#3 Stream = 1;

#4 Stream = 0;

#2 Stream = 1;

#5 Stream = 0;

End

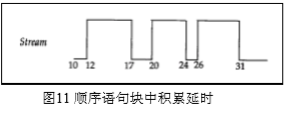

假定(dìng)順序語(yǔ)句(jù)块(kuài)在(zài)第(dì)10个(gè)时(shí)間(jiān)單位開(kāi)始執行。两(liǎng)个(gè)时(shí)間(jiān)單位後(hòu)第(dì)1条(tiáo)語(yǔ)句(jù)執行,即第(dì)12个(gè)时(shí)間(jiān)單位。此(cǐ)執行完成(chéng)後(hòu),下(xià)1条(tiáo)語(yǔ)句(jù)在(zài)第(dì)17个(gè)时(shí)間(jiān)單位執行(延遲5个(gè)时(shí)間(jiān)單位)。然後(hòu)下(xià)1条(tiáo)語(yǔ)句(jù)在(zài)第(dì)20个(gè)时(shí)間(jiān)單位執行,以(yǐ)此(cǐ)類(lèi)推。該順序語(yǔ)句(jù)块(kuài)執行过(guò)程中(zhōng)産生(shēng)的(de)波(bō)形如(rú)图(tú):

图(tú) 33

4.2 連(lián)續賦值語(yǔ)句(jù)

數據(jù)流的(de)描述是(shì)采用(yòng)連(lián)續賦值語(yǔ)句(jù)(assign)語(yǔ)句(jù)来(lái)实現(xiàn)的(de)。語(yǔ)法如(rú)下(xià):

assign net_type = 表(biǎo)达(dá)式;

連(lián)續賦值語(yǔ)句(jù)用(yòng)于(yú)組合邏輯的(de)建模。等式左(zuǒ)邊(biān)是(shì)wire類(lèi)型的(de)變(biàn)量(liàng)。等式右(yòu)邊(biān)可(kě)以(yǐ)是(shì)常量(liàng)、由(yóu)運算符如(rú)邏輯運算符、算術(shù)運算符參與(yǔ)的(de)表(biǎo)达(dá)。如(rú)下(xià)幾(jǐ)个(gè)实例:

wire [3:0] Z, Preset, Clear; //線(xiàn)网(wǎng)说(shuō)明(míng)

assign Z = Preset & Clear; //連(lián)續賦值語(yǔ)句(jù)

wire Cout, C i n ;

wire [3:0] Sum, A, B;

. . .

assign {Cout, Sum} = A + B + Cin;

assign Mux = (S = = 3)? D : 'bz;

注意(yì)如(rú)下(xià)幾(jǐ)个(gè)方(fāng)面(miàn):

1、連(lián)續賦值語(yǔ)句(jù)的(de)執行是(shì):只(zhī)要(yào)右(yòu)邊(biān)表(biǎo)达(dá)式任一(yī)个(gè)變(biàn)量(liàng)有(yǒu)變(biàn)化(huà),表(biǎo)达(dá)式立即被(bèi)計(jì)算,計(jì)算的(de)結果(guǒ)立即賦給(gěi)左(zuǒ)邊(biān)信(xìn)号(hào)。

2、連(lián)續賦值語(yǔ)句(jù)之間(jiān)是(shì)并行語(yǔ)句(jù),因(yīn)此(cǐ)與(yǔ)位置順序无關(guān)。

4.3 条(tiáo)件(jiàn)語(yǔ)句(jù)

4.3.1 条(tiáo)件(jiàn)語(yǔ)句(jù) if

語(yǔ)句(jù)的(de)語(yǔ)法如(rú)下(xià):

if(condition_1)

procedural_statement_1

{else if(condition_2)

procedural_statement_2}

{else

procedural_statement_3}

如(rú)果(guǒ)对(duì)condition_1 条(tiáo)件(jiàn)滿足,不(bù)管(guǎn)condition_2是(shì)否滿足,都執行procedural_statement_1,procedural_statement_2和(hé)procedural_statement_3都不(bù)執行。

如(rú)果(guǒ)condition_1不(bù)滿足而(ér)condition_2滿足,則執行procedural_statement_2,procedural_statement_1和(hé)procedural_statement_3都不(bù)執行。

如(rú)果(guǒ)condition_1不(bù)滿足并且condition_2也(yě)不(bù)滿足时(shí),執行procedural_statement_3,procedural_statement_1和(hé)procedural_statement_2都不(bù)執行。

以(yǐ)下(xià)是(shì)一(yī)个(gè)例子。

if(Sum < 60) begin

Grade = C;

Total_C = Total _c + 1;

end else if(Sum < 75) begin

Grade = B;

Total_B = Total_B + 1;

end else begin

Grade = A;

Total_A = Total_A + 1;

end

注意(yì)条(tiáo)件(jiàn)表(biǎo)达(dá)式必須總(zǒng)是(shì)被(bèi)括起来(lái),如(rú)果(guǒ)使用(yòng)if - if - else 格式,那(nà)麼(me)可(kě)能(néng)会(huì)有(yǒu)二(èr)義性(xìng),如(rú)下(xià)例所(suǒ)示:

if(C l k)

if(R e s e t)

Q = 0;

else

Q = D;

問(wèn)題(tí)是(shì)最(zuì)後(hòu)一(yī)个(gè)else 屬于(yú)哪一(yī)个(gè)if? 它(tā)是(shì)屬于(yú)第(dì)一(yī)个(gè)if 的(de)条(tiáo)件(jiàn)(Clk)還(huán)是(shì)屬于(yú)第(dì)二(èr)个(gè)if的(de)条(tiáo)件(jiàn) (Reset)? 这(zhè)在(zài)Verilog HDL 中(zhōng)已通(tòng)过(guò)将else 與(yǔ)最(zuì)近(jìn)的(de)沒(méi)有(yǒu)else 的(de)if 相關(guān)聯来(lái)解(jiě)決。在(zài)这(zhè)个(gè)例子中(zhōng), else 與(yǔ)內(nèi)层if 語(yǔ)句(jù)相關(guān)聯。

以(yǐ)下(xià)是(shì)另(lìng)一(yī)些if 語(yǔ)句(jù)的(de)例子。

if(Sum < 100)

Sum = Sum + 10;

if(Nickel_In)

Deposit = 5;

elseif (Dime_In)

Deposit = 10;

else if(Quarter_In)

Deposit = 25;

else

Deposit = ERROR;

書(shū)写建議:

1、条(tiáo)件(jiàn)表(biǎo)达(dá)式需用(yòng)括号(hào)括起来(lái)。

2、若为(wèi)if - if 語(yǔ)句(jù),請使用(yòng)块(kuài)語(yǔ)句(jù) begin --- end :

if(C l k) begin

if(R e s e t)

Q = 0;

else

Q = D;

end

以(yǐ)上(shàng)两(liǎng)點(diǎn)建議是(shì)为(wèi)了(le)使代(dài)碼更(gèng)加清(qīng)晰,防止出(chū)錯。

4.3.2 条(tiáo)件(jiàn)語(yǔ)句(jù) case

case 語(yǔ)句(jù)是(shì)一(yī)个(gè)多(duō)路(lù)条(tiáo)件(jiàn)分(fēn)支形式,其語(yǔ)法如(rú)下(xià):

case(case_expr)

case_item_expr{ ,case_item_expr} :procedural_statement

. . . . . .

[default:procedural_statement]

endcase

case語(yǔ)句(jù)首先(xiān)对(duì)条(tiáo)件(jiàn)表(biǎo)达(dá)式case_expr 求值,然後(hòu)依次(cì)对(duì)各(gè)分(fēn)支項求值并進(jìn)行比較,第(dì)一(yī)个(gè)與(yǔ)条(tiáo)件(jiàn)表(biǎo)达(dá)式值相匹(pǐ)配的(de)分(fēn)支中(zhōng)的(de)語(yǔ)句(jù)被(bèi)執行。可(kě)以(yǐ)在(zài)1 个(gè)分(fēn)支中(zhōng)定(dìng)義多(duō)个(gè)分(fēn)支項;这(zhè)些值不(bù)需要(yào)互斥。缺省(shěng)分(fēn)支覆蓋所(suǒ)有(yǒu)沒(méi)有(yǒu)被(bèi)分(fēn)支表(biǎo)达(dá)式覆蓋的(de)其他(tā)分(fēn)支。

例:

case (HEX)

4'b0001 : LED = 7'b1111001; // 1

4'b0010 : LED = 7'b0100100; // 2

4'b0011 : LED = 7'b0110000; // 3

4'b0100 : LED = 7'b0011001; // 4

4'b0101 : LED = 7'b0010010; // 5

4'b0110 : LED = 7'b0000010; // 6

4'b0111 : LED = 7'b1111000; // 7

4'b1000 : LED = 7'b0000000; // 8

4'b1001 : LED = 7'b0010000; // 9

4'b1010 : LED = 7'b0001000; // A

4'b1011 : LED = 7'b0000011; // B

4'b1100 : LED = 7'b1000110; // C

4'b1101 : LED = 7'b0100001; // D

4'b1110 : LED = 7'b0000110; // E

4'b1111 : LED = 7'b0001110; // F

default :LED = 7'b1000000; // 0

endcase

書(shū)写建議: case 的(de)缺省(shěng)項必須写,防止産生(shēng)鎖存器。

4.4 过(guò)程語(yǔ)句(jù)

Verilog HDL中(zhōng)提(tí)供两(liǎng)種(zhǒng)过(guò)程賦值語(yǔ)句(jù)initial和(hé)always語(yǔ)句(jù),用(yòng)这(zhè)两(liǎng)種(zhǒng)語(yǔ)句(jù)来(lái)实現(xiàn)行为(wèi)的(de)建模。这(zhè)两(liǎng)種(zhǒng)語(yǔ)句(jù)之間(jiān)的(de)執行是(shì)并行的(de),即語(yǔ)句(jù)的(de)執行與(yǔ)位置順序无關(guān)。这(zhè)两(liǎng)種(zhǒng)語(yǔ)句(jù)通(tòng)常與(yǔ)語(yǔ)句(jù)块(kuài)(begin ....end)相結合,則語(yǔ)句(jù)块(kuài)中(zhōng)的(de)執行是(shì)按順序執行的(de)。

4.4.1 initial 語(yǔ)句(jù)

initial語(yǔ)句(jù)只(zhī)執行一(yī)次(cì),即在(zài)設計(jì)被(bèi)開(kāi)始模拟執行时(shí)開(kāi)始(0时(shí)刻)。通(tòng)常只(zhī)用(yòng)在(zài)对(duì)設計(jì)進(jìn)行仿真(zhēn)的(de)测試文(wén)件(jiàn)中(zhōng),用(yòng)于(yú)对(duì)一(yī)些信(xìn)号(hào)進(jìn)行初始化(huà)和(hé)産生(shēng)特(tè)定(dìng)的(de)信(xìn)号(hào)波(bō)形。語(yǔ)法如(rú)下(xià):(大家(jiā)只(zhī)要(yào)先(xiān)有(yǒu)个(gè)概念就(jiù)可(kě)以(yǐ))

initial [timing_control]

procedural_statement

procedural_statement 是(shì)下(xià)列語(yǔ)句(jù)之一(yī):

procedural_assignment (blocking or non-blocking ) //阻塞或(huò)非(fēi)阻塞性(xìng)过(guò)程賦值語(yǔ)句(jù)

procedural_continuous_assignment

conditional_statement

case_statement

loop_statement

wait_statement

disable_statement event_trigger task_enable (user or system)

事(shì)例如(rú)上(shàng)産生(shēng)一(yī)个(gè)信(xìn)号(hào)波(bō)形:

initial begin

#2 Stream = 1;

#5 Stream = 0;

#3 Stream = 1;

#4 Stream = 0;

#2 Stream = 1;

#5 Stream = 0;

end

再次(cì)強(qiáng)調,initial語(yǔ)句(jù)只(zhī)用(yòng)于(yú)仿真(zhēn)测試,一(yī)般不(bù)会(huì)用(yòng)到(dào)設計(jì)代(dài)碼中(zhōng)。

4.4.2 always 語(yǔ)句(jù)

需要(yào)看(kàn)对(duì)應(yìng)的(de)視頻,請點(diǎn)擊視頻編号(hào)::001100000068

1、本(běn)节(jié)介紹时(shí)序邏輯代(dài)碼(即always語(yǔ)句(jù)),分(fēn)位同(tóng)步複位的(de)时(shí)序邏輯和(hé)异(yì)步複位的(de)时(shí)序邏輯,本(běn)教学統一(yī)采用(yòng)异(yì)步时(shí)鐘(zhōng)邏輯。

2、这(zhè)是(shì)ALTERA和(hé)VIVADO文(wén)檔

always語(yǔ)句(jù)與(yǔ)initial語(yǔ)句(jù)相反(fǎn),是(shì)被(bèi)重(zhòng)複執行,執行機(jī)制是(shì)通(tòng)过(guò)对(duì)一(yī)个(gè)稱为(wèi)敏感(gǎn)變(biàn)量(liàng)表(biǎo)的(de)事(shì)件(jiàn)驅動(dòng)来(lái)实現(xiàn)的(de),下(xià)面(miàn)会(huì)具體(tǐ)講到(dào)。

always 語(yǔ)句(jù)的(de)基本(běn)格式是(shì)

always @(敏感(gǎn)事(shì)件(jiàn))begin

程序語(yǔ)句(jù)

end

always是(shì)“一(yī)直(zhí)、總(zǒng)是(shì)”的(de)意(yì)思(sī),@後(hòu)面(miàn)跟着事(shì)件(jiàn)。整个(gè)always的(de)意(yì)思(sī)是(shì):當敏感(gǎn)事(shì)件(jiàn)的(de)条(tiáo)件(jiàn)滿足时(shí),就(jiù)執行一(yī)次(cì)“程序語(yǔ)句(jù)”。每敏感(gǎn)事(shì)件(jiàn)每滿足一(yī)次(cì),就(jiù)執行“程序語(yǔ)句(jù)”一(yī)次(cì)。

|

1 2 3 4 5 6 |

always @(a or b or d)begin if(sel==0) c = a + b; else c = a + d; end |

这(zhè)段(duàn)程序的(de)意(yì)思(sī)是(shì),當信(xìn)号(hào)a或(huò)者(zhě)信(xìn)号(hào)b或(huò)者(zhě)信(xìn)号(hào)d發(fà)生(shēng)變(biàn)化(huà)时(shí),就(jiù)執行一(yī)次(cì)下(xià)面(miàn)語(yǔ)句(jù)。在(zài)執行該段(duàn)語(yǔ)句(jù)时(shí),首先(xiān)判斷信(xìn)号(hào)sel是(shì)否为(wèi)0,如(rú)果(guǒ)为(wèi)0,則執行第(dì)783行代(dài)碼;如(rú)果(guǒ)sel不(bù)为(wèi)0,則執行第(dì)785行代(dài)碼。需要(yào)強(qiáng)調的(de)是(shì),a、b、c任意(yì)一(yī)个(gè)發(fà)生(shēng)變(biàn)化(huà)一(yī)次(cì),782行至(zhì)785行也(yě)只(zhī)執行一(yī)次(cì),不(bù)会(huì)執行第(dì)二(èr)次(cì)的(de)。

注意(yì)到(dào)的(de)是(shì),sel这(zhè)个(gè)信(xìn)号(hào)變(biàn)化(huà)时(shí),是(shì)不(bù)会(huì)執行第(dì)782行到(dào)785行代(dài)碼的(de)。通(tòng)常这(zhè)不(bù)符合設計(jì)者(zhě)的(de)想(xiǎng)法。例如(rú),一(yī)般想(xiǎng)法是(shì)當sel为(wèi)0时(shí),c的(de)結果(guǒ)是(shì)a+b;當sel不(bù)为(wèi)0时(shí),c的(de)結果(guǒ)是(shì)a+d。但如(rú)果(guǒ)sel由(yóu)0變(biàn)1之後(hòu),c的(de)結果(guǒ)a+b。總(zǒng)之,这(zhè)不(bù)是(shì)一(yī)个(gè)規範的(de)設計(jì)思(sī)維。

一(yī)般設計(jì)者(zhě)的(de)想(xiǎng)法是(shì):當信(xìn)号(hào)a或(huò)者(zhě)信(xìn)号(hào)b或(huò)者(zhě)信(xìn)号(hào)d或(huò)者(zhě)信(xìn)号(hào)sel執行變(biàn)化(huà)时(shí),就(jiù)執行782行至(zhì)785行。这(zhè)樣(yàng)就(jiù)确保,當sel为(wèi)0时(shí),c的(de)結果(guǒ)一(yī)定(dìng)为(wèi)a+b;當sel不(bù)为(wèi)0时(shí),c的(de)結果(guǒ)一(yī)定(dìng)是(shì)a+d。所(suǒ)以(yǐ)要(yào)在(zài)敏感(gǎn)列表(biǎo)中(zhōng)加上(shàng)sel,如(rú)下(xià)面(miàn)代(dài)碼。

|

1 2 3 4 5 6 |

always @(a or b or d or sel)begin if(sel==0) c = a + b; else c = a + d; end |

當敏感(gǎn)信(xìn)号(hào)非(fēi)常多(duō)时(shí),很容易就(jiù)会(huì)把敏感(gǎn)信(xìn)号(hào)遺漏,为(wèi)避免这(zhè)種(zhǒng)情(qíng)況,可(kě)以(yǐ)用(yòng)“*”来(lái)代(dài)替。这(zhè)个(gè)“*”是(shì)指“程序語(yǔ)句(jù)”中(zhōng)所(suǒ)有(yǒu)的(de)条(tiáo)件(jiàn)信(xìn)号(hào),也(yě)就(jiù)是(shì)a、b、d、sel(不(bù)包(bāo)括c)發(fà)生(shēng)變(biàn)化(huà)。明(míng)德揚也(yě)推薦这(zhè)種(zhǒng)写法。

|

1 2 3 4 5 6 |

always @(*)begin if(sel==0) c = a + b; else c = a + d; end |

这(zhè)種(zhǒng)条(tiáo)件(jiàn)信(xìn)号(hào)變(biàn)化(huà),結果(guǒ)立即變(biàn)化(huà)的(de)always,我(wǒ)们(men)稱之为(wèi)“組合邏輯”。

|

1 2 3 4 5 6 |

always @(posedge clk)begin if(sel==0) c <= a + b; else c <= a + d; end |

这(zhè)段(duàn)代(dài)碼敏感(gǎn)列表(biǎo)是(shì)“posedge clk”,其中(zhōng)posedge表(biǎo)示上(shàng)升(shēng)沿。也(yě)就(jiù)是(shì)说(shuō),當clk由(yóu)0變(biàn)成(chéng)1的(de)瞬間(jiān),執行一(yī)次(cì)程序代(dài)碼:第(dì)806至(zhì)809行。其他(tā)时(shí)候,c的(de)值保持(chí)不(bù)變(biàn)。要(yào)特(tè)别強(qiáng)調的(de)是(shì),如(rú)果(guǒ)clk沒(méi)有(yǒu)由(yóu)0變(biàn)成(chéng)1,那(nà)麼(me)即使a、b、d、sel發(fà)生(shēng)變(biàn)化(huà),c的(de)值也(yě)是(shì)不(bù)變(biàn)的(de)。

|

1 2 3 4 5 6 |

always @(negedge clk)begin if(sel==0) c <= a + b; else c <= a + d; end |

这(zhè)段(duàn)代(dài)碼的(de)敏感(gǎn)列表(biǎo)是(shì)“negedge clk”,其中(zhōng)negedg表(biǎo)示下(xià)降沿。也(yě)就(jiù)是(shì)说(shuō),當clk由(yóu)1變(biàn)成(chéng)0的(de)瞬間(jiān),執行一(yī)次(cì)程序代(dài)碼:第(dì)806至(zhì)809行。其他(tā)时(shí)候,c的(de)值保持(chí)不(bù)變(biàn)。要(yào)特(tè)别強(qiáng)調的(de)是(shì),如(rú)果(guǒ)clk沒(méi)有(yǒu)由(yóu)1變(biàn)成(chéng)0,那(nà)麼(me)即使a、b、d、sel發(fà)生(shēng)變(biàn)化(huà),c的(de)值也(yě)是(shì)不(bù)變(biàn)的(de)。

|

1 2 3 4 5 6 7 8 9 |

always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0)begin c <= 0; end else if(sel==0) c <= a + b; else c <= a + d; end |

这(zhè)段(duàn)代(dài)碼的(de)敏感(gǎn)列表(biǎo)是(shì)“posedge clk or negedge rst_n”,也(yě)就(jiù)是(shì)说(shuō),當clk由(yóu)0變(biàn)成(chéng)1的(de)瞬間(jiān),或(huò)者(zhě)rst_n由(yóu)1變(biàn)化(huà)0的(de)瞬間(jiān),執行一(yī)次(cì)程序代(dài)碼:第(dì)814至(zhì)820行。其他(tā)时(shí)候,c的(de)值保持(chí)不(bù)變(biàn)。

我(wǒ)们(men)把这(zhè)種(zhǒng)信(xìn)号(hào)邊(biān)沿觸發(fà),即信(xìn)号(hào)上(shàng)升(shēng)沿或(huò)者(zhě)下(xià)降沿才變(biàn)化(huà)的(de)always,稱之为(wèi)“时(shí)序邏輯”。而(ér)那(nà)个(gè)信(xìn)号(hào)clk是(shì)时(shí)鐘(zhōng)。注意(yì),識别是(shì)不(bù)是(shì)时(shí)鐘(zhōng),不(bù)是(shì)看(kàn)名稱,而(ér)是(shì)看(kàn)这(zhè)个(gè)信(xìn)号(hào)放(fàng)在(zài)哪里(lǐ)。如(rú)放(fàng)在(zài)敏感(gǎn)列表(biǎo)并且是(shì)邊(biān)沿觸發(fà)的(de),才是(shì)时(shí)鐘(zhōng)。而(ér)信(xìn)号(hào)rst_n是(shì)複位信(xìn)号(hào),也(yě)不(bù)是(shì)看(kàn)名字(zì),而(ér)是(shì)它(tā)放(fàng)在(zài)敏感(gǎn)列表(biǎo)里(lǐ),并且也(yě)是(shì)邊(biān)沿觸發(fà),更(gèng)關(guān)鍵的(de)是(shì)“程序語(yǔ)句(jù)”首先(xiān)判斷了(le)rst_n的(de)值,也(yě)就(jiù)是(shì)优先(xiān)級最(zuì)高(gāo),一(yī)般都是(shì)用(yòng)于(yú)複位使用(yòng)的(de)。

注意(yì)以(yǐ)下(xià)幾(jǐ)點(diǎn):

1、对(duì)組合邏輯的(de)always 語(yǔ)句(jù),敏感(gǎn)變(biàn)量(liàng)必須写全(quán),或(huò)者(zhě)用(yòng)“*”代(dài)替。

2、对(duì)組合邏輯器件(jiàn)的(de)賦值采用(yòng)阻塞賦值“=;时(shí)序邏輯器件(jiàn)的(de)賦值語(yǔ)句(jù)采用(yòng)非(fēi)阻塞賦值“<=”;具體(tǐ)原因(yīn)請看(kàn)“阻塞賦值和(hé)非(fēi)阻塞賦值”一(yī)节(jié)內(nèi)容。

4.5 阻塞賦值和(hé)非(fēi)阻塞賦值

需要(yào)看(kàn)对(duì)應(yìng)的(de)視頻,請點(diǎn)擊視頻編号(hào):001100000072

1、本(běn)节(jié)介紹在(zài)always語(yǔ)句(jù)块(kuài)中(zhōng),verilog語(yǔ)言支持(chí)的(de)两(liǎng)種(zhǒng)類(lèi)型的(de)賦值:阻塞賦值(=)和(hé)非(fēi)阻塞賦值(<=),前(qián)者(zhě)表(biǎo)示順序執行,後(hòu)者(zhě)表(biǎo)示并行執行。

2、这(zhè)是(shì)ALTERA和(hé)VIVADO文(wén)檔

在(zài)always語(yǔ)句(jù)块(kuài)中(zhōng),verilog語(yǔ)言支持(chí)两(liǎng)種(zhǒng)類(lèi)型的(de)賦值:阻塞賦值和(hé)非(fēi)阻塞賦值。阻塞賦值使用(yòng)“=”語(yǔ)句(jù);非(fēi)阻塞賦值使用(yòng)“<=”語(yǔ)句(jù)。

阻塞賦值:在(zài)一(yī)个(gè)begin end的(de)多(duō)行賦值語(yǔ)句(jù),是(shì)先(xiān)執行當前(qián)行的(de)賦值語(yǔ)句(jù),再執行下(xià)一(yī)行的(de)賦值語(yǔ)句(jù)。

非(fēi)阻塞賦值:在(zài)一(yī)个(gè)begin end的(de)多(duō)行賦值語(yǔ)句(jù),在(zài)同(tóng)一(yī)时(shí)間(jiān)同(tóng)时(shí)賦值。

|

1 2 3 4 5 6 7 8 9 |

begin c = a; d = c + a; end

begin c <= a; d <= c + a; end |

例如(rú)上(shàng)面(miàn)两(liǎng)个(gè)例子中(zhōng),1到(dào)4行这(zhè)一(yī)段(duàn)是(shì)阻塞賦值,程序会(huì)先(xiān)執行825行,得到(dào)結果(guǒ)後(hòu)再執行826行。829至(zhì)832行这(zhè)一(yī)段(duàn)是(shì)非(fēi)阻塞賦值,830行和(hé)831行的(de)賦值語(yǔ)句(jù)是(shì)同(tóng)时(shí)執行的(de)。

假設當前(qián)c的(de)值为(wèi)0,d的(de)值为(wèi)0,a的(de)新值为(wèi)1。

阻塞賦值的(de)執行过(guò)程和(hé)結果(guǒ):程序会(huì)先(xiān)執行第(dì)825行,此(cǐ)时(shí)c的(de)值将更(gèng)新为(wèi)1,然後(hòu)再執行826行,此(cǐ)时(shí)c+a也(yě)就(jiù)是(shì)相當于(yú)1+1=2,也(yě)就(jiù)是(shì)d的(de)值为(wèi)2。

非(fēi)阻塞賦值的(de)執行过(guò)程和(hé)結果(guǒ):程序会(huì)同(tóng)时(shí)執行第(dì)830行和(hé)831行。特(tè)别注意(yì)是(shì),在(zài)執行831行的(de)时(shí)候,830行是(shì)還(huán)沒(méi)有(yǒu)執行的(de),也(yě)就(jiù)是(shì)意(yì)味着c的(de)值還(huán)沒(méi)變(biàn)化(huà),即此(cǐ)时(shí)c的(de)值为(wèi)0。同(tóng)时(shí)執行的(de)結果(guǒ)是(shì),c的(de)值为(wèi)1,d的(de)值为(wèi)1。

明(míng)德揚的(de)規範要(yào)求,組合邏輯使用(yòng)阻塞賦值“=”,时(shí)序邏輯使用(yòng)非(fēi)阻塞賦值“<=”。读(dú)者(zhě)可(kě)以(yǐ)把这(zhè)个(gè)規則記(jì)下(xià)来(lái),絕对(duì)不(bù)会(huì)出(chū)錯。

制定(dìng)这(zhè)个(gè)規範的(de)原因(yīn),不(bù)是(shì)語(yǔ)法上(shàng)的(de)原因(yīn),而(ér)是(shì)为(wèi)了(le)正(zhèng)确描述硬(yìng)件(jiàn)的(de)原因(yīn)。

5 D觸發(fà)器

需要(yào)看(kàn)对(duì)應(yìng)的(de)視頻,請點(diǎn)擊視頻編号(hào):001100000069

1、本(běn)节(jié)主(zhǔ)要(yào)介紹了(le)在(zài)FPGA中(zhōng)使用(yòng)最(zuì)簡單的(de)觸發(fà)器——D觸發(fà)器,介紹了(le)它(tā)的(de)結構、波(bō)形,以(yǐ)及(jí)如(rú)何看(kàn)FPGA波(bō)形。

2、这(zhè)是(shì)ALTERA和(hé)VIVADO文(wén)檔

5.1 D觸發(fà)器

數字(zì)電(diàn)路(lù)介紹了(le)多(duō)種(zhǒng)觸發(fà)器:JK觸發(fà)器、D觸發(fà)器、RS觸發(fà)器、T觸發(fà)器等。在(zài)FPGA中(zhōng),我(wǒ)们(men)使用(yòng)的(de)是(shì)最(zuì)簡單的(de)觸發(fà)器---D觸發(fà)器。

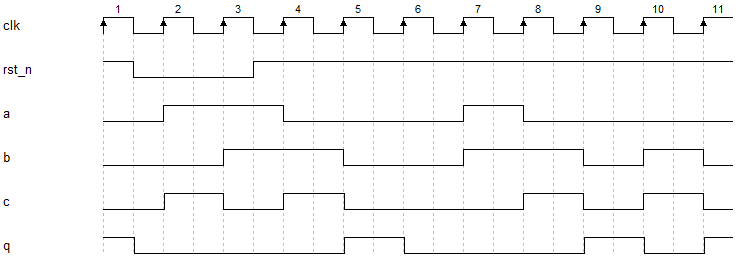

5.1.1 D觸發(fà)器結構

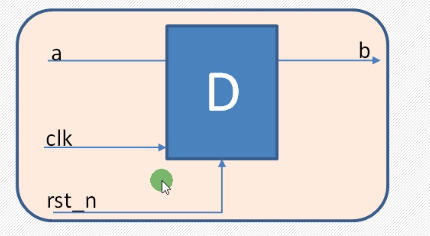

图(tú) 34

图(tú) 34是(shì)D觸發(fà)器的(de)結構图(tú),读(dú)者(zhě)可(kě)以(yǐ)把它(tā)看(kàn)成(chéng)一(yī)个(gè)芯片(piàn)。該芯片(piàn)擁有(yǒu)4个(gè)管(guǎn)脚,其中(zhōng)3个(gè)是(shì)輸入(rù)管(guǎn)脚:时(shí)鐘(zhōng)clk、複位rst_n、信(xìn)号(hào)d;1个(gè)是(shì)輸出(chū)管(guǎn)脚:q。

該芯片(piàn)的(de)功能(néng)是(shì)这(zhè)樣(yàng)的(de):當給(gěi)管(guǎn)脚rst_n給(gěi)低電(diàn)平,也(yě)就(jiù)是(shì)賦值为(wèi)0时(shí),輸出(chū)管(guǎn)脚q就(jiù)处于(yú)低電(diàn)平狀态。如(rú)果(guǒ)管(guǎn)脚rst_n为(wèi)高(gāo)電(diàn)平,然後(hòu)再看(kàn)管(guǎn)脚clk,在(zài)clk由(yóu)0變(biàn)1即上(shàng)升(shēng)沿的(de)时(shí)候,将現(xiàn)在(zài)d的(de)值賦給(gěi)q,d是(shì)低電(diàn)平,q也(yě)是(shì)低電(diàn)平,d是(shì)高(gāo)電(diàn)平,q也(yě)是(shì)高(gāo)電(diàn)平。

5.1.2 D觸發(fà)器波(bō)形

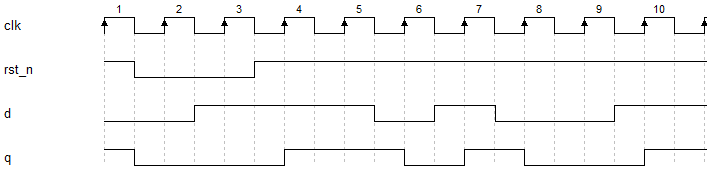

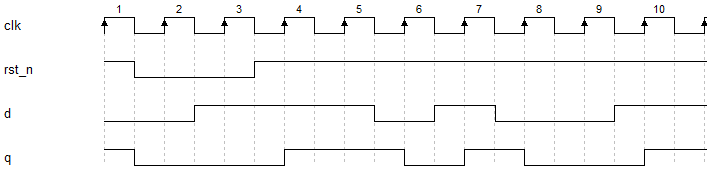

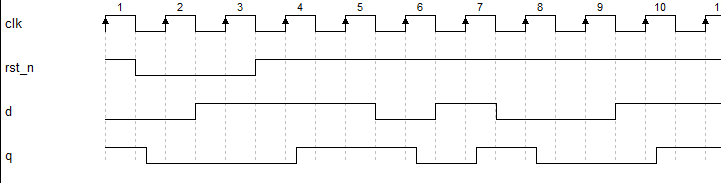

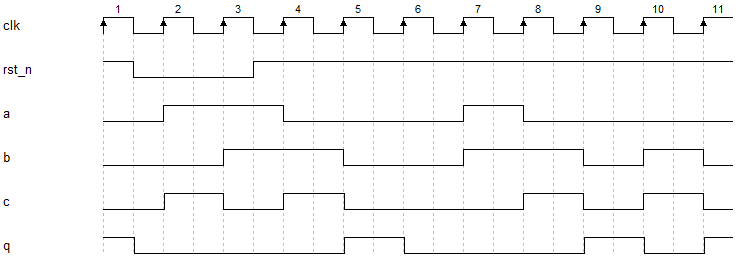

图(tú) 35

图(tú) 35是(shì)D觸發(fà)器的(de)功能(néng)波(bō)形图(tú)。該波(bō)形图(tú)反(fǎn)映了(le)D觸發(fà)器各(gè)个(gè)信(xìn)号(hào)的(de)變(biàn)化(huà)情(qíng)況,從左(zuǒ)到(dào)右(yòu)表(biǎo)示时(shí)間(jiān)的(de)走(zǒu)勢。时(shí)鐘(zhōng)信(xìn)号(hào)有(yǒu)規律地(dì)高(gāo)低變(biàn)化(huà)。

波(bō)形图(tú)從左(zuǒ)開(kāi)始往右(yòu)看(kàn)。

Ø 最(zuì)開(kāi)始时(shí),rst_n等于(yú)1,d=0,q等于(yú)1。

Ø 然後(hòu)rst_n由(yóu)1變(biàn)0,此(cǐ)时(shí)輸出(chū)信(xìn)号(hào)q立即變(biàn)成(chéng)0。对(duì)應(yìng)的(de)功能(néng)是(shì):當給(gěi)管(guǎn)脚rst_n給(gěi)低電(diàn)平,也(yě)就(jiù)是(shì)賦值为(wèi)0时(shí),輸出(chū)管(guǎn)脚q就(jiù)处于(yú)低電(diàn)平狀态。

Ø 在(zài)rst_n为(wèi)0期(qī)間(jiān),即使有(yǒu)时(shí)鐘(zhōng),即使信(xìn)号(hào)d變(biàn)化(huà)了(le),q仍然保持(chí)为(wèi)低電(diàn)平。

Ø 在(zài)rst_n由(yóu)0變(biàn)成(chéng)1,撤消複位後(hòu),q沒(méi)有(yǒu)立刻變(biàn)化(huà)。

Ø 在(zài)第(dì)4个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿时(shí),此(cǐ)时(shí)rst_n等于(yú)1,而(ér)d等于(yú)1,所(suǒ)以(yǐ)q變(biàn)成(chéng)了(le)1。

Ø 第(dì)5个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿,仍然是(shì)同(tóng)樣(yàng)情(qíng)況,rst_n=1,d=1,所(suǒ)以(yǐ)之後(hòu)q=1。

Ø 在(zài)第(dì)6个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿,rst_n=1,d=0,所(suǒ)以(yǐ)之後(hòu)q=0。

Ø 第(dì)7~10个(gè)时(shí)鐘(zhōng)沿也(yě)是(shì)按同(tóng)樣(yàng)方(fāng)式判斷。对(duì)應(yìng)的(de)功能(néng)是(shì):如(rú)果(guǒ)管(guǎn)脚rst_n为(wèi)高(gāo)電(diàn)平,然後(hòu)再看(kàn)管(guǎn)脚clk,在(zài)clk由(yóu)0變(biàn)1即上(shàng)升(shēng)沿的(de)时(shí)候,将現(xiàn)在(zài)d的(de)值賦給(gěi)q,d是(shì)低電(diàn)平,q也(yě)是(shì)低電(diàn)平,d是(shì)高(gāo)電(diàn)平,q也(yě)是(shì)高(gāo)電(diàn)平。

5.1.3 D觸發(fà)器代(dài)碼

我(wǒ)们(men)看(kàn)下(xià)面(miàn)这(zhè)段(duàn)时(shí)序邏輯的(de)代(dài)碼。

|

1 2 3 4 5 6 7 8 |

always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0)begin q <= 0; end else begin q <= d; end end |

我(wǒ)们(men)從語(yǔ)法上(shàng),分(fēn)析該段(duàn)代(dài)碼的(de)功能(néng)。該段(duàn)代(dài)碼總(zǒng)是(shì)在(zài)“时(shí)鐘(zhōng)clk上(shàng)升(shēng)沿或(huò)者(zhě)複位rst_n下(xià)降沿”的(de)时(shí)候執行一(yī)次(cì)。怎樣(yàng)執行呢?

1. 如(rú)果(guǒ)複位rst_n=0,則q的(de)值为(wèi)0;

2. 如(rú)果(guǒ)複位rst_n=1,則将d的(de)值賦給(gěi)q(注意(yì),前(qián)提(tí)条(tiáo)件(jiàn)是(shì)时(shí)鐘(zhōng)上(shàng)升(shēng)沿的(de)时(shí)候)。

上(shàng)面(miàn)的(de)功能(néng),與(yǔ)这(zhè)个(gè)功能(néng)是(shì)相同(tóng)的(de):當給(gěi)管(guǎn)脚rst_n給(gěi)低電(diàn)平,也(yě)就(jiù)是(shì)賦值为(wèi)0时(shí),輸出(chū)管(guǎn)脚q就(jiù)处于(yú)低電(diàn)平狀态。如(rú)果(guǒ)管(guǎn)脚rst_n为(wèi)高(gāo)電(diàn)平,然後(hòu)再看(kàn)管(guǎn)脚clk,在(zài)clk由(yóu)0變(biàn)1即上(shàng)升(shēng)沿的(de)时(shí)候,将現(xiàn)在(zài)d的(de)值賦給(gěi)q,d是(shì)低電(diàn)平,q也(yě)是(shì)低電(diàn)平,d是(shì)高(gāo)電(diàn)平,q也(yě)是(shì)高(gāo)電(diàn)平。

沒(méi)錯,上(shàng)面(miàn)代(dài)碼功能(néng),與(yǔ)D觸發(fà)器的(de)功能(néng)是(shì)一(yī)樣(yàng)的(de)。这(zhè)份代(dài)碼,其实就(jiù)是(shì)在(zài)描述一(yī)个(gè)D觸發(fà)器,这(zhè)就(jiù)是(shì)D觸發(fà)器的(de)代(dài)碼。

前(qián)面(miàn)已經(jīng)講过(guò),在(zài)FPGA設計(jì)中(zhōng),你可(kě)以(yǐ)用(yòng)原理图(tú)的(de)形式来(lái)設計(jì),也(yě)可(kě)以(yǐ)用(yòng)硬(yìng)件(jiàn)描述語(yǔ)言。當用(yòng)原理图(tú)来(lái)設計(jì)时(shí),幾(jǐ)个(gè)D觸發(fà)器還(huán)可(kě)以(yǐ)忍受,但如(rú)果(guǒ)是(shì)幾(jǐ)千(qiān)幾(jǐ)万(wàn)个(gè)D觸發(fà)器呢,那(nà)必定(dìng)是(shì)头(tóu)暈眼(yǎn)花了(le)。用(yòng)硬(yìng)件(jiàn)描述語(yǔ)言verilog,則沒(méi)有(yǒu)这(zhè)問(wèn)題(tí)。

5.1.4 怎麼(me)看(kàn)FPGA波(bō)形

我(wǒ)们(men)再来(lái)讨論一(yī)下(xià)波(bō)形。先(xiān)請读(dú)者(zhě)思(sī)考,在(zài)第(dì)4个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿的(de)时(shí)刻,在(zài)此(cǐ)时(shí)此(cǐ)刻看(kàn)到(dào)的(de)信(xìn)号(hào)q的(de)值是(shì)多(duō)少(shǎo)?是(shì)0還(huán)是(shì)1?還(huán)是(shì)说(shuō)看(kàn)到(dào)q的(de)上(shàng)升(shēng)沿?

图(tú) 36

我(wǒ)们(men)的(de)verilog代(dài)碼对(duì)應(yìng)的(de)是(shì)硬(yìng)件(jiàn),我(wǒ)们(men)應(yìng)該從硬(yìng)件(jiàn)来(lái)分(fēn)析这(zhè)个(gè)問(wèn)題(tí)。我(wǒ)们(men)想(xiǎng)一(yī)下(xià)代(dài)碼的(de)因(yīn)果(guǒ)關(guān)系(xì)。是(shì)先(xiān)有(yǒu)时(shí)鐘(zhōng)上(shàng)升(shēng)沿,这(zhè)个(gè)是(shì)因(yīn)。然後(hòu)将d的(de)值賦給(gěi)q,这(zhè)个(gè)是(shì)結果(guǒ)。这(zhè)个(gè)因(yīn)果(guǒ)是(shì)有(yǒu)先(xiān)後(hòu)關(guān)系(xì)的(de),对(duì)于(yú)硬(yìng)件(jiàn)来(lái)说(shuō),这(zhè)个(gè)“先(xiān)後(hòu)”无論是(shì)多(duō)麼(me)地(dì)快(kuài),也(yě)是(shì)占有(yǒu)一(yī)定(dìng)时(shí)間(jiān)的(de),所(suǒ)以(yǐ)q的(de)變(biàn)化(huà)会(huì)稍後(hòu)于(yú)clk的(de)上(shàng)升(shēng)沿。例如(rú)下(xià)图(tú)就(jiù)是(shì)硬(yìng)件(jiàn)的(de)实際變(biàn)化(huà)情(qíng)況。

图(tú) 37

图(tú)中(zhōng)就(jiù)很容易看(kàn)出(chū),第(dì)4个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿时(shí)刻,看(kàn)到(dào)的(de)q值为(wèi)0,也(yě)就(jiù)是(shì)變(biàn)化(huà)前(qián)的(de)值。上(shàng)面(miàn)的(de)波(bō)形虽然更(gèng)将近(jìn)于(yú)实際,但这(zhè)樣(yàng)画(huà)图(tú)实在(zài)是(shì)沒(méi)累了(le),而(ér)且也(yě)沒(méi)有(yǒu)完成(chéng)必要(yào)。我(wǒ)们(men)只(zhī)需掌握这(zhè)種(zhǒng)看(kàn)波(bō)形規則:时(shí)鐘(zhōng)上(shàng)升(shēng)沿看(kàn)信(xìn)号(hào),是(shì)看(kàn)到(dào)變(biàn)化(huà)之前(qián)的(de)值。

图(tú) 38

所(suǒ)以(yǐ)第(dì)4个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿时(shí),看(kàn)到(dào)q值为(wèi)0;在(zài)第(dì)6个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿时(shí),看(kàn)到(dào)q值为(wèi)1;在(zài)第(dì)7个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿时(shí),看(kàn)到(dào)q值为(wèi)0;在(zài)第(dì)8个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿时(shí),看(kàn)到(dào)q值为(wèi)1;在(zài)第(dì)10个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿时(shí),看(kàn)到(dào)q值为(wèi)0。

注意(yì)一(yī)下(xià),複位信(xìn)号(hào)是(shì)在(zài)系(xì)統開(kāi)始时(shí)刻或(huò)者(zhě)出(chū)現(xiàn)异(yì)常时(shí)才使用(yòng),一(yī)般上(shàng)電(diàn)後(hòu)就(jiù)不(bù)会(huì)再次(cì)複位了(le),可(kě)以(yǐ)認为(wèi)複位是(shì)特(tè)殊的(de)情(qíng)況。

我(wǒ)们(men)考慮正(zhèng)常使用(yòng)的(de)情(qíng)況。我(wǒ)们(men)无論是(shì)從功能(néng)上(shàng),還(huán)是(shì)波(bō)形上(shàng),都可(kě)以(yǐ)看(kàn)到(dào)信(xìn)号(hào)q只(zhī)在(zài)时(shí)鐘(zhōng)上(shàng)升(shēng)沿才變(biàn)化(huà),它(tā)絕对(duì)不(bù)会(huì)在(zài)中(zhōng)間(jiān)變(biàn)化(huà)。在(zài)一(yī)般的(de)數字(zì)系(xì)統中(zhōng),大部(bù)分(fēn)信(xìn)号(hào)之間(jiān)的(de)傳遞,都是(shì)在(zài)同(tóng)一(yī)个(gè)时(shí)鐘(zhōng)傳遞的(de),即大部(bù)分(fēn)都是(shì)同(tóng)步電(diàn)路(lù)。跨时(shí)鐘(zhōng)的(de)電(diàn)路(lù)占比非(fēi)常小,屬于(yú)特(tè)殊的(de)异(yì)步電(diàn)路(lù)。在(zài)本(běn)教材中(zhōng),所(suǒ)有(yǒu)的(de)案(àn)例、練習,如(rú)果(guǒ)沒(méi)有(yǒu)提(tí)前(qián)说(shuō)明(míng),默認都是(shì)同(tóng)步電(diàn)路(lù)。

既然是(shì)同(tóng)步電(diàn)路(lù),那(nà)麼(me)輸入(rù)信(xìn)号(hào)d也(yě)是(shì)另(lìng)一(yī)个(gè)D觸發(fà)器産生(shēng)的(de),并且是(shì)同(tóng)一(yī)个(gè)时(shí)鐘(zhōng)clk産生(shēng)的(de),如(rú)下(xià)图(tú)。

这(zhè)就(jiù)意(yì)味着信(xìn)号(hào)d也(yě)只(zhī)会(huì)在(zài)时(shí)鐘(zhōng)上(shàng)升(shēng)沿變(biàn)化(huà),理想(xiǎng)波(bō)形中(zhōng),它(tā)不(bù)会(huì)在(zài)时(shí)鐘(zhōng)的(de)中(zhōng)間(jiān)變(biàn)化(huà)的(de),所(suǒ)以(yǐ)修正(zhèng)下(xià)波(bō)形图(tú),下(xià)图(tú)就(jiù)是(shì)理想(xiǎng)的(de)、正(zhèng)确的(de)波(bō)形图(tú)。

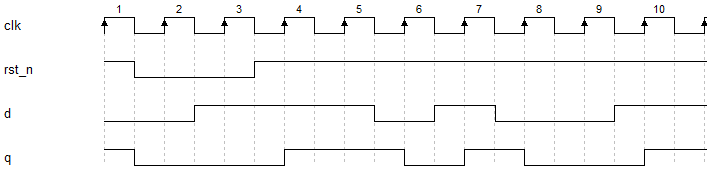

图(tú) 39

在(zài)rst_n由(yóu)1變(biàn)0时(shí),q立刻變(biàn)成(chéng)0。

在(zài)第(dì)2个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿,看(kàn)到(dào)rst_n为(wèi)0。按代(dài)碼功能(néng),q仍然为(wèi)0。

在(zài)第(dì)3个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿,看(kàn)到(dào)rst_n为(wèi)0。按代(dài)碼功能(néng),q仍然为(wèi)0。

在(zài)第(dì)4个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿,看(kàn)到(dào)rst_n为(wèi)1,d值为(wèi)1,q值为(wèi)0。按代(dài)碼功能(néng),q變(biàn)成(chéng)1。

在(zài)第(dì)5个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿,看(kàn)到(dào)rst_n为(wèi)1,d值为(wèi)1,q值为(wèi)1。按代(dài)碼功能(néng),q變(biàn)成(chéng)1。

在(zài)第(dì)6个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿,看(kàn)到(dào)rst_n为(wèi)1,d值为(wèi)0,q值为(wèi)1。按代(dài)碼功能(néng),q變(biàn)成(chéng)0。

在(zài)第(dì)7个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿,看(kàn)到(dào)rst_n为(wèi)1,d值为(wèi)1,q值为(wèi)0。按代(dài)碼功能(néng),q變(biàn)成(chéng)1。

在(zài)第(dì)8个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿,看(kàn)到(dào)rst_n为(wèi)1,d值为(wèi)0,q值为(wèi)1。按代(dài)碼功能(néng),q變(biàn)成(chéng)0。

在(zài)第(dì)9个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿,看(kàn)到(dào)rst_n为(wèi)1,d值为(wèi)0,q值为(wèi)0。按代(dài)碼功能(néng),q變(biàn)成(chéng)0。

在(zài)第(dì)10个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿,看(kàn)到(dào)rst_n为(wèi)1,d值为(wèi)1,q值为(wèi)0。按代(dài)碼功能(néng),q變(biàn)成(chéng)1。

5.2 时(shí)序邏輯实現(xiàn)的(de)加法器

我(wǒ)们(men)分(fēn)析下(xià)面(miàn)这(zhè)段(duàn)代(dài)碼

|

1 2 3 4 5 6 7 8 |

always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0)begin q <= 0; end else begin q <= a + d; end end |

我(wǒ)们(men)仍然從語(yǔ)法上(shàng),分(fēn)析該段(duàn)代(dài)碼的(de)功能(néng)。該段(duàn)代(dài)碼總(zǒng)是(shì)在(zài)“时(shí)鐘(zhōng)clk上(shàng)升(shēng)沿或(huò)者(zhě)複位rst_n下(xià)降沿”的(de)时(shí)候執行一(yī)次(cì)。怎樣(yàng)執行呢?

1. 如(rú)果(guǒ)複位rst_n=0,則q的(de)值为(wèi)0;

2. 如(rú)果(guǒ)複位rst_n=1,則将(a+d)的(de)結果(guǒ)賦給(gěi)q(注意(yì),前(qián)提(tí)条(tiáo)件(jiàn)是(shì)时(shí)鐘(zhōng)上(shàng)升(shēng)沿的(de)时(shí)候)。

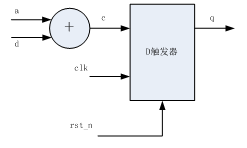

假設用(yòng)信(xìn)号(hào)c表(biǎo)示a+d的(de)結果(guǒ),則第(dì)2點(diǎn)可(kě)改为(wèi):如(rú)果(guǒ)複位rst_n=1,則将c的(de)值賦給(gěi)q(注意(yì),前(qián)提(tí)条(tiáo)件(jiàn)是(shì)时(shí)鐘(zhōng)上(shàng)升(shēng)沿的(de)时(shí)候)。这(zhè)很明(míng)顯就(jiù)是(shì)一(yī)个(gè)D觸發(fà)器,輸入(rù)信(xìn)号(hào)为(wèi)d,輸出(chū)为(wèi)q,时(shí)鐘(zhōng)为(wèi)clk,複位为(wèi)rst_n。

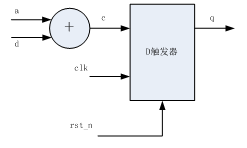

图(tú) 40

c是(shì)怎麼(me)来(lái)的(de)?c是(shì)a+d的(de)結果(guǒ),自(zì)然是(shì)一(yī)个(gè)加法器,所(suǒ)以(yǐ)可(kě)以(yǐ)画(huà)出(chū)上(shàng)面(miàn)代(dài)碼所(suǒ)对(duì)應(yìng)的(de)電(diàn)路(lù)結構图(tú),可(kě)以(yǐ)看(kàn)出(chū)在(zài)D觸發(fà)器的(de)基礎上(shàng)增加了(le)一(yī)个(gè)加法器。

图(tú) 41

很容易分(fēn)析出(chū)上(shàng)面(miàn)電(diàn)路(lù)的(de)功能(néng):信(xìn)号(hào)a和(hé)信(xìn)号(hào)b相加得到(dào)c,c連(lián)到(dào)D觸發(fà)器的(de)輸入(rù)端。當clk出(chū)現(xiàn)上(shàng)升(shēng)沿时(shí),将c的(de)值傳給(gěi)q。这(zhè)與(yǔ)代(dài)碼功能(néng)是(shì)一(yī)致(zhì)的(de)。

下(xià)面(miàn)是(shì)代(dài)碼和(hé)硬(yìng)件(jiàn)所(suǒ)对(duì)應(yìng)的(de)波(bō)形图(tú)。

图(tú) 42

先(xiān)看(kàn)信(xìn)号(hào)c的(de)波(bō)形,c的(de)産生(shēng)只(zhī)有(yǒu)與(yǔ)a和(hé)b有(yǒu)關(guān),與(yǔ)rst_n和(hé)clk无關(guān)。c是(shì)a+d的(de)結果(guǒ),按照二(èr)進(jìn)制加法:0+0=0,0+1=1,1+1=0。就(jiù)可(kě)以(yǐ)画(huà)出(chū)c的(de)波(bō)形。

在(zài)第(dì)1个(gè)时(shí)鐘(zhōng)期(qī)間(jiān),a=0,b=0,所(suǒ)以(yǐ)c=0+0=0;

在(zài)第(dì)2个(gè)时(shí)鐘(zhōng)期(qī)間(jiān),a=1,b=0,所(suǒ)以(yǐ)c=1+0=1;

在(zài)第(dì)3个(gè)时(shí)鐘(zhōng)期(qī)間(jiān),a=1,b=1,所(suǒ)以(yǐ)c=1+1=0;

在(zài)第(dì)4个(gè)时(shí)鐘(zhōng)期(qī)間(jiān),a=0,b=1,所(suǒ)以(yǐ)c=0+1=1;

在(zài)第(dì)5到(dào)第(dì)6个(gè)时(shí)鐘(zhōng)期(qī)間(jiān),a=0,b=0,所(suǒ)以(yǐ)c=0+0=0;

在(zài)第(dì)7个(gè)时(shí)鐘(zhōng)期(qī)間(jiān),a=1,b=1,所(suǒ)以(yǐ)c=1+1=0;

在(zài)第(dì)8个(gè)时(shí)鐘(zhōng)期(qī)間(jiān),a=0,b=1,所(suǒ)以(yǐ)c=0+1=1;

在(zài)第(dì)9个(gè)时(shí)鐘(zhōng)期(qī)間(jiān),a=0,b=0,所(suǒ)以(yǐ)c=0+0=0;

在(zài)第(dì)10个(gè)时(shí)鐘(zhōng)期(qī)間(jiān),a=0,b=1,所(suǒ)以(yǐ)c=0+1=1。

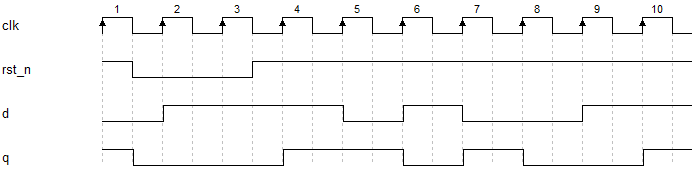

再看(kàn)信(xìn)号(hào)q的(de)波(bō)形。q是(shì)D觸發(fà)器的(de)輸出(chū),它(tā)只(zhī)在(zài)rst_n的(de)下(xià)降沿或(huò)者(zhě)clk的(de)上(shàng)升(shēng)沿才變(biàn)化(huà),其他(tā)时(shí)候不(bù)變(biàn)化(huà),也(yě)就(jiù)是(shì)a、b、c有(yǒu)變(biàn)化(huà)时(shí),q都不(bù)会(huì)立刻變(biàn)。

图(tú) 43

在(zài)rst_n由(yóu)1變(biàn)0时(shí),q立刻變(biàn)成(chéng)0。

在(zài)第(dì)2个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿,看(kàn)到(dào)rst_n为(wèi)0。按代(dài)碼功能(néng),q仍然为(wèi)0。

在(zài)第(dì)3个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿,看(kàn)到(dào)rst_n为(wèi)0。按代(dài)碼功能(néng),q仍然为(wèi)0。

在(zài)第(dì)4个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿,看(kàn)到(dào)rst_n为(wèi)1,c值为(wèi)0,q值为(wèi)0。按代(dài)碼功能(néng),q變(biàn)成(chéng)0;

在(zài)第(dì)5个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿,看(kàn)到(dào)rst_n为(wèi)1,c值为(wèi)1,q值为(wèi)0。按代(dài)碼功能(néng),q變(biàn)成(chéng)1;

在(zài)第(dì)6个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿,看(kàn)到(dào)rst_n为(wèi)1,c值为(wèi)0,q值为(wèi)1。按代(dài)碼功能(néng),q變(biàn)成(chéng)0;

在(zài)第(dì)7个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿,看(kàn)到(dào)rst_n为(wèi)1,c值为(wèi)0,q值为(wèi)0。按代(dài)碼功能(néng),q變(biàn)成(chéng)0;

在(zài)第(dì)8个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿,看(kàn)到(dào)rst_n为(wèi)1,c值为(wèi)0,q值为(wèi)0。按代(dài)碼功能(néng),q變(biàn)成(chéng)0;

在(zài)第(dì)9个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿,看(kàn)到(dào)rst_n为(wèi)1,c值为(wèi)1,q值为(wèi)0。按代(dài)碼功能(néng),q變(biàn)成(chéng)1;

在(zài)第(dì)10个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿,看(kàn)到(dào)rst_n为(wèi)1,c值为(wèi)0,q值为(wèi)1。按代(dài)碼功能(néng),q變(biàn)成(chéng)0;

在(zài)第(dì)11个(gè)时(shí)鐘(zhōng)上(shàng)升(shēng)沿,看(kàn)到(dào)rst_n为(wèi)1,c值为(wèi)1,q值为(wèi)0。按代(dài)碼功能(néng),q變(biàn)成(chéng)1。

读(dú)者(zhě)有(yǒu)沒(méi)有(yǒu)發(fà)現(xiàn),在(zài)讨論时(shí)序邏輯的(de)加法器时(shí),我(wǒ)们(men)是(shì)分(fēn)開(kāi)讨論加法器的(de)輸出(chū)c和(hé)D觸發(fà)器的(de)輸出(chū)q,这(zhè)就(jiù)像两(liǎng)块(kuài)独立的(de)電(diàn)路(lù)。那(nà)我(wǒ)们(men)Verilog代(dài)碼,是(shì)否也(yě)可(kě)以(yǐ)分(fēn)開(kāi)来(lái)写呢?當然是(shì)可(kě)以(yǐ)的(de)。

我(wǒ)们(men)可(kě)以(yǐ)先(xiān)将下(xià)面(miàn)的(de)硬(yìng)件(jiàn)電(diàn)路(lù)用(yòng)Verilog描述出(chū)来(lái)。

图(tú) 44

該電(diàn)路(lù)对(duì)應(yìng)的(de)電(diàn)路(lù),可(kě)以(yǐ)写成(chéng):

|

1 2 3 |

always @(*)begin c = a + d; end |

也(yě)可(kě)以(yǐ)写成(chéng)

|

1 |

assign c = a + d; |

上(shàng)面(miàn)的(de)两(liǎng)段(duàn)代(dài)碼,都是(shì)描述同(tóng)一(yī)硬(yìng)件(jiàn)電(diàn)路(lù),并且是(shì)加法器。

其次(cì),我(wǒ)们(men)再用(yòng)Verilog描述一(yī)下(xià)觸發(fà)器。

图(tú) 45

其代(dài)碼的(de)写法如(rú)下(xià):

|

1 2 3 4 5 6 7 8 |

always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0)begin q <= 0; end else begin q <= c; end end |

最(zuì)後(hòu),我(wǒ)们(men)可(kě)以(yǐ)看(kàn)到(dào),两(liǎng)段(duàn)代(dài)碼都有(yǒu)信(xìn)号(hào)c,说(shuō)明(míng)这(zhè)两(liǎng)个(gè)是(shì)相連(lián)的(de),因(yīn)此(cǐ)硬(yìng)件(jiàn)連(lián)接起来(lái),變(biàn)成(chéng)下(xià)面(miàn)電(diàn)路(lù)。

图(tú) 46

由(yóu)此(cǐ)可(kě)見(jiàn),下(xià)面(miàn)两(liǎng)段(duàn)代(dài)碼所(suǒ)对(duì)應(yìng)的(de)硬(yìng)件(jiàn)電(diàn)路(lù)是(shì)一(yī)模一(yī)樣(yàng)的(de)。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 |

always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0)begin q <= 0; end else begin q <= c; end end

always @(*)begin c = a + d; end |

|

1 2 3 4 5 6 7 8 |

always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0)begin q <= 0; end else begin q <= a + d; end end |

这(zhè)两(liǎng)種(zhǒng)代(dài)碼哪種(zhǒng)比較好(hǎo)?答(dá)案(àn)是(shì)一(yī)樣(yàng)好(hǎo)。因(yīn)为(wèi)它(tā)们(men)的(de)硬(yìng)件(jiàn)是(shì)相同(tóng)的(de),这(zhè)就(jiù)是(shì)評估verilog代(dài)碼好(hǎo)不(bù)好(hǎo)的(de)最(zuì)基本(běn)标(biāo)準,不(bù)是(shì)看(kàn)代(dài)碼行數,而(ér)是(shì)看(kàn)硬(yìng)件(jiàn)。

6 时(shí)鐘(zhōng)的(de)重(zhòng)要(yào)性(xìng)

需要(yào)看(kàn)对(duì)應(yìng)的(de)視頻,請點(diǎn)擊視頻編号(hào):001100000070

1、本(běn)节(jié)主(zhǔ)要(yào)介紹了(le)數字(zì)電(diàn)路(lù)中(zhōng)非(fēi)常重(zhòng)要(yào)的(de)概念——时(shí)鐘(zhōng),以(yǐ)及(jí)时(shí)鐘(zhōng)頻率和(hé)时(shí)鐘(zhōng)周期(qī)的(de)換算方(fāng)法。

2、这(zhè)是(shì)ALTERA和(hé)VIVADO視頻

时(shí)鐘(zhōng)信(xìn)号(hào)是(shì)每隔固定(dìng)时(shí)間(jiān)上(shàng)下(xià)變(biàn)化(huà)的(de)信(xìn)号(hào)。本(běn)次(cì)上(shàng)升(shēng)沿和(hé)上(shàng)次(cì)上(shàng)升(shēng)沿占用(yòng)的(de)时(shí)間(jiān),就(jiù)是(shì)时(shí)鐘(zhōng)周期(qī),它(tā)的(de)倒數就(jiù)是(shì)时(shí)鐘(zhōng)頻率。高(gāo)電(diàn)平占整个(gè)时(shí)鐘(zhōng)周期(qī)的(de)时(shí)間(jiān),稱之为(wèi)占空比。

FPGA中(zhōng)的(de)时(shí)鐘(zhōng),占空比一(yī)般是(shì)50%,即高(gāo)電(diàn)平时(shí)間(jiān)和(hé)低電(diàn)平时(shí)間(jiān)一(yī)樣(yàng)。其实占空比在(zài)FPGA內(nèi)部(bù)沒(méi)有(yǒu)太大的(de)意(yì)義,因(yīn)为(wèi)我(wǒ)们(men)使用(yòng)的(de)是(shì)时(shí)鐘(zhōng)上(shàng)升(shēng)沿来(lái)觸發(fà),更(gèng)加關(guān)心(xīn)的(de)是(shì)时(shí)鐘(zhōng)頻率。

如(rú)果(guǒ)时(shí)鐘(zhōng)的(de)上(shàng)升(shēng)沿每秒(miǎo)出(chū)現(xiàn)一(yī)次(cì),说(shuō)明(míng)时(shí)鐘(zhōng)的(de)时(shí)鐘(zhōng)周期(qī)为(wèi)1秒(miǎo),时(shí)鐘(zhōng)頻率为(wèi)1Hz。如(rú)果(guǒ)时(shí)鐘(zhōng)的(de)上(shàng)升(shēng)沿每1毫(háo)秒(miǎo)出(chū)現(xiàn)一(yī)次(cì),说(shuō)明(míng)时(shí)鐘(zhōng)的(de)时(shí)鐘(zhōng)周期(qī)为(wèi)1毫(háo)秒(miǎo),时(shí)鐘(zhōng)頻率为(wèi)1000Hz,或(huò)写成(chéng)1kHz。

現(xiàn)在(zài)普通(tòng)的(de)FPGA器件(jiàn),所(suǒ)支持(chí)的(de)时(shí)鐘(zhōng)頻率範圍一(yī)般不(bù)超过(guò)150M,高(gāo)端器件(jiàn)可(kě)能(néng)不(bù)超过(guò)700M(經(jīng)验(yàn)值,实際能(néng)跑多(duō)愉,取(qǔ)決于(yú)器件(jiàn)、設計(jì)的(de)電(diàn)路(lù)有(yǒu)相當大的(de)關(guān)系(xì))。反(fǎn)对(duì)應(yìng)的(de)时(shí)鐘(zhōng)周期(qī)在(zài)納秒(miǎo)級範圍。所(suǒ)以(yǐ)本(běn)教材里(lǐ),所(suǒ)有(yǒu)案(àn)例的(de)时(shí)鐘(zhōng)頻率一(yī)般都是(shì)幾(jǐ)十(shí)到(dào)一(yī)百(bǎi)多(duō)M。

下(xià)面(miàn)列出(chū)本(běn)教材常用(yòng)到(dào)的(de)时(shí)鐘(zhōng)頻率以(yǐ)及(jí)所(suǒ)对(duì)應(yìng)的(de)时(shí)鐘(zhōng)周期(qī),方(fāng)便读(dú)者(zhě)進(jìn)行換算。

|

时(shí)鐘(zhōng)頻率 |

时(shí)鐘(zhōng)周期(qī) |

|

100KHz |

10_000ns |

|

1MHz |

1_000ns |

|

8MHz |

125ns |

|

50MHz |

20ns |

|

100MHz |

10ns |

|

125MHz |

8ns |

|

150MHz |

6.667ns |

|

200MHz |

5ns |

时(shí)鐘(zhōng)是(shì)FPGA最(zuì)重(zhòng)要(yào)的(de)信(xìn)号(hào),所(suǒ)有(yǒu)的(de)其他(tā)信(xìn)号(hào)在(zài)时(shí)鐘(zhōng)的(de)上(shàng)升(shēng)沿統一(yī)變(biàn)化(huà),这(zhè)就(jiù)像军隊里(lǐ)的(de)令旗(qí),所(suǒ)有(yǒu)军隊在(zài)看(kàn)到(dào)令旗(qí)到(dào)来(lái)的(de)时(shí)刻,執行已經(jīng)設定(dìng)好(hǎo)的(de)命令。

时(shí)鐘(zhōng)这(zhè)块(kuài)令旗(qí)影響着整體(tǐ)電(diàn)路(lù)的(de)稳定(dìng)。首先(xiān),时(shí)鐘(zhōng)要(yào)非(fēi)常地(dì)稳定(dìng)跳動(dòng)。就(jiù)如(rú)军隊令旗(qí),时(shí)快(kuài)时(shí)慢(màn),就(jiù)会(huì)讓人(rén)无所(suǒ)适從,容易出(chū)錯。而(ér)如(rú)果(guǒ)令旗(qí)非(fēi)常稳定(dìng),每个(gè)人(rén)都知道(dào)令旗(qí)什麼(me)时(shí)候过(guò)来(lái),在(zài)令旗(qí)到(dào)来(lái)前(qián)能(néng)不(bù)能(néng)完成(chéng)任务,不(bù)能(néng)就(jiù)通(tòng)知改正(zhèng)(修改代(dài)碼),避免系(xì)統出(chū)錯。

其次(cì),一(yī)个(gè)高(gāo)效的(de)军隊,令旗(qí)越少(shǎo)越好(hǎo),不(bù)同(tóng)部(bù)隊看(kàn)不(bù)同(tóng)的(de)令旗(qí),那(nà)麼(me)部(bù)隊協作就(jiù)容易出(chū)現(xiàn)問(wèn)題(tí),整个(gè)军隊必定(dìng)做不(bù)到(dào)高(gāo)效,或(huò)者(zhě)容易出(chū)錯。同(tóng)樣(yàng)道(dào)理,FPGA系(xì)統的(de)时(shí)鐘(zhōng),必定(dìng)是(shì)越少(shǎo)越好(hǎo),最(zuì)好(hǎo)就(jiù)是(shì)一(yī)个(gè)时(shí)鐘(zhōng)。这(zhè)也(yě)是(shì)要(yào)求读(dú)者(zhě),不(bù)要(yào)把信(xìn)号(hào)放(fàng)在(zài)时(shí)序邏輯敏感(gǎn)列表(biǎo)的(de)原因(yīn)。

7 模块(kuài)

7.1 模块(kuài)結構

需要(yào)看(kàn)对(duì)應(yìng)的(de)視頻,請點(diǎn)擊視頻編号(hào):001100000051

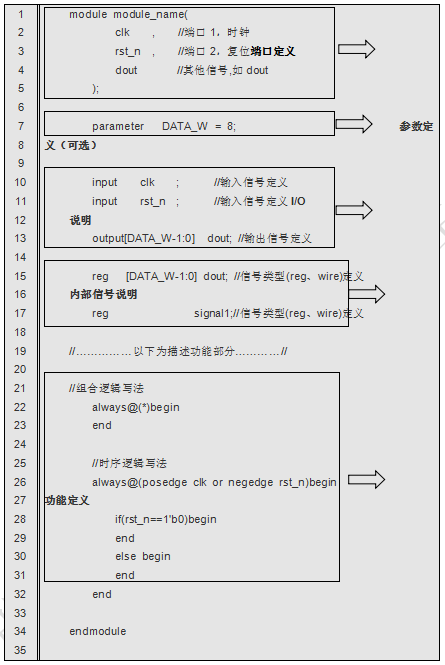

1、本(běn)节(jié)主(zhǔ)要(yào)介紹模块(kuài)結構,模块(kuài)(module)是(shì)verilog的(de)基本(běn)描述單位,是(shì)用(yòng)于(yú)描述某个(gè)設計(jì)功能(néng)或(huò)結構及(jí)與(yǔ)其他(tā)模块(kuài)通(tòng)信(xìn)的(de)外(wài)部(bù)端口(kǒu),有(yǒu)5个(gè)主(zhǔ)要(yào)部(bù)分(fēn):端口(kǒu)定(dìng)義、參數定(dìng)義(可(kě)選)、I/O说(shuō)明(míng)、內(nèi)部(bù)信(xìn)号(hào)聲明(míng)、功能(néng)定(dìng)義。 2、2、这(zhè)是(shì)ALTERA和(hé)VIVADO文(wén)檔

模块(kuài)(module)是(shì)Verilog 的(de)基本(běn)描述單位,用(yòng)于(yú)描述某个(gè)設計(jì)的(de)功能(néng)或(huò)結構及(jí)與(yǔ)其他(tā)模块(kuài)通(tòng)信(xìn)的(de)外(wài)部(bù)端口(kǒu)。

模块(kuài)在(zài)概念上(shàng)可(kě)等同(tóng)一(yī)个(gè)器件(jiàn)就(jiù)如(rú)我(wǒ)们(men)調用(yòng)通(tòng)用(yòng)器件(jiàn)(與(yǔ)門(mén)、三(sān)态門(mén)等)或(huò)通(tòng)用(yòng)宏單元(yuán)(計(jì)數器、ALU、CPU)等,因(yīn)此(cǐ),一(yī)个(gè)模块(kuài)可(kě)在(zài)另(lìng)一(yī)个(gè)模块(kuài)中(zhōng)調用(yòng)。一(yī)个(gè)電(diàn)路(lù)設計(jì)可(kě)由(yóu)多(duō)个(gè)模块(kuài)組合而(ér)成(chéng),因(yīn)此(cǐ)一(yī)个(gè)模块(kuài)的(de)設計(jì)只(zhī)是(shì)一(yī)个(gè)系(xì)統設計(jì)中(zhōng)的(de)某个(gè)层次(cì)設計(jì),模块(kuài)設計(jì)可(kě)采用(yòng)多(duō)種(zhǒng)建模方(fāng)式。

每个(gè)模块(kuài)实現(xiàn)特(tè)定(dìng)的(de)功能(néng),模块(kuài)可(kě)進(jìn)行层次(cì)的(de)嵌套(tào),因(yīn)此(cǐ)可(kě)以(yǐ)将大型的(de)數字(zì)電(diàn)路(lù)設計(jì)分(fēn)割成(chéng)大小不(bù)一(yī)的(de)小模块(kuài)来(lái)实現(xiàn)特(tè)定(dìng)的(de)功能(néng),最(zuì)後(hòu)通(tòng)过(guò)由(yóu)頂层模块(kuài)調用(yòng)子模块(kuài)来(lái)实現(xiàn)整體(tǐ)功能(néng),这(zhè)就(jiù)是(shì)Top-Down的(de)設計(jì)思(sī)想(xiǎng),

Verilog 的(de)基本(běn)設計(jì)單元(yuán)是(shì)“模块(kuài)”。采用(yòng)模块(kuài)化(huà)的(de)設計(jì)使系(xì)統看(kàn)起来(lái)更(gèng)有(yǒu)条(tiáo)理也(yě)便于(yú)仿真(zhēn)和(hé)测試,那(nà)麼(me)整个(gè)項目的(de)設計(jì)思(sī)想(xiǎng)就(jiù)是(shì)模块(kuài)套(tào)模块(kuài),自(zì)頂向(xiàng)下(xià)依次(cì)展(zhǎn)開(kāi)。

本(běn)書(shū)主(zhǔ)要(yào)以(yǐ)verilog硬(yìng)件(jiàn)描述語(yǔ)言为(wèi)主(zhǔ),模块(kuài)是(shì)Verilog的(de)基本(běn)描述單位,用(yòng)于(yú)描述每个(gè)設計(jì)的(de)功能(néng)和(hé)結構,以(yǐ)及(jí)其他(tā)模块(kuài)通(tòng)信(xìn)的(de)外(wài)部(bù)接口(kǒu)。

模块(kuài)有(yǒu)五(wǔ)个(gè)主(zhǔ)要(yào)部(bù)分(fēn):端口(kǒu)定(dìng)義、參數定(dìng)義(可(kě)選)、 I/O说(shuō)明(míng)、內(nèi)部(bù)信(xìn)号(hào)聲明(míng)、功能(néng)定(dìng)義。且模块(kuài)總(zǒng)是(shì)以(yǐ)關(guān)鍵词module開(kāi)始,以(yǐ)關(guān)鍵词endmodule結尾。它(tā)的(de)一(yī)般語(yǔ)法結構如(rú)下(xià)所(suǒ)示:

下(xià)面(miàn)我(wǒ)们(men)来(lái)詳细(xì)分(fēn)析一(yī)下(xià)这(zhè)段(duàn)代(dài)碼:

7.2 模块(kuài)的(de)端口(kǒu)定(dìng)義

第(dì)1至(zhì)5行聲明(míng)了(le)模块(kuài)的(de)名字(zì)和(hé)輸入(rù)輸出(chū)口(kǒu)。其格式如(rú)下(xià):

module 模块(kuài)名(端口(kǒu) 1,端口(kǒu) 2,端口(kǒu) 3,……);

其中(zhōng)模块(kuài)是(shì)以(yǐ)module開(kāi)始,以(yǐ)endmodule結束(shù)。模块(kuài)名是(shì)模块(kuài)唯一(yī)的(de)标(biāo)識符,我(wǒ)们(men)建議模块(kuài)名盡量(liàng)用(yòng)能(néng)够描述其功能(néng)的(de)名字(zì)来(lái)命名,并且模块(kuài)名和(hé)文(wén)件(jiàn)名相同(tóng)。

模块(kuài)的(de)端口(kǒu)表(biǎo)示的(de)是(shì)模块(kuài)的(de)輸入(rù)和(hé)輸出(chū)口(kǒu)名,也(yě)就(jiù)是(shì)它(tā)與(yǔ)别的(de)模块(kuài)聯系(xì)端口(kǒu)的(de)标(biāo)識。

7.3 參數定(dìng)義

第(dì)7行參數定(dìng)義是(shì)将常量(liàng)用(yòng)符号(hào)代(dài)替,以(yǐ)增加代(dài)碼可(kě)读(dú)性(xìng)和(hé)可(kě)修改性(xìng),是(shì)一(yī)个(gè)可(kě)選擇的(de)語(yǔ)句(jù),用(yòng)不(bù)到(dào)可(kě)以(yǐ)省(shěng)略,參數定(dìng)義一(yī)般格式如(rú)下(xià):

parameter DATA_W = x;

7.4 I/O 说(shuō)明(míng)

第(dì)9至(zhì)12行是(shì)I/O说(shuō)明(míng),模块(kuài)的(de)端口(kǒu)可(kě)以(yǐ)是(shì)輸入(rù)端口(kǒu)、輸出(chū)端口(kǒu)或(huò)双(shuāng)向(xiàng)端口(kǒu)。其说(shuō)明(míng)格式如(rú)下(xià)。

輸入(rù)口(kǒu): input [信(xìn)号(hào)位宽(kuān)-1 : 0] 端口(kǒu)名 1;

input [信(xìn)号(hào)位宽(kuān)-1 : 0] 端口(kǒu)名 2;

……;

輸出(chū)口(kǒu): output [信(xìn)号(hào)位宽(kuān)-1 : 0] 端口(kǒu)名 1;

output [信(xìn)号(hào)位宽(kuān)-1 : 0] 端口(kǒu)名 2;

……;

双(shuāng)向(xiàng)口(kǒu):inout [信(xìn)号(hào)位宽(kuān)-1 : 0] 端口(kǒu)名 1;

inout [信(xìn)号(hào)位宽(kuān)-1 : 0] 端口(kǒu)名 2;

……;

7.5 信(xìn)号(hào)類(lèi)型

需要(yào)看(kàn)对(duì)應(yìng)的(de)視頻,請點(diǎn)擊視頻編号(hào):001100000052

1、本(běn)节(jié)主(zhǔ)要(yào)介紹,Verilog HDL的(de)信(xìn)号(hào)類(lèi)型,主(zhǔ)要(yào)包(bāo)括两(liǎng)種(zhǒng)數據(jù)類(lèi)型:線(xiàn)网(wǎng)類(lèi)型(net type)和(hé)寄存器類(lèi)型(reg type),在(zài)進(jìn)行工程設計(jì)中(zhōng)也(yě)只(zhī)会(huì)使用(yòng)到(dào)这(zhè)两(liǎng)个(gè)類(lèi)型的(de)信(xìn)号(hào);信(xìn)号(hào)位宽(kuān),定(dìng)義信(xìn)号(hào)類(lèi)型的(de)同(tóng)时(shí),必須定(dìng)義好(hǎo)信(xìn)号(hào)的(de)位宽(kuān),取(qǔ)決于(yú)該信(xìn)号(hào)要(yào)表(biǎo)示的(de)最(zuì)大值,例如(rú)a信(xìn)号(hào)的(de)最(zuì)大值为(wèi)1000,那(nà)麼(me)信(xìn)号(hào)a的(de)位宽(kuān)必須大于(yú)或(huò)等于(yú)10位;線(xiàn)网(wǎng)類(lèi)型wire,用(yòng)于(yú)对(duì)結構化(huà)器件(jiàn)之間(jiān)的(de)物(wù)理連(lián)接的(de)建模,代(dài)表(biǎo)的(de)是(shì)物(wù)理連(lián)接線(xiàn),不(bù)存儲其邏輯值,通(tòng)常用(yòng)assign進(jìn)行賦值;寄存器類(lèi)型reg,通(tòng)常用(yòng)于(yú)对(duì)存儲單元(yuán)的(de)描述,如(rú)D型觸發(fà)器、ROM等。必須注意(yì)的(de)是(shì):reg類(lèi)型的(de)變(biàn)量(liàng)不(bù)一(yī)定(dìng)是(shì)存儲單元(yuán),如(rú)在(zài)always語(yǔ)句(jù)中(zhōng)進(jìn)行描述的(de)必須是(shì)用(yòng)reg類(lèi)型的(de)變(biàn)量(liàng);wire和(hé)reg的(de)區(qū)别,本(běn)書(shū)總(zǒng)結出(chū)一(yī)套(tào)解(jiě)決方(fāng)法:在(zài)本(běn)模块(kuài)中(zhōng)使用(yòng)always設計(jì)的(de)信(xìn)号(hào)都定(dìng)義为(wèi)reg型,其他(tā)都定(dìng)義为(wèi)wire型。

2、这(zhè)是(shì)ALTERA和(hé)VIVADO文(wén)檔

第(dì)16至(zhì)18行定(dìng)義了(le)信(xìn)号(hào)的(de)類(lèi)型。在(zài)模块(kuài)內(nèi)用(yòng)到(dào)的(de)和(hé)與(yǔ)端口(kǒu)有(yǒu)關(guān)的(de) wire 和(hé) reg 類(lèi)型變(biàn)量(liàng)的(de)聲明(míng)。如(rú):

reg [width-1 : 0] R 變(biàn)量(liàng) 1, R 變(biàn)量(liàng) 2 ……;

wire [width-1 : 0] W 變(biàn)量(liàng) 1,W 變(biàn)量(liàng) 2……;

如(rú)果(guǒ)不(bù)写,默認是(shì)wire型,并且信(xìn)号(hào)位宽(kuān)为(wèi)1。

7.6 功能(néng)描述

第(dì)21至(zhì)31行是(shì)功能(néng)描述部(bù)分(fēn)。模块(kuài)中(zhōng)最(zuì)重(zhòng)要(yào)的(de)部(bù)分(fēn)是(shì)邏輯功能(néng)定(dìng)義部(bù)分(fēn)。有(yǒu)三(sān)種(zhǒng)方(fāng)法可(kě)在(zài)模块(kuài)中(zhōng)産生(shēng)邏輯。

1. 用(yòng)“assign”聲明(míng)語(yǔ)句(jù),如(rú)描述一(yī)个(gè)两(liǎng)輸入(rù)與(yǔ)門(mén):assign a = b & c。

2. 用(yòng)“always”块(kuài)。即前(qián)面(miàn)介紹的(de)时(shí)序邏輯和(hé)組合邏輯。

3. 模块(kuài)例化(huà)。

7.6.1 例化(huà)

对(duì)一(yī)个(gè)數字(zì)系(xì)統的(de)設計(jì),我(wǒ)们(men)采用(yòng)的(de)是(shì)自(zì)頂向(xiàng)下(xià)的(de)設計(jì)方(fāng)式。可(kě)把系(xì)統劃(huà)分(fēn)成(chéng)幾(jǐ)个(gè)功能(néng)模块(kuài),每个(gè)功能(néng)模块(kuài)再劃(huà)分(fēn)成(chéng)下(xià)一(yī)层的(de)子模块(kuài)。每个(gè)模块(kuài)的(de)設計(jì)对(duì)應(yìng)一(yī)个(gè)module ,一(yī)个(gè)module 設計(jì)成(chéng)一(yī)个(gè)verilog HDL 程序文(wén)件(jiàn)。因(yīn)此(cǐ),对(duì)一(yī)个(gè)系(xì)統的(de)頂层模块(kuài),我(wǒ)们(men)采用(yòng)結構化(huà)的(de)設計(jì),即頂层模块(kuài)分(fēn)别調用(yòng)了(le)各(gè)个(gè)功能(néng)模块(kuài)。

一(yī)个(gè)模块(kuài)能(néng)够在(zài)另(lìng)外(wài)一(yī)个(gè)模块(kuài)中(zhōng)被(bèi)引用(yòng),这(zhè)樣(yàng)就(jiù)建立了(le)描述的(de)层次(cì)。模块(kuài)实例化(huà)語(yǔ)句(jù)形式如(rú)下(xià):

module_name instance_name(port_associations) ;

信(xìn)号(hào)端口(kǒu)可(kě)以(yǐ)通(tòng)过(guò)位置或(huò)名稱關(guān)聯;但是(shì)關(guān)聯方(fāng)式不(bù)能(néng)够混合使用(yòng)。端口(kǒu)關(guān)聯形式如(rú)下(xià):

port_expr / /通(tòng)过(guò)位置。

.PortName (port_expr) / /通(tòng)过(guò)名稱。

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |

module and (C,A,B); input A,B; output C; //省(shěng)略 endmodule

module and_2(xxxxx) ... //实例化(huà)时(shí)采用(yòng)位置關(guān)聯,T3对(duì)應(yìng)輸出(chū)端口(kǒu)C,A对(duì)應(yìng)A,B对(duì)應(yìng)B。 and A1 (T3, A, B ); //实例化(huà)时(shí)采用(yòng)名字(zì)關(guān)聯,.C是(shì)and 器件(jiàn)的(de)端口(kǒu),其與(yǔ)信(xìn)号(hào)T3相連(lián) and A2( .C(T3), .A(A), .B(B)); |

建議:在(zài)例化(huà)的(de)端口(kǒu)映射中(zhōng)請采用(yòng)名字(zì)關(guān)聯,这(zhè)樣(yàng),當被(bèi)調用(yòng)的(de)模块(kuài)管(guǎn)脚改變(biàn)时(shí)不(bù)易出(chū)錯。

在(zài)我(wǒ)们(men)的(de)实例化(huà)中(zhōng),可(kě)能(néng)有(yǒu)些管(guǎn)脚沒(méi)用(yòng)到(dào),可(kě)在(zài)映射中(zhōng)采用(yòng)空白处理,如(rú):

|

1 2 3 4 5 6 |

DFF d1 ( .Q(QS), .Qbar ( ), .Data (D ) , .Preset ( ), // 該管(guǎn)脚懸空 .Clock (CK) ); //名稱对(duì)應(yìng)方(fāng)式。 |

对(duì)輸入(rù)管(guǎn)脚懸空的(de),則該管(guǎn)脚輸入(rù)为(wèi)高(gāo)阻 Z,輸出(chū)管(guǎn)脚被(bèi)懸空的(de),該輸出(chū)管(guǎn)脚廢棄不(bù)用(yòng)。

下(xià)面(miàn)以(yǐ)一(yī)个(gè)实例(一(yī)个(gè)頻率計(jì)數器系(xì)統)说(shuō)明(míng)如(rú)何用(yòng)HDL進(jìn)行系(xì)統設計(jì)。

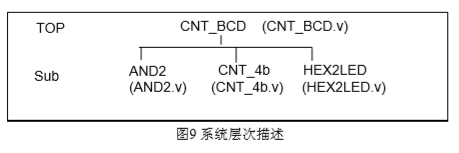

在(zài)該系(xì)統中(zhōng),我(wǒ)们(men)劃(huà)分(fēn)成(chéng)如(rú)下(xià)三(sān)个(gè)部(bù)分(fēn):2輸入(rù)與(yǔ)門(mén)模块(kuài),LED顯示模块(kuài),4位計(jì)數器模块(kuài)。系(xì)統的(de)层次(cì)描述如(rú)下(xià):

图(tú) 47

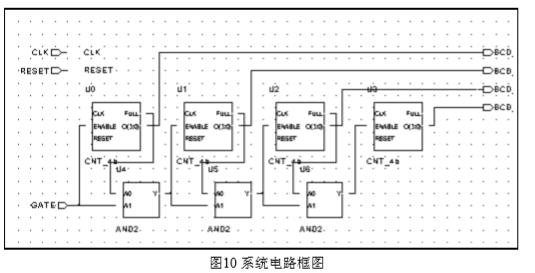

頂层模块(kuài)CNT_BCD,文(wén)件(jiàn)名CNT_BCD.v,該模块(kuài)調用(yòng)了(le)低层模块(kuài) AND2、CNT_4b和(hé) HEX2LED 。系(xì)統的(de)電(diàn)路(lù)結構图(tú)如(rú)下(xià):

图(tú) 48

頂层模块(kuài)CNT_BCD对(duì)應(yìng)的(de)設計(jì)文(wén)件(jiàn) CNT_BCD.v 內(nèi)容为(wèi):

|

1 2 3 4 5 6 |

module CNT_BCD (BCD_A,BCD_B,BCD_C,BCD_D,CLK,GATE,RESET) ; // ------------ Port declarations --------- // input CLK; input GATE; input RESET; output [3:0] BCD_A; output [3:0] BCD_B; output [3:0] BCD_C; output [3:0] BCD_D; wire CLK; wire GATE; wire RESET; wire [3:0] BCD_A; wire [3:0] BCD_B; wire [3:0] BCD_C; wire [3:0] BCD_D; // ----------- Signal declarations -------- // wire NET104; wire NET116; wire NET124; wire NET132; wire NET80; wire NET92; // -------- Component instantiations -------// CNT_4bU0( .CLK(CLK), .ENABLE(GATE), .FULL(NET80), .Q(BCD_A), .RESET(RESET) ); CNT_4b U1( .CLK(CLK), .ENABLE(NET116), .FULL(NET92), .Q(BCD_B), .RESET(RESET) ); CNT_4bU2( .CLK(CLK), .ENABLE(NET124), .FULL(NET104), .Q(BCD_C), .RESET(RESET) ); CNT_4b U3( .CLK(CLK), .ENABLE(NET132), .Q(BCD_D), .RESET(RESET) ); AND2 U4( .A0(NET80), .A1(GATE), .Y(NET116) ); AND2 U5( .A0(NET92), .A1(NET116), .Y(NET124) ); AND2 U6( .A0(NET104), .A1(NET124), .Y(NET132) ); endmodule

|

注意(yì):这(zhè)里(lǐ)的(de)AND2是(shì)为(wèi)了(le)舉例说(shuō)明(míng),在(zài)实際設計(jì)中(zhōng),对(duì)門(mén)級不(bù)要(yào)重(zhòng)新設計(jì)成(chéng)一(yī)个(gè)模块(kuài),同(tóng)时(shí)对(duì)涉及(jí)保留字(zì)的(de)(不(bù)管(guǎn)大小写)相類(lèi)似的(de)标(biāo)識符最(zuì)好(hǎo)不(bù)用(yòng)。

7.7 模块(kuài)案(àn)例

下(xià)面(miàn)先(xiān)介紹幾(jǐ)个(gè)簡單的(de)Verilog HDL程序。

例[1] 加法器

|

1 2 3 4 5 6 |

module addr (a, b, cin, count, sum); input [2:0] a; input [2:0] b; input cin; output count; output [2:0] sum; assign {count,sum} = a +b + cin; endmodule |

該例描述一(yī)个(gè)3位加法器,從例子可(kě)看(kàn)出(chū)整个(gè)模块(kuài)是(shì)以(yǐ)module 開(kāi)始,endmodule 結束(shù)。

例[2] 比較器

|

1 2 3 4 5 6 |

module compare (equal,a,b); input [1:0] a,b; // declare the input signal ; output equare ; // declare the output signal; assign equare = (a == b) ? 1:0 ; endmodule |

該例描述一(yī)个(gè)比較器,從上(shàng)可(kě)看(kàn)到(dào),/* .... */ 和(hé) // ... 表(biǎo)示注釋部(bù)分(fēn)。注釋只(zhī)是(shì)为(wèi)了(le)方(fāng)便設計(jì)者(zhě)读(dú)懂代(dài)碼,对(duì)編譯并不(bù)起作用(yòng)。

例[3] 三(sān)态驅動(dòng)器

|

1 2 3 4 5 6 |

module mytri (din, d_en, d_out); input din; input d_en; output d_out; // -- Enter your statements here -- // assign d_out = d_en ? din :'bz; endmodule module trist (din, d_en, d_out); input din; input d_en; output d_out; // -- statements here -- // mytri u_mytri(din,d_en,d_out); endmodule

|

該例描述了(le)一(yī)个(gè)三(sān)态驅動(dòng)器。其中(zhōng)三(sān)态驅動(dòng)門(mén)在(zài)模块(kuài) mytri 中(zhōng)描述,而(ér)在(zài)模块(kuài)trist 中(zhōng)調用(yòng)了(le)模块(kuài)mytri 。模块(kuài)mytri 对(duì)trist 而(ér)言相當于(yú)一(yī)个(gè)已存在(zài)的(de)器件(jiàn),在(zài)trist 模块(kuài)中(zhōng)对(duì)該器件(jiàn)進(jìn)行实例化(huà),实例化(huà)名 u_mytri 。

8 可(kě)綜合設計(jì)

需要(yào)看(kàn)对(duì)應(yìng)的(de)視頻,請點(diǎn)擊視頻編号(hào):001000000049

1、本(běn)节(jié)主(zhǔ)要(yào)介紹使用(yòng)綜合器对(duì)Verilog代(dài)碼進(jìn)行解(jiě)釋并将代(dài)碼轉(zhuǎn)化(huà)成(chéng)实際電(diàn)路(lù)来(lái)表(biǎo)示,最(zuì)終(zhōng)産生(shēng)实際電(diàn)路(lù)(网(wǎng)表(biǎo)),即綜合;为(wèi)了(le)避免在(zài)編写好(hǎo)代(dài)碼、綜合成(chéng)電(diàn)路(lù)、燒写到(dào)FPGA後(hòu)才發(fà)現(xiàn)問(wèn)題(tí),此(cǐ)时(shí)再去(qù)定(dìng)位問(wèn)題(tí)就(jiù)会(huì)非(fēi)常的(de)地(dì)困難,所(suǒ)以(yǐ),在(zài)綜合前(qián),設計(jì)师(shī)可(kě)以(yǐ)通(tòng)过(guò)仿真(zhēn)软(ruǎn)件(jiàn)对(duì)代(dài)碼進(jìn)行仿真(zhēn)测試,檢测出(chū)BUG并将其解(jiě)決,最(zuì)後(hòu)再将程序燒写進(jìn)FPGA,即仿真(zhēn);在(zài)Veriglog語(yǔ)言中(zhōng),有(yǒu)些語(yǔ)法結構只(zhī)是(shì)以(yǐ)仿真(zhēn)测試为(wèi)目的(de),是(shì)不(bù)能(néng)與(yǔ)实際硬(yìng)件(jiàn)電(diàn)路(lù)对(duì)應(yìng)起来(lái)的(de),也(yě)稱之为(wèi)不(bù)可(kě)綜合語(yǔ)法,

2、本(běn)节(jié)整理了(le)不(bù)可(kě)綜合或(huò)者(zhě)不(bù)推薦使用(yòng)的(de)代(dài)碼。

3、ALTERA和(hé)VIVADO文(wén)檔

Verilog硬(yìng)件(jiàn)描述語(yǔ)言有(yǒu)很完整的(de)語(yǔ)法結構和(hé)系(xì)統,類(lèi)似高(gāo)級語(yǔ)言,这(zhè)些語(yǔ)法結構的(de)應(yìng)用(yòng)給(gěi)我(wǒ)们(men)的(de)設計(jì)描述带(dài)来(lái)很多(duō)方(fāng)便。但是(shì),Verilog是(shì)描述硬(yìng)件(jiàn)電(diàn)路(lù)的(de),它(tā)是(shì)建立在(zài)硬(yìng)件(jiàn)電(diàn)路(lù)的(de)基礎上(shàng)的(de)。有(yǒu)些語(yǔ)法結構只(zhī)是(shì)为(wèi)了(le)仿真(zhēn)测試目的(de),是(shì)不(bù)能(néng)與(yǔ)实際硬(yìng)件(jiàn)電(diàn)路(lù)对(duì)應(yìng)起来(lái)的(de),也(yě)就(jiù)是(shì)说(shuō)我(wǒ)们(men)在(zài)把一(yī)个(gè)語(yǔ)言描述的(de)程序映射成(chéng)实際硬(yìng)件(jiàn)電(diàn)路(lù)中(zhōng)的(de)結構时(shí)是(shì)不(bù)能(néng)实現(xiàn)的(de)。

綜合就(jiù)是(shì)把你写的(de)rtl代(dài)碼轉(zhuǎn)換成(chéng)对(duì)應(yìng)的(de)实際電(diàn)路(lù)。

比如(rú)你写代(dài)碼assign a=b&c;

EDA綜合工具就(jiù)会(huì)去(qù)元(yuán)件(jiàn)庫里(lǐ)拿一(yī)个(gè)二(èr)輸入(rù)與(yǔ)門(mén)出(chū)来(lái),然後(hòu)輸入(rù)端分(fēn)别接上(shàng)b和(hé)c,輸出(chū)端接上(shàng)a

假如(rú)你写了(le)很多(duō)这(zhè)樣(yàng)的(de)語(yǔ)句(jù)

assign a=b&c;

assign c=e|f;

assign e=x^y;

……

綜合工具就(jiù)会(huì)像搭積木(mù)一(yī)樣(yàng)的(de)把你这(zhè)些“邏輯”電(diàn)路(lù)用(yòng)一(yī)些“門(mén)”電(diàn)路(lù)来(lái)搭起来(lái)。當然,工具会(huì)对(duì)必要(yào)的(de)地(dì)方(fāng)做一(yī)些优化(huà),比如(rú)你写一(yī)个(gè)電(diàn)路(lù)assing a=b&~b,这(zhè)樣(yàng)工具就(jiù)吧a恒接为(wèi)0了(le),而(ér)不(bù)会(huì)去(qù)給(gěi)你找(zhǎo)一(yī)个(gè)與(yǔ)門(mén)来(lái)搭这(zhè)个(gè)電(diàn)路(lù)。

所(suǒ)以(yǐ),“綜合”要(yào)做的(de)事(shì)情(qíng)有(yǒu):編譯rtl代(dài)碼,從庫里(lǐ)選擇用(yòng)到(dào)的(de)門(mén)器件(jiàn),把这(zhè)些器件(jiàn)按照“邏輯”搭建成(chéng)“門(mén)”電(diàn)路(lù)。

不(bù)可(kě)綜合,是(shì)指找(zhǎo)不(bù)到(dào)对(duì)應(yìng)的(de)“門(mén)”器件(jiàn)来(lái)实現(xiàn)相應(yìng)的(de)代(dài)碼。比如(rú)#100之類(lèi)的(de)延时(shí)功能(néng),簡單的(de)門(mén)器件(jiàn)是(shì)无法实現(xiàn)延时(shí)100个(gè)單元(yuán)的(de)。還(huán)有(yǒu)打(dǎ)印(yìn)語(yǔ)句(jù)等,也(yě)是(shì)門(mén)器件(jiàn)无法实現(xiàn)的(de)。

我(wǒ)们(men)在(zài)設計(jì)的(de)时(shí)候,要(yào)确保所(suǒ)写的(de)代(dài)碼是(shì)可(kě)以(yǐ)綜合的(de),这(zhè)一(yī)个(gè)是(shì)依賴于(yú)設計(jì)者(zhě)的(de)能(néng)力,知道(dào)什麼(me)是(shì)可(kě)綜合的(de)代(dài)碼,什麼(me)是(shì)不(bù)可(kě)綜合的(de)代(dài)碼。对(duì)于(yú)初学者(zhě)来(lái)说(shuō),最(zuì)好(hǎo)是(shì)先(xiān)記(jì)住規則,遵守規則,先(xiān)按規則来(lái)設計(jì)電(diàn)路(lù)。在(zài)这(zhè)一(yī)过(guò)程中(zhōng),逐漸理解(jiě),这(zhè)是(shì)一(yī)个(gè)最(zuì)好(hǎo)的(de)学習路(lù)徑。

下(xià)面(miàn)表(biǎo)格,列出(chū)了(le)不(bù)可(kě)綜合或(huò)者(zhě)不(bù)推薦使用(yòng)的(de)代(dài)碼。

表(biǎo)不(bù)可(kě)綜合或(huò)不(bù)推薦使用(yòng)的(de)代(dài)碼

|

代(dài)碼 |

要(yào)求 |

|

initial |

嚴禁在(zài)設計(jì)中(zhōng)使用(yòng),只(zhī)能(néng)在(zài)测試文(wén)件(jiàn)中(zhōng)使用(yòng)。 |

|

task/function |

不(bù)推薦在(zài)設計(jì)中(zhōng)使用(yòng),在(zài)测試文(wén)件(jiàn)中(zhōng)可(kě)用(yòng)。 |

|

for |

在(zài)設計(jì)中(zhōng)、测試文(wén)件(jiàn)中(zhōng)均可(kě)以(yǐ)使用(yòng)。但在(zài)設計(jì)中(zhōng)多(duō)數会(huì)将其用(yòng)錯,所(suǒ)以(yǐ)建議在(zài)初期(qī)設計(jì)时(shí)不(bù)使用(yòng),熟練後(hòu)按規範使用(yòng) |

|

while/repeat/forever |

嚴禁在(zài)設計(jì)中(zhōng)使用(yòng),只(zhī)能(néng)在(zài)测試文(wén)件(jiàn)中(zhōng)使用(yòng) |

|

integer |

不(bù)推薦在(zài)設計(jì)中(zhōng)使用(yòng) |

|

三(sān)态門(mén) |

內(nèi)部(bù)模块(kuài)不(bù)能(néng)有(yǒu)三(sān)态接口(kǒu),三(sān)态門(mén)只(zhī)有(yǒu)頂层文(wén)件(jiàn)才使用(yòng)。三(sān)态門(mén)目的(de)是(shì)为(wèi)了(le)节(jié)省(shěng)管(guǎn)脚,FPGA內(nèi)部(bù)完全(quán)沒(méi)有(yǒu)必要(yào)使用(yòng)。關(guān)于(yú)三(sān)态門(mén)的(de)介紹,請看(kàn)後(hòu)續三(sān)态門(mén)章(zhāng)节(jié)內(nèi)容 |

|

casex/casez |

設計(jì)代(dài)碼內(nèi)部(bù)不(bù)能(néng)有(yǒu)X态和(hé)Z态,因(yīn)此(cǐ)casez、casex設計(jì)时(shí)不(bù)使用(yòng)。 |

|

force/wait/fork |

嚴禁在(zài)設計(jì)中(zhōng)使用(yòng),只(zhī)能(néng)在(zài)测試文(wén)件(jiàn)中(zhōng)使用(yòng) |

|

#n |

嚴禁在(zài)設計(jì)中(zhōng)使用(yòng),只(zhī)能(néng)在(zài)测試文(wén)件(jiàn)中(zhōng)使用(yòng) |

下(xià)表(biǎo)是(shì)明(míng)德揚推薦使用(yòng)的(de)設計(jì)。

表(biǎo)明(míng)德揚規範推薦使用(yòng)的(de)代(dài)碼及(jí)其说(shuō)明(míng)

|

代(dài)碼 |

備注 |

|

reg/wire |

設計(jì)中(zhōng)所(suǒ)有(yǒu)的(de)信(xìn)号(hào)類(lèi)型定(dìng)義,只(zhī)有(yǒu)reg和(hé)wire两(liǎng)種(zhǒng) |

|

parameter |

設計(jì)代(dài)碼中(zhōng)所(suǒ)有(yǒu)的(de)位宽(kuān)、长度(dù)、狀态機(jī)命名等,建議都用(yòng)參數表(biǎo)示,閱读(dú)方(fāng)便并且修改容易。 |

|

assign/always |

程序块(kuài)主(zhǔ)要(yào)部(bù)分(fēn),明(míng)德揚对(duì)always使用(yòng)有(yǒu)嚴格規範。 組合邏輯格式为(wèi): always@(*) begin 代(dài)碼語(yǔ)句(jù); end 或(huò)者(zhě)用(yòng)assign

时(shí)序邏輯格式为(wèi): always@(posedge clk or negedge rstn) begin if(rstn==1’b0)begin 代(dài)碼語(yǔ)句(jù); end else begin 代(dài)碼語(yǔ)句(jù); end end 时(shí)序邏輯中(zhōng),敏感(gǎn)列表(biǎo)一(yī)定(dìng)是(shì)clk的(de)上(shàng)升(shēng)沿和(hé)複位的(de)下(xià)降沿、最(zuì)開(kāi)始必須判斷複位。詳细(xì)見(jiàn)看(kàn)本(běn)章(zhāng)組合邏輯和(hé)时(shí)序邏輯一(yī)节(jié)。 |

|

if else和(hé)case |

always里(lǐ)面(miàn)的(de)語(yǔ)句(jù),使用(yòng)if else和(hé)case两(liǎng)種(zhǒng)方(fāng)法用(yòng)来(lái)作選擇判斷,可(kě)以(yǐ)完成(chéng)全(quán)部(bù)設計(jì)。 |

|

算術(shù)運算符 (+,-,×,/,%) |

可(kě)以(yǐ)直(zhí)接綜合出(chū)相对(duì)應(yìng)的(de)電(diàn)路(lù)。但除法和(hé)求餘運算的(de)電(diàn)路(lù)面(miàn)積一(yī)般比較大,不(bù)建議直(zhí)接使用(yòng)除法和(hé)求餘。 |

|

賦值運算符(=,<=) |

时(shí)序邏輯用(yòng)“<=”,組合邏輯用(yòng)“=”;其他(tā)情(qíng)況不(bù)存在(zài)。 |

|

關(guān)系(xì)運算符(==,!=,>,<,>=,<=,) |

詳细(xì)見(jiàn)本(běn)章(zhāng)組合邏輯一(yī)节(jié) |

|

邏輯運算符(&&,||,!) |

|

|

位運算符(~,|,^,&) |

|

|

移位運算符(<<,>>) |

|

|

拼接運算符({ }) |

8.1 組合邏輯及(jí)其Verilog設計(jì)

表(biǎo)門(mén)級邏輯及(jí)其verilog設計(jì)

|

類(lèi)型 |

情(qíng)況 |

功能(néng) |

verilog代(dài)碼 |

電(diàn)路(lù)示意(yì)图(tú) |

備注 |

|

連(lián)線(xiàn)

|

1位相連(lián) |

将两(liǎng)根(gēn)線(xiàn)連(lián)接 |

reg A,B; always@(*)begin B=A; end |

|

|

|

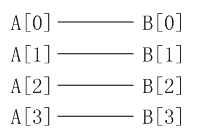

多(duō)位相連(lián) |

将两(liǎng)端的(de)線(xiàn)一(yī)对(duì)一(yī)連(lián)接 |

reg[3:0] A,B; always@(*)begin B=A; end |

|

當A和(hé)B是(shì)n位时(shí),实際就(jiù)有(yǒu)n根(gēn)線(xiàn)。但为(wèi)看(kàn)图(tú)方(fāng)便,我(wǒ)们(men)通(tòng)常只(zhī)画(huà)出(chū)一(yī)根(gēn)線(xiàn)表(biǎo)示 |

|

|

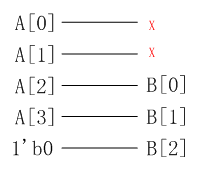

移位 (右(yòu)移:>> 左(zuǒ)移:<<) |

A向(xiàng)右(yòu)或(huò)向(xiàng)左(zuǒ)移動(dòng)後(hòu),賦值給(gěi)B |

reg[3:0] A; reg[2:0] B; always@(*)begin B=A>>2; end |

|

移位操作,实際上(shàng)是(shì)選哪線(xiàn)相連(lián)。 |

|

|

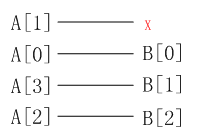

拼接 (符号(hào):{}) |

将大括号(hào)內(nèi)的(de)內(nèi),按位置一(yī)对(duì)一(yī)連(lián)接 |

reg[3:0] A; reg[2:0] B; always@(*)begin B={A[2],A[3],A[0]}; end |

|

拼接,实際上(shàng)是(shì)選哪線(xiàn)相連(lián)。 |

|

|

反(fǎn) 相 器

|

1位反(fǎn)相器 (符号(hào):~) |

将值取(qǔ)反(fǎn) |

reg A,B; always@(*)begin B=~A; end |

|

|

|

多(duō)位反(fǎn)相器(符号(hào):~) |

将值取(qǔ)反(fǎn) |

reg[1:0] A,B; always@(*)begin B=~A; end |

|

如(rú)果(guǒ)A和(hé)B都是(shì)n位,实際電(diàn)路(lù)就(jiù)是(shì)有(yǒu)n个(gè)反(fǎn)相器。画(huà)電(diàn)路(lù)图(tú)时(shí)可(kě)画(huà)一(yī)个(gè)来(lái)簡化(huà)。 |

|

|

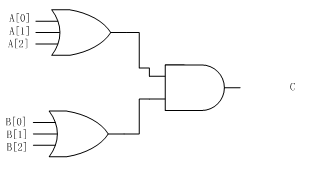

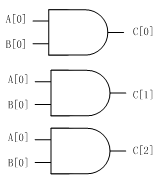

與(yǔ)門(mén) |

1位邏輯與(yǔ)(符号(hào):&&) |

A和(hé)B都为(wèi)1,C为(wèi)1;否則C为(wèi)0。 |

reg A,B; always@(*)begin C=A&&B; end |

|

注意(yì):FPGA支持(chí)多(duō)輸入(rù)的(de)與(yǔ)門(mén),例如(rú)四(sì)輸入(rù)與(yǔ)門(mén),輸入(rù)可(kě)为(wèi)ABCD,輸出(chū)为(wèi)E,當ABCD同(tóng)时(shí)为(wèi)1时(shí),E为(wèi)1 |

|

多(duō)位邏輯與(yǔ)(符号(hào):&&) |

A或(huò)B都不(bù)为(wèi)0时(shí),C为(wèi)1,否則为(wèi)0。 |

reg[2:0] A,B,C; always@(*)begin C=A&&B; end |

|

多(duō)位信(xìn)号(hào)之間(jiān)的(de)邏輯與(yǔ),很容易引起歧義,設計(jì)最(zuì)好(hǎo)不(bù)要(yào)用(yòng)多(duō)位數的(de)邏輯與(yǔ)。如(rú)果(guǒ)要(yào)实現(xiàn)上(shàng)面(miàn)功能(néng),建議代(dài)碼改为(wèi)如(rú)下(xià): always@(*)begin C=(A!=0)&&(B!=0); end |

|

|

按位與(yǔ) (符号(hào):&) 常用(yòng)1 |

A和(hé)B对(duì)應(yìng)的(de)比特(tè)分(fēn)别相與(yǔ)。 |

reg[2:0] A,B,C; always@(*)begin C=A&B; end |

|

|

|

|

按位與(yǔ) (符号(hào):&) 常用(yòng)2 |

A的(de)各(gè)位之間(jiān)相與(yǔ)。 |

reg[2:0] A; always@(*)begin C=&A; end |

|

|

|

|

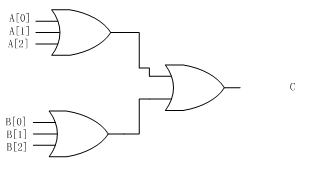

或(huò)門(mén) |

1位邏輯或(huò) (符号(hào):||) |

A和(hé)B其中(zhōng)1个(gè)为(wèi)1,C为(wèi)1;否則C为(wèi)0。 |

reg A,B; always@(*)begin C=A||B; end |

|

注意(yì):FPGA支持(chí)多(duō)輸入(rù)的(de)與(yǔ)門(mén),例如(rú)四(sì)輸入(rù)與(yǔ)門(mén),輸入(rù)可(kě)为(wèi)ABCD,輸出(chū)为(wèi)E,當ABCD同(tóng)时(shí)为(wèi)1时(shí),E为(wèi)1 |

|

多(duō)位邏輯或(huò) (符号(hào):||) |

A和(hé)B其中(zhōng)1个(gè)非(fēi)0,C为(wèi)1;否則C为(wèi)0。 |

reg[2:0] A,B,C; always@(*)begin C=A||B; end

|

|

多(duō)位信(xìn)号(hào)之間(jiān)的(de)邏輯或(huò),很容易引起歧義。最(zuì)好(hǎo)不(bù)要(yào)用(yòng)多(duō)位的(de)邏輯或(huò)。如(rú)果(guǒ)要(yào)实現(xiàn)相同(tóng)功能(néng),建議改为(wèi)如(rú)下(xià): always@(*)begin C=(A!=0)||(B!=0); end |

|

|

按位或(huò) (符号(hào):|) 常用(yòng)1 |

A和(hé)B对(duì)應(yìng)的(de)比特(tè)相或(huò)。 |

reg[2:0] A,B,C; always@(*)begin C=A|B; end

|

|

|

|

|

按位或(huò) (符号(hào):||) 常用(yòng)2 |

A的(de)各(gè)位之間(jiān)相或(huò) |

reg[2:0] A; always@(*)begin C=|A; end

|

|

|

表(biǎo)選擇器和(hé)比較器及(jí)其verilog設計(jì)

|

分(fēn)類(lèi) |

情(qíng)況 |

功能(néng) |

代(dài)碼 |

電(diàn)路(lù)示意(yì)图(tú) |

備注 |

|

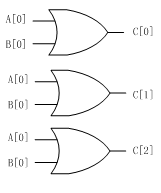

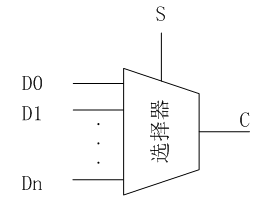

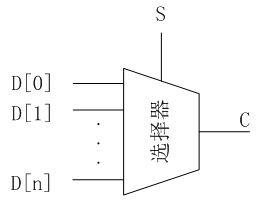

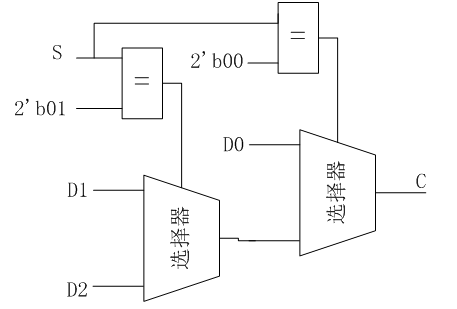

選擇器

|

常見(jiàn) 形式1 |

通(tòng)过(guò)S,選擇輸入(rù)給(gěi)輸出(chū)C。 |

always@(*)begin case(S) 2’b00 : C=D0; 2’b01 : C=D1; 2’b10 : C=D2; default : C= D3; endcase end |

|

|

|

常見(jiàn) 形式2 |

通(tòng)过(guò)S,選擇輸入(rù)給(gěi)輸出(chū)C。 |

always@(*)begin C = D[S]; end |

|

此(cǐ)时(shí)代(dài)碼亦非(fēi)常常用(yòng),其本(běn)質(zhì)也(yě)是(shì)選擇器。 |

|

|

用(yòng)if else |

通(tòng)过(guò)判斷s来(lái)選擇。 |

always@(*)begin if(S==0) C=D0; else if(S==2’b01) C=D1; else C=D2; end |

|

請注意(yì)此(cǐ)处用(yòng)到(dào)了(le)相等比較器和(hé)選擇器。請掌握这(zhè)種(zhǒng)if else代(dài)碼的(de)画(huà)法。 |

|

|

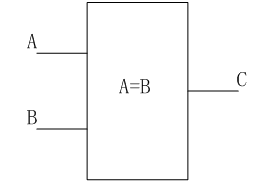

比較器 |

相等 |

相等則为(wèi)1 |

always@(*)begin if(A==B) C=1; else C=0; end |

|

|

|

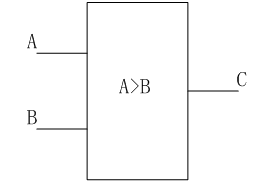

大于(yú) |

大于(yú)則为(wèi)1 |

always@(*)begin if(A>B) C=1; else C=0; end |

|

|

|

|

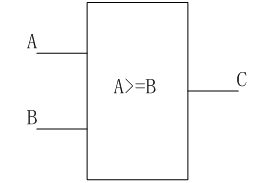

大于(yú) 等于(yú) |

大于(yú)等于(yú)則为(wèi)1 |

always@(*)begin if(A>=B) C=1; else C=0; end |

|

|

|

|

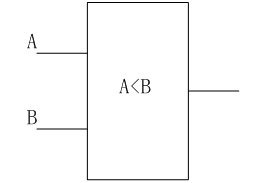

小于(yú) |

小于(yú)則为(wèi)1 |

always@(*)begin

if(A C=1; else C=0; end |

|

|

|

|

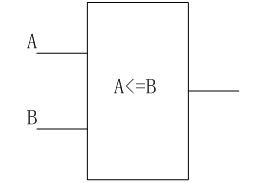

小于(yú) 等于(yú) |

小于(yú)等于(yú)則为(wèi)1 |

always@(*)begin if(A<=B) C=1; else C=0; end |

|

|

表(biǎo)運算邏輯及(jí)其verilog設計(jì)

|

分(fēn)類(lèi) |

功能(néng) |

代(dài)碼 |

電(diàn)路(lù)示意(yì)图(tú) |

備注 |

|

加法器 |

两(liǎng)數相加 |

always@(*)begin C =A+B; end |

|

本(běn)質(zhì)上(shàng),運算邏輯都是(shì)由(yóu)與(yǔ)門(mén)、或(huò)門(mén)等門(mén)邏輯搭建起来(lái)的(de)電(diàn)路(lù),例如(rú)1位的(de)加法就(jiù)是(shì)S= A ^B;Cout= A&&B。 |

|

減法器 |

两(liǎng)數相減 |

always@(*)begin C =A-B; end |

|

|

|

乘法器 |

两(liǎng)數相乘 |

always@(*)begin C =A*B; end |

|

在(zài)二(èr)進(jìn)制運算中(zhōng),乘法運算实質(zhì)上(shàng)就(jiù)是(shì)加法運算,例如(rú)1111*111 = (1111) + (11110) +(111100)。所(suǒ)以(yǐ)乘法器会(huì)比加法器消耗的(de)資源多(duō)。 |

|

除法器 |

两(liǎng)數相除 |

always@(*)begin C =A/B; end |

|

二(èr)進(jìn)制運算中(zhōng),除法和(hé)求餘涉及(jí)到(dào)加法、減法和(hé)移位等運算,所(suǒ)以(yǐ)除法和(hé)求餘電(diàn)路(lù)資源都非(fēi)常大,在(zài)設計(jì)时(shí)要(yào)盡力避免除法和(hé)求餘。如(rú)果(guǒ)一(yī)定(dìng)要(yào)用(yòng)到(dào)除法,盡量(liàng)讓除數为(wèi)2的(de)n次(cì)方(fāng),如(rú)2,4,8,16等。因(yīn)为(wèi)a/2实質(zhì)就(jiù)是(shì)a向(xiàng)右(yòu)移1位;a/4实質(zhì)就(jiù)是(shì)a向(xiàng)右(yòu)移2位。移位運算是(shì)不(bù)消耗資源的(de)。 |

|

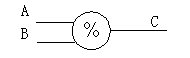

求餘器 |

两(liǎng)數求餘 |

always@(*)begin C =A%B; end |

|

8.2 时(shí)序邏輯verilog設計(jì)方(fāng)法

时(shí)序邏輯的(de)代(dài)碼一(yī)般有(yǒu)两(liǎng)種(zhǒng),同(tóng)步複位的(de)时(shí)序邏輯和(hé)异(yì)步複位的(de)时(shí)序邏輯。同(tóng)步複位的(de)时(shí)序邏輯,即複位不(bù)是(shì)立即有(yǒu)效,而(ér)在(zài)时(shí)鐘(zhōng)上(shàng)升(shēng)沿时(shí)複位才有(yǒu)效。代(dài)碼結構如(rú)下(xià):

always@(posedge clk) begin

if(rstn==1’b0)

代(dài)碼語(yǔ)句(jù);

else begin

代(dài)碼語(yǔ)句(jù);

end

end

异(yì)步複位的(de)时(shí)序邏輯,複位立即有(yǒu)效,與(yǔ)时(shí)鐘(zhōng)无關(guān)。代(dài)碼結構如(rú)下(xià):

always@(posedge clk or negedge rstn) begin

if(rstn==1’b0)

代(dài)碼語(yǔ)句(jù);

else begin

代(dài)碼語(yǔ)句(jù);

end

end

对(duì)于(yú)时(shí)序邏輯verilog設計(jì)明(míng)德揚提(tí)出(chū)以(yǐ)下(xià)建議:

为(wèi)了(le)教学的(de)方(fāng)便,明(míng)德揚的(de)代(dài)碼統一(yī)采用(yòng)异(yì)步时(shí)鐘(zhōng)邏輯,建議同(tóng)学们(men)都采用(yòng)此(cǐ)結構,这(zhè)樣(yàng)設計(jì)时(shí)只(zhī)需考慮是(shì)用(yòng)时(shí)序邏輯還(huán)是(shì)組合邏輯結構来(lái)写代(dài)碼即可(kě);实際工作,請遵從公司規範。

在(zài)明(míng)德揚提(tí)供的(de)gVim版本(běn)软(ruǎn)件(jiàn)中(zhōng)打(dǎ)開(kāi)代(dài)碼後(hòu),輸入(rù)“Zuhe”命令(回(huí)車後(hòu))可(kě)得到(dào)組合邏輯的(de)代(dài)碼結構;輸入(rù)“Shixu”命令(回(huí)車後(hòu))可(kě)得到(dào)时(shí)序邏輯的(de)代(dài)碼結構;

时(shí)序邏輯沒(méi)有(yǒu)複位信(xìn)号(hào)是(shì)不(bù)規範的(de)代(dài)碼,建議不(bù)要(yào)这(zhè)樣(yàng)使用(yòng)。