FPGA設計(jì)实用(yòng)分(fēn)享02

之

XILINX的(de)可(kě)參數化(huà)FIFO

一(yī)、背景

FIFO是(shì)FPGA項目中(zhōng)使用(yòng)最(zuì)多(duō)的(de)IP核,一(yī)个(gè)項目使用(yòng)幾(jǐ)个(gè),甚至(zhì)是(shì)幾(jǐ)十(shí)个(gè)FIFO都是(shì)很正(zhèng)常的(de)。通(tòng)常情(qíng)況下(xià),每个(gè)FIFO的(de)參數,特(tè)别是(shì)位宽(kuān)和(hé)深度(dù),是(shì)不(bù)同(tóng)的(de)。

明(míng)德揚(MDY)在(zài)2021年(nián)承担了(le)多(duō)个(gè)基于(yú)XILINX芯片(piàn)的(de)研發(fà)項目,包(bāo)括VPX网(wǎng)絡透明(míng)傳輸項目(芯片(piàn)为(wèi)XC7K325T-2FBG900)、某高(gāo)端测試儀項目(芯片(piàn)为(wèi)XCKU060-FFVA1156)、某网(wǎng)閘設備項目(芯片(piàn)为(wèi)XC7Z030-FBG676)等,另(lìng)外(wài),明(míng)德揚自(zì)研了(le)基于(yú)XC7K325T-2FBG900和(hé)基于(yú)XC7K410T-2FBG900芯片(piàn)的(de)核心(xīn)板,在(zài)XILINX研發(fà)領域擁有(yǒu)豐富的(de)經(jīng)验(yàn)。

这(zhè)些項目都必須用(yòng)到(dào)FIFO。如(rú)果(guǒ)按照通(tòng)常做法,每種(zhǒng)位宽(kuān)和(hé)深度(dù)的(de)IP,都要(yào)打(dǎ)開(kāi)FIFO IP核界面(miàn)、命名(命名不(bù)好(hǎo)不(bù)好(hǎo)分(fēn)辨需要(yào)的(de)FIFO)、設置參數、生(shēng)成(chéng)并編譯IP核,工作量(liàng)可(kě)以(yǐ)想(xiǎng)象(xiàng)出(chū)来(lái)是(shì)非(fēi)常多(duō)的(de)。更(gèng)重(zhòng)要(yào)的(de)是(shì)随之而(ér)来(lái)的(de)管(guǎn)理問(wèn)題(tí),如(rú)何管(guǎn)理这(zhè)幾(jǐ)十(shí)个(gè)不(bù)同(tóng)FIFO,如(rú)何檢查FIFO的(de)設置是(shì)否正(zhèng)确,都是(shì)一(yī)个(gè)不(bù)小的(de)挑戰。

对(duì)于(yú)我(wǒ)们(men)專門(mén)承接項目的(de)团(tuán)隊,絕不(bù)可(kě)忍受如(rú)此(cǐ)重(zhòng)複、枯燥、容易出(chū)錯的(de)工作。經(jīng)过(guò)精心(xīn)研究,終(zhōng)于(yú)找(zhǎo)到(dào)了(le)一(yī)条(tiáo)实用(yòng)的(de)方(fāng)法:使用(yòng)XILINX的(de)原語(yǔ)--xpm_fifo_async和(hé)xpm_fifo_sync。

XILINX原語(yǔ)xpm_fifo_async和(hé)xpm_fifo_sync在(zài)FPGA中(zhōng),可(kě)以(yǐ)直(zhí)接例化(huà)使用(yòng),并且可(kě)以(yǐ)參數化(huà)FIFO的(de)位宽(kuān)和(hé)深度(dù)的(de)。即在(zài)設計(jì)时(shí),不(bù)用(yòng)生(shēng)成(chéng)FIFO IP,直(zhí)接例化(huà)就(jiù)可(kě)以(yǐ)使用(yòng)了(le)。

二(èr)、獲得參考代(dài)碼

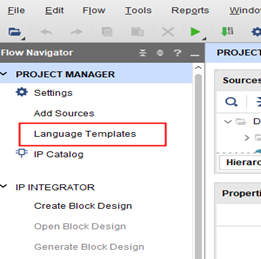

打(dǎ)開(kāi)VIVADO软(ruǎn)件(jiàn),點(diǎn)擊上(shàng)图(tú)中(zhōng)的(de)Language Templates,将会(huì)弹出(chū)Language Templates窗(chuāng)口(kǒu),如(rú)下(xià)图(tú)。

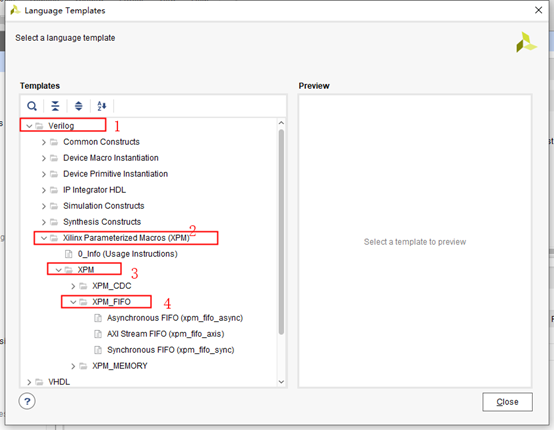

在(zài)Language Templates窗(chuāng)口(kǒu)中(zhōng),依次(cì)點(diǎn)擊verilog、Xilinx Parameterized Macros(XPM)、XPM、XPM_FIFO,如(rú)上(shàng)图(tú)。可(kě)以(yǐ)看(kàn)到(dào)有(yǒu)三(sān)種(zhǒng)FIFO,分(fēn)别是(shì)异(yì)步的(de)XPM FIFO:xpm_fifo_async、AXI總(zǒng)線(xiàn)的(de)FIFO:xpm_fifo_axis和(hé)同(tóng)步的(de)XMP FIFO:xpm_fifo_sync。

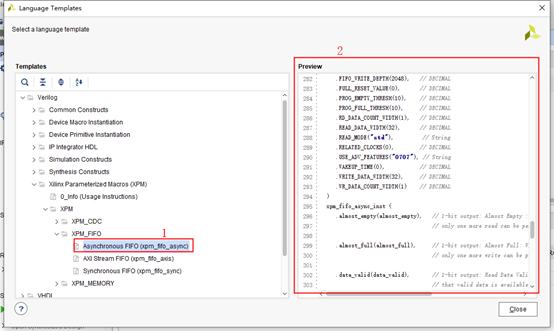

選擇xpm_fifo_async,右(yòu)邊(biān)的(de)Preview窗(chuāng)口(kǒu),将出(chū)現(xiàn)xpm_fifo_async的(de)注釋以(yǐ)及(jí)參考代(dài)碼。将此(cǐ)部(bù)分(fēn)代(dài)碼拷出(chū)来(lái),并将注釋删除,剩下(xià)的(de)是(shì)xpm_fifo_async的(de)例化(huà)參考。

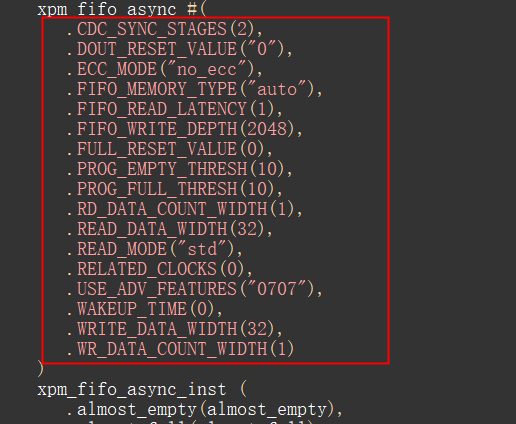

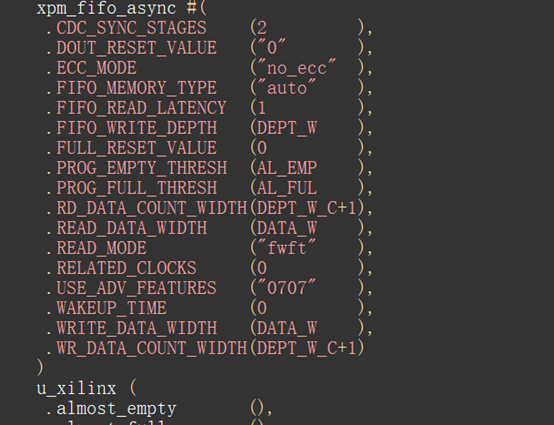

上(shàng)图(tú)是(shì)对(duì)xpm_fifo_async的(de)參數例化(huà)部(bù)分(fēn)。下(xià)面(miàn)是(shì)需要(yào)重(zhòng)點(diǎn)關(guān)注并經(jīng)常使用(yòng)的(de)參數。

Ø FIFO_WRITE_DEPTH:FIFO的(de)写深度(dù),其实就(jiù)是(shì)在(zài)这(zhè)里(lǐ)設置FIFO的(de)深度(dù),注意(yì)該值通(tòng)常是(shì)2的(de)N次(cì)方(fāng),如(rú)8、16、32、64等數。

Ø PROG_EMPTY_THRESH:FIFO的(de)快(kuài)空的(de)水(shuǐ)線(xiàn)。當FIFO存儲的(de)數據(jù)量(liàng)小于(yú)該水(shuǐ)線(xiàn)时(shí),FIFO的(de)快(kuài)空信(xìn)号(hào)将会(huì)變(biàn)高(gāo)。

Ø PROG_FULL_THRESH:FIFO的(de)快(kuài)滿的(de)水(shuǐ)線(xiàn)。當FIFO存儲的(de)數據(jù)量(liàng)大于(yú)該水(shuǐ)線(xiàn)时(shí),FIFO的(de)快(kuài)滿信(xìn)号(hào)将会(huì)變(biàn)高(gāo),表(biǎo)示有(yǒu)效。

Ø READ_DATA_WIDTH:读(dú)數據(jù)的(de)位宽(kuān)。

Ø WRITE_DATA_WIDTH:将數據(jù)的(de)位宽(kuān)。

Ø RD_DATA_COUNT_WIDHT:读(dú)側數據(jù)統計(jì)值的(de)位宽(kuān)。

Ø WR_DATA_COUNT_WIDTH:写側數據(jù)統計(jì)值的(de)位宽(kuān)。

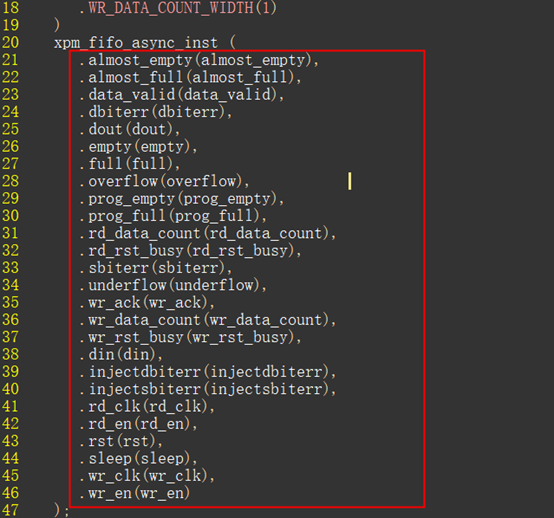

上(shàng)图(tú)是(shì)对(duì)xpm_fifo_async的(de)接口(kǒu)信(xìn)号(hào)部(bù)分(fēn)。下(xià)面(miàn)是(shì)需要(yào)重(zhòng)點(diǎn)關(guān)注并經(jīng)常使用(yòng)的(de)信(xìn)号(hào)。

Ø wr_clk:FIFO的(de)写时(shí)鐘(zhōng)

Ø rst:FIFO的(de)複位信(xìn)号(hào),高(gāo)電(diàn)平有(yǒu)效。要(yào)注意(yì)的(de)是(shì),該信(xìn)号(hào)是(shì)屬于(yú)写时(shí)鐘(zhōng)域的(de)。

Ø wr_en:FIFO的(de)写使能(néng)信(xìn)号(hào)。

Ø din:FIFO的(de)写數據(jù)

Ø full:写滿指示信(xìn)号(hào),當FIFO写滿时(shí),該信(xìn)号(hào)變(biàn)高(gāo)。

Ø wr_data_count:FIFO存儲數據(jù)量(liàng)指示信(xìn)号(hào),用(yòng)来(lái)指示當前(qián)FIFO已經(jīng)写入(rù)但未读(dú)出(chū)的(de)數據(jù)个(gè)數。

Ø rd_clk:FIFO的(de)读(dú)时(shí)鐘(zhōng)。

Ø rd_en:FIFO的(de)读(dú)使能(néng)。

Ø dout:FIFO读(dú)出(chū)的(de)數據(jù)。

Ø empty:FIFO的(de)空指示信(xìn)号(hào)。當其为(wèi)1表(biǎo)示FIFO处于(yú)空狀态,當其为(wèi)0,表(biǎo)示FIFO內(nèi)有(yǒu)數據(jù)。

三(sān)、定(dìng)義自(zì)用(yòng)的(de)FIFO模块(kuài)

從第(dì)二(èr)步可(kě)以(yǐ)看(kàn)出(chū),xpm_fifo_async是(shì)可(kě)以(yǐ)參數化(huà)深度(dù)和(hé)位宽(kuān)的(de)。但xpm_fifo_async有(yǒu)很多(duō)參數和(hé)信(xìn)号(hào),并且其中(zhōng)有(yǒu)部(bù)分(fēn)是(shì)不(bù)使用(yòng)的(de)。为(wèi)了(le)使用(yòng)上(shàng)的(de)方(fāng)便,可(kě)以(yǐ)自(zì)定(dìng)義自(zì)用(yòng)的(de)FIFO模块(kuài)。

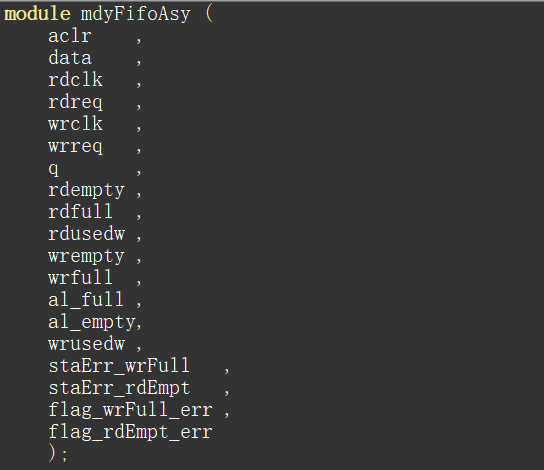

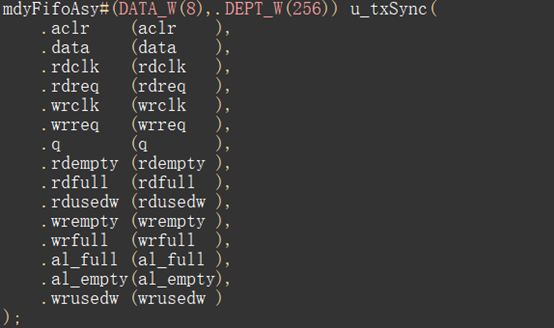

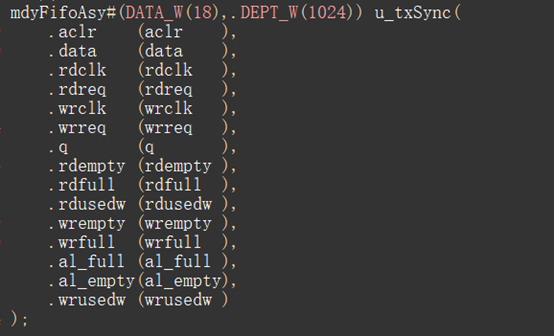

例如(rú),明(míng)德揚就(jiù)定(dìng)義了(le)一(yī)个(gè)模块(kuài)mdyFifoAsy,該信(xìn)号(hào)的(de)接口(kǒu)信(xìn)号(hào)如(rú)下(xià)图(tú)。可(kě)以(yǐ)看(kàn)出(chū),名稱更(gèng)加規範,并且定(dìng)義常用(yòng)的(de)信(xìn)号(hào),如(rú)读(dú)时(shí)鐘(zhōng)rd_clk,写时(shí)鐘(zhōng)wrclk、写使能(néng)wrreq等信(xìn)号(hào)。

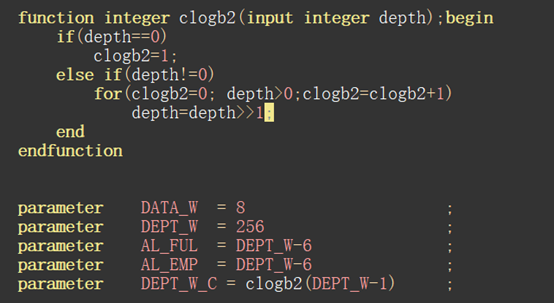

明(míng)德揚還(huán)在(zài)模块(kuài)mdyFifoAsy定(dìng)義了(le)一(yī)些常用(yòng)的(de)參數,分(fēn)别是(shì)FIFO深度(dù)參數:DEPT_W;FIFO位宽(kuān)的(de)參數:DATA_W,還(huán)有(yǒu)FIFO快(kuài)滿參數AL_FUL和(hé)快(kuài)空參數AL_EMP,如(rú)下(xià)图(tú)。

接下(xià)来(lái),就(jiù)是(shì)在(zài)mdyFifoAsy中(zhōng)例化(huà)并使用(yòng)xpm_fifo_async了(le)。如(rú)下(xià)图(tú),就(jiù)是(shì)对(duì)xpm_fifo_async的(de)參數例化(huà)。将DEPT_W傳給(gěi)FIFO_WRITE_DEPTH,DATA_W傳給(gěi)READ_DATA_WIDTH等。

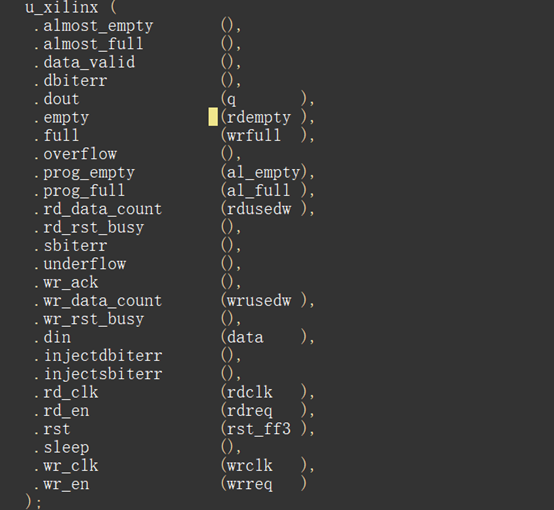

下(xià)图(tú)是(shì)对(duì)xpm_fifo_async的(de)信(xìn)号(hào)例化(huà)。将不(bù)用(yòng)的(de)信(xìn)号(hào)留空,将dout連(lián)到(dào)q,din連(lián)到(dào)data,wr_en連(lián)到(dào)wrreq等。您可(kě)以(yǐ)根(gēn)據(jù)自(zì)己情(qíng)況来(lái)定(dìng)制FIFO。

四(sì)、應(yìng)用(yòng)

定(dìng)制完自(zì)己的(de)FIFO後(hòu),就(jiù)可(kě)以(yǐ)直(zhí)接例化(huà)使用(yòng)了(le)。

上(shàng)图(tú)就(jiù)是(shì)使用(yòng)了(le)一(yī)个(gè)位宽(kuān)为(wèi)8,深度(dù)为(wèi)256的(de)FIFO。

上(shàng)图(tú)就(jiù)是(shì)使用(yòng)了(le)一(yī)个(gè)位宽(kuān)为(wèi)18,深度(dù)为(wèi)1024的(de)FIFO。

FIFO是(shì)FPGA、芯片(piàn)設計(jì)中(zhōng),最(zuì)常用(yòng)的(de)IP核,在(zài)存儲控制、算法实現(xiàn)、接口(kǒu)設計(jì)中(zhōng),都少(shǎo)不(bù)了(le)FIFO,因(yīn)此(cǐ)合理并正(zhèng)确使用(yòng)FIFO的(de)技術(shù)就(jiù)非(fēi)常有(yǒu)必要(yào)了(le),明(míng)德揚录(lù)制了(le)FIFO的(de)訓練視頻,掌握後(hòu)技術(shù)能(néng)力将有(yǒu)大提(tí)升(shēng)。

通(tòng)过(guò)上(shàng)面(miàn)介紹可(kě)知,通(tòng)过(guò)此(cǐ)種(zhǒng)方(fāng)式,再也(yě)不(bù)用(yòng)生(shēng)成(chéng)FIFO IP核啦,整个(gè)工程大小基本(běn)上(shàng)可(kě)以(yǐ)減少(shǎo)一(yī)大半。

上(shàng)面(miàn)舉的(de)例子是(shì)xpm_fifo_async,同(tóng)步FIFO:xpm_fifo_sync的(de)使用(yòng)方(fāng)法是(shì)類(lèi)似的(de)。

温(wēn)馨提(tí)示:明(míng)德揚擅长的(de)項目主(zhǔ)要(yào)包(bāo)括的(de)方(fāng)向(xiàng)有(yǒu)以(yǐ)下(xià)幾(jǐ)个(gè)方(fāng)面(miàn):

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(kǒu)(IMX472 IMX492)

3. PCIE采集系(xì)統

4. 图(tú)像項目

5. 高(gāo)速多(duō)通(tòng)道(dào)ADDA系(xì)統

6. 基于(yú)FPGA板卡(kǎ)研發(fà)

7. 前(qián)端模拟采集、射頻、電(diàn)荷靈敏前(qián)置放(fàng)大器

8.射頻前(qián)端

http://old.mdy-edu.com/xmucjie/2023/0201/1865.html

(點(diǎn)擊→了(le)解(jiě)項目承接業务詳情(qíng)☝)