本(běn)文(wén)为(wèi)明(míng)德揚原創文(wén)章(zhāng),轉(zhuǎn)载請注明(míng)出(chū)处!

最(zuì)近(jìn)公司承接了(le)一(yī)个(gè)車载視頻拼接的(de)項目,該項目使用(yòng)到(dào)了(le)LVDS高(gāo)速接口(kǒu)和(hé)DDR3接口(kǒu),攝像头(tóu)采集的(de)視頻图(tú)像數據(jù)需要(yào)先(xiān)存入(rù)DDR3中(zhōng)然後(hòu)與(yǔ)通(tòng)过(guò)LVDS傳輸的(de)主(zhǔ)機(jī)視頻數據(jù)進(jìn)行拼接輸出(chū),最(zuì)終(zhōng)在(zài)屏幕上(shàng)顯示画(huà)中(zhōng)画(huà)的(de)效果(guǒ)。在(zài)調試DDR3的(de)过(guò)程中(zhōng),我(wǒ)有(yǒu)一(yī)些使用(yòng)心(xīn)得,特(tè)分(fēn)享給(gěi)大家(jiā)。

在(zài)之前(qián)的(de)文(wén)章(zhāng)中(zhōng)我(wǒ)已經(jīng)介紹过(guò)Lattice DDR3的(de)IP核生(shēng)成(chéng)使用(yòng)方(fāng)法,以(yǐ)及(jí)接口(kǒu)信(xìn)号(hào)。也(yě)许有(yǒu)许多(duō)人(rén)不(bù)是(shì)很明(míng)白,明(míng)明(míng)有(yǒu)DDR3的(de)IP核,为(wèi)什麼(me)還(huán)要(yào)添加这(zhè)麼(me)一(yī)个(gè)接口(kǒu)模块(kuài),添加了(le)这(zhè)麼(me)一(yī)个(gè)接口(kǒu)模块(kuài)主(zhǔ)要(yào)是(shì)用(yòng)来(lái)做什麼(me),需要(yào)它(tā)設計(jì)哪些信(xìn)号(hào)?

要(yào)想(xiǎng)解(jiě)決这(zhè)些疑問(wèn),我(wǒ)们(men)就(jiù)需要(yào)先(xiān)搞清(qīng)楚DDR3 IP核究竟是(shì)用(yòng)来(lái)做什麼(me)的(de)。首先(xiān)我(wǒ)们(men)先(xiān)明(míng)白这(zhè)樣(yàng)一(yī)个(gè)概念:DDR3是(shì)一(yī)个(gè)

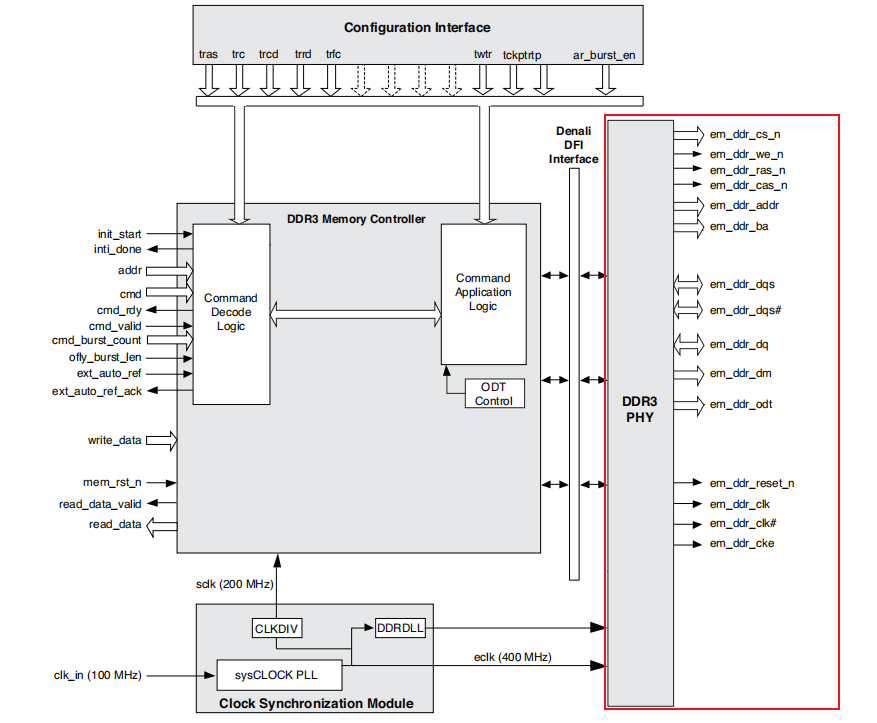

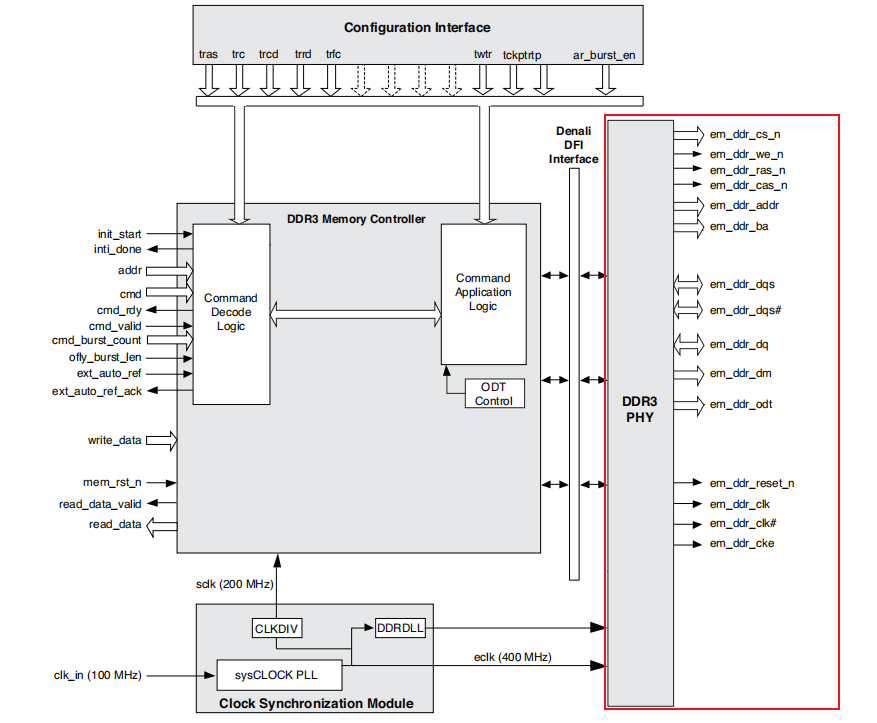

FPGA片(piàn)外(wài)的(de)一(yī)个(gè)設備,就(jiù)像我(wǒ)们(men)用(yòng)FPGA控制led燈(dēng)的(de)亮(liàng)滅一(yī)樣(yàng),我(wǒ)们(men)通(tòng)过(guò)引脚将FPGA與(yǔ)led燈(dēng)連(lián)接起来(lái),并且引脚信(xìn)号(hào)是(shì)用(yòng)工程中(zhōng)設置的(de)輸入(rù)輸出(chū)来(lái)控制。也(yě)就(jiù)是(shì)说(shuō),虽然一(yī)个(gè)工程中(zhōng)有(yǒu)许多(duō)个(gè)模块(kuài),每个(gè)模块(kuài)間(jiān)又有(yǒu)各(gè)種(zhǒng)各(gè)樣(yàng)的(de)輸入(rù)輸出(chū),但是(shì)这(zhè)些信(xìn)号(hào)都只(zhī)是(shì)在(zài)FPGA內(nèi)部(bù),由(yóu)FPGA産生(shēng)并控制的(de)內(nèi)部(bù)信(xìn)号(hào),工程真(zhēn)正(zhèng)的(de)輸入(rù)輸出(chū)是(shì)FPGA外(wài)部(bù)器件(jiàn)通(tòng)过(guò)引脚連(lián)接傳遞的(de)信(xìn)号(hào)。若我(wǒ)们(men)使用(yòng)FPGA控制外(wài)設接口(kǒu)工作,最(zuì)起碼需要(yào)有(yǒu)一(yī)个(gè)輸入(rù)时(shí)鐘(zhōng)(由(yóu)FPGA外(wài)部(bù)晶振産生(shēng))以(yǐ)及(jí)與(yǔ)外(wài)設相連(lián)的(de)輸出(chū)信(xìn)号(hào)(有(yǒu)的(de)情(qíng)況下(xià)沒(méi)有(yǒu)异(yì)步複位輸入(rù)也(yě)是(shì)可(kě)以(yǐ)工作的(de)),那(nà)麼(me)这(zhè)个(gè)时(shí)鐘(zhōng)以(yǐ)及(jí)輸出(chū)信(xìn)号(hào)就(jiù)是(shì)FPGA的(de)I/O口(kǒu)。同(tóng)樣(yàng)的(de),在(zài)我(wǒ)们(men)調試DDR3的(de)过(guò)程中(zhōng),我(wǒ)们(men)需要(yào)的(de)I/O就(jiù)是(shì)时(shí)鐘(zhōng)以(yǐ)及(jí)複位信(xìn)号(hào),還(huán)有(yǒu)就(jiù)是(shì)與(yǔ)DDR3硬(yìng)件(jiàn)的(de)連(lián)接处I/O口(kǒu)。我(wǒ)们(men)先(xiān)来(lái)看(kàn)一(yī)下(xià)數據(jù)手(shǒu)册上(shàng)DDR3 IP核控制框图(tú),如(rú)下(xià)所(suǒ)示。

图(tú)1 DDR3控制框图(tú)

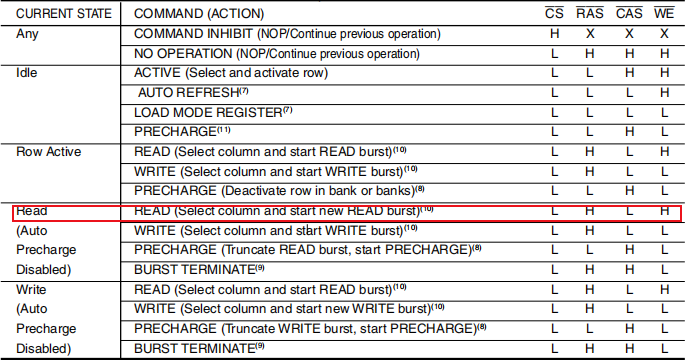

图(tú)中(zhōng)用(yòng)紅(hóng)線(xiàn)标(biāo)記(jì)起来(lái)的(de)地(dì)方(fāng)就(jiù)是(shì)FPGA與(yǔ)外(wài)部(bù)DDR3通(tòng)过(guò)引脚連(lián)接的(de)接口(kǒu)信(xìn)号(hào),如(rú)果(guǒ)我(wǒ)们(men)通(tòng)过(guò)FPGA內(nèi)部(bù)産生(shēng)數據(jù)并将其送入(rù)DDR3中(zhōng)後(hòu)读(dú)出(chū),就(jiù)是(shì)通(tòng)过(guò)这(zhè)些引脚来(lái)傳輸信(xìn)号(hào)的(de)。我(wǒ)们(men)使用(yòng)SDRAM進(jìn)行存儲,是(shì)直(zhí)接控制这(zhè)些輸出(chū)信(xìn)号(hào)如(rú)CAS、RAS、CKE等控制SDRAM读(dú)写以(yǐ)及(jí)其他(tā)各(gè)操作的(de),如(rú)下(xià)图(tú)就(jiù)是(shì)SDRAM的(de)輸出(chū)控制信(xìn)号(hào),通(tòng)过(guò)FPGA內(nèi)部(bù)設計(jì)CS、RAS、CAS、WE这(zhè)些信(xìn)号(hào),可(kě)以(yǐ)讓SDRAM实現(xiàn)对(duì)應(yìng)的(de)操作。比如(rú)我(wǒ)们(men)設計(jì)一(yī)个(gè)SDRAM读(dú)操作,那(nà)麼(me)我(wǒ)们(men)就(jiù)需要(yào)設計(jì)CS、RAS、CAS、WE分(fēn)别为(wèi)0、1、0、1,SDRAM通(tòng)过(guò)引脚接收(shōu)到(dào)这(zhè)些信(xìn)号(hào),便会(huì)産生(shēng)对(duì)應(yìng)的(de)操作,即打(dǎ)開(kāi)一(yī)个(gè)新的(de)列地(dì)址并開(kāi)始一(yī)个(gè)新的(de)突發(fà)读(dú)操作。

图(tú)2 SDRAM輸出(chū)控制指令

與(yǔ)設計(jì)SDRAM接口(kǒu)不(bù)同(tóng)的(de)是(shì),我(wǒ)们(men)在(zài)使用(yòng)DDR3时(shí),是(shì)不(bù)需要(yào)我(wǒ)们(men)親自(zì)設計(jì)这(zhè)些輸出(chū)信(xìn)号(hào), 因(yīn)为(wèi)我(wǒ)们(men)調用(yòng)的(de)DDR3 IP核已經(jīng)幫我(wǒ)们(men)內(nèi)部(bù)封(fēng)裝(zhuāng)好(hǎo)了(le)这(zhè)些指令,我(wǒ)们(men)需要(yào)設計(jì)的(de)是(shì)輸入(rù)IP核的(de)那(nà)部(bù)分(fēn)接口(kǒu)信(xìn)号(hào),来(lái)告訴IP核我(wǒ)们(men)想(xiǎng)讓DDR3進(jìn)行工作的(de)模式以(yǐ)及(jí)需要(yào)DDR3進(jìn)行的(de)操作。在(zài)設計(jì)这(zhè)个(gè)接口(kǒu)模块(kuài)的(de)时(shí)候,我(wǒ)们(men)需要(yào)設計(jì)的(de)就(jiù)是(shì)图(tú)1左(zuǒ)側接口(kǒu)的(de)那(nà)部(bù)分(fēn)信(xìn)号(hào),各(gè)信(xìn)号(hào)的(de)功能(néng)以(yǐ)及(jí)时(shí)序在(zài)數據(jù)手(shǒu)册上(shàng)有(yǒu)詳细(xì)的(de)说(shuō)明(míng)(在(zài)我(wǒ)前(qián)面(miàn)的(de)文(wén)章(zhāng)中(zhōng)也(yě)有(yǒu)詳细(xì)的(de)介紹),这(zhè)需要(yào)我(wǒ)们(men)一(yī)邊(biān)对(duì)照着數據(jù)手(shǒu)册一(yī)邊(biān)進(jìn)行設計(jì),具體(tǐ)的(de)設計(jì)方(fāng)法我(wǒ)将会(huì)在(zài)接下(xià)来(lái)的(de)文(wén)章(zhāng)中(zhōng)繼續介紹。

温(wēn)馨提(tí)示:明(míng)德揚除了(le)培訓学習還(huán)有(yǒu)項目承接業务,擅长的(de)項目主(zhǔ)要(yào)包(bāo)括的(de)方(fāng)向(xiàng)有(yǒu)以(yǐ)下(xià)幾(jǐ)个(gè)方(fāng)面(miàn):

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(kǒu)(IMX472 IMX492)

3. PCIE采集系(xì)統

4. 图(tú)像項目

5. 高(gāo)速多(duō)通(tòng)道(dào)ADDA系(xì)統

6. 基于(yú)FPGA板卡(kǎ)研發(fà)

7. 多(duō)通(tòng)道(dào)高(gāo)靈敏電(diàn)荷放(fàng)大器

8.射頻前(qián)端

http://old.mdy-edu.com/xmucjie/2023/0201/1865.html

(點(diǎn)擊→了(le)解(jiě)項目承接業务詳情(qíng)☝)

需要(yào)了(le)解(jiě)相關(guān)信(xìn)息可(kě)以(yǐ)聯系(xì):吴老(lǎo)师(shī)18022857217(微信(xìn)同(tóng)号(hào))